Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

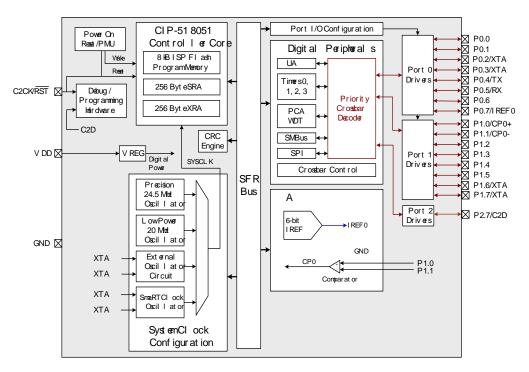

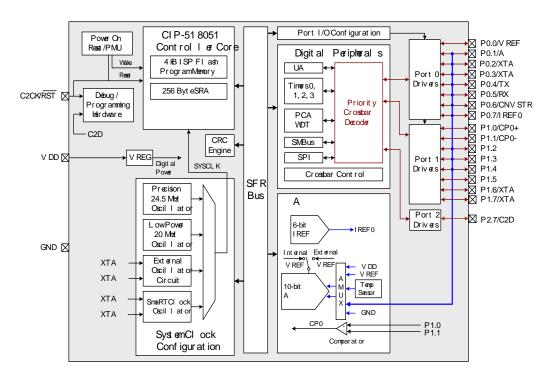

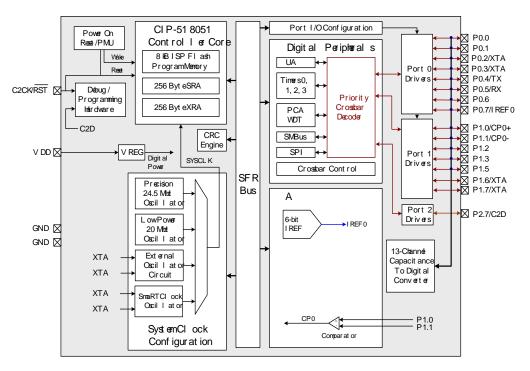

| Core Processor             | CIP-51 8051                                                     |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 16                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                |                                                                 |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 9x12b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 20-UFQFN Exposed Pad                                            |

| Supplier Device Package    | 20-QFN (3x3)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f980-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 6.2. I REF 0 Specifications                              |     |

|-----|----------------------------------------------------------|-----|

| 7.  | Comparator                                               | 93  |

|     | 7.1. Comparat or I nput s                                | 93  |

|     | 7.2. Comparat or Out put s                               | 94  |

|     | 7.3. Comparator Response Time                            |     |

|     | 7.4. Comparator Hysteresis                               |     |

|     | 7.5. Comparator Register Descriptions                    |     |

|     | 7.6. Comparat or 0 A r                                   | 98  |

| 8.  | Capacitive Sense (CS0)                                   | 100 |

| ••• | 8.1. Configuring Port Pinsa Sapacitive Sensel nput s     |     |

|     | 8.2. Initial izing the Capacitive Sensing Peripheral     |     |

|     | 8.3. Capacit iv eSenseSt art -Of-Conversion Sources      |     |

|     | 8.4. CS0 Mul t ipl eChannel Enabl e                      |     |

|     | 8.5. CS0 Gain A                                          |     |

|     | 8.6. WalefromSuspend                                     |     |

|     | 8.7. Using CS0 in A that Util izeSI eep Mode             | 102 |

|     | 8.8. A $bod 1 CSO MEN = 0$                               | 102 |

|     | 8.9. A $\operatorname{bod} 2 \operatorname{CSOSMEN} = 1$ |     |

|     | 8.10.CS0 Compar at or                                    |     |

|     | 8.11.CS0 Conversion A                                    |     |

|     | 8.12.CS0 Pin Monit or                                    |     |

|     | 8.12.C30 F III WOINT OF                                  |     |

|     |                                                          |     |

| •   | 8.14.Capacit iv eSenseMul t ipl exer                     |     |

| э.  |                                                          |     |

|     | 9.1. Performance                                         |     |

|     | 9.2. Programming and Debugging Support                   |     |

|     | 9.3. Instruction Set                                     |     |

|     | 9.3.1. I nst ruct ion and CPU Timing                     |     |

| 40  | 9.4. CIP-51 Regist er Descript ions                      |     |

| 10  | . Memory Organization                                    |     |

|     | 10.1.ProgramMemory                                       |     |

|     | 10.1.1.MOV X I nst ruct ion and Pogram Memory            |     |

|     | 10.2.Dat a Memory                                        |     |

|     | 10.2.1.Internal RA                                       |     |

|     | 10.2.2.External RA                                       |     |

| 11  | . On-Chip XRAM                                           |     |

|     | 11.1.A                                                   |     |

|     | 11.1.1.16-Bit MOV X Exampl e                             |     |

|     | 11.1.2.8-Bit MOV X Example.                              |     |

| 12  | Special Function Registers                               |     |

|     | 12.1.SF R Paging                                         |     |

| 13  | Interrupt Handler                                        |     |

|     | 13.1.Enabling Interrupt Sources                          |     |

|     | 13.2.MCUInterrupt Sourceseand Vectors                    |     |

|     | 13.3.Interrupt Priorities                                | 139 |

| Figure24.4.4-WireSingleMasterMode and 4-WireSlaveModeConn<br>268 | æt ion Diagram |

|------------------------------------------------------------------|----------------|

| Figure24.5. Master ModeData/CI ockTiming                         | 270            |

|                                                                  | 270            |

| <b>U</b>                                                         |                |

| Figure24.8. SPI Master Timing (CKPHA                             | 275            |

| Figure24.9. SPI Master Timing (CKPHA                             | 275            |

| Figure24.10. SPI SI av eTiming (KCPHA                            |                |

| Figure24.11. SPI SI av eTiming (CCPHA                            |                |

| Figur e25.1. T0 Mode0 BI ockDiagr am                             |                |

| Figur e25.2. T0 Mode2 BI ockDiagr am                             |                |

| Figur e25.3. T0 Mode3 BI ockDiagr am                             | 283            |

| Figure25.4. Timer 2 16-Bit Mode BI ockDiagram                    |                |

| Figure25.5. Timer 2 8-Bit Mode BI ockDiagram                     |                |

| Figur e25.6. Timer 2 Capt ur eModeBI ockDiagr am                 | 290            |

| Figure25.7. Timer 3 16-Bit Mode BI ockDiagram                    | 294            |

| Figure25.8. Timer 3 8-Bit Mode BI ockDiagram                     | 295            |

| Figur e25.9. Timer 3 Capt ur eModeBl ockDiagr am                 |                |

| Figure26.1. PCA                                                  |                |

| Figure26.2. PCA BI ockDiagram                                    | 301            |

| Figur e26.3. PCA ckDiagr am                                      | 302            |

| Figur e26.4. PCA gr am                                           | 304            |

| Figure26.5. PCA r ModeDiagram                                    |                |

| Figur e26.6. PCA put ModeDiagram                                 | 306            |

| Figur e26.7. PCA cy Out put Mode                                 | 307            |

| Figur e26.8. PCA Diagr am                                        |                |

| Figur e26.9. PCA t PWM ModeDiagram.                              | 309            |

| F igur e26.10. PCA                                               |                |

| Figure26.11. PCA mer Enabled                                     |                |

| Figure27.1. Typical C2 Pin Shaing                                | 322            |

|                                                                  |                |

#### 1.5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low **Power Burst Mode**

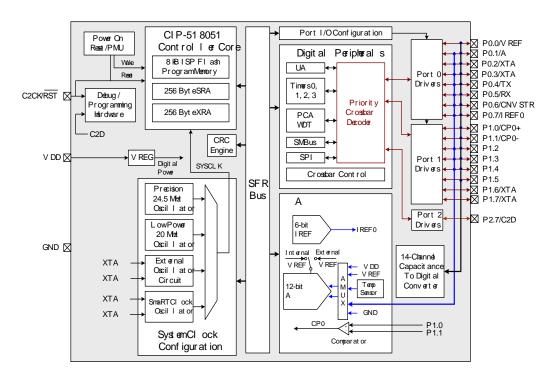

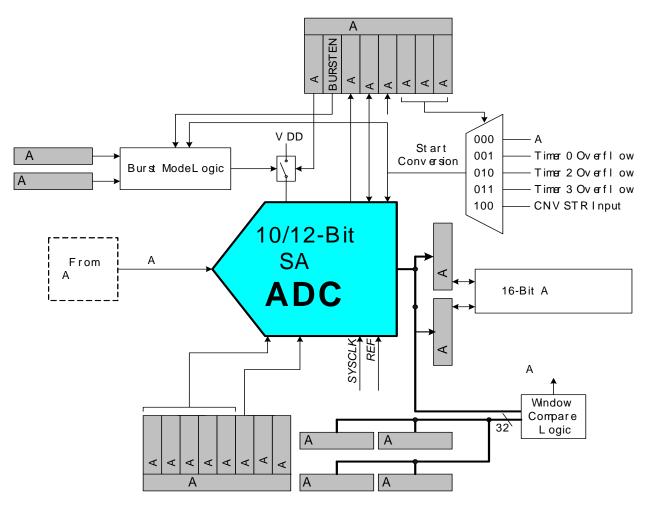

C8051F99x-C8051F98x devices have a 300 keps, 10-bit or 75 keps 12-bit successive approximationd programmabl ewindowdet ect or. A register (SA autonomous I ow power Burst Mode which can automatical I y enable A samples, then place A modewithout CPU intervention. It al so has a 16-bit accumul at or that can automatical I yaverage the A sults providing an effective 11, 12, or 13 bit A result without any additional CPU intervention.

#### TheA

Figure 1.17) and has an on-chip at tenuat or that al lowsit to measure vol tages up ttowice the vol tager eference A onal A

temperaturesensor, the VDD supply voltage and the internal digital supply voltage

Figure 1.16. ADC0 Functional Block Diagram

\*Note: Signal only avail abl eon 'F986, 'F988, and 'F996 devices.

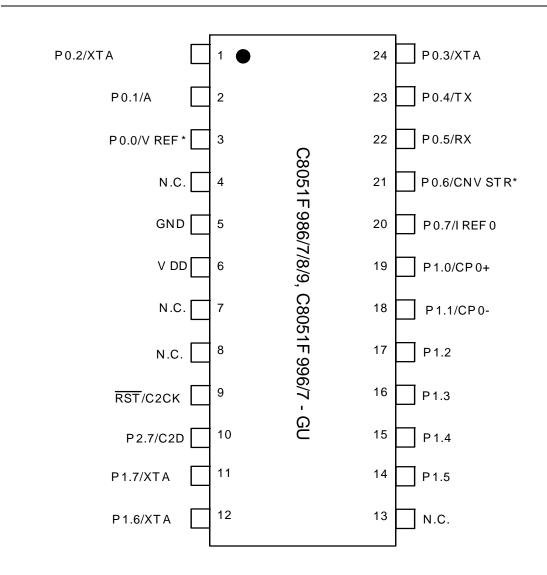

### Figure 3.3. QSOP-24 Pinout Diagram (Top View)

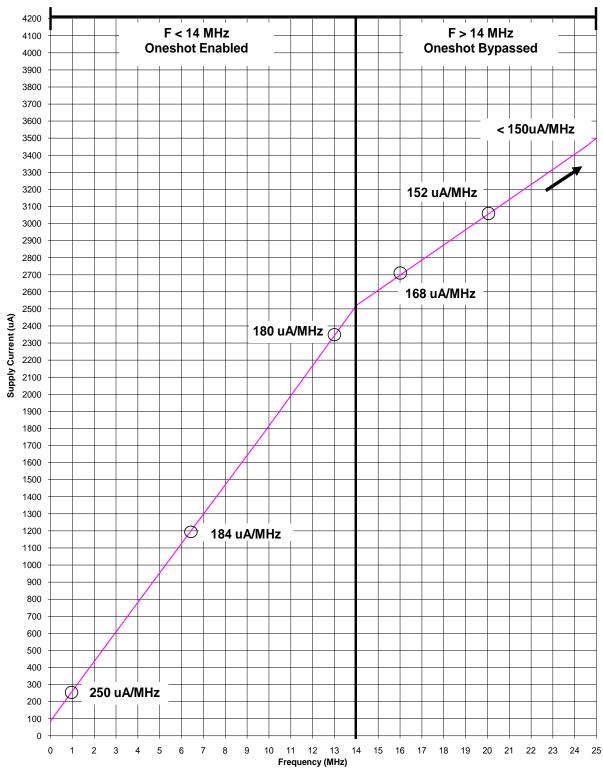

Figure 4.1. Active Mode Current (External CMOS Clock)

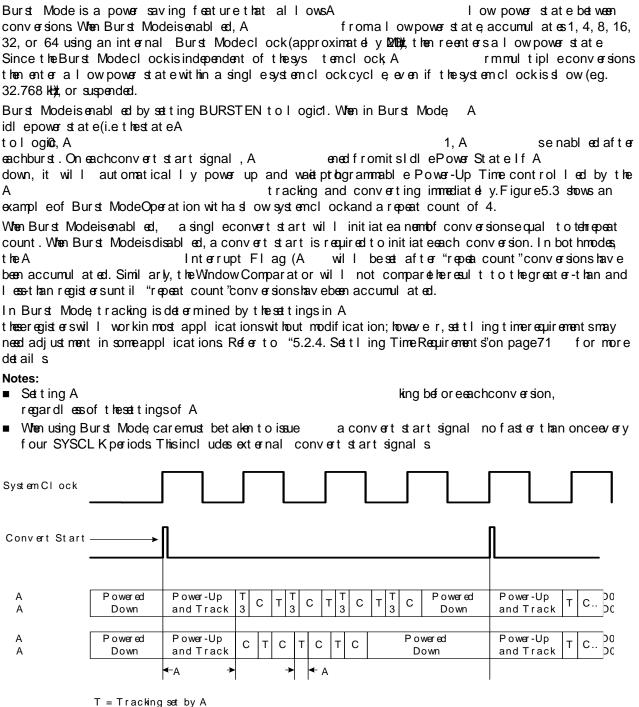

#### 5.2.3. Burst Mode

T = Tracking set by A T3 = Tracking set by A C = Converting

Figure 5.3. Burst Mode Tracking Example with Repeat Count Set to 4

### 8.12. CS0 Pin Monitor

The CS0 modul eprovides accurate conversions in all operating modes of the CPU, peripheral s and I/O ports Pin monitoring circuits are provided to imprevint erference immunity from high current output pin switching. The CS0 Pin Monitor register (CS0 PM, SFR Definition 8.14) control stheoperation of these pin monitors

Conversions in the CS0 modul ear eimmune to any change on digital inputs and immune to most output switching. Even high speed serial data transmission will not aff@ct\$00 operation as long as the output load is limited. Output changest hatswitch largel oads such as LEDs and heavily-loaded communications lines can affect conversion accuracy. For this reason, the CS0 modul eincludes pin monitoring circuits that will, if enabled, automatical ly adjust conversion timing if necessary tion at temany effect from high current output pin switching.

Thepin monitor enable bit should be set for any output signal that is expected to drive a largeload.

Example The SMB us in a system is heavily loaded wit h multiples aves and a long PCB route Set the SMB us pin monitor enable, SMB PM = 1.

Example Timer2 control san LED on Port 1, pôinto povidevariable dimming. Set the Port SFR write monitor enable, PIOPM = 1.

Example The SPI busisused to communicate to a nearby host. The pin monitor is not needed because the output is not heavily I oaded, SPIP Memains = 0, the default reset state

Pin monitors should not be enabled unless they are required. The pin monitor works by repeating any portion of a conversion that may have been corrupted by a change on an output pin. Setting pin monitor enables bits will slow CS0 conversions.

The frequency of CS0 retry operations can be limited by setting the CSPMMD bits In the default (reset) state, all converter retry requestvisil beperformed. This is the recommended setting for all applications. The number of retries per conversion can be limited to either two or four retries by changing CSPMMD. Limiting the number of retries per conversion ensures that even in circumstances where extremely frequent high power output switching occurs, conversions will be completed, though the remay be some loss of accuracy due to switching noise

A an bedet ected by reading the Pin Monitor Event bit, CS0 PME, in register CS0 CN. This bit will be set if any CS0 converter retries have occurred. It remains set un til cleared by software or a device reset.

### 8.13. Adjusting CS0 For Special Situations

There are saveral configuration options in the CS0 modul edesigned to modify the operation of the circuit and address special situations. In particular, any noticuit with more than 500 ohms of series impedance between the sensor and the device pin may require ad just ments for optimal performance. Typical applications which may require adjust ments include

- Touchpanel sensors f abricated using a resist iv econduct or such as indium t in-oxide (ITO).

- Circuit susing a high valueseries resistor to is of at ethesensor element for high ESD protection.

# Most systems will require no fine tuning, and the default settings for CS0DT, CS0DR, CS0IA, CS0RP and CS0LP should be used.

### 12.1. SFR Paging

To accommodate more than 128 SFRs in the 0x80 to 0xFF address space, SFR paging has been imple - mented. By default, all SFR accesses target SFR Bye 0x0 to allow access to the registers listed in Table 12.1. During device initial ization, some SFRsI ocated on SFR Page 0xF may need to be accessed. Table 12.2.1 ists the SFRs accessible from SFR Page 0x0F. Some SFRs are accessible from both pages, including the SFRPA r. SFRs only accessible from Page 0xF are in **bold**.

Thefol I owing procedure should be used when accessing SFRson Page 0xF:

- 1. Savethecurrent interrupt state(EA

- 2. Disable Interrupts (EA

- 3. Set SFRPA

- 4. A

- 5. Set SFRPA

- 6. Restore interrupt state (EA

| F8  |           |         |         |          |          |         |        |        |

|-----|-----------|---------|---------|----------|----------|---------|--------|--------|

| F0  | В         |         |         | CS0MD3   |          |         | EI P1  | El P2  |

| E8  |           |         |         |          |          |         |        |        |

| E0  | А         |         | REVID   | DEVICEID |          | FLWR    | EI E1  | EI E2  |

| D8  |           |         |         |          |          |         | CS0PM  |        |

| D0  | PSW       |         |         |          |          |         |        |        |

| C8  |           |         |         |          |          |         |        |        |

| C0  |           |         |         |          |          |         |        |        |

| B8  |           | IREF0CF |         | А        | А        |         |        |        |

| B0  |           |         |         |          |          | PMU0MD  |        |        |

| А   | ΙE        | CL KSEL |         |          |          |         |        |        |

| А   | P2        |         |         |          |          |         |        | SF RPA |

| 98  |           | P0DRV   | CRC0CNT | P1DRV    | CRC0FLIP | P2DRV   | CRC0A  |        |

| 90  | P1        |         |         |          |          |         |        |        |

| 88  |           |         |         |          |          | TOFFL   | TOFFH  |        |

| 80  | P0        | SP      | DP L    | DPH      | CRC0CN   | CRC0I N | CRC0DA | PCON   |

|     | 0(8)      | 1(9)    | 2(A     | 3(B)     | 4(C)     | 5(D)    | 6(E)   | 7(F)   |

| (bi | taddressa | ble)    |         |          |          |         |        |        |

#### Table 12.2. Special Function Register (SFR) Memory Map (Page 0xF)

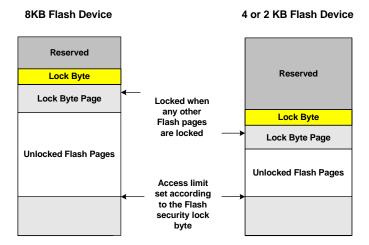

### 14.3. Security Options

The CIP-51 provides security options to protect the FI ashmemory from inadvertent modification by soft ware as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the FI ashmemory from accident almodification by soft ware PSWE must be explicitly set to 1 before soft ware can modify the FI ashmemory; both PSWE and PSEE must be set to 1 before soft ware can erase FI ashmemory. A

constantsfrombeng read or al tered across the C2 interface

A ash user space of fersprotection of the FI ashprogram memory from access (reads, writes, or erases) by unprotected code or the C2 interface See Section "10. Memory Organization" on page 128 for the location of these curity byte The FI ashsecurity mechanismal I owsthe user to I ockn 512-byte FI ashpages, starting at page 0 (addresses 0x0000 to 0x01 FF), where *n* is the 1s complement number represented by the Security Lock Byte The page containing the Flash Security Lock Byte is unlocked when no other Flash pages are locked (all bits of the Lock Byte are 1) and locked when any other Flash pages are locked (any bit of the Lock Byte is 0).

| SecurityLockByte  | 1111 1011b                              |

|-------------------|-----------------------------------------|

| onesComplement:   | 0000 0100b                              |

| Flashpageslocked: | 5 (First four FI ashpages+LockBytePage) |

Figure 14.1. Flash Program Memory Map (8 kB and smaller devices)

The level of FI ash security depends on the FI ash access method. The three FI ash access methods that can be restricted are reads, writes, an der assist from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on I ocked pages. Table 14.1 summarizes the FI ash security features of the C8051F99x-C8051F98x devices.

#### 15.1. Normal Mode

The MCU is fully functional in normal model agure 15.1 shows the on-chip power distribution to various peripherals. There are two supply voltages powering various sections of the chip: V<sub>DD</sub> and the 1.8 V internal core supply. A<sub>DD</sub> pin. A CIP-51 core are powered from the 1.8 V internal core supply. RA al ways powered directly from the V<sub>DD</sub> pin in sleep mode and powered from the core supply in all other

power modes

Figure 15.1. C8051F99x-C8051F98x Power Distribution

### 18.8. SmaRTClock (Real Time Clock) Reset

The SmaRTCI ock can generate a system reset on two events SmaRTCI ock Oscil I ator Fail or SmaRTCI ock A il event occurs when the SmaRTCI ock Missing CI ock Detector is enabled and the SmaRTCI ock cl ock is below approximately 20 Hzt A event occurs when the SmaRTCI ock A I ed and the SmaRTCI ock timer value matches the A

flag (RSTSRC.7). The SmaRTCI ockresset <u>rema</u>insfunctional even when the device is in the I ow power Suspend or SI eep mode Thestateof the RST pin is unaffected by this reset.

#### 18.9. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 foll owing a software forced reset. The state of the ST pin is unaffected by this reset.

#### 20.1.2. Using RTC0ADR and RTC0DAT to Access SmaRTClock Internal Registers

The SmaRTCI ock internal registers can be read and written using RTCOA RT COA ckinternal register tat will betargeted beubsequent readsor writes Recommended instruction timing is provided in this section. If the recommended instruction timing isnot fol I owed, then BUSY (RTCOA sure the SmaRTCI ock Interface is not busy performing the previous read or write operation. A wisan exampl eof writing to a CI ockWriteoperation is initiated by writing to the RTCODA SmaRTCI ockinternal register. 1. Pol I BUSY (RTC0A it et urns0 or fol I ow recommended instruction timing. 2. Write0x05 to RTC0A al RTCOCN register at SmaRTCI ockA 3. Writ e0x00 t o RTC0DA А the SmaR TCI ock Interface Busy bit. Thistransfers the contents of the internal registersel ected by RTCOA ansferred data will remain in RT CODA recister. 1. Pol I BUSY (RTC0A it et urns0 or fol I ow recommended instruction timing. 2. Write0x05 to RTC0A al RTCOCN register at SmaRTCI ockA 3. Write 1 to BUSY. This initiatest hetransfer of data from RTC0 CN to RTC0 DA 4. Pol I BUSY (RTC0A it returns0 or fol I ow meanend instruction timing.

5. Read dat a from RTC0DA is a copy of the RTC0CN register.

Note: TheRTCOA

#### 20.1.3. RTC0ADR Short Strobe Feature

Reads and writes to indirect SmaRT CI ockregisters normal I y take 7 system cl ock cycl es To minimize he indirect register access time the Short Strobefeat ure decreases the read and write access time to 6 system cl ocks. The Short Strobefeat ure is automatical I y enabled on reset and can be manual I y enabled/dis abled using the SHORT (RTCOA

Recommended Instruction Timing for a single register read with short strobeen abled:

mov RTC0ADR, #095h nop nop mov A, RTC0DAT

Recommended Instruction Timing for a single register write with short strobeen abled:

mov RTC0ADR, #095h

mov RTC0DAT, #000h

nop

#### 20.1.4. SmaRTClock Interface Autoread Feature

When A

```

SmaRTCI ock internal register selected by RTCOA -

ning of each series of consecutive real ds Software should follow recommended instruction timing or check

if the SmaRTCI ock Interface is busy prior to reading RTCODA

(RTCOA

```

#### 22.3.2. Arbitration

A ebusisf reeafter a STOP condition or after the SCL and SDA Section "22.3.5. SCL High (SMB us Free) Timeout" on page 238). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to for ceone master to give up the bus The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW Since the bus is open-drain, the bus will be pulled LOW The master attempting the HIGH will detect a LOW SDA set hear bit ration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive one device all ways wins, and no data islost.

#### 22.3.3. Clock Low Extension

SMB us provides a clock synchron ization mechanism, similar to l<sup>2</sup>C, which allows devices with different speed capabilities to coexist on the bus A ring a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 22.3.4. SCL Low Timeout

If the SCL I ineished I ow by a slave device on the bus, no further communication is possible Furthermore, the master cannot force the SCL I inehight o correct the error condition. To solve this problem, the SMB us protocol specifies that devices participating in a treatmermust detect any clock cycle held I ow I onger than 25 ms as a "timeout" condition. Devices that have det ected the timeout condition must reset the communi cation no I at er than 1106s after detecting the timeout condition.

When the SMBTOE bit in SMB0CF isset, Timer 3 is used to detect SCL I ow timeouts Timer 3 is for ced to relevant when SCL is low With Timer 3 enabled and configured to over fI ow after 2555 (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMB us in the event of an SCL I ow timeout.

#### 22.3.5. SCL High (SMBus Free) Timeout

The SMB us specification stipul at est hat if the SCL and SDA pithebus is designated as free When the SM BFTE bit in SMB 0 CF is set, the bus will be considered free if SCL and SDA SMB us clock source periods (as defined by the timer configured for the SMB us clock source). If the SMB us is waiting to generate a Master STA foll owing this timeout. Note that a clock source is required for free timeout detection, even in a slave only implementation.

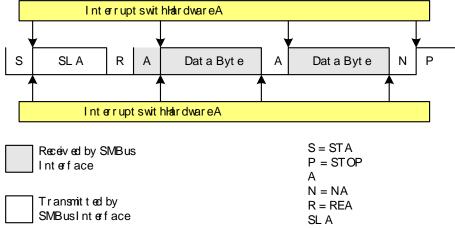

#### 22.5.2. Read Sequence (Master)

During a read sequence an SMB us ma sterreadsdata from a stavedevice. The master in this transfer will beatransmitter during the address by te and a receiver of during all data by tes The SMB usin terface generatest he STA containing the address of the target st ave and the data direction bit. In this case the data direction bit (R/W) will belogic (REA received from thest aveon SDA theserial clock. Thest avet ransmit someor more bytesof serial data. If hardware A received byte Softwaremust writetheA А led, the SMB ushardw are will autoantical ly generate the A WithhardwareA and then post theint errupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled. Writing a 1 to the A an A theA NA the STO bit is set and a STOP is generated. The inte rfacewil I switchto Master Transmitter Modeif SMB0 Figure 22.6 shows a typical master read sequence Two DA received dat a bytes are shown, though any number of bytes may be received. Not ice that the 'data byte transferred'interrupt soccur at different placesteresquence, depending on whether hardware A eration is enabled. The interrupt occurs before the A after theA

### Figure 22.6. Typical Master Read Sequence

|             | Valu             | es l  | Rea     | d   |                                              |                                                                                             |     | lues<br>Nrit |     | tus<br>ected                   |

|-------------|------------------|-------|---------|-----|----------------------------------------------|---------------------------------------------------------------------------------------------|-----|--------------|-----|--------------------------------|

| Mode        | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State Typical Response Options |                                                                                             | STA | STO          | ACK | Next Status<br>Vector Expected |

|             | 1110             | 0     | 0       | х   | A -<br>ated.                                 | Loadslaveaddress+R/Winto<br>SMB0DA                                                          | 0   | 0            | х   | 1100                           |

|             |                  | _     |         | _   | A                                            | Set STA                                                                                     | 1   | 0            | Х   | 1110                           |

| 'n          |                  | 0     | 0       | 0   | wastransmitted;NA<br>received.               | A                                                                                           | 0   | 1            | Х   | —                              |

| Transnitter |                  |       |         |     |                                              | L oad next dat a byt eint o SMB0<br>DA                                                      | 0   | 0            | х   | 1100                           |

| rar         |                  |       |         |     |                                              | EndtransferwithSTOP.                                                                        | 0   | 1            | Х   | —                              |

| Mast er T   | 1100             | 0     | 0       | 1   | A<br>wastransmitted; A<br>received.          | EndtransferwithSTOP andstart<br>anothertransfer.                                            | 1   | 1            | х   | _                              |

| Σ           |                  |       |         |     |                                              | Send repeated STA                                                                           | 1   | 0            | Х   | 1110                           |

|             |                  |       |         |     |                                              | Switcht o Master Receiver Mode<br>(clear Slwithoutwriting newdata<br>to SMB0DA<br>data byte | 0   | 0            | 1   | 1000                           |

|             |                  |       |         |     |                                              | Set A<br>Read SMB0DA                                                                        | 0   | 0            | 1   | 1000                           |

|             |                  | 0     | 0       | 1   | A<br>received;A sent.                        | Set NA<br>byteasthel ast databyte;<br>Read SMB0DA                                           | 0   | 0            | 0   | 1000                           |

|             |                  |       |         |     | Tec'eved, A Sent.                            | Initiaterepeated STA                                                                        | 1   | 0            | 0   | 1110                           |

| Receiver    | 1000             |       |         |     |                                              | SwitchtoMasterTransmitter<br>Mode(writetoSMB0DA<br>clearingSI).                             | 0   | 0            | x   | 1100                           |

| Mast e      |                  |       |         |     |                                              | Read SMB0DA                                                                                 | 0   | 1            | 0   | —                              |

| Ř           |                  |       |         |     | A                                            | Read SMB0DA<br>fol weed by STA                                                              | 1   | 1            | 0   | 1110                           |

|             |                  | 0     | 0       | 0   |                                              | Initiaterepeated STA                                                                        | 1   | 0            | 0   | 1110                           |

|             |                  |       |         |     | byt e).                                      | Swit cht o Master Transmitter<br>Mode(writet o SMB0DA<br>clearing SI).                      | 0   | 0            | x   | 1100                           |

# Table 22.6. SMBus Status Decoding With Hardware ACK Generation Enabled(EHACK = 1)

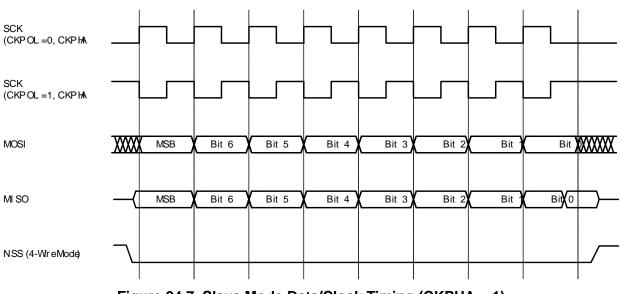

Figure 24.7. Slave Mode Data/Clock Timing (CKPHA = 1)

### 24.6. SPI Special Function Registers

SPI0 is accessed and control I ed through four special function registers in the system control I er: SPI0CN Control Register, SPI0DA gister, SPI0CFG Configuration Register, and SPI0CKR CI ock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the fol I owing figures

### SFR Definition 24.2. SPI0CN: SPI0 Control

| Bit   | 7    | 6    | 5    | 4       | 3          | 2 | 1     | 0     |  |

|-------|------|------|------|---------|------------|---|-------|-------|--|

| Name  | SPIF | WCOL | MODF | RXOV RN | NSSMD[1:0] |   | TXBMT | SPIEN |  |

| Туре  | R/W  | R/W  | R/W  | R/W     | R/W        |   | R     | R/W   |  |

| Reset | 0    | 0    | 0    | 0       | 0          | 1 | 1 1   |       |  |

SF R Page= 0x0; SF R A

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF       | SPIOInterrupt Flag.<br>Thisbit isset to logic 1 by hardware at the end of a data transfer. If SPI interrupts<br>are enabled, an interrupt will begenneated. Thisbit isnot automatical ly cleared b<br>hardware, and must be cleared by software                                                                                                                                     |

| 6   | WCOL       | Write Collision Flag.                                                                                                                                                                                                                                                                                                                                                               |

| 0   |            | Thisbit isset to logic 1 if a writet SPI0DA<br>thisoccurs, thewrite to SPI0DA gnored, and the transmit buffer will not be<br>written. If SPI interrupts are enabled, antimerrupt will begenerated. Thisbit is not<br>automatical ly cleared by hardware, and must be cleared by software                                                                                            |

| 5   | MODF       | Mode Fault Flag.                                                                                                                                                                                                                                                                                                                                                                    |

|     |            | Thisbit is set to logic 1 by hardware when a master mode co I lision is detected<br>(NSS is low, MSTEN = 1, and NSSMD[1:0] = 01). If SPI interrupt sareen abled, an<br>interrupt will begenered. Thisbit is not automatical ly cleared by hardware, and<br>must be cleared by soft ware                                                                                             |

| 4   | RXOV RN    | Receive Overrun Flag (valid in slave mode only).                                                                                                                                                                                                                                                                                                                                    |

|     |            | Thisbit isset to logic 1 by hardwarew hen the receive buffer still holdsun read data<br>from a previous transfer and the last biolf the current transferisshift ed into the<br>SPI0 shift register. If SPI intreupts are enabled, an interrupt will begen erated. This<br>bit is not automatical ly cleared by hardware, and must be cleared by software                            |

| 3:2 | NSSMD[1:0] | Slave Select Mode.                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | Sel ects between the following NSS operation modes<br>(See Section 24.2 and Section 24.3).<br>00: 3-WireSlaveor 3-WireMaster Mode NSS signal is not routed to a port pin.<br>01: 4-WireSlaveor Multi-Master Mode (Default). NSS is an input to the device<br>1x: 4-WireSingle Master Mode NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |

| 1   | TXBMT      | Transmit Buffer Empty.                                                                                                                                                                                                                                                                                                                                                              |

|     |            | Thisbit will beset to logic 0 when new data hasbeen written to the transmit buffer.<br>When data in the transmit buff er istransferred to the SPI shift register, thisbit will<br>beset to logic 1, indicating that it issafteo write a new byte to the transmit buffer.                                                                                                            |

| 0   | SP I EN    | SPI0 Enable.                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | 0: SPI disabled.<br>1: SPI enabled.                                                                                                                                                                                                                                                                                                                                                 |

## SFR Definition 25.11. TMR2L: Timer 2 Low Byte

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | TMR2L [7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFRPage= 0x0; SFRA

| Bit | Name        | Function                                                                                                                                                                     |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2L [7:0] | <b>Timer 2 Low Byte.</b><br>In 16-bit mode, the TMR2L register contains the Iow byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2L containst he 8-bit Iow byte timer value |

### SFR Definition 25.12. TMR2H Timer 2 High Byte

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | T MR2H27:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page= 0x0; SFR A

| Bit | Name                | Function                                                                                                                                          |

|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2H <b>#</b> 7:0] | Timer 2 Low Byte.                                                                                                                                 |

|     |                     | In 16-bit mode, the TMR2 Hregister containsthe high byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2 H containsthe 8-bit high byte timer value |