Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                    |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                          |

| Number of I/O              | 16                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 20-UFQFN Exposed Pad                                           |

| Supplier Device Package    | 20-QFN (3x3)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f981-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

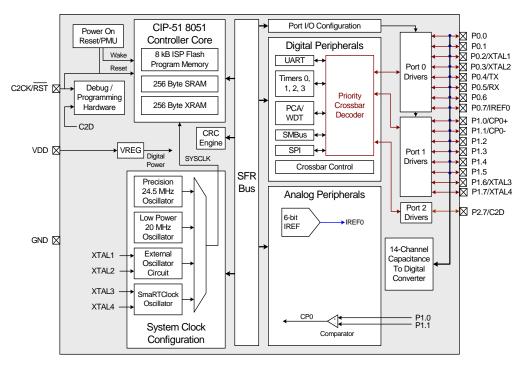

Figure 1.13. C8051F997 Block Diagram

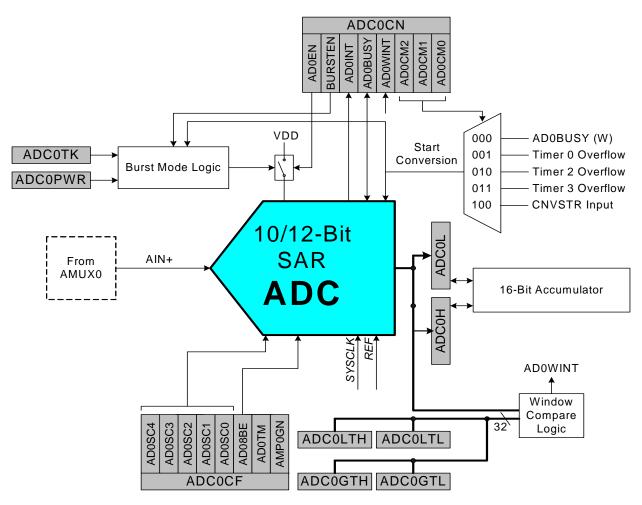

# 1.5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

C8051F99x-C8051F98x devices have a 300 ksps, 10-bit or 75 ksps 12-bit successive-approximationregister (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically average the ADC results, providing an effective 11, 12, or 13 bit ADC result without any additional CPU intervention.

The ADC can sample the voltage at select GPIO pins (see Figure 1.17) and has an on-chip attenuator that allows it to measure voltages up to twice the voltage reference. Additional ADC inputs include an on-chip temperature sensor, the VDD supply voltage, and the internal digital supply voltage.

\*Note: Signal only available on 'F986, 'F988, and 'F996 devices.

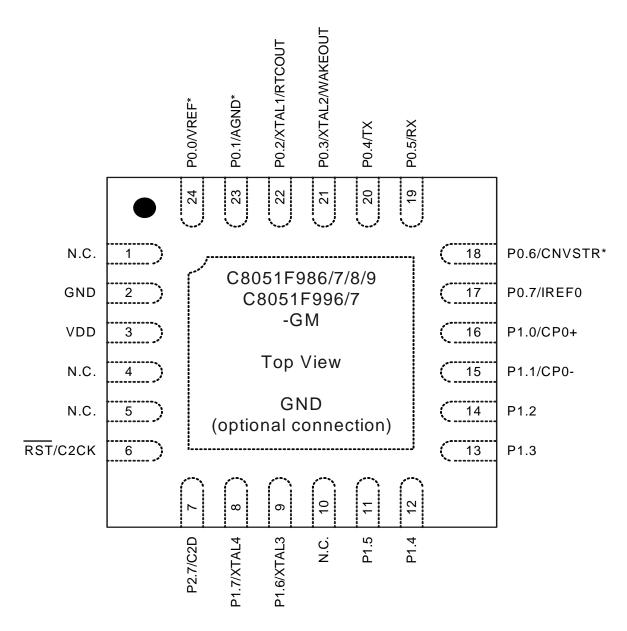

Figure 3.2. QFN-24 Pinout Diagram (Top View)

## Table 4.13. IREF0 Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C, unless otherwise specified.

| Static PerformanceResolution6bitsOutput Compliance RangeLow Power Mode, Source<br>High Current Mode, Source<br>Low Power Mode, Sink0 $V_{DD} - 0.4$<br>$V_{DD} - 0.8$<br>$V_{DD} - 0.8$ Integral Nonlinearity<±0.2±1.0LSBDifferential Nonlinearity<±0.2±1.0LSBOffset Error±5%High Current Mode, Source±6%Integral Nonlinearity<±0.1±0.5LSBDifferential Nonlinearity<±0.1±0.5LSBFull Scale ErrorLow Power Mode, Source±6High Current Mode, Source±8%How Power Mode, Sink±8%Absolute Current ErrorLow Power Mode, Sink±8Output Settling Time to 1/2 LSB300nsStartup Time1 $\mu A$ Net Power Supply Current<br>(Vop Supplied to IREFO minus<br>any output source current)IREFODAT = 00000110IREFODAT = 100100110 $\mu A$ IREFODAT = 111111 $\mu A$ IREFODAT = 00000111 $\mu A$ IREFODAT = 00000110IREFODAT = 00000110 $\mu A$ IREFODAT = 00000110 $\mu A$ IREFODAT = 00000111 $\mu A$ <th>Parameter</th> <th>Conditions</th> <th>Min</th> <th>Тур</th> <th>Max</th> <th>Units</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Parameter                                | Conditions                                        | Min      | Тур   | Max                                      | Units |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------|----------|-------|------------------------------------------|-------|

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Static Performance                       |                                                   |          |       |                                          |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Resolution                               | 6                                                 |          |       | bits                                     |       |

| $\begin{array}{ c c c c c } \hline Differential Nonlinearity & < < \pm 0.2 & \pm 1.0 & LSB \\ \hline Offset Error & - & < \pm 0.1 & \pm 0.5 & LSB \\ \hline Low Power Mode, Source & & & \pm 5 & \% \\ \hline High Current Mode, Source & & & \pm 6 & \% \\ \hline Low Power Mode, Sink & & & \pm 8 & \% \\ \hline Low Power Mode, Sink & & & \pm 8 & \% \\ \hline Low Power Mode, Sink & & & \pm 8 & \% \\ \hline High Current Mode, Sink & & & \pm 8 & \% \\ \hline Absolute Current Error & Low Power Mode & & < \pm 1 & \pm 3 & \% \\ \hline Dynamic Performance & & & & & & & \\ \hline Output Settling Time to 1/2 LSB & & 300 & & ns \\ \hline Startup Time & & 1 & & \mus \\ \hline Power Consumption & & & & & \\ Net Power Supply Current & & & & & \\ (Vop Supplied to IREF0 minus any output source current) & Low Power Mode, Source & & & & \\ IREF0DAT = 000001 & & 10 & & \muA \\ IREF0DAT = 000001 & & 10 & & \muA \\ IREF0DAT = 111111 & & 10 & & \muA \\ IREF0DAT = 111111 & & 10 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 1000001 & & 1 & & \muA \\ IREF0DAT = 000001 & & 1 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 12 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & & & & $                                                                                                                                                                                                                                                                                                                                                                                                                                    | Output Compliance Range                  | High Current Mode, Source<br>Low Power Mode, Sink | 0<br>0.3 |       | V <sub>DD</sub> – 0.8<br>V <sub>DD</sub> | V     |

| $\begin{array}{ c c c c c } \hline \label{eq:constraint} Offset Error & & - & - & \pm 0.1 & \pm 0.5 & LSB \\ \hline \mbox{Low Power Mode, Source} & & - & \pm 5 & \% \\ \hline \mbox{High Current Mode, Source} & & - & \pm 6 & \% \\ \hline \mbox{Low Power Mode, Sink} & & - & \pm 8 & \% \\ \hline \mbox{High Current Mode, Sink} & & - & \pm 8 & \% \\ \hline \mbox{High Current Mode, Sink} & & - & \pm 8 & \% \\ \hline \mbox{Absolute Current Error} & Low Power Mode & & <\pm 1 & \pm 3 & \% \\ \hline \mbox{Dynamic Performance} & & 1 & & \pm 8 & \% \\ \hline \mbox{Dynamic Performance} & & - & \pm 8 & \% \\ \hline \mbox{Dynamic Performance} & & - & \pm 8 & \% \\ \hline \mbox{Dynamic Performance} & & & \pm 8 & \% \\ \hline \mbox{Output Settling Time to 1/2 LSB} & & 300 & & ns \\ \hline \mbox{Startup Time} & & 1 & & \mu s \\ \hline \mbox{Power Consumption} \\ \hline \mbox{Net Power Supply Current} & Low Power Mode, Source \\ \mbox{IREF0DAT = 000001} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 11 & & \mu A \\ \hline \mbox{IREF0DAT = 1000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 12 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline IREF0DAT =$                                                                     | Integral Nonlinearity                    |                                                   | _        | <±0.2 | ±1.0                                     | LSB   |

| $\begin{tabular}{ c c c c c c c } \hline Low Power Mode, Source & - & - & \pm 5 & \% \\ \hline High Current Mode, Source & - & - & \pm 6 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline Absolute Current Error & Low Power Mode & - & <\pm 1 & \pm 3 & \% \\ \hline Dynamic Performance & & & & & & & \\ \hline Output Settling Time to 1/2 LSB & - & 300 & - & ns \\ \hline Startup Time & - & 1 & - & \mus \\ \hline Power Consumption & & & & & & & \\ Net Power Supply Current (V_{DD} supplied to IREF0 minus any output source current) & Low Power Mode, Source IREF0DAT = 000001 & - & 10 & - & \muA \\ IREF0DAT = 111111 & - & 10 & - & \muA \\ IREF0DAT = 111111 & - & 10 & - & \muA \\ IREF0DAT = 111111 & - & 10 & - & \muA \\ IREF0DAT = 1000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 111111 & - & 11 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 111111 & - & 11 & - & \muA \\ IREF0DAT = 000001 & - & 12 & - & \muA \\ IREF0DAT = 000001 & - & 12 & - & \muA \\ IREF0DAT = 000001 & - & 12 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & & \muA \\ IREF0DAT = 111111 & - & 81 & - &$ | Differential Nonlinearity                |                                                   | —        | <±0.2 | ±1.0                                     | LSB   |

| Full Scale Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Offset Error                             |                                                   | _        | <±0.1 | ±0.5                                     | LSB   |

| Full Scale ErrorImage: Sink intermediate inter                                                                                                                                                                                                                                                          |                                          | Low Power Mode, Source                            |          | —     | ±5                                       | %     |

| $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Full Scole Error                         | High Current Mode, Source                         |          | —     | ±6                                       | %     |

| Absolute Current ErrorLow Power Mode<br>Sourcing 20 $\mu$ A-<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          | Low Power Mode, Sink                              | —        | —     | ±8                                       | %     |

| Absolute Current ErrorSourcing 20 $\mu$ AImage: Constraint of the second se                                                                                                                                                                                                                                        |                                          | High Current Mode, Sink                           |          | —     | ±8                                       | %     |

| Output Settling Time to 1/2 LSB         —         300         —         ns           Startup Time         —         1         —         µs           Power Consumption         —         1         —         µs           Net Power Supply Current<br>(V <sub>DD</sub> supplied to IREF0 minus<br>any output source current)         Low Power Mode, Source<br>IREF0DAT = 000001         —         10         —         µA           High Current Mode, Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Absolute Current Error                   |                                                   | _        | <±1   | ±3                                       | %     |

| Startup Time         —         1         —         μs           Power Consumption         Net Power Supply Current (V <sub>DD</sub> supplied to IREF0 minus any output source current)         Low Power Mode, Source         10         —         μA           IREF0DAT = 000001         —         10         —         μA           IREF0DAT = 111111         —         10         —         μA           IREF0DAT = 000001         —         10         —         μA           IREF0DAT = 000001         —         10         —         μA           IREF0DAT = 111111         —         10         —         μA           IREF0DAT = 000001         —         1         —         μA           IREF0DAT = 111111         —         11         —         μA           IREF0DAT = 000001         —         12         —         μA           IREF0DAT = 111111         —         81         —         μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Dynamic Performance                      |                                                   |          |       |                                          |       |

| Power ConsumptionNet Power Supply Current<br>(V <sub>DD</sub> supplied to IREF0 minus<br>any output source current)Low Power Mode, Source<br>IREF0DAT = 00000110µAIREF0DAT = 11111110µAHigh Current Mode, Source<br>IREF0DAT = 00000110µAIREF0DAT = 00000110µAIREF0DAT = 00000110µAIREF0DAT = 00000110µAIREF0DAT = 11111110µAIREF0DAT = 0000011µAIREF0DAT = 11111111µAIREF0DAT = 00000112µAIREF0DAT = 00000112µAIREF0DAT = 11111181µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output Settling Time to 1/2 LSB          |                                                   | —        | 300   | —                                        | ns    |

| Net Power Supply Current<br>(V <sub>DD</sub> supplied to IREF0 minus<br>any output source current)Low Power Mode, Source<br>IREF0DAT = 00000110 $ \mu A$ IREF0DAT = 111111-10- $\mu A$ High Current Mode, Source<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Startup Time                             |                                                   | —        | 1     | —                                        | μs    |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Power Consumption                        |                                                   |          |       |                                          |       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (V <sub>DD</sub> supplied to IREF0 minus | IREF0DAT = 000001<br>IREF0DAT = 111111            | —        |       |                                          | •     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                          | IREF0DAT = 000001<br>IREF0DAT = 111111            | —        |       | _                                        |       |

| IREF0DAT = 111111 — 81 — µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          | IREF0DAT = 111111<br>High Current Mode, Sink      | _        | 11    | _                                        | μA    |

| Note: Refer to "PWM Enhanced Mode" on page 91 for information on how to improve IREF0 resolution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Note: Refer to "PW/M Enhanced My         | IREF0DAT = 111111                                 |          | 81    | resolution                               |       |

#### 5.2. Modes of Operation

ADC0 has a maximum conversion speed of 300 ksps in 10-bit mode. The ADC0 conversion clock (SARCLK) is a divided version of the system clock when burst mode is disabled (BURSTEN = 0), or a divided version of the low power oscillator when burst mode is enabled (BURSEN = 1). The clock divide value is determined by the AD0SC bits in the ADC0CF register.

#### 5.2.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2–0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a 1 to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 3 overflow

- 5. A rising edge on the CNVSTR input signal (pin P0.6)

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. When Timer 2 or Timer 3 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2/3 is in 16-bit mode. See "25. Timers" on page 278 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.6. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.6 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.6, set to 1 Bit 6 in register P0SKIP. See "21. Port Input/Output" on page 215 for details on Port I/O configuration.

#### 5.2.4. Settling Time Requirements

A minimum amount of tracking time is required before each conversion can be performed, to allow the sampling capacitor voltage to settle. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For many applications, these three SAR clocks will meet the minimum tracking time requirements, and higher values for the external source impedance will increase the required tracking time.

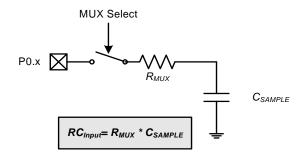

Figure 5.4 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 5.1. When measuring the Temperature Sensor output or  $V_{DD}$  with respect to GND,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 4.10 for ADC0 minimum settling time requirements as well as the mux impedance and sampling capacitor values.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL}C_{SAMPLE}$$

#### **Equation 5.1. ADC0 Settling Time Requirements**

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

*n* is the ADC resolution in bits (10).

Note: The value of CSAMPLE depends on the PGA Gain. See Table 4.10 for details.

### Figure 5.4. ADC0 Equivalent Input Circuits

# C8051F99x-C8051F98x

# SFR Definition 5.1. ADC0CN: ADC0 Control

| Bit   | 7     | 6       | 5      | 4       | 3       | 2           | 1 | 0 |

|-------|-------|---------|--------|---------|---------|-------------|---|---|

| Name  | AD0EN | BURSTEN | AD0INT | AD0BUSY | AD0WINT | ADC0CM[2:0] |   |   |

| Туре  | R/W   | R/W     | R/W    | W       | R/W     | R/W         |   |   |

| Reset | 0     | 0       | 0      | 0       | 0       | 0           | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xE8; bit-addressable;

| Bit | Name        | Function                                                                                                                                                                                 |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AD0EN       | ADC0 Enable.                                                                                                                                                                             |

|     |             | 0: ADC0 Disabled (low-power shutdown).<br>1: ADC0 Enabled (active and ready for data conversions).                                                                                       |

| 6   | BURSTEN     | ADC0 Burst Mode Enable.<br>0: ADC0 Burst Mode Disabled.                                                                                                                                  |

|     |             | 1: ADC0 Burst Mode Enabled.                                                                                                                                                              |

| 5   | AD0INT      | ADC0 Conversion Complete Interrupt Flag.                                                                                                                                                 |

|     |             | Set by hardware upon completion of a data conversion (BURSTEN=0), or a burst of conversions (BURSTEN=1). Can trigger an interrupt. Must be cleared by software.                          |

| 4   | AD0BUSY     | ADC0 Busy.                                                                                                                                                                               |

|     |             | Writing 1 to this bit initiates an ADC conversion when ADC0CM[2:0] = 000.                                                                                                                |

| 3   | AD0WINT     | ADC0 Window Compare Interrupt Flag.                                                                                                                                                      |

|     |             | Set by hardware when the contents of ADC0H:ADC0L fall within the window speci-<br>fied by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL. Can trigger an interrupt.<br>Must be cleared by software. |

| 2:0 | ADC0CM[2:0] | ADC0 Start of Conversion Mode Select.                                                                                                                                                    |

|     |             | Specifies the ADC0 start of conversion source.                                                                                                                                           |

|     |             | 000: ADC0 conversion initiated on write of 1 to AD0BUSY.<br>001: ADC0 conversion initiated on overflow of Timer 0.                                                                       |

|     |             | 010: ADC0 conversion initiated on overflow of Timer 0.                                                                                                                                   |

|     |             | 011: ADC0 conversion initiated on overflow of Timer 3.                                                                                                                                   |

|     |             | 1xx: ADC0 conversion initiated on rising edge of CNVSTR.                                                                                                                                 |

# SFR Definition 5.2. ADC0CF: ADC0 Configuration

| Bit   | 7               | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                         | 4            | 3           | 2       | 1     | 0       |  |

|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|---------|-------|---------|--|

| Nam   | e               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AD0SC[4:0]                                                                                                                                                                                                                                                                                                                                                                                                |              |             | AD08BE  | AD0TM | AMP0GN  |  |

| Туре  | •               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                                                                                                                                                                                                                                                                                                                                                                                                       |              |             | R/W     | R/W   | R/W     |  |

| Rese  | t 1             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                         | 1            | 1           | 0       | 0     | 0       |  |

| SFR F | age = 0x0; SI   | R Address =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | = 0x97                                                                                                                                                                                                                                                                                                                                                                                                    |              |             | •       |       |         |  |

| Bit   | Name            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                           |              | Functior    | 1       |       |         |  |

| 7:3   | AD0SC[4:0]      | ADC0 SAR Conversion Clock Divider.<br>SAR Conversion clock is derived from FCLK by the following equation, where<br>ADOSC refers to the 5-bit value held in bits ADOSC[4:0]. SAR Conversion clock<br>requirements are given in Table 4.10.<br>BURSTEN = 0: FCLK is the current system clock.<br>BURSTEN = 1: FCLK is the 20 MHz low power oscillator, independent of the system<br>clock.<br>$ADOSC = \frac{FCLK}{CLK_{SAR}} - 1 *$<br>*Round the result up.<br>or<br>$CLK_{SAR} = \frac{FCLK}{ADOSC + 1}$ |                                                                                                                                                                                                                                                                                                                                                                                                           |              |             |         |       | n clock |  |

| 2     | AD08BE          | 0: ADC0 op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | t <b>Mode Ena</b> l<br>erates in 10<br>erates in 8-l                                                                                                                                                                                                                                                                                                                                                      | -bit mode (n | ormal opera | ation). |       |         |  |

| 1     | AD0TM<br>AMP0GN | Selects betw<br>0: Normal T<br>lowing the s<br>1: Delayed<br>cycles follow<br>this time.                                                                                                                                                                                                                                                                                                                                                                                                                   | ADC0 Track Mode.<br>Selects between Normal or Delayed Tracking Modes.<br>0: Normal Track Mode: When ADC0 is enabled, conversion begins immediately fol<br>lowing the start-of-conversion signal.<br>1: Delayed Track Mode: When ADC0 is enabled, conversion begins 3 SAR clock<br>cycles following the start-of-conversion signal. The ADC is allowed to track during<br>this time.<br>ADC0 Gain Control. |              |             |         |       |         |  |

|       |                 | 0: The on-c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | hip PGA gai<br>hip PGA gai                                                                                                                                                                                                                                                                                                                                                                                |              |             |         |       |         |  |

## 8.11. CS0 Conversion Accumulator

CS0 can be configured to accumulate multiple conversions on an input channel. The number of samples to be accumulated is configured using the CS0ACU2:0 bits (CS0CF2:0). The accumulator can accumulate 1, 4, 8, 16, 32, or 64 samples. After the defined number of samples have been accumulated, the result is divided by either 1, 4, 8, 16, 32, or 64 (depending on the CS0ACU[2:0] setting) and copied to the CS0DH:CS0DL SFRs.

| Auto-Scan Enabled | Accumulator Enabled | CS0 Conversion<br>Complete<br>Interrupt<br>Behavior                      | CS0 Greater Than Interrupt<br>Behavior                                                                                                                                          | CS0MX Behavior                                                                                                                                                                                                                     |

|-------------------|---------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N                 | Ν                   | CS0INT Interrupt<br>serviced after 1<br>conversion com-<br>pletes        | Interrupt serviced after 1 con-<br>version completes if value in<br>CS0DH:CS0DL is greater than<br>CS0THH:CS0THL                                                                | CS0MX unchanged.                                                                                                                                                                                                                   |

| N                 | Y                   | CS0INT Interrupt<br>serviced after <i>M</i><br>conversions com-<br>plete | Interrupt serviced after <i>M</i> conversions complete if value in CS0DH:CS0DL (post accumulate and divide) is greater than CS0THH:CS0THL                                       | CS0MX unchanged.                                                                                                                                                                                                                   |

| Y                 | Ν                   | CS0INT Interrupt<br>serviced after 1<br>conversion com-<br>pletes        | Interrupt serviced after con-<br>version completes if value in<br>CS0DH:CS0DL is greater than<br>CS0THH:CS0THL;<br>Auto-Scan stopped                                            | If greater-than comparator detects conver-<br>sion value is greater than<br>CS0THH:CS0THL, CS0MX is left<br>unchanged; otherwise, CS0MX updates to<br>the next channel (CS0MX + 1) and wraps<br>back to CS0SS after passing CS0SE. |

| Y                 | Y                   | CS0INT Interrupt<br>serviced after <i>M</i><br>conversions com-<br>plete | Interrupt serviced after <i>M</i> con-<br>versions complete if value in<br>CS0DH:CS0DL (post accumu-<br>late and divide) is greater than<br>CS0THH:CS0THL; Auto-Scan<br>stopped | If greater-than comparator detects conver-<br>sion value is greater than<br>CS0THH:CS0THL, CS0MX is left<br>unchanged; otherwise, CS0MX updates to<br>the next channel (CS0MX + 1) and wraps<br>back to CS0SS after passing CS0SE. |

Table 8.1. Operation with Auto-scan and Accumulate

# C8051F99x-C8051F98x

# SFR Definition 13.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Page = All; SFR Address = 0xA8; Bit-Addressable

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

# SFR Definition 14.2. REVID: Revision Identification

| Bit   | 7          | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|----|---|---|---|---|--|--|

| Name  | REVID[7:0] |   |   |    |   |   |   |   |  |  |

| Туре  |            |   |   | R/ | W |   |   |   |  |  |

| Reset | 0          | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

#### SFR Page = 0xF; SFR Address = 0xE2

| Bit | Name       | Function                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | REVID[7:0] | Revision Identification.                                                                                                                            |

|     |            | These bits contain a value that can be decoded to determine the silicon revision. For example, 0x00 for Rev A, 0x01 for Rev B, 0x02 for Rev C, etc. |

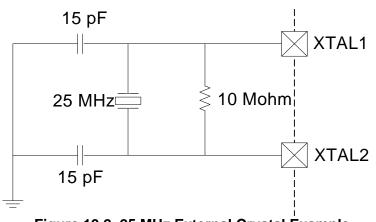

Figure 19.2. 25 MHz External Crystal Example

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

When using an external crystal, the external oscillator drive circuit must be configured by software for *Crystal Oscillator Mode* or *Crystal Oscillator Mode with divide by 2 stage*. The divide by 2 stage ensures that the clock derived from the external oscillator has a duty cycle of 50%. The External Oscillator Frequency Control value (XFCN) must also be specified based on the crystal frequency. The selection should be based on Table 19.1. For example, a 25 MHz crystal requires an XFCN setting of 111b.

| XFCN | Crystal Frequency                         | Bias Current | Typical Supply Current<br>(VDD = 2.4 V) |

|------|-------------------------------------------|--------------|-----------------------------------------|

| 000  | f ≤ 20 kHz                                | 0.5 µA       | 3.0 μA, f = 32.768 kHz                  |

| 001  | 20 kHz < f ≤ 58 kHz                       | 1.5 µA       | 4.8 μA, f = 32.768 kHz                  |

| 010  | 58 kHz < f ≤ 155 kHz                      | 4.8 µA       | 9.6 μA, f = 32.768 kHz                  |

| 011  | 155 kHz < f ≤ 415 kHz                     | 14 µA        | 28 µA, f = 400 kHz                      |

| 100  | 415 kHz $<$ f $\leq$ 1.1 MHz              | 40 µA        | 71 µA, f = 400 kHz                      |

| 101  | $1.1 \text{ MHz} < f \le 3.1 \text{ MHz}$ | 120 µA       | 193 µA, f = 400 kHz                     |

| 110  | $3.1 \text{ MHz} < f \le 8.2 \text{ MHz}$ | 550 µA       | 940 µA, f = 8 MHz                       |