Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                     |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 16                                                              |

| Program Memory Size        | 4KB (4K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                |                                                                 |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 10x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 20-UFQFN Exposed Pad                                            |

| Supplier Device Package    | 20-QFN (3x3)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f982-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | 19.2.Low Power Internal Oscillator                                              | 189 |

|-------------|---------------------------------------------------------------------------------|-----|

|             | 19.3.External Oscillator Drive Circuit                                          | 189 |

|             | 19.3.1.External Crystal Mode                                                    | 189 |

|             | 19.3.2.External RC Mode                                                         |     |

|             | 19.3.3.External Capacitor Mode                                                  |     |

|             |                                                                                 |     |

|             | 19.3.4.External CMOS Clock Mode                                                 |     |

|             | 19.4. Special Function Registers for Selecting and Configuring the System Clock |     |

| 20.         | SmaRTClock (Real Time Clock)                                                    |     |

|             | 20.1.SmaRTClock Interface                                                       | 198 |

|             | 20.1.1.SmaRTClock Lock and Key Functions                                        | 198 |

|             | 20.1.2. Using RTC0ADR and RTC0DAT to Access SmaRTClock Internal Regis           |     |

|             |                                                                                 |     |

|             | 20.1.3.RTC0ADR Short Strobe Feature                                             |     |

|             | 20.1.4.SmaRTClock Interface Autoread Feature                                    |     |

|             |                                                                                 |     |

|             | 20.1.5.RTC0ADR Autoincrement Feature                                            |     |

|             | 20.2.SmaRTClock Clocking Sources                                                |     |

|             | 20.2.1. Using the SmaRTClock Oscillator with a Crystal or External CMOS Clo     | ock |

|             |                                                                                 | 203 |

|             | 20.2.2.Using the SmaRTClock Oscillator in Self-Oscillate Mode                   | 204 |

|             | 20.2.3.Using the Low Frequency Oscillator (LFO)                                 |     |

|             | 20.2.4.Programmable Load Capacitance                                            |     |

|             | 20.2.5. Automatic Gain Control (Crystal Mode Only) and SmaRTClock Bias Do       |     |

|             |                                                                                 |     |

|             | bling                                                                           |     |

|             | 20.2.6.Missing SmaRTClock Detector                                              |     |

|             | 20.2.7.SmaRTClock Oscillator Crystal Valid Detector                             |     |

|             | 20.3.SmaRTClock Timer and Alarm Function                                        |     |

|             | 20.3.1.Setting and Reading the SmaRTClock Timer Value                           | 208 |

|             | 20.3.2.Setting a SmaRTClock Alarm                                               | 209 |

|             | 20.3.3.Software Considerations for using the SmaRTClock Timer and Alarm .       |     |

| 21.         | Port Input/Output                                                               |     |

|             | 21.1.Port I/O Modes of Operation                                                |     |

|             | 21.1.1.Port Pins Configured for Analog I/O                                      |     |

|             |                                                                                 |     |

|             | 21.1.2.Port Pins Configured For Digital I/O                                     |     |

|             | 21.1.3.Interfacing Port I/O to 5 V Logic                                        |     |

|             | 21.1.4.Increasing Port I/O Drive Strength                                       |     |

|             | 21.2.Assigning Port I/O Pins to Analog and Digital Functions                    |     |

|             | 21.2.1.Assigning Port I/O Pins to Analog Functions                              | 217 |

|             | 21.2.2.Assigning Port I/O Pins to Digital Functions                             | 218 |

|             | 21.2.3.Assigning Port I/O Pins to External Digital Event Capture Functions      |     |

|             | 21.3.Priority Crossbar Decoder                                                  |     |

|             | 21.4.Port Match                                                                 |     |

|             | 21.5.Special Function Registers for Accessing and Configuring Port I/O          |     |

| 22          |                                                                                 |     |

| <b>ZZ</b> . | SMBus                                                                           |     |

|             | 22.1.Supporting Documents                                                       |     |

|             | 22.2.SMBus Configuration                                                        | 236 |

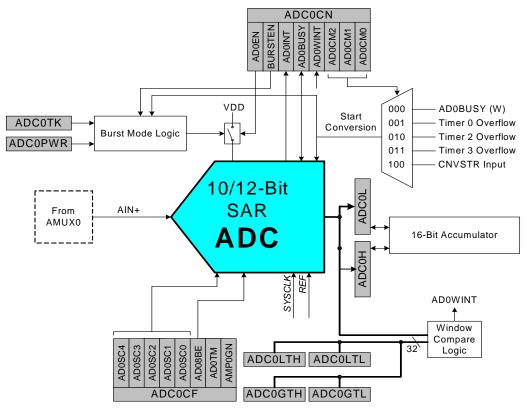

# 5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

The ADC0 on C8051F980/6 and C8051F990/6 devices is a 300 ksps, 10-bit or 75 ksps, 12-bit successiveapproximation-register (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically oversample and average the ADC results. See Section 5.4 for more details on using the ADC in 12-bit mode. C8051F982 and C8051F988 devices only support the 10-bit mode.

The ADC is fully configurable under software control via Special Function Registers. The ADC0 operates in Single-ended mode and may be configured to measure various different signals using the analog multiplexer described in "5.7. ADC0 Analog Multiplexer" on page 83. The voltage reference for the ADC is selected as described in "5.9. Voltage and Ground Reference Options" on page 88.

Figure 5.1. ADC0 Functional Block Diagram

#### 5.2. Modes of Operation

ADC0 has a maximum conversion speed of 300 ksps in 10-bit mode. The ADC0 conversion clock (SARCLK) is a divided version of the system clock when burst mode is disabled (BURSTEN = 0), or a divided version of the low power oscillator when burst mode is enabled (BURSEN = 1). The clock divide value is determined by the AD0SC bits in the ADC0CF register.

#### 5.2.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2–0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a 1 to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 3 overflow

- 5. A rising edge on the CNVSTR input signal (pin P0.6)

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. When Timer 2 or Timer 3 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2/3 is in 16-bit mode. See "25. Timers" on page 278 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.6. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.6 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.6, set to 1 Bit 6 in register P0SKIP. See "21. Port Input/Output" on page 215 for details on Port I/O configuration.

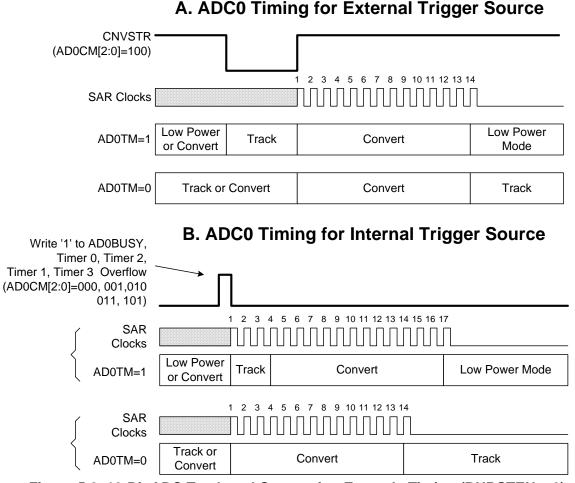

#### 5.2.2. Tracking Modes

Each ADC0 conversion must be preceded by a minimum tracking time in order for the converted result to be accurate. The minimum tracking time is given in Table 4.10. The AD0TM bit in register ADC0CN controls the ADC0 track-and-hold mode. In its default state when Burst Mode is disabled, the ADC0 input is continuously tracked, except when a conversion is in progress. When the AD0TM bit is logic 1, ADC0 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a tracking period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR signal is used to initiate conversions in low-power tracking mode, ADC0 tracks only when CNVSTR is low; conversion begins on the rising edge of CNVSTR (see Figure 5.2). Tracking can also be disabled (shutdown) when the device is in low power standby or sleep modes. Low-power track-and-hold mode is also useful when AMUX settings are frequently changed, due to the settling time requirements described in "5.2.4. Settling Time Requirements" on page 71.

Figure 5.2. 10-Bit ADC Track and Conversion Example Timing (BURSTEN = 0)

#### 5.2.5. Gain Setting

The ADC has gain settings of 1x and 0.5x. In 1x mode, the full scale reading of the ADC is determined directly by V<sub>REF</sub>. In 0.5x mode, the full-scale reading of the ADC occurs when the input voltage is V<sub>REF</sub> x 2. The 0.5x gain setting can be useful to obtain a higher input Voltage range when using a small V<sub>REF</sub> voltage, or to measure input voltages that are between V<sub>REF</sub> and V<sub>DD</sub>. Gain settings for the ADC are controlled by the AMP0GN bit in register ADC0CF.

#### 5.3. 8-Bit Mode

Setting the ADC08BE bit in register ADC0CF to 1 will put the ADC in 8-bit mode. In 8-bit mode, only the 8 MSBs of data are converted, allowing the conversion to be completed in two fewer SAR clock cycles than a 10-bit conversion. This can result in an overall lower power consumption since the system can spend more time in a low power mode. The two LSBs of a conversion are always 00 in this mode, and the ADC0L register will always read back 0x00.

#### 5.4. 12-Bit Mode (C8051F980/6 and C8051F990/6 devices only)

C8051F980/6 and C8051F990/6 devices have an enhanced SAR converter that provides 12-bit resolution while retaining the 10- and 8-bit operating modes of the other devices in the family. When configured for 12-bit conversions, the ADC performs four 10-bit conversions using four different reference voltages and combines the results into a single 12-bit value. Unlike simple averaging techniques, this method provides true 12-bit resolution of AC or DC input signals without depending on noise to provide dithering. The converter also employs a hardware Dynamic Element Matching algorithm that reconfigures the largest elements of the internal DAC for each of the four 10-bit conversions to cancel any matching errors, enabling the converter to achieve 12-bit linearity performance to go along with its 12-bit resolution. For best performance, the Low Power Oscillator should be selected as the system clock source while taking 12-bit ADC measurements.

The 12-bit mode is enabled by setting the AD012BE bit (ADC0AC.7) to logic 1 and configuring Burst Mode for four conversions as described in Section 5.2.3. The conversion can be initiated using any of the methods described in Section 5.2.1, and the 12-bit result will appear in the ADC0H and ADC0L registers. Since the 12-bit result is formed from a combination of four 10-bit results, the maximum output value is  $4 \times (1023) = 4092$ , rather than the max value of  $(2^{12} - 1) = 4095$  that is produced by a traditional 12-bit converter. To further increase resolution, the burst mode repeat value may be configured to any multiple of four conversions. For example, if a repeat value of 16 is selected, the ADC0 output will be a 14-bit number (sum of four 12-bit numbers) with 13 effective bits of resolution.

#### 5.5. Low Power Mode

The SAR converter provides a low power mode that allows a significant reduction in operating current when operating at low SAR clock frequencies. Low power mode is enabled by setting the AD0LPM bit (ADC0PWR.7) to 1. In general, low power mode is recommended when operating with SAR conversion clock frequency at 4 MHz or less. See the Electrical Characteristics chapter for details on power consumption and the maximum clock frequencies allowed in each mode. Setting the Low Power Mode bit reduces the bias currents in both the SAR converter and in the High-Speed Voltage Reference.

# SFR Definition 5.3. ADC0AC: ADC0 Accumulator Configuration

| Bit   | 7       | 6     | 5                        | 4 | 3 | 2 | 1   | 0 |

|-------|---------|-------|--------------------------|---|---|---|-----|---|

| Name  | AD012BE | AD0AE | AD0SJST[2:0] AD0RPT[2:0] |   |   |   | ]   |   |

| Туре  | R/W     | W     | R/W                      |   |   |   | R/W |   |

| Reset | 0       | 0     | 0                        | 0 | 0 | 0 | 0   | 0 |

#### SFR Page = 0x0; SFR Address = 0xBA

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AD012BE      | ADC0 12-Bit Mode Enable.<br>Enables 12-bit Mode on C8051F980/6 and C8051F990/6 devices.<br>0: 12-bit Mode Disabled.<br>1: 12-bit Mode Enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6   | AD0AE        | <ul> <li>ADC0 Accumulate Enable.</li> <li>Enables multiple conversions to be accumulated when burst mode is disabled.</li> <li>0: ADC0H:ADC0L contain the result of the latest conversion when Burst Mode is disabled.</li> <li>1: ADC0H:ADC0L contain the accumulated conversion results when Burst Mode is disabled. Software must write 0x0000 to ADC0H:ADC0L to clear the accumulated result.</li> <li>This bit is write-only. Always reads 0b.</li> </ul>                                                                                                                   |

| 5:3 | AD0SJST[2:0] | ADC0 Accumulator Shift and Justify.<br>Specifies the format of data read from ADC0H:ADC0L.<br>000: Right justified. No shifting applied.<br>001: Right justified. Shifted right by 1 bit.<br>010: Right justified. Shifted right by 2 bits.<br>011: Right justified. Shifted right by 3 bits.<br>100: Left justified. No shifting applied.<br>All remaining bit combinations are reserved.                                                                                                                                                                                       |

| 2:0 | AD0RPT[2:0]  | <ul> <li>ADC0 Repeat Count.</li> <li>Selects the number of conversions to perform and accumulate in Burst Mode.</li> <li>This bit field must be set to 000 if Burst Mode is disabled.</li> <li>000: Perform and Accumulate 1 conversion.</li> <li>001: Perform and Accumulate 4 conversions.</li> <li>010: Perform and Accumulate 8 conversions.</li> <li>011: Perform and Accumulate 16 conversions.</li> <li>100: Perform and Accumulate 32 conversions.</li> <li>101: Perform and Accumulate 64 conversions.</li> <li>All remaining bit combinations are reserved.</li> </ul> |

### 5.6. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to userprogrammed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

### SFR Definition 5.8. ADC0GTH: ADC0 Greater-Than High Byte

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | AD0GT[15:8] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Page = 0x0; SFR Address = 0xC4

| Bit | Name        | Function                                                                  |

|-----|-------------|---------------------------------------------------------------------------|

| 7:0 | AD0GT[15:8] | ADC0 Greater-Than High Byte.                                              |

|     |             | Most Significant Byte of the 16-bit Greater-Than window compare register. |

## SFR Definition 5.9. ADC0GTL: ADC0 Greater-Than Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| Name  |   | AD0GT[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W        |   |   |   |   |   |   |

| Reset | 1 | 1          | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = 0x0; SFR Address = 0xC3

| Bit   | Name                                                   | Function                                                                   |  |  |  |  |

|-------|--------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| 7:0   | AD0GT[7:0]                                             | ADC0 Greater-Than Low Byte.                                                |  |  |  |  |

|       |                                                        | Least Significant Byte of the 16-bit Greater-Than window compare register. |  |  |  |  |

| Note: | e: In 8-bit mode, this register should be set to 0x00. |                                                                            |  |  |  |  |

## 8.9. Automatic Scanning (Method 2—CS0SMEN = 1)

When CS0SMEN is enabled, CS0 uses an alternate autoscanning method that uses the contents of CS0SCAN0 and CS0SCAN1 to determine which channels to include in the scan. This maximizes flexibility for application development and can result in more power efficient scanning. The following procedure can be used to configure the device for Automatic Scanning with CS0SMEN = 1.

- 1. Set the CS0SMEN bit to 1.

- 2. Select the start of conversion mode (CS0CM[2:0]) if not already configured. Mode 101b is the mode of choice for most systems.

- 3. Configure the CS0SCAN0 and CS0SCAN1 registers to enable channels in the scan.

- 4. Configure the CS0THH:CS0THL digital comparator threshold and polarity.

- 5. Enable wake from suspend on end of scan (CS0WOI = 1) if this functionality is desired.

- 6. Set CS0SS to point to the first channel in the scan. Note: CS0SS uses the same bit mapping as the CS0MX register.

- 7. Issue a start of conversion (BUSY = 1).

- 8. Enable the CS0 Wakeup Source and place the device in Suspend mode (optional).

If using Mode 101b, scanning will stop once a "touch" has been detected using the digital comparator. The CS0MX register will contain the channel mux value of the channel that caused the interrupt. Setting the busy bit when servicing the interrupt will cause the scan to continue where it left off. Scanning will also stop after all channels have been sampled and no "touches" have been detected. If the CS0WOI bit is set, a wake from suspend event will be generated. Note: When automatic scanning is enabled, the contents of the CS0MX register are only valid when the digital comparator interrupt is set and BUSY = 0.

#### 8.10. CS0 Comparator

The CS0 comparator compares the latest capacitive sense conversion result with the value stored in CS0THH:CS0THL. If the result is less than or equal to the stored value, the CS0CMPF bit(CS0CN:0) is set to 0. If the result is greater than the stored value, CS0CMPF is set to 1.

If the CS0 conversion accumulator is configured to accumulate multiple conversions, a comparison will not be made until the last conversion has been accumulated.

An interrupt will be generated if CS0 greater-than comparator interrupts are enabled by setting the ECSDC bit (EIE2.5) when the comparator sets CS0CMPF to 1.

If auto-scan is running when the comparator sets the CS0CMPF bit, no further auto-scan initiated conversions will start until firmware sets CS0BUSY to 1.

A CS0 greater-than comparator event can wake a device from suspend mode. This feature is useful in systems configured to continuously sample one or more capacitive sense channels. The device will remain in the low-power suspend state until the captured value of one of the scanned channels causes a CS0 greater-than comparator event to occur. It is not necessary to have CS0 comparator interrupts enabled in order to wake a device from suspend with a greater-than event.

For a summary of behavior with different CS0 comparator, auto-scan, and auto accumulator settings, please see Table 8.1.

# SFR Definition 13.7. IT01CF: INT0/INT1 Configuration

| Bit   | 7     | 6          | 5     | 4 | 3     | 2 | 1          | 0 |

|-------|-------|------------|-------|---|-------|---|------------|---|

| Name  | IN1PL | IN1SL[2:0] |       |   | IN0PL |   | IN0SL[2:0] |   |

| Туре  | R/W   | R/W        |       |   | R/W   |   | R/W        |   |

| Reset | 0     | 0          | 0 0 0 |   |       | 0 | 0          | 1 |

#### SFR Page = 0x0; SFR Address = 0xE4

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IN1PL      | INT1 Polarity.         0: INT1 input is active low.         1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6:4 | IN1SL[2:0] | INT1 Port Pin Selection Bits.         These bits select which Port pin is assigned to INT1. Note that this pin assignment is independent of the Crossbar; INT1 will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.         000: Select P0.0         001: Select P0.1         010: Select P0.2         011: Select P0.3         100: Select P0.4         101: Select P0.5         111: Select P0.7 |

| 3   | IN0PL      | INTO Polarity.<br>0: INTO input is active low.<br>1: INTO input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2:0 | IN0SL[2:0] | <b>INTO</b> Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INTO. Note that this pin assignment is independent of the Crossbar; INTO will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P0.0<br>001: Select P0.1<br>010: Select P0.2<br>011: Select P0.3<br>100: Select P0.4<br>101: Select P0.5<br>110: Select P0.6<br>111: Select P0.7              |

# SFR Definition 14.2. REVID: Revision Identification

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | REVID[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Page = 0xF; SFR Address = 0xE2

| Bit | Name       | Function                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | REVID[7:0] | Revision Identification.                                                                                                                            |

|     |            | These bits contain a value that can be decoded to determine the silicon revision. For example, 0x00 for Rev A, 0x01 for Rev B, 0x02 for Rev C, etc. |

### 14.5. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

To help prevent the accidental modification of Flash by firmware, the  $V_{DD}$  Monitor must be enabled and enabled as a reset source on C8051F99x-C8051F98x devices for the Flash to be successfully modified. If either the  $V_{DD}$  Monitor or the  $V_{DD}$  Monitor reset source is not enabled, a Flash Error Device Reset will be generated when the firmware attempts to modify the Flash.

The following guidelines are recommended for any system that contains routines which write or erase Flash from code.

#### 14.5.1. $V_{DD}$ Maintenance and the $V_{DD}$ Monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. Make certain that the minimum  $V_{DD}$  rise time specification of 1 ms is met. If the system cannot meet this rise time specification, then add an external  $V_{DD}$  brownout circuit to the RST pin of the device that holds the device in reset until  $V_{DD}$  reaches the minimum device operating voltage and re-asserts RST if  $V_{DD}$  drops below the minimum device operating voltage.

- 3. Keep the on-chip V<sub>DD</sub> Monitor enabled and enable the V<sub>DD</sub> Monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> Monitor and enabling the V<sub>DD</sub> Monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories website.

#### Notes:

- On C8051F99x-C8051F98x devices, both the V<sub>DD</sub> Monitor and the V<sub>DD</sub> Monitor reset source must be enabled to write or erase Flash without generating a Flash Error Device Reset.

- 2. On C8051F99x-C8051F98x devices, both the  $V_{DD}$  Monitor and the  $V_{DD}$  Monitor reset source are enabled by hardware after a power-on reset.

- 4. As an added precaution, explicitly enable the V<sub>DD</sub> Monitor and enable the V<sub>DD</sub> Monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> Monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct, but "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

#### 15.2. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

**Note:** To ensure the MCU enters a low power state upon entry into Idle Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "18.6. PCA Watchdog Timer Reset" on page 185 for more information on the use and configuration of the WDT.

#### 15.3. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter stop mode as soon as the instruction that sets the bit completes execution. In stop mode the precision internal oscillator and CPU are stopped; the state of the low power oscillator and the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout.

Stop mode is a legacy 8051 power mode; it will not result in optimal power savings. Sleep or suspend mode will provide more power savings if the MCU needs to be inactive for a long period of time.

**Note:** To ensure the MCU enters a low power state upon entry into Stop Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

# SFR Definition 15.3. PMU0MD: Power Management Unit Mode

| Bit   | 7     | 6      | 5      | 4   | 3   | 2   | 1   | 0   |

|-------|-------|--------|--------|-----|-----|-----|-----|-----|

| Name  | RTCOE | WAKEOE | MONDIS |     |     |     |     |     |

| Туре  | R/W   | R/W    | R/W    | R/W | R/W | R/W | R/W | R/W |

| Reset | 0     | 0      | 0      | 0   | 0   | 0   | 0   | 0   |

#### SFR Page = 0xF; SFR Address = 0xB5

| Bit   | Name          | Function                                                                                                                                                                                                                                                                               |

|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | RTCOE         | Buffered SmaRTClock Output Enable.                                                                                                                                                                                                                                                     |

|       |               | Enables the buffered SmaRTClock oscillator output on P0.2.<br>0: Buffered SmaRTClock output not enabled.                                                                                                                                                                               |

|       |               | 1: Buffered SmaRTClock output is enabled.                                                                                                                                                                                                                                              |

| 6     | WAKEOE        | Wakeup Request Output Enable.                                                                                                                                                                                                                                                          |

|       |               | Enables the Sleep Mode wake-up request signal on P0.3.                                                                                                                                                                                                                                 |

|       |               | 0: Wake-up request signal is not enabled.                                                                                                                                                                                                                                              |

|       |               | 1: Wake-up request signal is enabled.                                                                                                                                                                                                                                                  |

| 5     | MONDIS*       | POR Supply Monitor Disable.                                                                                                                                                                                                                                                            |

|       |               | Writing a 1 to this bit disables the POR supply monitor.                                                                                                                                                                                                                               |

| 4:0   | Unused        | Read = 00000b. Write = Don't Care.                                                                                                                                                                                                                                                     |

| Notes | sleep mode cu | ply Monitor should not be disabled if the supply voltage is greater than 2.4 V. The lowest power urrent, 10 nA typical, can only be achieved when the supply voltage is less than 2.4 V. The sleep mode for voltages above 2.4 V is 50 nA typical with the POR Supply Monitor enabled. |

Rev. 1.2

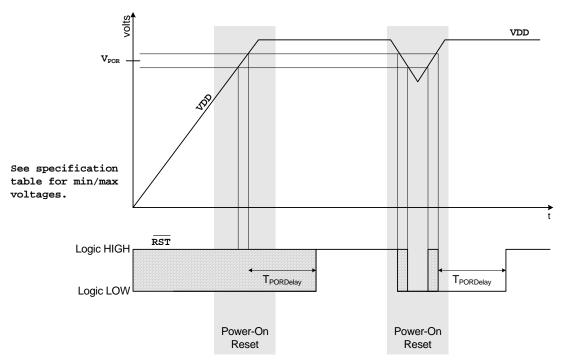

#### 18.1. Power-On Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin voltage tracks V<sub>DD</sub> (through a weak pull-up) until the device is released from reset. After VDD settles above VPOR, a delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>POR</sub>). Figure 18.2 plots the power-on and V<sub>DD</sub> monitor reset timing. For valid ramp times (less than 3 ms), the power-on reset delay (T<sub>PORDelay</sub>) is typically 7 ms (V<sub>DD</sub> = 1.8 V) or 15 ms (V<sub>DD</sub> = 3.6 V).

**Note:** The maximum  $V_{DD}$  ramp time is 3 ms; slower ramp times may cause the device to be released from reset before  $V_{DD}$  reaches the  $V_{POR}$  level.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000), software can read the PORSF flag to determine if a power-up was the cause of reset. The contents of internal data memory should be assumed to be undefined after a power-on reset.

The POR supply monitor can be disabled to save power by writing 1 to the MONDIS (PMU0MD.5) bit. When the POR supply monitor is disabled, all reset sources will trigger a full POR and will re-enable the POR supply monitor.

Figure 18.2. Power-Fail Reset Timing Diagram

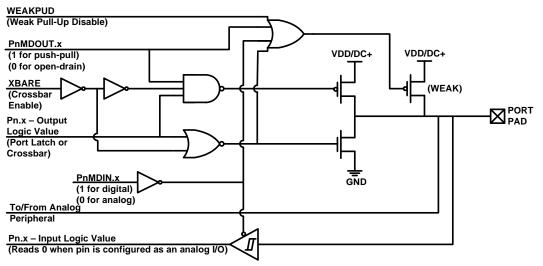

### 21.1. Port I/O Modes of Operation

Port pins P0.0–P1.7 use the Port I/O cell shown in Figure 21.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN registers. On reset, all Port I/O cells default to a digital high impedance state with weak pull-ups enabled.

#### 21.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, oscillator input/output, or AGND, VREF, or Current Reference output should be configured for analog I/O (PnMDIN.n = 0). When a pin is configured for analog I/O, its weak pullup and digital receiver are disabled. In most cases, software should also disable the digital output drivers. Port pins configured for analog I/O will always read back a value of 0 regardless of the actual voltage on the pin.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

#### 21.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high and low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user must ensure that digital I/O are always internally or externally pulled or driven to a valid logic state. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

Figure 21.2. Port I/O Cell Block Diagram

# SFR Definition 21.17. P1DRV: Port1 Drive Strength

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------|---|---|---|---|---|---|---|

| Name  | P1DRV[7:0]      |   |   |   |   |   |   |   |

| Туре  | R/W             |   |   |   |   |   |   |   |

| Reset | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

SFR Page = 0xF; SFR Address = 0x9B

| Bit | Name       | Function                                                                                                                                                                                               |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |  |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |  |

## SFR Definition 21.18. P2: Port2

| Bit   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|---|---|---|---|---|---|---|

| Name  | P2  |   |   |   |   |   |   |   |

| Туре  | R/W | R | R | R | R | R | R | R |

| Reset | 1   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = All; SFR Address = 0xA0; Bit-Addressable

| Bit | Name   | Description                                                                                                                                   | Read                                                                          | Write |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------|

| 7   | P2     | <b>Port 2 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW.  |

| 6:0 | Unused | Read = 0000000b; Write = D                                                                                                                    | on't Care.                                                                    |       |

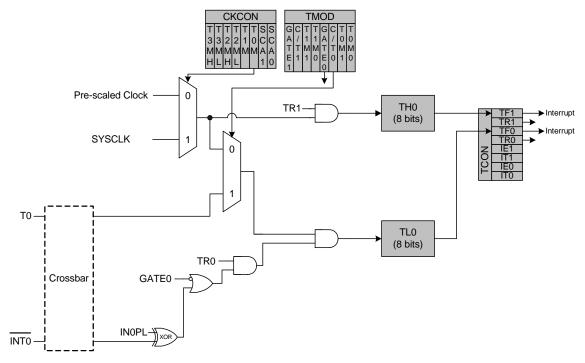

#### 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 25.3. T0 Mode 3 Block Diagram

### 26.4. Watchdog Timer Mode

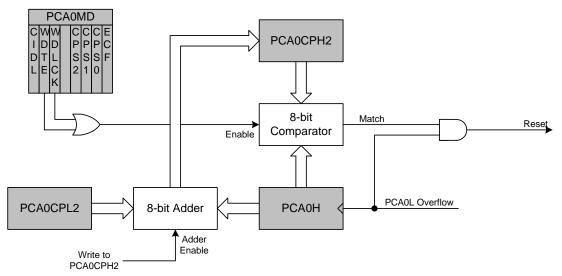

A programmable watchdog timer (WDT) function is available through the PCA Module 2. The WDT is used to generate a reset if the time between writes to the WDT update register (PCA0CPH2) exceed a specified limit. The WDT can be configured and enabled/disabled as needed by software.

With the WDTE bit set in the PCA0MD register, Module 2 operates as a watchdog timer (WDT). The Module 2 high byte is compared to the PCA counter high byte; the Module 2 low byte holds the offset to be used when WDT updates are performed. The Watchdog Timer is enabled on reset. Writes to some PCA registers are restricted while the Watchdog Timer is enabled. The WDT will generate a reset shortly after code begins execution. To avoid this reset, the WDT should be explicitly disabled (and optionally re-configured and re-enabled if it is used in the system).

#### 26.4.1. Watchdog Timer Operation

While the WDT is enabled:

- PCA counter is forced on.

- Writes to PCA0L and PCA0H are not allowed.

- PCA clock source bits (CPS2–CPS0) are frozen.

- PCA Idle control bit (CIDL) is frozen.

- Module 2 is forced into software timer mode.

- Writes to the Module 2 mode register (PCA0CPM2) are disabled.

While the WDT is enabled, writes to the CR bit will not change the PCA counter state; the counter will run until the WDT is disabled. The PCA counter run control bit (CR) will read zero if the WDT is enabled but user software has not enabled the PCA counter. If a match occurs between PCA0CPH2 and PCA0H while the WDT is enabled, a reset will be generated. To prevent a WDT reset, the WDT may be updated with a write of any value to PCA0CPH2. Upon a PCA0CPH2 write, PCA0H plus the offset held in PCA0CPL2 is loaded into PCA0CPH2 (See Figure 26.11).

Figure 26.11. PCA Module 2 with Watchdog Timer Enabled

# 27. C2 Interface

C8051F99x-C8051F98x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

#### 27.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

#### C2 Register Definition 27.1. C2ADD: C2 Address

| Bit   | 7          | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|-----------------|---|---|---|---|---|---|

| Name  | C2ADD[7:0] |                 |   |   |   |   |   |   |

| Туре  | R/W        |                 |   |   |   |   |   |   |

| Reset | 0          | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

| Bit | Name       |                                                                                                                               | Function                                                                           |  |  |  |  |  |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0 | C2ADD[7:0] | C2 Address.                                                                                                                   |                                                                                    |  |  |  |  |  |

|     |            | The C2ADD register is accessed via the C2 interface to select the target Data regis for C2 Data Read and Data Write commands. |                                                                                    |  |  |  |  |  |

|     |            | Address Description                                                                                                           |                                                                                    |  |  |  |  |  |

|     |            | 0x00                                                                                                                          | Selects the Device ID register for Data Read instructions                          |  |  |  |  |  |

|     |            | 0x01                                                                                                                          | Selects the Revision ID register for Data Read instructions                        |  |  |  |  |  |

|     |            | 0x02                                                                                                                          | Selects the C2 Flash Programming Control register for Data Read/Write instructions |  |  |  |  |  |

|     |            | 0xB4                                                                                                                          | Selects the C2 Flash Programming Data register for Data Read/Write instructions    |  |  |  |  |  |