Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

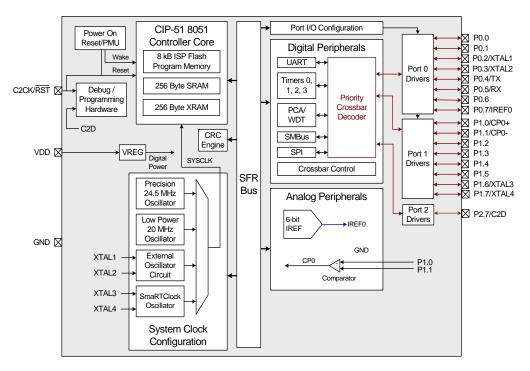

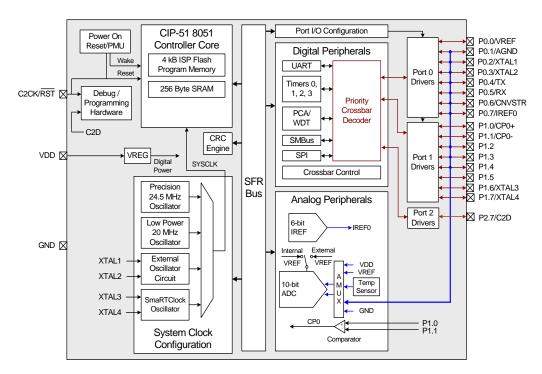

| Core Processor             | CIP-51 8051                                                      |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                            |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 4KB (4K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 512 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                      |

| Data Converters            | -                                                                |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-UFQFN Exposed Pad                                             |

| Supplier Device Package    | 20-QFN (3x3)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f983-c-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1. | System Overview                                                            | 17  |

|----|----------------------------------------------------------------------------|-----|

|    | 1.1. CIP-51 <sup>™</sup> Microcontroller Core                              | 25  |

|    | 1.1.1. Fully 8051 Compatible                                               | 25  |

|    | 1.1.2. Improved Throughput                                                 | 25  |

|    | 1.1.3. Additional Features                                                 |     |

|    | 1.2. Port Input/Output                                                     | 26  |

|    | 1.3. Serial Ports                                                          | 27  |

|    | 1.4. Programmable Counter Array                                            | 27  |

|    | 1.5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Pow |     |

|    | Burst Mode                                                                 |     |

|    | 1.6. Programmable Current Reference (IREF0)                                | 29  |

|    | 1.7. Comparator                                                            | 29  |

| 2. | Ordering Information                                                       | 31  |

| 3. | Pinout and Package Definitions                                             | 32  |

| 4. |                                                                            |     |

|    | 4.1. Absolute Maximum Specifications                                       |     |

|    | 4.2. Electrical Characteristics                                            | -   |

| 5. | SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Pow      | /er |

|    | Burst Mode                                                                 |     |

|    | 5.1. Output Code Formatting                                                | 67  |

|    | 5.2. Modes of Operation                                                    |     |

|    | 5.2.1. Starting a Conversion                                               | 68  |

|    | 5.2.2. Tracking Modes                                                      |     |

|    | 5.2.3. Burst Mode                                                          |     |

|    | 5.2.4. Settling Time Requirements                                          |     |

|    | 5.2.5. Gain Setting                                                        |     |

|    | 5.3. 8-Bit Mode                                                            |     |

|    | 5.4. 12-Bit Mode (C8051F980/6 and C8051F990/6 devices only)                |     |

|    | 5.5. Low Power Mode                                                        |     |

|    | 5.6. Programmable Window Detector                                          |     |

|    | 5.6.1. Window Detector In Single-Ended Mode                                |     |

|    | 5.6.2. ADC0 Specifications                                                 |     |

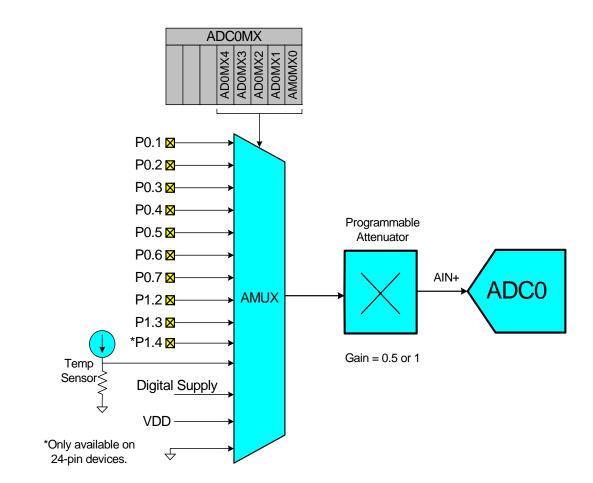

|    | 5.7. ADC0 Analog Multiplexer                                               |     |

|    | 5.8. Temperature Sensor                                                    |     |

|    | 5.8.1. Calibration                                                         |     |

|    | 5.9. Voltage and Ground Reference Options                                  |     |

|    | 5.10.External Voltage Reference                                            |     |

|    | 5.11.Internal Voltage Reference                                            |     |

|    | 5.12.Analog Ground Reference                                               |     |

|    | 5.13.Temperature Sensor Enable                                             | 89  |

|    | 5.14.Voltage Reference Electrical Specifications                           |     |

| 6. | Programmable Current Reference (IREF0)                                     |     |

|    | 6.1. PWM Enhanced Mode                                                     | 91  |

|     |            | 21.9. P0SKIP: Port0 Skip                          |     |

|-----|------------|---------------------------------------------------|-----|

|     |            | 21.10. P0MDIN: Port0 Input Mode                   |     |

| SFR | Definition | 21.11. P0MDOUT: Port0 Output Mode                 | 229 |

| SFR | Definition | 21.12. P0DRV: Port0 Drive Strength                | 230 |

|     |            | 21.13. P1: Port1                                  |     |

|     |            | 21.14. P1SKIP: Port1 Skip                         |     |

|     |            | 21.15. P1MDIN: Port1 Input Mode                   |     |

|     |            | 21.16. P1MDOUT: Port1 Output Mode                 |     |

|     |            | 21.17. P1DRV: Port1 Drive Strength                |     |

|     |            | 21.18. P2: Port2                                  |     |

|     |            | 21.19. P2MDOUT: Port2 Output Mode                 |     |

|     |            | 21.20. P2DRV: Port2 Drive Strength                |     |

|     |            | 22.1. SMB0CF: SMBus Clock/Configuration           |     |

|     |            | 22.2. SMB0CN: SMBus Control                       |     |

|     |            | 22.3. SMB0ADR: SMBus Slave Address                |     |

|     |            | 22.4. SMB0ADM: SMBus Slave Address Mask           |     |

|     |            | 22.5. SMB0DAT: SMBus Data                         |     |

|     |            | 23.1. SCON0: Serial Port 0 Control                |     |

|     |            | 23.2. SBUF0: Serial (UART0) Port Data Buffer      |     |

|     |            | 24.1. SPI0CFG: SPI0 Configuration                 |     |

|     |            | 24.2. SPI0CN: SPI0 Control                        |     |

|     |            | 24.3. SPI0CKR: SPI0 Clock Rate                    |     |

|     |            | 24.4. SPI0DAT: SPI0 Data                          |     |

|     |            | 25.1. CKCON: Clock Control                        |     |

|     |            | 25.2. TCON: Timer Control                         |     |

|     |            | 25.3. TMOD: Timer Mode                            |     |

|     |            | 25.4. TL0: Timer 0 Low Byte                       |     |

|     |            | 25.5. TL1: Timer 1 Low Byte                       |     |

|     |            | 25.6. TH0: Timer 0 High Byte                      |     |

|     |            | 25.7. TH1: Timer 1 High Byte                      |     |

|     |            | 25.8. TMR2CN: Timer 2 Control                     |     |

|     |            | 25.9. TMR2RLL: Timer 2 Reload Register Low Byte   |     |

|     |            | 25.10. TMR2RLH: Timer 2 Reload Register High Byte |     |

|     |            | 25.11. TMR2L: Timer 2 Low Byte                    |     |

|     |            | 25.12. TMR2H Timer 2 High Byte                    |     |

|     |            | 25.13. TMR3CN: Timer 3 Control                    |     |

|     |            | 25.14. TMR3RLL: Timer 3 Reload Register Low Byte  |     |

|     |            | 25.15. TMR3RLH: Timer 3 Reload Register High Byte |     |

|     |            | 25.16. TMR3L: Timer 3 Low Byte                    |     |

|     |            | 25.17. TMR3H Timer 3 High Byte                    |     |

|     |            | 26.1. PCA0CN: PCA Control                         |     |

|     |            | 26.2. PCA0MD: PCA Mode                            |     |

|     |            | 26.3. PCA0PWM: PCA PWM Configuration              |     |

|     |            | 26.4. PCA0CPMn: PCA Capture/Compare Mode          |     |

| SFR | Definition | 26.5. PCA0L: PCA Counter/Timer Low Byte           | 317 |

## C8051F99x-C8051F98x

# C8051F99x-C8051F98x

Figure 1.17. ADC0 Multiplexer Block Diagram

## 1.6. Programmable Current Reference (IREF0)

C8051F99x-C8051F98x devices include an on-chip programmable current reference (source or sink) with two output current settings: low power mode and high current mode. The maximum current output in low power mode is 63  $\mu$ A (1  $\mu$ A steps) and the maximum current output in high current mode is 504  $\mu$ A (8  $\mu$ A steps).

## 1.7. Comparator

C8051F99x-C8051F98x devices include an on-chip programmable voltage comparator: Comparator 0 (CPT0) which is shown in Figure 1.18.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0), or an asynchronous "raw" output (CP0A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output when the device is in some low power modes.

The comparator inputs may be connected to Port I/O pins or to other internal signals. Port pins may also be used to directly sense capacitive touch switches.

|                | Pin                                    | Number                                 | S                                    |                  |                                                                                                                                              |  |  |

|----------------|----------------------------------------|----------------------------------------|--------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name           | 'F980/1/2<br>'F983/5<br>'F990/1<br>-GM | <pre>'F986/7 'F988/9 'F996/7 -GM</pre> | 'F986/7<br>'F988/9<br>'F996/7<br>-GU | Туре             | Description                                                                                                                                  |  |  |

| P0.1/          | 1                                      | 23                                     | 2                                    | D I/O or<br>A In | Port 0.1. See Port I/O Section for a complete description                                                                                    |  |  |

| AGND*          |                                        |                                        |                                      | G                | Optional Analog Ground. See Section "5.9. Voltage and Ground Reference Options" on page 88.                                                  |  |  |

| P0.2/          | 20                                     | 22                                     | 1                                    | D I/O or<br>A In | Port 0.2. See Port I/O Section for a complete description.                                                                                   |  |  |

| XTAL1/         |                                        |                                        |                                      | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator. See Section "19. Clocking Sources" on page 188. |  |  |

| RTCOUT         |                                        |                                        |                                      | D Out            | Buffered SmaRTClock oscillator output.                                                                                                       |  |  |

| P0.3/          | 19                                     | 21                                     | 24                                   | D I/O or<br>A In | Port 0.3. See Section "21. Port Input/Output" on page 215 for a complete description.                                                        |  |  |

| XTAL2/         |                                        |                                        |                                      | A Out            | External Clock Output. This pin is the excitation driver for an external crystal or resonator.                                               |  |  |

|                |                                        |                                        |                                      | D In             | External Clock Input. This pin is the external clock input in external CMOS clock mode.                                                      |  |  |

|                |                                        |                                        |                                      | A In             | External Clock Input. This pin is the external clock input in capacitor or RC oscillator configurations.                                     |  |  |

|                |                                        |                                        |                                      |                  | See Section "19. Clocking Sources" on page 188 for<br>complete details.                                                                      |  |  |

| WAKEOUT        |                                        |                                        |                                      | D Out            | Wake-up request signal to wake up external devices.                                                                                          |  |  |

| P0.4/          | 18                                     | 20                                     | 23                                   | D I/O or<br>A In | Port 0.4. See Section "21. Port Input/Output" on page 215 for a complete description.                                                        |  |  |

| ТΧ             |                                        |                                        |                                      | D Out            | UART TX Pin. See Section "21. Port Input/Output" on page 215.                                                                                |  |  |

| P0.5/          | 17                                     | 19                                     | 22                                   | D I/O or<br>A In | Port 0.5. See Section "21. Port Input/Output" on page 215 for a complete description.                                                        |  |  |

| RX             |                                        |                                        |                                      | D In             | UART RX Pin. See Section "21. Port Input/Output" on page 215.                                                                                |  |  |

| *Note: Availal | ble only on t                          | he C805 <sup>-</sup>                   | 1F980/2/6                            | 6/8 and C80      | 051F990/6 devices.                                                                                                                           |  |  |

## Table 3.1. Pin Definitions for the C8051F99x-C8051F98x (Continued)

\*Note: Signal only available on 'F980, 'F982 and 'F990 devices.

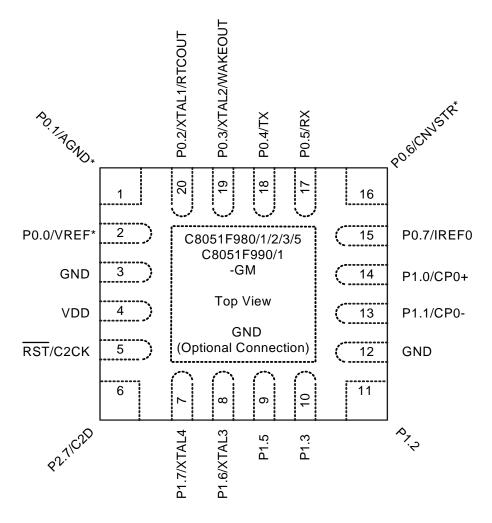

Figure 3.1. QFN-20 Pinout Diagram (Top View)

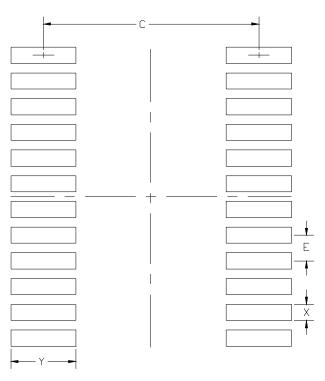

## Table 3.7. PCB Land Pattern

| Dimension | MIN       | MAX  |  |

|-----------|-----------|------|--|

| С         | 5.20      | 5.30 |  |

| E         | 0.635 BSC |      |  |

| X         | 0.30      | 0.40 |  |

| Y         | 1.50      | 1.60 |  |

#### Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

3. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

#### Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

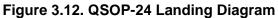

## 5.9. Voltage and Ground Reference Options

The voltage reference MUX is configurable to use an externally connected voltage reference, the internal voltage reference, or one of two power supply voltages (see Figure 5.10). The ground reference MUX allows the ground reference for ADC0 to be selected between the ground pin (GND) or a port pin dedicated to analog ground (P0.1/AGND).

The voltage and ground reference options are configured using the REF0CN SFR described on page 90. Electrical specifications are can be found in the Electrical Specifications Chapter.

**Important Note About the V<sub>REF</sub> and AGND Inputs:** Port pins are used as the external V<sub>REF</sub> and AGND inputs. When using an external voltage reference or the internal precision reference, P0.0/VREF should be configured as an analog input and skipped by the Digital Crossbar. When using AGND as the ground reference to ADC0, P0.1/AGND should be configured as an analog input and skipped by the Digital Crossbar. Refer to Section "21. Port Input/Output" on page 215 for complete Port I/O configuration details. The external reference voltage must be within the range  $0 \le V_{REF} \le VDD$  and the external ground reference must be at the same DC voltage potential as GND.

Figure 5.10. Voltage Reference Functional Block Diagram

## SFR Definition 8.15. CS0MX: Capacitive Sense Mux Channel Select

| Bit   | 7        | 6        | 5        | 4        | 3          | 2   | 1   | 0   |

|-------|----------|----------|----------|----------|------------|-----|-----|-----|

| Name  | Reserved | Reserved | Reserved | Reserved | CS0MX[3:0] |     |     |     |

| Туре  | R/W      | R/W      | R/W      | R/W      | R/W        | R/W | R/W | R/W |

| Reset | 0        | 0        | 0        | 0        | 0          | 0   | 0   | 0   |

SFR Page = 0x0; SFR Address = 0xAB

| Bit | Name       |             | Description                                               |  |  |  |  |

|-----|------------|-------------|-----------------------------------------------------------|--|--|--|--|

| 7:5 | Reserved   | Read = 000  | Read = 0000b; Write = 0000b.                              |  |  |  |  |

| 4:0 | CS0MX[4:0] | CS0 Mux C   | CS0 Mux Channel Select.                                   |  |  |  |  |

|     |            | Selects one | of the 14 input channels for Capacitive Sense conversion. |  |  |  |  |

|     |            | Value       | Channel                                                   |  |  |  |  |

|     |            | 0000        | P0.0                                                      |  |  |  |  |

|     |            | 0001        | P0.1                                                      |  |  |  |  |

|     |            | 0010        | P0.2                                                      |  |  |  |  |

|     |            | 0011        | P0.3                                                      |  |  |  |  |

|     |            | 0100        | <b>00</b> P0.4                                            |  |  |  |  |

|     |            | 0101        | P0.5                                                      |  |  |  |  |

|     |            | 0110        | P0.6                                                      |  |  |  |  |

|     |            | 0111        | P0.7                                                      |  |  |  |  |

|     |            | 1000        | P1.0                                                      |  |  |  |  |

|     |            | 1001        | P1.1                                                      |  |  |  |  |

|     |            | 1010        | P1.2                                                      |  |  |  |  |

|     |            | 1011        | P1.3                                                      |  |  |  |  |

|     |            | 1100        | P1.4 (24-pin packages only)                               |  |  |  |  |

|     |            | 1101        | P1.5                                                      |  |  |  |  |

|     |            | 1110        | Reserved                                                  |  |  |  |  |

|     |            | 1111        | Reserved                                                  |  |  |  |  |

#### Notes on Registers, Operands and Addressing Modes:

**Rn**—Register R0–R7 of the currently selected register bank.

@Ri—Data RAM location addressed indirectly through R0 or R1.

**rel**—8-bit, signed (twos complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct**—8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data—8-bit constant

#data16—16-bit constant

**bit**—Direct-accessed bit in Data RAM or SFR

**addr11**—11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16**—16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

## SFR Definition 13.7. IT01CF: INT0/INT1 Configuration

| Bit   | 7     | 6   | 5          | 4 | 3     | 2          | 1   | 0 |

|-------|-------|-----|------------|---|-------|------------|-----|---|

| Name  | IN1PL |     | IN1SL[2:0] |   | IN0PL | IN0SL[2:0] |     |   |

| Туре  | R/W   | R/W |            |   | R/W   |            | R/W |   |

| Reset | 0     | 0   | 0          | 0 | 0     | 0          | 0   | 1 |

#### SFR Page = 0x0; SFR Address = 0xE4

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IN1PL      | INT1 Polarity.         0: INT1 input is active low.         1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6:4 | IN1SL[2:0] | INT1 Port Pin Selection Bits.         These bits select which Port pin is assigned to INT1. Note that this pin assignment is independent of the Crossbar; INT1 will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.         000: Select P0.0         001: Select P0.1         010: Select P0.2         011: Select P0.3         100: Select P0.4         101: Select P0.5         111: Select P0.7 |

| 3   | IN0PL      | INTO Polarity.<br>0: INTO input is active low.<br>1: INTO input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2:0 | IN0SL[2:0] | <b>INTO</b> Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INTO. Note that this pin assignment is independent of the Crossbar; INTO will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P0.0<br>001: Select P0.1<br>010: Select P0.2<br>011: Select P0.3<br>100: Select P0.4<br>101: Select P0.5<br>110: Select P0.6<br>111: Select P0.7              |

| Action                                                                   | C2 Debug      | User Firmware executing from: |               |  |

|--------------------------------------------------------------------------|---------------|-------------------------------|---------------|--|

|                                                                          | Interface     | an unlocked page              | a locked page |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)      | Permitted     | Permitted                     | Permitted     |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)        | Not Permitted | FEDR                          | Permitted     |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)      | Permitted     | Permitted                     | Permitted     |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)       | Not Permitted | FEDR                          | Permitted     |  |

| Read contents of Lock Byte<br>(if no pages are locked)                   | Permitted     | Permitted                     | Permitted     |  |

| Read contents of Lock Byte<br>(if any page is locked)                    | Not Permitted | FEDR                          | Permitted     |  |

| Erase page containing Lock Byte<br>(if no pages are locked)              | Permitted     | FEDR                          | FEDR          |  |

| Erase page containing Lock Byte—Unlock all pages (if any page is locked) | Only by C2DE  | FEDR                          | FEDR          |  |

| Lock additional pages<br>(change 1s to 0s in the Lock Byte)              | Not Permitted | FEDR                          | FEDR          |  |

| Unlock individual pages<br>(change 0s to 1s in the Lock Byte)            | Not Permitted | FEDR                          | FEDR          |  |

| Read, Write or Erase Reserved Area                                       | Not Permitted | FEDR                          | FEDR          |  |

## Table 14.1. Flash Security Summary

• C2DE—C2 Device Erase (Erases all Flash pages including the page containing the Lock Byte)

■ FEDR—Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is 1 after reset)

All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

• Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

- The scratchpad is locked when all other Flash pages are locked.

- The scratchpad is erased when a Flash Device Erase command is performed.

## 15.2. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

**Note:** To ensure the MCU enters a low power state upon entry into Idle Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "18.6. PCA Watchdog Timer Reset" on page 185 for more information on the use and configuration of the WDT.

## 15.3. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter stop mode as soon as the instruction that sets the bit completes execution. In stop mode the precision internal oscillator and CPU are stopped; the state of the low power oscillator and the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout.

Stop mode is a legacy 8051 power mode; it will not result in optimal power savings. Sleep or suspend mode will provide more power savings if the MCU needs to be inactive for a long period of time.

**Note:** To ensure the MCU enters a low power state upon entry into Stop Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

## SFR Definition 15.2. PMU0FL: Power Management Unit Flag<sup>1,2</sup>

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|-------|---|---|---|---|---|---|---|--------|

| Name  |   |   |   |   |   |   |   | CS0WK  |

| Туре  | R | R | R | R | R | R | R | R/W    |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Varies |

SFR Page = 0x0; SFR Address = 0xCE

| Bit | Name   | Description                           | Write                                                                     | Read                                           |

|-----|--------|---------------------------------------|---------------------------------------------------------------------------|------------------------------------------------|

| 7:1 | Unused | Unused                                | Don't Care.                                                               | 000000b                                        |

| 0   | CS0WK  | CS0 Wake-up Source<br>Enable and Flag | 0: Disable wake-up on<br>CS0 event.<br>1: Enable wake-up on CS0<br>event. | Set to 1 if CS0 event caused the last wake-up. |

Notes:

1. The Low Power Internal Oscillator cannot be disabled and the MCU cannot be placed in Suspend or Sleep Mode if any wake-up flags are set to 1. Software should clear all wake-up sources after each reset and after each wake-up from Suspend or Sleep Modes.

2. PMU0 requires two system clocks to update the wake-up source flags after waking from Suspend mode. The wake-up source flags will read '0' during the first two system clocks following the wake from Suspend mode.

## 20.1. SmaRTClock Interface

The SmaRTClock Interface consists of three registers: RTC0KEY, RTC0ADR, and RTC0DAT. These interface registers are located on the CIP-51's SFR map and provide access to the SmaRTClock internal registers listed in Table 20.1. The SmaRTClock internal registers can only be accessed indirectly through the SmaRTClock Interface.

| SmaRTClock<br>Address | SmaRTClock<br>Register | Register Name                                   | Description                                                                                      |  |  |  |  |

|-----------------------|------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| 0x00–0x03             | CAPTUREn               | SmaRTClock Capture<br>Registers                 | Four Registers used for setting the 32-bit<br>SmaRTClock timer or reading its current value.     |  |  |  |  |

| 0x04                  | RTC0CN                 | SmaRTClock Control<br>Register                  | Controls the operation of the SmaRTClock State Machine.                                          |  |  |  |  |

| 0x05                  | RTC0XCN                | SmaRTClock Oscillator<br>Control Register       | Controls the operation of the SmaRTClock<br>Oscillator.                                          |  |  |  |  |

| 0x06                  | RTC0XCF                | SmaRTClock Oscillator<br>Configuration Register | Controls the value of the progammable oscillator load capacitance and enables/disables AutoStep. |  |  |  |  |

| 0x08–0x0B             | ALARMn                 | SmaRTClock Alarm<br>Registers                   | Four registers used for setting or reading the 32-bit SmaRTClock alarm value.                    |  |  |  |  |

Table 20.1. SmaRTClock Internal Registers

## 20.1.1. SmaRTClock Lock and Key Functions

The SmaRTClock Interface has an RTC0KEY register for legacy reasons, however, all writes to this register are ignored. The SmaRTClock interface is always unlocked on C8051F99x-C8051F98x.

## 20.3.3. Software Considerations for using the SmaRTClock Timer and Alarm

The SmaRTClock timer and alarm have two operating modes to suit varying applications. The two modes are described below:

#### Mode 1:

The first mode uses the SmaRTClock timer as a perpetual timebase which is never reset to zero. Every 36 hours, the timer is allowed to overflow without being stopped or disrupted. The alarm interval is software managed and is added to the ALRMn registers by software after each alarm. This allows the alarm match value to always stay ahead of the timer by one software managed interval. If software uses 32-bit unsigned addition to increment the alarm match value, then it does not need to handle overflows since both the timer and the alarm match value will overflow in the same manner.

This mode is ideal for applications which have a long alarm interval (e.g., 24 or 36 hours) and/or have a need for a perpetual timebase. An example of an application that needs a perpetual timebase is one whose wake-up interval is constantly changing. For these applications, software can keep track of the number of timer overflows in a 16-bit variable, extending the 32-bit (36 hour) timer to a 48-bit (272 year) perpetual timebase.

#### Mode 2:

The second mode uses the SmaRTClock timer as a general purpose up counter which is auto reset to zero by hardware after each alarm. The alarm interval is managed by hardware and stored in the ALRMn registers. Software only needs to set the alarm interval once during device initialization. After each alarm, software should keep a count of the number of alarms that have occurred in order to keep track of time.

This mode is ideal for applications that require minimal software intervention and/or have a fixed alarm interval. This mode is the most power efficient since it requires less CPU time per alarm.

## SFR Definition 21.6. P1MASK: Port1 Mask Register

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|-------------|---|---|---|---|---|---|---|--|--|--|

| Name  | P1MASK[7:0] |   |   |   |   |   |   |   |  |  |  |

| Туре  | R/W         |   |   |   |   |   |   |   |  |  |  |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Page= 0x0; SFR Address = 0xBF

| Bit | Name        | Function                                                                                                                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MASK[7:0] | Port 1 Mask Value.                                                                                                                                                                                  |

|     |             | Selects P1 pins to be compared to the corresponding bits in P1MAT.<br>0: P1.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P1.n pin logic value is compared to P1MAT.n. |

## SFR Definition 21.7. P1MAT: Port1 Match Register

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|--|

| Name  | P1MAT[7:0] |   |   |   |   |   |   |   |  |  |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |  |  |

| Reset | 1          | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |  |  |

SFR Page = 0x0; SFR Address = 0xCF

| Bit | Name       | Function                                                                                                                                                                                    |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MAT[7:0] | Port 1 Match Value.                                                                                                                                                                         |

|     |            | Match comparison value used on Port 1 for bits in P1MASK which are set to 1.<br>0: P1.n pin logic value is compared with logic LOW.<br>1: P1.n pin logic value is compared with logic HIGH. |

## 22.5. SMBus Transfer Modes

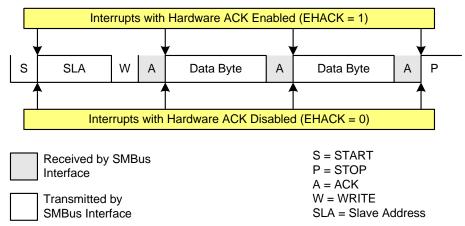

The SMBus interface may be configured to operate as master and/or slave. At any particular time, it will be operating in one of the following four modes: Master Transmitter, Master Receiver, Slave Transmitter, or Slave Receiver. The SMBus interface enters Master Mode any time a START is generated, and remains in Master Mode until it loses an arbitration or generates a STOP. An SMBus interrupt is generated at the end of all SMBus byte frames. Note that the position of the ACK interrupt when operating as a receiver depends on whether hardware ACK generation is enabled. As a receiver, the interrupt for an ACK occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled. As a transmitter, interrupts occur **after** the ACK, regardless of whether hardware ACK generation is enabled or not.

#### 22.5.1. Write Sequence (Master)

During a write sequence, an SMBus master writes data to a slave device. The master in this transfer will be a transmitter during the address byte, and a transmitter during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 0 (WRITE). The master then transmits one or more bytes of serial data. After each byte is transmitted, an acknowledge bit is generated by the slave. The transfer is ended when the STO bit is set and a STOP is generated. Note that the interface will switch to Master Receiver Mode if SMB0DAT is not written following a Master Transmitter interrupt. Figure 22.5 shows a typical master write sequence. Two transmit data bytes are shown, though any number of bytes may be transmitted. Notice that all of the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode, regardless of whether hardware ACK generation is enabled.

Figure 22.5. Typical Master Write Sequence

| Γ                  | Values Read      |       |         |     |                                                                    |                                                                                                                        |   | lues<br>Nrit |     | tus<br>ected                   |

|--------------------|------------------|-------|---------|-----|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---|--------------|-----|--------------------------------|

| Mode               | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                                                | Typical Response Options                                                                                               |   | STO          | ACK | Next Status<br>Vector Expected |

|                    | 1110             | 0     | 0       | х   | A master START was gener-<br>ated.                                 | Load slave address + R/W into SMB0DAT.                                                                                 | 0 | 0            | х   | 1100                           |

|                    |                  |       | •       | _   | was transmitted: NACK                                              | Set STA to restart transfer.                                                                                           | 1 | 0            | Х   | 1110                           |

| Sr.                |                  | 0     | 0       | 0   |                                                                    | Abort transfer.                                                                                                        | 0 | 1            | Х   | —                              |

| Master Transmitter |                  |       |         |     | A master data or address byte<br>was transmitted; ACK<br>received. | Load next data byte into SMB0-<br>DAT.                                                                                 | 0 | 0            | х   | 1100                           |

| Trar               |                  |       |         |     |                                                                    | End transfer with STOP.                                                                                                | 0 | 1            | Х   | _                              |

| aster <sup>-</sup> | 1100             | 0     | 0       | 1   |                                                                    | End transfer with STOP and start another transfer.                                                                     | 1 | 1            | х   | —                              |

| Σ                  |                  | Ŭ     | Ŭ       |     |                                                                    | Send repeated START.                                                                                                   | 1 | 0            | Х   | 1110                           |

|                    |                  |       |         |     |                                                                    | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT). Set ACK for initial<br>data byte. | 0 | 0            | 1   | 1000                           |

|                    |                  |       |         | 1   | A master data byte was<br>received; ACK sent.                      | Set ACK for next data byte;<br>Read SMB0DAT.                                                                           | 0 | 0            | 1   | 1000                           |

|                    |                  | 0     | 0       |     |                                                                    | Set NACK to indicate next data<br>byte as the last data byte;<br>Read SMB0DAT.                                         | 0 | 0            | 0   | 1000                           |

| ٣                  |                  |       |         |     |                                                                    | Initiate repeated START.                                                                                               | 1 | 0            | 0   | 1110                           |

| Master Receiver    | 1000             |       |         |     |                                                                    | Switch to Master Transmitter<br>Mode (write to SMB0DAT before<br>clearing SI).                                         | 0 | 0            | x   | 1100                           |

| aste               |                  |       |         |     |                                                                    | Read SMB0DAT; send STOP.                                                                                               | 0 | 1            | 0   | —                              |

| Ŵ                  |                  |       |         |     | A master data byte was                                             | Read SMB0DAT; Send STOP followed by START.                                                                             | 1 | 1            | 0   | 1110                           |

|                    |                  | 0     | 0       | 0   | received; NACK sent (last                                          | Initiate repeated START.                                                                                               | 1 | 0            | 0   | 1110                           |

|                    |                  |       |         |     | byte).                                                             | Switch to Master Transmitter<br>Mode (write to SMB0DAT before<br>clearing SI).                                         | 0 | 0            | x   | 1100                           |

# Table 22.6. SMBus Status Decoding With Hardware ACK Generation Enabled(EHACK = 1)

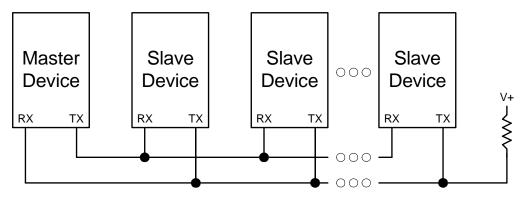

Figure 23.6. UART Multi-Processor Mode Interconnect Diagram