Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                       |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 2KB (2K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-UFQFN Exposed Pad                                              |

| Supplier Device Package    | 20-QFN (3x3)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f985-c-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 26.6. PCA0H: PCA Counter/Timer High Byte          | 317 |

|------------------------------------------------------------------|-----|

| SFR Definition 26.7. PCA0CPLn: PCA Capture Module Low Byte       | 318 |

| SFR Definition 26.8. PCA0CPHn: PCA Capture Module High Byte      | 318 |

| C2 Register Definition 27.1. C2ADD: C2 Address                   | 319 |

| C2 Register Definition 27.2. DEVICEID: C2 Device ID              | 320 |

| C2 Register Definition 27.3. REVID: C2 Revision ID               | 320 |

| C2 Register Definition 27.4. FPCTL: C2 Flash Programming Control | 321 |

| C2 Register Definition 27.5. FPDAT: C2 Flash Programming Data    | 321 |

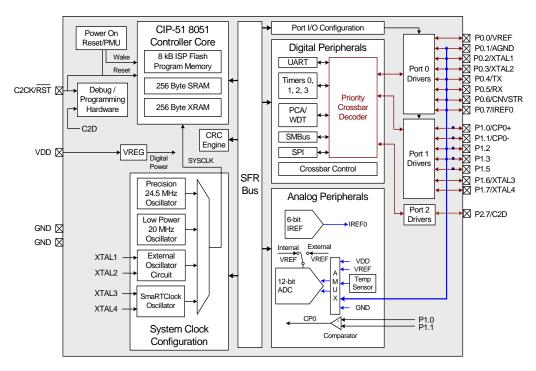

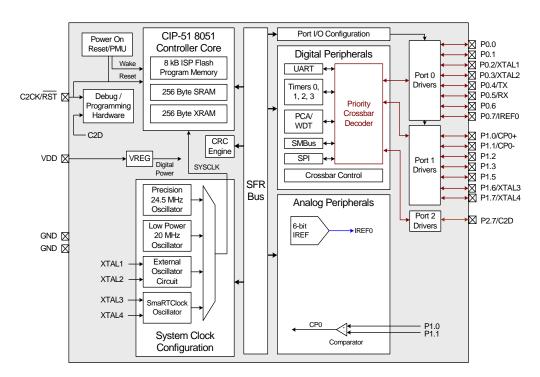

# 1. System Overview

C8051F99x-C8051F98x devices are fully integrated mixed-signal system-on-a-chip MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- Ultra low power consumption in active and sleep modes.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- 10-bit 300 ksps or 12-bit 75 ksps single-ended ADC with analog multiplexer

- 6-bit programmable current reference (resolution can be increased with PWM)

- Precision programmable 24.5 MHz internal oscillator with spread spectrum technology.

- 8 kB, 4 kB, or 2 kB of on-chip Flash memory

- 512 bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable counter/timer array (PCA) with three capture/compare modules and watchdog timer function

- On-chip power-on reset, V<sub>DD</sub> monitor, and temperature sensor

- One on-chip voltage comparator

- Up to 14 Capacitive Touch Inputs

- Up to 17 Port I/O

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051F99x-C8051F98x devices are truly stand-alone system-on-a-chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 1.8 to 3.6 V operation over the industrial temperature range (-40 to +85 °C). The Port I/O and RST pins are powered from the supply voltage. The C8051F99x-C8051F98x devices are available in 20-pin or 24-pin QFN or 24-pin QSOP packages. All package options are lead-free and RoHS compliant. See Table 2.1 for ordering information. Block diagrams are included in Figure 1.1 through Figure 1.9.

Figure 1.2. C8051F981 Block Diagram

| Dimension | Min  | Мах  |

|-----------|------|------|

| D         | 2.71 | REF  |

| D2        | 1.60 | 1.80 |

| е         | 0.50 | BSC  |

| E         | 2.71 | REF  |

| E2        | 1.60 | 1.80 |

| f         | 2.53 | REF  |

| GD        | 2.10 | —    |

| GE        | 2.10 | —    |

| W         | —    | 0.34 |

| Х         | —    | 0.28 |

| Y         | 0.61 | REF  |

| ZE        | _    | 3.31 |

| ZD        | _    | 3.31 |

#### Table 3.3. PCB Land Pattern

Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-782 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- **4.** A 1.45 x 1.45 mm square aperture should be used for the center pad. This provides approximately 70% solder paste coverage on the pad, which is optimum to assure correct component stand-off.

#### **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

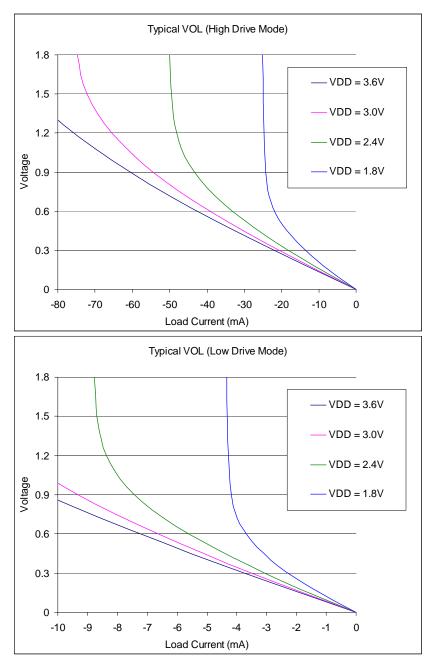

## 4.2. Electrical Characteristics

#### **Table 4.2. Global Electrical Characteristics**

-40 to +85 °C, 25 MHz system clock unless otherwise specified. See "AN358: Optimizing Low Power Operation of the 'F9xx" for details on how to achieve the supply current specifications listed in this table.

| Parameter                                                   | Conditions                                                                                                | Min      | Тур        | Max  | Units    |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------|------------|------|----------|

| Supply Voltage (V <sub>DD</sub> )                           |                                                                                                           | 1.8      | 2.4        | 3.6  | V        |

| Minimum RAM Data                                            | not in sleep mode                                                                                         | _        | 1.4        |      | V        |

| Retention Voltage <sup>1</sup>                              | in sleep mode                                                                                             | —        | 0.3        | 0.45 |          |

| SYSCLK (System Clock) <sup>2</sup>                          |                                                                                                           | 0        | _          | 25   | MHz      |

| T <sub>SYSH</sub> (SYSCLK High Time)                        |                                                                                                           | 18       | —          | _    | ns       |

| T <sub>SYSL</sub> (SYSCLK Low Time)                         |                                                                                                           | 18       | —          | _    | ns       |

| Specified Operating<br>Temperature Range                    |                                                                                                           | -40      | —          | +85  | °C       |

| Digital Supply Current—CP                                   | U Active (Normal Mode, fetching instruct                                                                  | tions fr | om Fla     | sh)  |          |

| I <sub>DD</sub> <sup>3, 4, 5</sup>                          | V <sub>DD</sub> = 1.8–3.6 V, F = 24.5 MHz<br>(includes precision oscillator current)                      |          | 3.6        | 4.5  | mA       |

|                                                             | V <sub>DD</sub> = 1.8–3.6 V, F = 20 MHz<br>(includes low power oscillator current)                        |          | 3.1        | _    | mA       |

|                                                             | $V_{DD}$ = 1.8 V, F = 1 MHz<br>$V_{DD}$ = 3.6 V, F = 1 MHz<br>(includes external oscillator/GPIO current) |          | 225<br>290 |      | μΑ<br>μΑ |

|                                                             | V <sub>DD</sub> = 1.8–3.6 V, F = 32.768 kHz<br>(includes SmaRTClock oscillator current)                   | _        | 84         | _    | μA       |

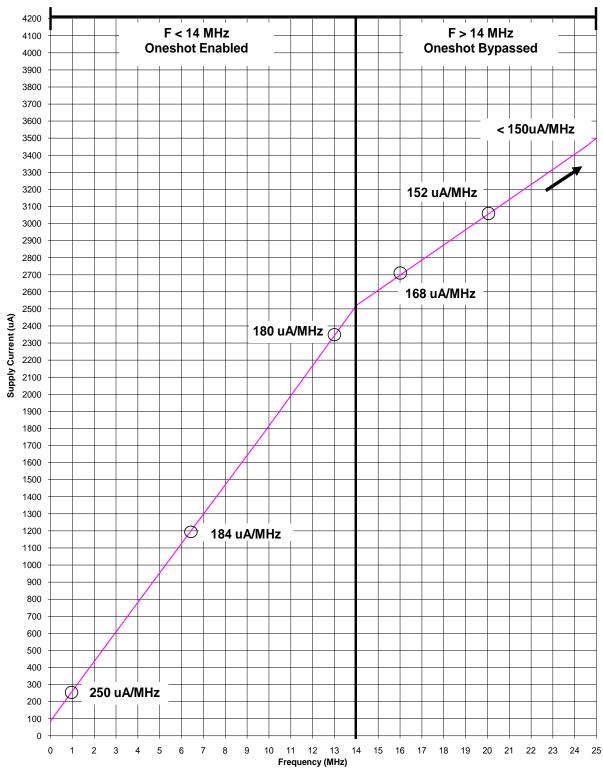

| I <sub>DD</sub> Frequency<br>Sensitivity <sup>1, 3, 5</sup> | $V_{DD}$ = 1.8–3.6 V, T = 25 °C, F < 14 MHz<br>(Flash oneshot active, see Section 14.6)                   | _        | 174        | —    | µA/MHz   |

|                                                             | V <sub>DD</sub> = 1.8–3.6 V, T = 25 °C, F > 14 MHz<br>(Flash oneshot bypassed, see Section<br>14.6)       |          | 88         |      | µA/MHz   |

Figure 4.1. Active Mode Current (External CMOS Clock)

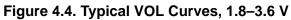

# 5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

The ADC0 on C8051F980/6 and C8051F990/6 devices is a 300 ksps, 10-bit or 75 ksps, 12-bit successiveapproximation-register (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically oversample and average the ADC results. See Section 5.4 for more details on using the ADC in 12-bit mode. C8051F982 and C8051F988 devices only support the 10-bit mode.

The ADC is fully configurable under software control via Special Function Registers. The ADC0 operates in Single-ended mode and may be configured to measure various different signals using the analog multiplexer described in "5.7. ADC0 Analog Multiplexer" on page 83. The voltage reference for the ADC is selected as described in "5.9. Voltage and Ground Reference Options" on page 88.

Figure 5.1. ADC0 Functional Block Diagram

# SFR Definition 6.2. IREF0CF: Current Reference Configuration

| Bit   | 7     | 6   | 5   | 4   | 3   | 2   | 1          | 0 |  |  |

|-------|-------|-----|-----|-----|-----|-----|------------|---|--|--|

| Name  | PWMEN |     |     |     |     |     | PWMSS[2:0] |   |  |  |

| Туре  | R/W   | R/W | R/W | R/W | R/W | R/W |            |   |  |  |

| Reset | 0     | 0   | 0   | 0   | 0   | 0   | 0          | 0 |  |  |

#### SFR Page = All; SFR Address = 0xB9

| Bit | Name       | Function                                                                                                                |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------|

| 7   | PWMEN      | PWM Enhanced Mode Enable.                                                                                               |

|     |            | Enables the PWM Enhanced Mode.                                                                                          |

|     |            | 0: PWM Enhanced Mode disabled.                                                                                          |

|     |            | 1: PWM Enhanced Mode enabled.                                                                                           |

| 6:3 | Unused     | Read = 0000b, Write = don't care.                                                                                       |

| 2:0 | PWMSS[2:0] | PWM Source Select.                                                                                                      |

|     |            | Selects the PCA channel to use for the fine-tuning control signal.<br>000: CEX0 selected as fine-tuning control signal. |

|     |            | 001: CEX1 selected as fine-tuning control signal.                                                                       |

|     |            | 010: CEX2 selected as fine-tuning control signal.                                                                       |

|     |            | All Other Values: Reserved.                                                                                             |

#### 6.2. IREF0 Specifications

See Table 4.13 on page 62 for a detailed listing of IREF0 specifications.

# SFR Definition 8.3. CS0DH: Capacitive Sense Data High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | CS0DH[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R          | R | R | R | R | R | R | R |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Page = 0x0; SFR Address = 0xEE

| Bit | Name  | Description                                                                    |

|-----|-------|--------------------------------------------------------------------------------|

| 7:0 | CS0DH | CS0 Data High Byte.                                                            |

|     |       | Stores the high byte of the last completed 16-bit Capacitive Sense conversion. |

## SFR Definition 8.4. CS0DL: Capacitive Sense Data Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | CS0DL[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R          | R | R | R | R | R | R | R |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Page = 0x0; SFR Address = 0xED

| Bit | Name  | Description                                                                   |

|-----|-------|-------------------------------------------------------------------------------|

| 7:0 | CS0DL | CS0 Data Low Byte.                                                            |

|     |       | Stores the low byte of the last completed 16-bit Capacitive Sense conversion. |

## Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register | Address | SFR Page | Description                           | Page |

|----------|---------|----------|---------------------------------------|------|

| CS0DH    | 0xEE    | 0x0      | CS0 Data High Byte                    | 109  |

| CS0DL    | 0xED    | 0x0      | CS0 Data Low Byte                     | 109  |

| CS0MD1   | 0xAF    | 0x0      | CS0 Mode1                             | 113  |

| CS0MD2   | 0xF3    | 0x0      | CS0 Mode 2                            | 114  |

| CS0MD3   | 0xF3    | 0xF      | CS0 Mode 3                            | 115  |

| CS0MX    | 0xAB    | 0x0      | CS0 Mux Channel Select                | 118  |

| CS0PM    | 0xDE    | 0xF      | CS0 Power Management                  | 116  |

| CS0SCAN0 | 0xD2    | 0x0      | CS0 Scan Channel Enable 0             | 110  |

| CS0SCAN1 | 0xD3    | 0x0      | CS0 Scan Channel Enable 1             | 110  |

| CS0SE    | 0xDE    | 0x0      | CS0 Auto-Scan End Channel             | 111  |

| CSOSS    | 0xDD    | 0x0      | CS0 Auto-Scan Start Channel           | 111  |

| CS0THH   | 0xFE    | 0x0      | CS0 Comparator Threshold High Byte    | 112  |

| CS0THL   | 0xFD    | 0x0      | CS0 Comparator Threshold Low Byte     | 112  |

| DEVICEID | 0xE3    | 0xF      | Device ID                             | 154  |

| DPH      | 0x83    | All      | Data Pointer High                     | 125  |

| DPL      | 0x82    | All      | Data Pointer Low                      | 125  |

| EIE1     | 0xE6    | All      | Extended Interrupt Enable 1           | 144  |

| EIE2     | 0xE7    | All      | Extended Interrupt Enable 2           | 146  |

| EIP1     | 0xF6    | All      | Extended Interrupt Priority 1         | 145  |

| EIP2     | 0xF7    | All      | Extended Interrupt Priority 2         | 147  |

| FLKEY    | 0xB7    | All      | Flash Lock And Key                    | 160  |

| FLSCL    | 0xB6    | 0x0      | Flash Scale Register                  | 161  |

| FLWR     | 0xE5    | All      | Flash Write Only Register             | 161  |

| IE       | 0xA8    | All      | Interrupt Enable                      | 142  |

| IP       | 0xB8    | All      | Interrupt Priority                    | 143  |

| IREF0CF  | 0xB9    | All      | Current Reference IREF0 Configuration | 92   |

| IREF0CN  | 0xD6    | 0x0      | Current Reference IREF0 Control       | 91   |

| IT01CF   | 0xE4    | 0x0      | INT0/INT1 Configuration               | 149  |

| OSCICL   | 0xB3    | 0x0      | Internal Oscillator Calibration       | 195  |

| OSCICN   | 0xB2    | 0x0      | Internal Oscillator Control           | 194  |

| OSCXCN   | 0xB1    | 0x0      | External Oscillator Control           | 196  |

| P0       | 0x80    | All      | Port 0 Latch                          | 228  |

| P0DRV    | 0x99    | 0xF      | Port 0 Drive Strength                 | 230  |

| POMASK   | 0xC7    | 0x0      | Port 0 Mask                           | 225  |

| POMAT    | 0xD7    | 0x0      | Port 0 Match                          | 225  |

| POMDIN   | 0xF1    | 0x0      | Port 0 Input Mode Configuration       | 229  |

| POMDOUT  | 0xA4    | 0x0      | Port 0 Output Mode Configuration      | 229  |

| P0SKIP   | 0xD4    | 0x0      | Port 0 Skip                           | 228  |

| P1       | 0x90    | All      | Port 1 Latch                          | 231  |

| P1DRV    | 0x9B    | 0xF      | Port 1 Drive Strength                 | 233  |

| P1MASK   | 0xBF    | 0x0      | Port 1 Mask                           | 226  |

| P1MAT    | 0xCF    | 0x0      | Port 1 Match                          | 226  |

| P1MDIN   | 0xF2    | 0x0      | Port 1 Input Mode Configuration       | 232  |

| P1MDOUT  | 0xA5    | 0x0      | Port 1 Output Mode Configuration      | 228  |

# SFR Definition 13.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Page = All; SFR Address = 0xA8; Bit-Addressable

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

# 14. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 4.6 for complete Flash memory electrical characteristics.

## 14.1. Programming the Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "27. C2 Interface" on page 319.

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before programming Flash memory using MOVX, Flash programming operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software. For detailed guidelines on programming Flash from firmware, please see Section "14.5. Flash Write and Erase Guidelines" on page 156.

To ensure the integrity of the Flash contents, the on-chip VDD Monitor must be enabled and enabled as a reset source in any system that includes code that writes and/or erases Flash memory from software. Furthermore, there should be no delay between enabling the  $V_{DD}$  Monitor and enabling the  $V_{DD}$  Monitor as a reset source. Any attempt to write or erase Flash memory while the  $V_{DD}$  Monitor is disabled, or not enabled as a reset source, will cause a Flash Error device reset.

#### 14.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 14.4.

# SFR Definition 14.5. FLSCL: Flash Scale

| Bit   | 7 | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|--------|---|---|---|---|---|---|

| Name  |   | BYPASS |   |   |   |   |   |   |

| Туре  | R | R/W    | R | R | R | R | R | R |

| Reset | 0 | 0      | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xB6

| Bit   | Name                                                                                                                                                                                                                                                                                                                                | Function                                                                                                                                                                                                                                                                  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7     | Reserved                                                                                                                                                                                                                                                                                                                            | Always Write to 0.                                                                                                                                                                                                                                                        |  |  |  |  |

| 6     | BYPASS                                                                                                                                                                                                                                                                                                                              | Flash Read Timing One-Shot Bypass.                                                                                                                                                                                                                                        |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                     | <ul> <li>0: The one-shot determines the Flash read time. This setting should be used for operating frequencies less than 14 MHz.</li> <li>1: The system clock determines the Flash read time. This setting should be used for frequencies greater than 14 MHz.</li> </ul> |  |  |  |  |

| 5:0   | Reserved                                                                                                                                                                                                                                                                                                                            | Reserved. Always Write to 000000b.                                                                                                                                                                                                                                        |  |  |  |  |

| Note: | Operations which clear the BYPASS bit do not need to be immediately followed by a benign 3-byte instruction.<br>For code compatibility with C8051F930/31/20/21 devices, a benign 3-byte instruction whose third byte is a<br>don't care should follow the clear operation. See the C8051F93x-C8051F92x data sheet for more details. |                                                                                                                                                                                                                                                                           |  |  |  |  |

## SFR Definition 14.6. FLWR: Flash Write Only

| Bit    | 7              | 6                                                               | 5    | 4 | 3 | 2 | 1 | 0 |

|--------|----------------|-----------------------------------------------------------------|------|---|---|---|---|---|

| Nam    | ame FLWR[7:0]  |                                                                 |      |   |   |   |   |   |

| Type W |                |                                                                 |      |   |   |   |   |   |

| Rese   | et 0           | 0                                                               | 0    | 0 | 0 | 0 | 0 | 0 |

| SFR F  | Page = All; SF | R Address = 0                                                   | )xE5 |   |   |   |   |   |

| Bit    | Name           | Function                                                        |      |   |   |   |   |   |

| 7:0    | FLWR[7:0]      | Flash Write Only.                                               |      |   |   |   |   |   |

|        |                | All writes to this register have no effect on system operation. |      |   |   |   |   |   |

# 17. Voltage Regulator (VREG0)

C8051F99x-C8051F98x devices include an internal voltage regulator (VREG0) to regulate the internal core supply to 1.8 V from a VDD supply of 1.8 to 3.6 V. Electrical characteristics for the on-chip regulator are specified in the Electrical Specifications chapter.

The REGOCN register allows the Precision Oscillator Bias to be disabled, reducing supply current in all non-Sleep power modes. This bias should only be disabled when the precision oscillator is not being used.

The internal regulator (VREG0) is disabled when the device enters Sleep Mode and remains enabled when the device enters Suspend Mode. See Section "15. Power Management" on page 162 for complete details about low power modes.

#### SFR Definition 17.1. REG0CN: Voltage Regulator Control

| Bit   | 7 | 6        | 5        | 4       | 3 | 2 | 1 | 0        |

|-------|---|----------|----------|---------|---|---|---|----------|

| Name  |   | Reserved | Reserved | OSCBIAS |   |   |   | Reserved |

| Туре  | R | R/W      | R/W      | R/W     | R | R | R | R/W      |

| Reset | 0 | 0        | 0        | 0       | 0 | 0 | 0 | 0        |

#### SFR Page = 0x0; SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused   | Read = 0b. Write = Don't care.                                                                                                                                                                            |

| 6:5 | Reserved | Read = 00b. Must Write 00b.                                                                                                                                                                               |

| 4   | OSCBIAS  | Precision Oscillator Bias.                                                                                                                                                                                |

|     |          | When set to 1, the bias used by the precision oscillator is forced on. If the precision oscillator is not being used, this bit may be cleared to 0 to reduce supply current in all non-Sleep power modes. |

| 3:1 | Unused   | Read = 000b. Write = Don't care.                                                                                                                                                                          |

| 0   | Reserved | Read = 0b. Must Write 0b.                                                                                                                                                                                 |

#### 17.1. Voltage Regulator Electrical Specifications

See Table 4.15 on page 64 for detailed Voltage Regulator Electrical Specifications.

#### 20.1.2. Using RTC0ADR and RTC0DAT to Access SmaRTClock Internal Registers

The SmaRTClock internal registers can be read and written using RTC0ADR and RTC0DAT. The RTC0ADR register selects the SmaRTClock internal register that will be targeted by subsequent reads or writes. Recommended instruction timing is provided in this section. If the recommended instruction timing is not followed, then BUSY (RTC0ADR.7) should be checked prior to each read or write operation to make sure the SmaRTClock Interface is not busy performing the previous read or write operation. A SmaRTClock Write operation is initiated by writing to the RTC0DAT register. Below is an example of writing to a SmaRTClock internal register.

- 1. Poll BUSY (RTC0ADR.7) until it returns 0 or follow recommended instruction timing.

- 2. Write 0x05 to RTC0ADR. This selects the internal RTC0CN register at SmaRTClock Address 0x05.

- 3. Write 0x00 to RTC0DAT. This operation writes 0x00 to the internal RTC0CN register.

A SmaRTClock Read operation is initiated by setting the SmaRTClock Interface Busy bit. This transfers the contents of the internal register selected by RTC0ADR to RTC0DAT. The transferred data will remain in RTC0DAT until the next read or write operation. Below is an example of reading a SmaRTClock internal register.

- 1. Poll BUSY (RTC0ADR.7) until it returns 0 or follow recommended instruction timing.

- 2. Write 0x05 to RTC0ADR. This selects the internal RTC0CN register at SmaRTClock Address 0x05.

- 3. Write 1 to BUSY. This initiates the transfer of data from RTC0CN to RTC0DAT.

- 4. Poll BUSY (RTC0ADR.7) until it returns 0 or follow recommend instruction timing.

- 5. Read data from RTC0DAT. This data is a copy of the RTC0CN register.

Note: The RTC0ADR and RTC0DAT registers will retain their state upon a device reset.

#### 20.1.3. RTC0ADR Short Strobe Feature

Reads and writes to indirect SmaRTClock registers normally take 7 system clock cycles. To minimize the indirect register access time, the Short Strobe feature decreases the read and write access time to 6 system clocks. The Short Strobe feature is automatically enabled on reset and can be manually enabled/disabled using the SHORT (RTC0ADR.4) control bit.

Recommended Instruction Timing for a single register read with short strobe enabled:

```

mov RTC0ADR, #095h

nop

nop

mov A, RTC0DAT

```

Recommended Instruction Timing for a single register write with short strobe enabled:

mov RTC0ADR, #095h

mov RTC0DAT, #000h

nop

#### 20.1.4. SmaRTClock Interface Autoread Feature

When Autoread is enabled, each read from RTC0DAT initiates the next indirect read operation on the SmaRTClock internal register selected by RTC0ADR. Software should set the BUSY bit once at the beginning of each series of consecutive reads. Software should follow recommended instruction timing or check if the SmaRTClock Interface is busy prior to reading RTC0DAT. Autoread is enabled by setting AUTORD (RTC0ADR.6) to logic 1.

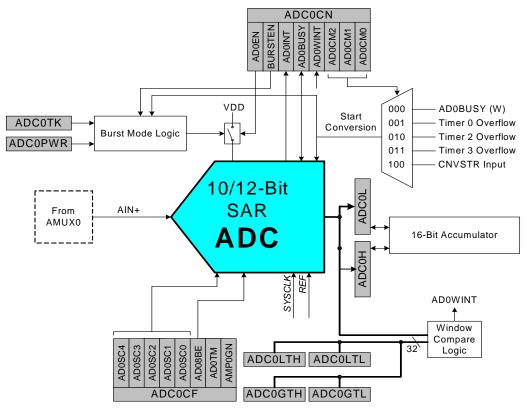

#### 25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see Section "13.6. External Interrupts INT0 and INT1" on page 148 for details on the external input signals INT0 and INT1).

Figure 25.2. T0 Mode 2 Block Diagram

#### 25.3.2. 8-Bit Timers with Auto-Reload

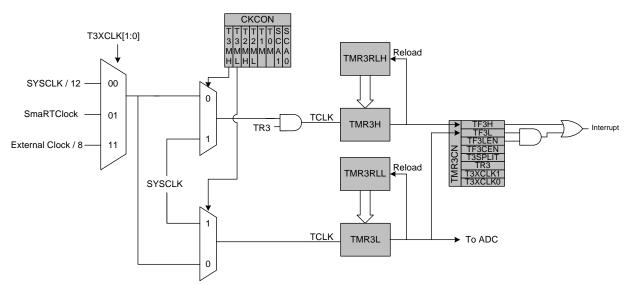

When T3SPLIT is set, Timer 3 operates as two 8-bit timers (TMR3H and TMR3L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.8. TMR3RLL holds the reload value for TMR3L; TMR3RLH holds the reload value for TMR3H. The TR3 bit in TMR3CN handles the run control for TMR3H. TMR3L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, the external oscillator clock source divided by 8, or the SmaRTClock. The Timer 3 Clock Select bits (T3MH and T3ML in CKCON) select either SYSCLK or the clock defined by the Timer 3 External Clock Select bits (T3XCLK[1:0] in TMR3CN), as follows:

| ТЗМН | T3XCLK[1:0] | TMR3H Clock<br>Source |

|------|-------------|-----------------------|

| 0    | 00          | SYSCLK / 12           |

| 0    | 01          | SmaRTClock            |

| 0    | 10          | Reserved              |

| 0    | 11          | External Clock / 8    |

| 1    | Х           | SYSCLK                |

| T3ML | T3XCLK[1:0] | TMR3L Clock<br>Source |

|------|-------------|-----------------------|

| 0    | 00          | SYSCLK / 12           |

| 0    | 01          | SmaRTClock            |

| 0    | 10          | Reserved              |

| 0    | 11          | External Clock / 8    |

| 1    | Х           | SYSCLK                |

The TF3H bit is set when TMR3H overflows from 0xFF to 0x00; the TF3L bit is set when TMR3L overflows from 0xFF to 0x00. When Timer 3 interrupts are enabled, an interrupt is generated each time TMR3H overflows. If Timer 3 interrupts are enabled and TF3LEN (TMR3CN.5) is set, an interrupt is generated each time either TMR3L or TMR3H overflows. When TF3LEN is enabled, software must check the TF3H and TF3L flags to determine the source of the Timer 3 interrupt. The TF3H and TF3L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.8. Timer 3 8-Bit Mode Block Diagram

# SFR Definition 25.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1     | 0       |

|-------|------|------|--------|--------|---------|-----|-------|---------|

| Name  | TF3H | TF3L | TF3LEN | TF3CEN | T3SPLIT | TR3 | T3XCI | _K[1:0] |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R/W   |         |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0     | 0       |

#### SFR Page = 0x0; SFR Address = 0x91

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF3H        | Timer 3 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |             | Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6   | TF3L        | Timer 3 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |             | Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5   | TF3LEN      | Timer 3 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |             | When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | TF3CEN      | Timer 3 SmaRTClock/External Oscillator Capture Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |             | When set to 1, this bit enables Timer 3 Capture Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | T3SPLIT     | Timer 3 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |             | When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |             | 0: Timer 3 operates in 16-bit auto-reload mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |             | 1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2   | TR3         | Timer 3 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |             | Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1:0 | T3XCLK[1:0] | Timer 3 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |             | This bit selects the "external" and "capture trigger" clock sources for Timer 3. If<br>Timer 3 is in 8-bit mode, this bit selects the "external" clock source for both timer<br>bytes. Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be<br>used to select between the "external" clock and the system clock for either timer.<br>Note: External clock sources are synchronized with the system clock.<br>00: External Clock is SYSCLK /12. Capture trigger is SmaRTClock.<br>01: External Clock is External Oscillator/8. Capture trigger is SmaRTClock.<br>10: External Clock is SYSCLK/12. Capture trigger is External Oscillator/8.<br>11: External Clock is SmaRTClock. Capture trigger is External Oscillator/8. |

# 27. C2 Interface

C8051F99x-C8051F98x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

#### 27.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

#### C2 Register Definition 27.1. C2ADD: C2 Address

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | C2ADD[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | Name       |                                                                                                                                                        | Function                                                                           |  |  |  |  |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0 | C2ADD[7:0] | <b>C2 Address.</b><br>The C2ADD register is accessed via the C2 interface to select the target Data register for C2 Data Read and Data Write commands. |                                                                                    |  |  |  |  |  |

|     |            |                                                                                                                                                        |                                                                                    |  |  |  |  |  |

|     |            | Address Description                                                                                                                                    |                                                                                    |  |  |  |  |  |

|     |            | 0x00                                                                                                                                                   | Selects the Device ID register for Data Read instructions                          |  |  |  |  |  |

|     |            | 0x01                                                                                                                                                   | Selects the Revision ID register for Data Read instructions                        |  |  |  |  |  |

|     |            | 0x02                                                                                                                                                   | Selects the C2 Flash Programming Control register for Data Read/Write instructions |  |  |  |  |  |

|     |            | 0xB4                                                                                                                                                   | Selects the C2 Flash Programming Data register for Data Read/Write instructions    |  |  |  |  |  |