Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                     |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                           |

| Number of I/O              | 16                                                              |

| Program Memory Size        | 2KB (2K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 20-UFQFN Exposed Pad                                            |

| Supplier Device Package    | 20-QFN (3x3)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f985-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

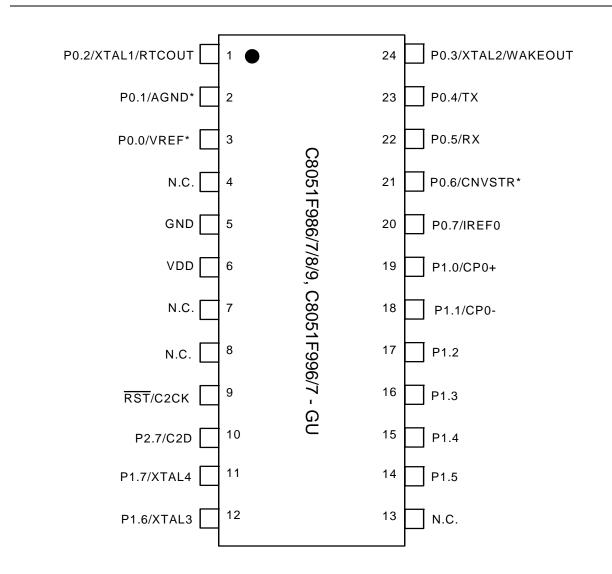

\*Note: Signal only available on 'F986, 'F988, and 'F996 devices.

#### Figure 3.3. QSOP-24 Pinout Diagram (Top View)

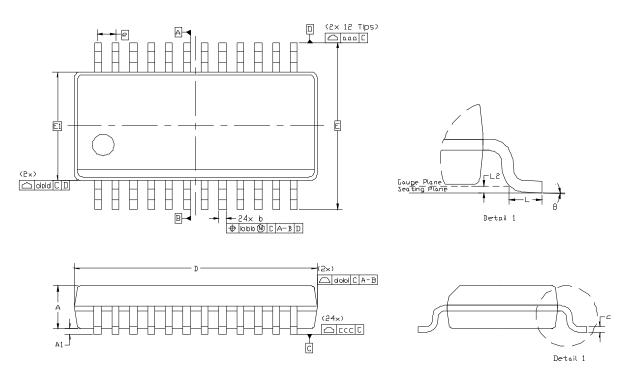

Figure 3.11. QSOP-24 Package Diagram

| Table | 3.6. | QSOP-24 | Package  | Dimensions |

|-------|------|---------|----------|------------|

| Table | 5.0. |         | I denage | Dimensions |

| Dimension | Min       | Тур       | Max  | Dimension | Min      | Тур  | Мах  |

|-----------|-----------|-----------|------|-----------|----------|------|------|

| A         | _         | —         | 1.75 | L         | 0.40     | —    | 1.27 |

| A1        | 0.10      | —         | 0.25 | L2        | 0.25 BSC |      |      |

| b         | 0.20      | —         | 0.30 | θ         | 0°       | —    | 8°   |

| С         | 0.10      | —         | 0.25 | aaa       | 0.20     |      |      |

| D         |           | 8.65 BSC. |      | bbb       |          | 0.18 |      |

| E         |           | 6.00 BSC  |      | CCC       |          | 0.10 |      |

| E1        | 3.90 BSC  |           |      | ddd       |          | 0.10 |      |

| е         | 0.635 BSC |           |      |           |          |      |      |

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MO-147, variation AE.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 8.4. CS0 Multiple Channel Enable

CS0 has the capability of measuring the total capacitance of multiple channels using a single conversion. When the multiple channel feature is enabled (CS0MCEN = 1), Channels selected by CS0SCAN0/1 are internally shorted together and the combined node is selected as the CS0 input. This mode can be used to detect a capacitance change on multiple channels using a single conversion and is useful for implementing "wake-on-multiple channels".

#### 8.5. CS0 Gain Adjustment

The gain of the CS0 circuit can be adjusted in integer increments from 1x to 8x (8x is the default). High gain gives the best sensitivity and resolution for small capacitors, such as those typically implemented as touch-sensitive PCB features. To measure larger capacitance values, the gain should be lowered accordingly. The bits CS0CG[2:0] in register CS0MD set the gain value.

#### 8.6. Wake from Suspend

CS0 has the capability of waking the device from a low power suspend mode upon detection of a "touch" using the digital comparator. When the CS0SMEN is set to 1, CS0 may also wake up the device after an end of scan event when CS0CM[2:0] are set to 101b or after each conversion when CS0CM[2:0] are set to 110b or 111b. If the accumulate feature is enabled, the device wakes up after all samples have been accumulated. The CS0WOI bit in the CS0MD1 register can be used to configure desire wake from suspend behavior.

#### 8.7. Using CS0 in Applications that Utilize Sleep Mode

To achieve maximum power efficiency, CS0 should be enabled only when taking a conversion and disabled at all other times. CS0 must be disabled by software prior to entering Sleep Mode.

102

## SFR Definition 8.13. CS0MD3: Capacitive Sense Mode 3

| 7             | 6                                                       | 5                                                                                                                                     | 4                                                                                                                                                                                                                                                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                         |  |  |

|---------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               |                                                         |                                                                                                                                       | CS0R                                                                                                                                                                                                                                                                  | P[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                            | CS0LP[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                           |  |  |

| R/W           | R/W                                                     | R/W                                                                                                                                   | R/W                                                                                                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W R/W I                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W                                                                                                                                                                                       |  |  |

| 0             | 0                                                       | 0                                                                                                                                     | 0                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                         |  |  |

| ige = 0xF; SF | R Address :                                             | = 0xF3                                                                                                                                |                                                                                                                                                                                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                            | II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                           |  |  |

| Name          |                                                         | Description                                                                                                                           |                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                           |  |  |

| Unused        | Read = 0                                                | 000b; Write =                                                                                                                         | Don't care                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                           |  |  |

| CS0RP[1:0]    | These bi<br>ramp tim<br>cient. Se<br>00: Ram<br>01: Ram | ts are used t<br>es. For most<br>e the discus<br>p time is less<br>p time is bet                                                      | o compensa<br>touch-sens<br>sion in Secti<br>s than 1.5 μs<br>ween 1.5 μs                                                                                                                                                                                             | itive switches<br>on 8.13 for n<br>s.<br>and 3 μs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | s, the defaul                                                                                                                                                                                                                                                                                              | t (fastest) va                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                                                                                                                                                                         |  |  |

|               | R/W<br>0<br>age = 0xF; SF<br>Name<br>Unused             | R/W R/W   0 0   age = 0xF; SFR Address = Name   Unused Read = 0   CS0RP[1:0] CS0 Ran   These bir ramp tim cient. Se 00: Ram   01: Ram | R/W   R/W   R/W     0   0   0     age = 0xF; SFR Address = 0xF3   Name     Unused   Read = 000b; Write =     CS0RP[1:0]   CS0 Ramp Selection     These bits are used tramp times. For most cient. See the discuss     00: Ramp time is less     01: Ramp time is betw | R/W   R/W   R/W   R/W     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   0   0   0     0   Read = 000b; Write = Don't care   CSORP[1:0]     CSORP[1:0]   CSO Ramp Selection.     These bits are used to compensar   ramp times. For most touch-sens     cient. See the discussion in Secti   00: Ramp time is less than 1.5 µs     01: Ramp time is between 1.5 µs   01: Ramp time is between 1.5 µs | R/W   R/W   R/W   R/W   R/W     0   0   0   0   0     age = 0xF; SFR Address = 0xF3   Mame   Description     Unused   Read = 000b; Write = Don't care   CS0RP[1:0]     CS0RP[1:0]   CS0 Ramp Selection.   These bits are used to compensate CS0 conversation ramp times. For most touch-sensitive switches | R/W   R/W   R/W   R/W   R/W   R/W     0   0   0   0   0   0     0   0   0   0   0   0   0     0   0   0   0   0   0   0     0   0   0   0   0   0   0     0   0   0   0   0   0   0     0   0   0   0   0   0   0     0   0   0   0   0   0   0     0   0   0   0   0   0   0     0   0   0   0   0   0   0     0   Read = 000b; Write = Don't care   Description   These bits are used to compensate CS0 conversions for or ramp times. For most touch-sensitive switches, the defaul cient. See the discussion in Section 8.13 for more informat 00: Ramp time is less than 1.5 µs.   01: Ramp time is between 1.5 µs and 3 µs. | R/WR/WR/WR/WR/WR/W00000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000 |  |  |

|     |            | 10: Ramp time is between 3 μs and 6 μs.                                                                                                                                                                                                                                                                                                                                                             |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |            | 11: Ramp time is greater than 6 μs.                                                                                                                                                                                                                                                                                                                                                                 |

| 2:0 | CS0LP[2:0] | <b>CS0 Low Pass Filter Selection.</b><br>These bits set the internal corner frequency of the CS0 low-pass filter. Higher values of CS0LP result in a lower internal corner frequency.                                                                                                                                                                                                               |

|     |            | For most touch-sensitive switches, the default setting of 000b should be used. If<br>the CS0RP bits are adjusted from their default value, the CS0LP bits should nor-<br>mally be set to 001b. Settings higher than 001b will result in attenuated readings<br>from the CS0 module and should be used only under special circumstances. See<br>the discussion in Section 8.13 for more information. |

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |

| JC rel               | Jump if Carry is set                                | 2     | 2/3             |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/3             |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/4             |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/4             |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3     | 3/4             |

|                      | Program Branching                                   | ·     |                 |

| ACALL addr11         | Absolute subroutine call                            | 2     | 3               |

| LCALL addr16         | Long subroutine call                                | 3     | 4               |

| RET                  | Return from subroutine                              | 1     | 5               |

| RETI                 | Return from interrupt                               | 1     | 5               |

| AJMP addr11          | Absolute jump                                       | 2     | 3               |

| LJMP addr16          | Long jump                                           | 3     | 4               |

| SJMP rel             | Short jump (relative address)                       | 2     | 3               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 3               |

| JZ rel               | Jump if A equals zero                               | 2     | 2/3             |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 3/4             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/4             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/3             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/4             |

| NOP                  | No operation                                        | 1     | 1               |

# Table 9.1. CIP-51 Instruction Set Summary (Continued)

#### Notes on Registers, Operands and Addressing Modes:

**Rn**—Register R0–R7 of the currently selected register bank.

@Ri—Data RAM location addressed indirectly through R0 or R1.

**rel**—8-bit, signed (twos complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct**—8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data—8-bit constant

#data16—16-bit constant

**bit**—Direct-accessed bit in Data RAM or SFR

**addr11**—11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16**—16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

| Interrupt Source                | t Source Interrupt Vector Order Priority |     | Pending Flag                                                               | Bit<br>addressable? | Cleared<br>by HW? | Enable Flag        | Priority<br>Control |

|---------------------------------|------------------------------------------|-----|----------------------------------------------------------------------------|---------------------|-------------------|--------------------|---------------------|

| Reset                           | 0x0000                                   | Тор | None                                                                       | N/A                 | N/A               | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0 (INT0)     | 0x0003                                   | 0   | IE0 (TCON.1)                                                               | Y                   | Y                 | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow                | 0x000B                                   | 1   | TF0 (TCON.5)                                                               | Y                   | Y                 | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1 (INT1)     | 0x0013                                   | 2   | IE1 (TCON.3)                                                               | Y                   | Y                 | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow                | 0x001B                                   | 3   | TF1 (TCON.7)                                                               | Y                   | Y                 | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                           | 0x0023                                   | 4   | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                   | Ν                 | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow                | 0x002B                                   | 5   | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                   | N                 | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                            | 0x0033                                   | 6   | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                   | N                 | ESPI0 (IE.6)       | PSPI0 (IP.6)        |

| SMB0                            | 0x003B                                   | 7   | SI (SMB0CN.0)                                                              | Y                   | Ν                 | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| SmaRTClock Alarm                | 0x0043                                   | 8   | ALRM (RTC0CN.2) <sup>2</sup>                                               | Ν                   | Ν                 | EARTC0<br>(EIE1.1) | PARTC0<br>(EIP1.1)  |

| ADC0 Window Comparator          | 0x004B                                   | 9   | AD0WINT (ADC0CN.3)                                                         | Y                   | Ν                 | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| ADC0 End of Conversion          | 0x0053                                   | 10  | AD0INT (ADC0CN.5)                                                          | Υ                   | Ν                 | EADC0<br>(EIE1.3)  | PADC0<br>(EIP1.3)   |

| Programmable Counter<br>Array   | 0x005B                                   | 11  | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                           | Υ                   | Ν                 | EPCA0<br>(EIE1.4)  | PPCA0<br>(EIP1.4)   |

| Comparator0                     | 0x0063                                   | 12  | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | Ν                   | Ν                 | ECP0<br>(EIE1.5)   | PCP0<br>(EIP1.5)    |

| Reserved                        | 0x006B                                   | 13  |                                                                            |                     |                   |                    |                     |

| Timer 3 Overflow                | 0x0073                                   | 14  | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | Ν                   | Ν                 | ET3<br>(EIE1.7)    | PT3<br>(EIP1.7)     |

| Supply Monitor Early<br>Warning | 0x007B                                   | 15  | VDDOK (VDM0CN.5) <sup>1</sup>                                              | Ν                   | Ν                 | EWARN<br>(EIE2.0)  | PWARN<br>(EIP2.0)   |

| Port Match                      | 0x0083                                   | 16  | None                                                                       |                     |                   | EMAT<br>(EIE2.1)   | PMAT<br>(EIP2.1)    |

| SmaRTClock Oscillator Fail      | 0x008B                                   | 17  | OSCFAIL (RTC0CN.5) <sup>2</sup>                                            | Ν                   | Ν                 | ERTC0F<br>(EIE2.2) | PFRTC0F<br>(EIP2.2) |

| Reserved                        | 0x0093                                   | 18  |                                                                            |                     |                   |                    |                     |

| CS0 Conversion Complete         | 0x009B                                   | 19  | CS0INT (CS0CN.5)                                                           | Y                   | Ν                 | ECSCPT<br>(EIE2.4) | PCSCPT<br>(EIP2.4)  |

| CS0 Digital Comparator          | 0x00A3                                   | 20  | CS0CMPF (CS0CN.0)                                                          | Y                   | N                 | ECSDC<br>(EIE2.5)  | PCSDC<br>(EIP2.5)   |

| CS0 End of Scan                 | 0x00AB                                   | 21  | CS0EOS (CS0CN.6)                                                           | Y                   | Ν                 | ECSEOS<br>(EIE2.6) | PCSEOS<br>(EIP2.6)  |

Table 13.1. Interrupt Summary

Notes:

1. Indicates a read-only interrupt pending flag. The interrupt enable may be used to prevent software from vectoring to the associated interrupt service routine.

2. Indicates a register located in an indirect memory space.

### 13.5. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described in the following register descriptions. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

### 15.7. Determining the Event that Caused the Last Wakeup

When waking from idle mode, the CPU will vector to the interrupt which caused it to wake up. When waking from stop mode, the RSTSRC register may be read to determine the cause of the last reset.

Upon exit from suspend or sleep mode, the wake-up flags in the PMU0CF and PMU0FL registers can be read to determine the event which caused the device to wake up. After waking up, the wake-up flags will continue to be updated if any of the wake-up events occur. Wake-up flags are always updated, even if they are not enabled as wake-up sources.

All wake-up flags enabled as wake-up sources in PMU0CF and PMU0FL must be cleared before the device can enter suspend or sleep mode. After clearing the wake-up flags, each of the enabled wake-up events should be checked in the individual peripherals to ensure that a wake-up event did not occur while the wake-up flags were being cleared.

Notes:

#### SFR Definition 16.5. CRC0CNT: CRC0 Automatic Flash Sector Count

| Bit   | 7               | 6         | 5                                     | 4            | 3 | 2 | 1 | 0 |  |

|-------|-----------------|-----------|---------------------------------------|--------------|---|---|---|---|--|

| Nam   | e               |           |                                       | CRC0CNT[4:0] |   |   |   |   |  |

| Туре  | e R             | R         | R                                     | R/W          |   |   |   |   |  |

| Rese  | et 0            | 0         | 0                                     | 0 0 0 0 0    |   |   |   |   |  |

| SFR F | Page = All; SFR | Address = | 0x9A                                  |              |   |   |   |   |  |

| Bit   | Name            |           | Function                              |              |   |   |   |   |  |

| 7:5   | Unused          | Read = 0  | Read = 000b; Write = Don't Care.      |              |   |   |   |   |  |

| 4:0   | CRC0CNT[4:0]    | Automa    | utomatic CRC Calculation Block Count. |              |   |   |   |   |  |

calculation is (CRC0ST+CRC0CNT) x Block Size - 1.

1. The block size is 256 bytes.

These bits specify the number of Flash blocks to include in an automatic CRC calculation. The last address of the last Flash block included in the automatic CRC

2. The maximum number of blocks that may be computed in a single operation is 31. To compute a CRC on all 32 blocks, perform one operation on 31 blocks, then perform a second operation on 1 block without clearing the CRC result.

| S       | Y    |

|---------|------|

| SILICON | LABS |

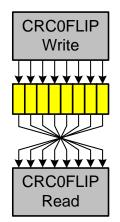

#### 16.5. CRC0 Bit Reverse Feature

CRC0 includes hardware to reverse the bit order of each bit in a byte as shown in Figure 16.2. Each byte of data written to CRC0FLIP is read back bit reversed. For example, if 0xC0 is written to CRC0FLIP, the data read back is 0x03. Bit reversal is a useful mathematical function used in algorithms such as the FFT.

Figure 16.2. Bit Reverse Register

### SFR Definition 16.6. CRC0FLIP: CRC0 Bit Flip

| Bit   | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---------------|---|---|---|---|---|---|---|--|--|

| Name  | CRC0FLIP[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W           |   |   |   |   |   |   |   |  |  |

| Reset | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

#### SFR Page = All; SFR Address = 0x9C

| Bit | Name          | Function                                                                                                                                                                                  |

|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC0FLIP[7:0] | CRC0 Bit Flip.                                                                                                                                                                            |

|     |               | Any byte written to CRC0FLIP is read back in a bit-reversed order, i.e. the written LSB becomes the MSB. For example:<br>If 0xC0 is written to CRC0FLIP, the data read back will be 0x03. |

|     |               | If 0x05 is written to CRC0FLIP, the data read back will be 0xA0.                                                                                                                          |

### 18.4. Missing Clock Detector Reset

The missing clock detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The missing clock detector reset is automatically disabled when the device is in the low power suspend or sleep mode. Upon exit from either low power state, the enabled/disabled state of this reset source is restored to its previous value. The state of the RST pin is unaffected by this reset.

### 18.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The Comparator0 reset source remains functional even when the device is in the low power <u>susp</u>end and sleep states as long as Comparator0 is also enabled as a wake-up source. The state of the RST pin is unaffected by this reset.

#### 18.6. PCA Watchdog Timer Reset

The programmable watchdog timer (WDT) function of the programmable counter array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "26.4. Watchdog Timer Mode" on page 311; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The PCA Watchdog Timer reset source is automatically disabled when the device is in the low power suspend or sleep mode. Upon exit from either low power state, the enabled/disabled state of this reset source is restored to its previous value. The state of the RST pin is unaffected by this reset.

#### 18.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above the Lock Byte address.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above the Lock Byte address.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above the Lock Byte address.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "14.3. Security Options" on page 152).

- A Flash write or erase is attempted while the V<sub>DD</sub> Monitor is disabled.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

### SFR Definition 21.6. P1MASK: Port1 Mask Register

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-------------|---|---|---|---|---|---|---|--|--|

| Name  | P1MASK[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W         |   |   |   |   |   |   |   |  |  |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Page= 0x0; SFR Address = 0xBF

| Bit | Name        | Function                                                                                                                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MASK[7:0] | Port 1 Mask Value.                                                                                                                                                                                  |

|     |             | Selects P1 pins to be compared to the corresponding bits in P1MAT.<br>0: P1.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P1.n pin logic value is compared to P1MAT.n. |

# SFR Definition 21.7. P1MAT: Port1 Match Register

| Bit   | 7          | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|----|---|---|---|---|--|--|

| Name  | P1MAT[7:0] |   |   |    |   |   |   |   |  |  |

| Туре  |            |   |   | R/ | W |   |   |   |  |  |

| Reset | 1          | 1 | 1 | 1  | 1 | 1 | 1 | 1 |  |  |

SFR Page = 0x0; SFR Address = 0xCF

| Bit | Name       | Function                                                                                                                                                                                    |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MAT[7:0] | Port 1 Match Value.                                                                                                                                                                         |

|     |            | Match comparison value used on Port 1 for bits in P1MASK which are set to 1.<br>0: P1.n pin logic value is compared with logic LOW.<br>1: P1.n pin logic value is compared with logic HIGH. |

## SFR Definition 21.19. P2MDOUT: Port2 Output Mode

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P2MDOUT |   |   |   |   |   |   |   |

| Туре  | R/W     | R | R | R | R | R | R | R |

| Reset | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xA6

| Bit | Name    | Function                                                                                                |

|-----|---------|---------------------------------------------------------------------------------------------------------|

| 7   | P2MDOUT | Output Configuration Bits for P2.7.                                                                     |

|     |         | These bits control the digital driver.<br>0: P2.7 Output is open-drain.<br>1: P2.7 Output is push-pull. |

| 6:0 | Unused  | Read = 0000000b; Write = Don't Care.                                                                    |

## SFR Definition 21.20. P2DRV: Port2 Drive Strength

| Bit   | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------|---|---|---|---|---|---|---|

| Name  | P2DRV |   |   |   |   |   |   |   |

| Туре  | R/W   | R | R | R | R | R | R | R |

| Reset | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Page = 0xF; SFR Address = 0x9D

| Bit | Name   | Function                                                                                                                                                                   |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | P2DRV  | Drive Strength Configuration Bits for P2.7.                                                                                                                                |

|     |        | Configures digital I/O Port cells to high or low output drive strength.<br>0: P2.7 Output has low output drive strength.<br>1: P2.7 Output has high output drive strength. |

| 6:0 | Unused | Read = 0000000b; Write = Don't Care.                                                                                                                                       |

# SFR Definition 22.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7     | 6   | 5    | 4       | 3      | 2      | 1          | 0 |

|-------|-------|-----|------|---------|--------|--------|------------|---|

| Name  | ENSMB | INH | BUSY | EXTHOLD | SMBTOE | SMBFTE | SMBCS[1:0] |   |

| Туре  | R/W   | R/W | R    | R/W     | R/W    | R/W    | R/W        |   |

| Reset | 0     | 0   | 0    | 0       | 0      | 0      | 0          | 0 |

#### SFR Page = 0x0; SFR Address = 0xC1

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENSMB      | SMBus Enable.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit enables the SMBus interface when set to 1. When enabled, the interface constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                                                                                                             |

| 6   | INH        | SMBus Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the SMBus does not generate an interrupt when slave events occur. This effectively removes the SMBus slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                    |

| 5   | BUSY       | SMBus Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                |

| 4   | EXTHOLD    | SMBus Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | This bit controls the SDA setup and hold times according to Table 22.2.<br>0: SDA Extended Setup and Hold Times disabled.<br>1: SDA Extended Setup and Hold Times enabled.                                                                                                                                                                                                                                                            |

| 3   | SMBTOE     | SMBus SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | This bit enables SCL low timeout detection. If set to logic 1, the SMBus forces<br>Timer 3 to reload while SCL is high and allows Timer 3 to count when SCL goes low.<br>If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in reload<br>while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms,<br>and the Timer 3 interrupt service routine should reset SMBus communication. |

| 2   | SMBFTE     | SMBus Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                              |

| 1:0 | SMBCS[1:0] | SMBus Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | These two bits select the SMBus clock source, which is used to generate the SMBus<br>bit rate. The selected device should be configured according to Equation 22.1.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10:Timer 2 High Byte Overflow                                                                                                                                                                                  |

|     |            | 11: Timer 2 Low Byte Overflow                                                                                                                                                                                                                                                                                                                                                                                                         |

#### 22.4.4. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

#### SFR Definition 22.5. SMB0DAT: SMBus Data

| Bit   | 7            | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|--------------|---|---|----|---|---|---|---|--|--|

| Name  | SMB0DAT[7:0] |   |   |    |   |   |   |   |  |  |

| Туре  |              |   |   | R/ | W |   |   |   |  |  |

| Reset | 0            | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

#### SFR Page = 0x0; SFR Address = 0xC2

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SMB0DAT[7:0] | SMBus Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | The SMB0DAT register contains a byte of data to be transmitted on the SMBus serial interface or a byte that has just been received on the SMBus serial interface. The CPU can read from or write to this register whenever the SI serial interrupt flag (SMB0CN.0) is set to logic 1. The serial data in the register remains stable as long as the SI flag is set. When the SI flag is not set, the system may be in the process of shifting data in/out and the CPU should not attempt to access this register. |

## SFR Definition 24.3. SPI0CKR: SPI0 Clock Rate

| Bit           | 7 6 5 4 3 2 1 |                                                                                                      |                                             |                                                                                        |                                               |                                               |                                                                   |                           |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------|---------------------------|--|

| Name SCR[7:0] |               |                                                                                                      |                                             |                                                                                        |                                               |                                               |                                                                   |                           |  |

| Туре          | e R/W         |                                                                                                      |                                             |                                                                                        |                                               |                                               |                                                                   |                           |  |

| Reset         | 0             | 0                                                                                                    | 0                                           | 0                                                                                      | 0                                             |                                               |                                                                   |                           |  |

| SFR Pa        | ge = 0x0; SF  | R Address =                                                                                          | = 0xA2                                      |                                                                                        | 1                                             |                                               | I                                                                 | I                         |  |

| Bit           | Name          |                                                                                                      |                                             |                                                                                        |                                               |                                               |                                                                   |                           |  |

| 7:0           | SCR[7:0]      | configured<br>sion of the<br>the system<br>register.<br>f <sub>SCK</sub> =<br>for 0 <= S<br>Example: | s determine<br>d for master<br>e system clo | mode opera<br>ck, and is gi<br>Jency and S<br>SCLK<br>CKR[7:0] +<br>255<br>= 2 MHz and | tion. The Solven in the formula $PIOCKR$ is t | CK clock fre<br>ollowing equ<br>he 8-bit valu | en the SPI0 of<br>quency is a c<br>ation, where<br>ue held in the | livided ver-<br>SYSCLK is |  |

## SFR Definition 24.4. SPI0DAT: SPI0 Data

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | SPI0DAT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xA3

| Bit | Name         | Function                                                                                                                                                                                                                                     |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0DAT[7:0] | SPI0 Transmit and Receive Data.                                                                                                                                                                                                              |

|     |              | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer. |

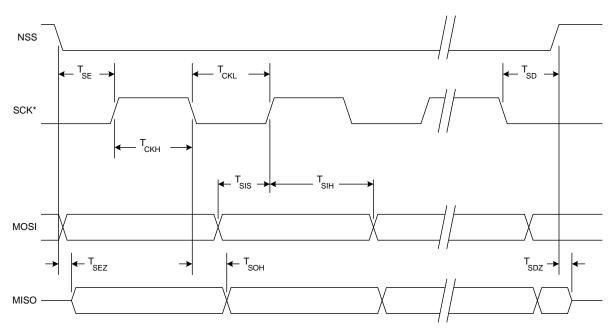

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

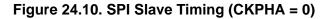

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

## SFR Definition 25.2. TCON: Timer Control

| Bit                                          | 7                                                   | 6                                                                                                                                                                                                                                                                | 5           | 4   | 3   | 2   | 1   | 0   |  |  |

|----------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|-----|-----|-----|-----|--|--|

|                                              |                                                     | TR1                                                                                                                                                                                                                                                              | TF0         | TR0 | IE1 | IT1 | IE0 | ITO |  |  |

| Name                                         | ·                                                   |                                                                                                                                                                                                                                                                  |             |     |     |     |     |     |  |  |

| Туре                                         | R/W                                                 | R/W                                                                                                                                                                                                                                                              | R/W         | R/W | R/W | R/W | R/W | R/W |  |  |

| Rese                                         | t 0                                                 | 0                                                                                                                                                                                                                                                                | 0           | 0   | 0   | 0   | 0   | 0   |  |  |

| SFR P                                        | SFR Page = 0x0; SFR Address = 0x88; Bit-Addressable |                                                                                                                                                                                                                                                                  |             |     |     |     |     |     |  |  |

| Bit                                          | Name                                                | Function                                                                                                                                                                                                                                                         |             |     |     |     |     |     |  |  |

| 7 TF1 Timer 1 Overflow Flag.                 |                                                     |                                                                                                                                                                                                                                                                  |             |     |     |     |     |     |  |  |

|                                              |                                                     | Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.                                                                                    |             |     |     |     |     |     |  |  |

| 6                                            | TR1                                                 | Timer 1 Run Control.                                                                                                                                                                                                                                             |             |     |     |     |     |     |  |  |

| Timer 1 is enabled by setting this bit to 1. |                                                     |                                                                                                                                                                                                                                                                  |             |     |     |     |     |     |  |  |

| 5 TF0 Timer 0 Overflow Flag.                 |                                                     |                                                                                                                                                                                                                                                                  |             |     |     |     |     |     |  |  |

|                                              |                                                     | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                    |             |     |     |     |     |     |  |  |

| 4                                            | TR0                                                 | Timer 0 Ru                                                                                                                                                                                                                                                       | n Control.  |     |     |     |     |     |  |  |

|                                              |                                                     | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                     |             |     |     |     |     |     |  |  |

| 3                                            | IE1                                                 | External Interrupt 1.                                                                                                                                                                                                                                            |             |     |     |     |     |     |  |  |

|                                              |                                                     | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                          |             |     |     |     |     |     |  |  |

| 2                                            | 2 IT1 Interrupt 1 Type Select.                      |                                                                                                                                                                                                                                                                  |             |     |     |     |     |     |  |  |