# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                       |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 17                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                    |

| Supplier Device Package    | 24-QSOP                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f987-c-gur |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | 19.2.Low Power Internal Oscillator                                              | 189 |

|-------------|---------------------------------------------------------------------------------|-----|

|             | 19.3.External Oscillator Drive Circuit                                          | 189 |

|             | 19.3.1.External Crystal Mode                                                    | 189 |

|             | 19.3.2.External RC Mode                                                         |     |

|             | 19.3.3.External Capacitor Mode                                                  |     |

|             |                                                                                 |     |

|             | 19.3.4.External CMOS Clock Mode                                                 |     |

|             | 19.4. Special Function Registers for Selecting and Configuring the System Clock |     |

| 20.         | SmaRTClock (Real Time Clock)                                                    |     |

|             | 20.1.SmaRTClock Interface                                                       | 198 |

|             | 20.1.1.SmaRTClock Lock and Key Functions                                        | 198 |

|             | 20.1.2. Using RTC0ADR and RTC0DAT to Access SmaRTClock Internal Regis           |     |

|             |                                                                                 |     |

|             | 20.1.3.RTC0ADR Short Strobe Feature                                             |     |

|             | 20.1.4.SmaRTClock Interface Autoread Feature                                    |     |

|             |                                                                                 |     |

|             | 20.1.5.RTC0ADR Autoincrement Feature                                            |     |

|             | 20.2.SmaRTClock Clocking Sources                                                |     |

|             | 20.2.1. Using the SmaRTClock Oscillator with a Crystal or External CMOS Clo     | ock |

|             |                                                                                 | 203 |

|             | 20.2.2.Using the SmaRTClock Oscillator in Self-Oscillate Mode                   | 204 |

|             | 20.2.3.Using the Low Frequency Oscillator (LFO)                                 |     |

|             | 20.2.4.Programmable Load Capacitance                                            |     |

|             | 20.2.5. Automatic Gain Control (Crystal Mode Only) and SmaRTClock Bias Do       |     |

|             |                                                                                 |     |

|             | bling                                                                           |     |

|             | 20.2.6.Missing SmaRTClock Detector                                              |     |

|             | 20.2.7.SmaRTClock Oscillator Crystal Valid Detector                             |     |

|             | 20.3.SmaRTClock Timer and Alarm Function                                        |     |

|             | 20.3.1.Setting and Reading the SmaRTClock Timer Value                           | 208 |

|             | 20.3.2.Setting a SmaRTClock Alarm                                               | 209 |

|             | 20.3.3.Software Considerations for using the SmaRTClock Timer and Alarm .       |     |

| 21.         | Port Input/Output                                                               |     |

|             | 21.1.Port I/O Modes of Operation                                                |     |

|             | 21.1.1.Port Pins Configured for Analog I/O                                      |     |

|             |                                                                                 |     |

|             | 21.1.2.Port Pins Configured For Digital I/O                                     |     |

|             | 21.1.3.Interfacing Port I/O to 5 V Logic                                        |     |

|             | 21.1.4.Increasing Port I/O Drive Strength                                       |     |

|             | 21.2.Assigning Port I/O Pins to Analog and Digital Functions                    |     |

|             | 21.2.1.Assigning Port I/O Pins to Analog Functions                              | 217 |

|             | 21.2.2.Assigning Port I/O Pins to Digital Functions                             | 218 |

|             | 21.2.3.Assigning Port I/O Pins to External Digital Event Capture Functions      |     |

|             | 21.3.Priority Crossbar Decoder                                                  |     |

|             | 21.4.Port Match                                                                 |     |

|             | 21.5.Special Function Registers for Accessing and Configuring Port I/O          |     |

| <b></b>     |                                                                                 |     |

| <b>ZZ</b> . | SMBus                                                                           |     |

|             | 22.1.Supporting Documents                                                       |     |

|             | 22.2.SMBus Configuration                                                        | 236 |

| OF 0.4.40 hit Time an with Auto Dalaged                             | 004 |

|---------------------------------------------------------------------|-----|

| 25.3.1.16-bit Timer with Auto-Reload                                |     |

| 25.3.2.8-Bit Timers with Auto-Reload                                |     |

| 25.3.3.SmaRTClock/External Oscillator Capture Mode                  | 296 |

| 26. Programmable Counter Array                                      | 300 |

| 26.1.PCA Counter/Timer                                              | 301 |

| 26.2.PCA0 Interrupt Sources                                         | 302 |

| 26.3.Capture/Compare Modules                                        | 303 |

| 26.3.1.Edge-triggered Capture Mode                                  | 304 |

| 26.3.2.Software Timer (Compare) Mode                                |     |

| 26.3.3.High-Speed Output Mode                                       | 306 |

| 26.3.4. Frequency Output Mode                                       | 306 |

| 26.3.5. 8-bit, 9-bit, 10-bit and 11-bit Pulse Width Modulator Modes | 307 |

| 26.3.6. 16-Bit Pulse Width Modulator Mode                           | 310 |

| 26.4.Watchdog Timer Mode                                            | 311 |

| 26.4.1.Watchdog Timer Operation                                     |     |

| 26.4.2.Watchdog Timer Usage                                         | 312 |

| 26.5.Register Descriptions for PCA0                                 | 313 |

| 27.C2 Interface                                                     |     |

| 27.1.C2 Interface Registers                                         | 319 |

| 27.2.C2 Pin Sharing                                                 |     |

| Document Change List                                                |     |

| Contact Information                                                 | 325 |

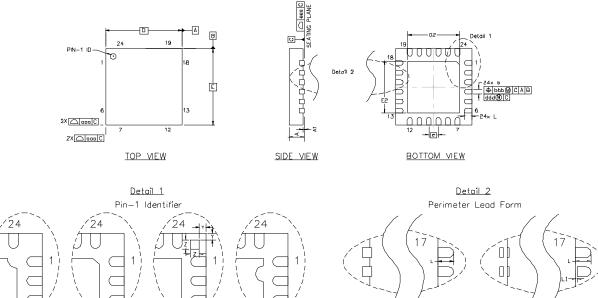

Option 1 Irregular Corner

Option 1 Edge Exposed

Option 2 Edge Pull-Back

#### Figure 3.9. QFN-24 Package Drawing

| Dimension | Min      | Тур  | Max  |  | Dimension | Min  | Тур  | Max  |

|-----------|----------|------|------|--|-----------|------|------|------|

| А         | 0.70     | 0.75 | 0.80 |  | L         | 0.30 | 0.40 | 0.50 |

| A1        | 0.00     | 0.02 | 0.05 |  | L1        | 0.00 | —    | 0.15 |

| b         | 0.18     | 0.25 | 0.30 |  | aaa       | _    | —    | 0.15 |

| D         | 4.00 BSC |      |      |  | bbb       | _    | —    | 0.10 |

| D2        | 2.55     | 2.70 | 2.80 |  | ddd       | _    | —    | 0.05 |

| е         | 0.50 BSC |      |      |  | eee       | —    | —    | 0.08 |

| E         | 4.00 BSC |      |      |  | Z         | _    | 0.24 |      |

| E2        | 2.55     | 2.70 | 2.80 |  | Y         | _    | 0.18 | —    |

#### Table 3.4. QFN-24 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation WGGD except for custom features D2, E2, Z, Y, and L which are toleranced per supplier designation.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

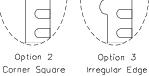

Figure 3.11. QSOP-24 Package Diagram

| Table | 3.6. | QSOP-24 | Package  | Dimensions |

|-------|------|---------|----------|------------|

| Table | 5.0. |         | I denage | Dimensions |

| Dimension | Min       | Тур       | Max  |  | Dimension | Min      | Тур  | Мах  |

|-----------|-----------|-----------|------|--|-----------|----------|------|------|

| A         | _         | —         | 1.75 |  | L         | 0.40     | —    | 1.27 |

| A1        | 0.10      | —         | 0.25 |  | L2        | 0.25 BSC |      |      |

| b         | 0.20      | —         | 0.30 |  | θ         | 0°       | —    | 8°   |

| С         | 0.10      | —         | 0.25 |  | aaa       | 0.20     |      |      |

| D         |           | 8.65 BSC. |      |  | bbb       | 0.18     |      |      |

| E         | 6.00 BSC  |           |      |  | CCC       |          | 0.10 |      |

| E1        | 3.90 BSC  |           |      |  | ddd       |          | 0.10 |      |

| е         | 0.635 BSC |           |      |  |           |          |      |      |

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MO-147, variation AE.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### Table 4.12. Voltage Reference Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                    | Conditions                                     | Min  | Тур        | Max             | Units |  |  |  |  |  |

|------------------------------|------------------------------------------------|------|------------|-----------------|-------|--|--|--|--|--|

| Internal High-Speed Referenc | nternal High-Speed Reference (REFSL[1:0] = 11) |      |            |                 |       |  |  |  |  |  |

| Output Voltage               | –40 to +85 °C,<br>V <sub>DD</sub> = 1.8−3.6 V  | 1.62 | 1.65       | 1.68            | V     |  |  |  |  |  |

| VREF Turn-on Time            |                                                | —    | _          | 1.5             | μs    |  |  |  |  |  |

| Supply Current               | Normal Power Mode<br>Low Power Mode            | _    | 260<br>140 |                 | μA    |  |  |  |  |  |

| External Reference (REFSL[1: | 0] = 00, REFOE = 0)                            | •    |            |                 |       |  |  |  |  |  |

| Input Voltage Range          |                                                | 0    | —          | V <sub>DD</sub> | V     |  |  |  |  |  |

| Input Current                | Sample Rate = 300 ksps;<br>VREF = 3.0 V        | —    | 5.25       | —               | μA    |  |  |  |  |  |

### SFR Definition 8.2. CS0CF: Capacitive Sense Configuration

| Bit   | 7              | 6 | 5          | 4 | 3              | 2           | 1 | 0 |

|-------|----------------|---|------------|---|----------------|-------------|---|---|

| Name  | <b>CS0SMEN</b> |   | CS0CM[2:0] |   | <b>CSOMCEN</b> | CS0ACU[2:0] |   |   |

| Туре  | R/W            |   | R/W        |   | R              | R/W         |   |   |

| Reset | 0              | 0 | 0          | 0 | 0              | 0           | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xAA

| Bit | Name           | Description                                                                                                                       |

|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 7   | <b>CS0SMEN</b> | CS0 Channel Scan Masking Enable.                                                                                                  |

|     |                | 0: The CS0SCAN0 and CS0SCAN1 register contents are ignored.<br>1: The CS0SCAN0 and CS0SCAN1 registers are used to determine which |

|     |                | channels will be included in the scan.                                                                                            |

| 6:4 | CS0CM[2:0]     | CS0 Start of Conversion Mode Select.                                                                                              |

|     |                | 000: Conversion initiated on every write of 1 to CS0BUSY.                                                                         |

|     |                | 001: Conversion initiated on overflow of Timer 0.                                                                                 |

|     |                | 010: Conversion initiated on overflow of Timer 2.                                                                                 |

|     |                | 011: Conversion initiated on overflow of Timer 1.                                                                                 |

|     |                | 100: Conversion initiated on overflow of Timer 3.                                                                                 |

|     |                | When CS0SMEN = 0                                                                                                                  |

|     |                | 101: Reserved.                                                                                                                    |

|     |                | 110: Conversion initiated continuously on the channel selected by CS0MX after writing 1 to CS0BUSY.                               |

|     |                | 111: Conversions initiated continuously on channels from CS0SS to CS0SE after writing 1 to CS0BUSY.                               |

|     |                | When CS0SMEN = 1                                                                                                                  |

|     |                | 101: Single Scan Mode, scans the channels selected by CS0SCAN0/1 once.                                                            |

|     |                | 110: Conversion initiated continuously on the channel selected by CS0MX after writing 1 to CS0BUSY.                               |

|     |                | 111: Auto Scan Mode, continuously scans the channels selected by CS0SCAN0/1.                                                      |

| 3   | <b>CSOMCEN</b> | CS0 Multiple Channel Enable.                                                                                                      |

|     |                | 0: Multiple channel feature is disabled.                                                                                          |

|     |                | 1: Channels selected by CS0SCAN0/1 are internally shorted together and the                                                        |

|     |                | combined node is selected as the CS0 input. This mode can be used to detect a                                                     |

|     |                | capacitance change on multiple channels using a single conversion.                                                                |

| 2:0 | CS0ACU[2:0]    | CS0 Accumulator Mode Select.                                                                                                      |

|     |                | 000: Accumulate 1 sample.                                                                                                         |

|     |                | 001: Accumulate 4 samples.                                                                                                        |

|     |                | 010: Accumulate 8 samples.                                                                                                        |

|     |                | 011: Accumulate 16 samples                                                                                                        |

|     |                | 100: Accumulate 32 samples.                                                                                                       |

|     |                | 101: Accumulate 64 samples.                                                                                                       |

|     |                | 11x: Reserved.                                                                                                                    |

### SFR Definition 8.3. CS0DH: Capacitive Sense Data High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | CS0DH[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R          | R | R | R | R | R | R | R |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Page = 0x0; SFR Address = 0xEE

| Bit | Name  | Description                                                                    |

|-----|-------|--------------------------------------------------------------------------------|

| 7:0 | CS0DH | CS0 Data High Byte.                                                            |

|     |       | Stores the high byte of the last completed 16-bit Capacitive Sense conversion. |

#### SFR Definition 8.4. CS0DL: Capacitive Sense Data Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|------------|---|---|---|---|---|---|--|--|--|

| Name  |   | CS0DL[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  | R | R          | R | R | R | R | R | R |  |  |  |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Page = 0x0; SFR Address = 0xED

| Bit | Name  | Description                                                                   |

|-----|-------|-------------------------------------------------------------------------------|

| 7:0 | CS0DL | CS0 Data Low Byte.                                                            |

|     |       | Stores the low byte of the last completed 16-bit Capacitive Sense conversion. |

### SFR Definition 8.15. CS0MX: Capacitive Sense Mux Channel Select

| Bit   | 7        | 6        | 5        | 4        | 3   | 2    | 1      | 0   |

|-------|----------|----------|----------|----------|-----|------|--------|-----|

| Name  | Reserved | Reserved | Reserved | Reserved |     | CS0M | X[3:0] |     |

| Туре  | R/W      | R/W      | R/W      | R/W      | R/W | R/W  | R/W    | R/W |

| Reset | 0        | 0        | 0        | 0        | 0   | 0    | 0      | 0   |

SFR Page = 0x0; SFR Address = 0xAB

| Bit | Name       |                         | Description                                               |  |  |  |

|-----|------------|-------------------------|-----------------------------------------------------------|--|--|--|

| 7:5 | Reserved   | Read = 000              | 0b; Write = 0000b.                                        |  |  |  |

| 4:0 | CS0MX[4:0] | CS0 Mux Channel Select. |                                                           |  |  |  |

|     |            | Selects one             | of the 14 input channels for Capacitive Sense conversion. |  |  |  |

|     |            | Value                   | Channel                                                   |  |  |  |

|     |            | 0000                    | P0.0                                                      |  |  |  |

|     |            | 0001                    | P0.1                                                      |  |  |  |

|     |            | 0010                    | P0.2                                                      |  |  |  |

|     |            | 0011                    | P0.3                                                      |  |  |  |

|     |            | 0100                    | P0.4                                                      |  |  |  |

|     |            | 0101                    | P0.5                                                      |  |  |  |

|     |            | 0110                    | P0.6                                                      |  |  |  |

|     |            | 0111                    | P0.7                                                      |  |  |  |

|     |            | 1000                    | P1.0                                                      |  |  |  |

|     |            | 1001                    | P1.1                                                      |  |  |  |

|     |            | 1010                    | P1.2                                                      |  |  |  |

|     |            | 1011                    | P1.3                                                      |  |  |  |

|     |            | 1100                    | P1.4 (24-pin packages only)                               |  |  |  |

|     |            | 1101                    | P1.5                                                      |  |  |  |

|     |            | 1110                    | Reserved                                                  |  |  |  |

|     |            | 1111                    | Reserved                                                  |  |  |  |

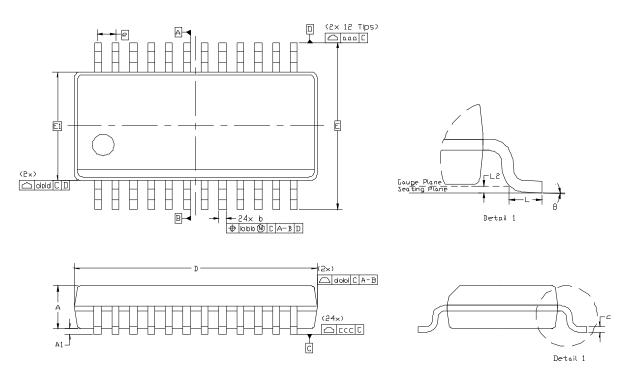

### 9. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 27) and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 9.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25 MHz Clock

- 0 to 25 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### 9.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

Figure 9.1. CIP-51 Block Diagram

### SFR Definition 9.6. PSW: Program Status Word

| Bit   | 7            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                                                                            | 4             | 3             | 2            | 1              | 0           |  |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|--------------|----------------|-------------|--|

| Nam   | e CY         | AC                                                                                                                                                                                                                                                                                                                                                                                                                                                | F0                                                                                                                                                                                                                                           | RS            | [1:0]         | OV           | F1             | PARITY      |  |

| Туре  | R/W          | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W                                                                                                                                                                                                                                          | R/            | R/W           |              | R/W            | R           |  |

| Rese  | et O         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                            | 0 0 0 0       |               | 0            | 0              |             |  |

| SFR F | age = All; S | SFR Address =                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0xD0; Bit-A                                                                                                                                                                                                                                  | ddressable    | •             |              |                |             |  |

| Bit   | Name         |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |               | Function      |              |                |             |  |

| 7     | CY           |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>Carry Flag.</b><br>This bit is set when the last arithmetic operation resulted in a carry (addition) or a bor-<br>bow (subtraction). It is cleared to logic 0 by all other arithmetic operations.                                         |               |               |              |                |             |  |

| 6     | AC           | This bit is set<br>borrow from (s                                                                                                                                                                                                                                                                                                                                                                                                                 | This bit is set when the last arithmetic operation resulted in a carry into (addition) or a orrow from (subtraction) the high order nibble. It is cleared to logic 0 by all other arithmetic operations.                                     |               |               |              |                |             |  |

| 5     | F0           | <b>User Flag 0.</b><br>This is a bit-ad                                                                                                                                                                                                                                                                                                                                                                                                           | <b>User Flag 0.</b><br>This is a bit-addressable, general purpose flag for use under software control.                                                                                                                                       |               |               |              |                |             |  |

| 4:3   | RS[1:0]      | These bits sel<br>00: Bank 0, Ao<br>01: Bank 1, Ao<br>10: Bank 2, Ao                                                                                                                                                                                                                                                                                                                                                                              | Register Bank Select.<br>These bits select which register bank is used during register accesses.<br>00: Bank 0, Addresses 0x00-0x07<br>01: Bank 1, Addresses 0x08-0x0F<br>10: Bank 2, Addresses 0x10-0x17<br>11: Bank 3, Addresses 0x18-0x1F |               |               |              |                |             |  |

| 2     | OV           | <ul> <li>Overflow Flag.</li> <li>This bit is set to 1 under the following circumstances: <ul> <li>An ADD, ADDC, or SUBB instruction causes a sign-change overflow.</li> <li>A MUL instruction results in an overflow (result is greater than 255).</li> <li>A DIV instruction causes a divide-by-zero condition.</li> </ul> </li> <li>The OV bit is cleared to 0 by the ADD, ADDC, SUBB, MUL, and DIV instructions in all other cases.</li> </ul> |                                                                                                                                                                                                                                              |               |               |              |                |             |  |

| 1     | F1           | <b>User Flag 1.</b><br>This is a bit-ad                                                                                                                                                                                                                                                                                                                                                                                                           | ddressable,                                                                                                                                                                                                                                  | general purp  | ose flag for  | use under so | oftware contr  | ol.         |  |

| 0     | PARITY       | <b>Parity Flag.</b><br>This bit is set t<br>if the sum is e                                                                                                                                                                                                                                                                                                                                                                                       | •                                                                                                                                                                                                                                            | ne sum of the | eight bits in | the accumu   | lator is odd a | and cleared |  |

### SFR Definition 13.2. IP: Interrupt Priority

| Bit    | 7             | 6                                                                        | 5                                                                                                                                                                                                                        | 4                          | 3                           | 2          | 1   | 0   |  |

|--------|---------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|------------|-----|-----|--|

| Name   |               | PSPI0                                                                    | PT2                                                                                                                                                                                                                      | PS0                        | PT1                         | PX1        | PT0 | PX0 |  |

| Туре   | R             | R/W                                                                      | R/W                                                                                                                                                                                                                      | R/W                        | R/W                         | R/W        | R/W | R/W |  |

| Reset  | 1             | 0                                                                        | 0                                                                                                                                                                                                                        | 0                          | 0                           | 0          | 0   | 0   |  |

| SFR Pa | age = All; \$ | SFR Address =                                                            | 0xB8; Bit-A                                                                                                                                                                                                              | ddressable                 |                             |            |     |     |  |

| Bit    | Name          | Function                                                                 |                                                                                                                                                                                                                          |                            |                             |            |     |     |  |

| 7      | Unused        | Read = 1b, W                                                             | rite = don't c                                                                                                                                                                                                           | care.                      |                             |            |     |     |  |

| 6      | PSPI0         | This bit sets th<br>0: SPI0 interru                                      | Serial Peripheral Interface (SPI0) Interrupt Priority Control.<br>This bit sets the priority of the SPI0 interrupt.<br>0: SPI0 interrupt set to low priority level.<br>1: SPI0 interrupt set to high priority level.     |                            |                             |            |     |     |  |

| 5      | PT2           | This bit sets th<br>0: Timer 2 inte                                      | Timer 2 Interrupt Priority Control.         This bit sets the priority of the Timer 2 interrupt.         0: Timer 2 interrupt set to low priority level.         1: Timer 2 interrupt set to high priority level.        |                            |                             |            |     |     |  |

| 4      | PS0           | This bit sets th<br>0: UART0 inte                                        | UARTO Interrupt Priority Control.<br>This bit sets the priority of the UARTO interrupt.<br>0: UARTO interrupt set to low priority level.<br>1: UARTO interrupt set to high priority level.                               |                            |                             |            |     |     |  |

| 3      | PT1           | This bit sets th<br>0: Timer 1 inte                                      | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                   |                            |                             |            |     |     |  |

| 2      | PX1           | This bit sets th<br>0: External Int                                      | External Interrupt 1 Priority Control.<br>This bit sets the priority of the External Interrupt 1 interrupt.<br>0: External Interrupt 1 set to low priority level.<br>1: External Interrupt 1 set to high priority level. |                            |                             |            |     |     |  |

| 1      | PT0           | This bit sets th<br>0: Timer 0 inte                                      | Timer 0 Interrupt Priority Control.         This bit sets the priority of the Timer 0 interrupt.         0: Timer 0 interrupt set to low priority level.         1: Timer 0 interrupt set to high priority level.        |                            |                             |            |     |     |  |

| 0      | PX0           | External Inter<br>This bit sets th<br>0: External Int<br>1: External Int | ne priority of<br>errupt 0 set                                                                                                                                                                                           | the Externa to low priorit | l Interrupt 0 i<br>y level. | interrupt. |     |     |  |

#### 14.6. Minimizing Flash Read Current

The Flash memory in the C8051F99x-C8051F98x devices is responsible for a substantial portion of the total digital supply current when the device is executing code. Below are suggestions to minimize Flash read current.

- Use idle, suspend, or sleep modes while waiting for an interrupt, rather than polling the interrupt flag. Idle Mode is particularly well-suited for use in implementing short pauses, since the wake-up time is no more than three system clock cycles. See the Power Management chapter for details on the various low-power operating modes.

- 2. C8051F99x-C8051F98x devices have a one-shot timer that saves power when operating at system clock frequencies of 14 MHz or less. The one-shot timer generates a minimum-duration enable signal for the Flash sense amps on each clock cycle in which the Flash memory is accessed. This allows the Flash to remain in a low power state for the remainder of the long clock cycle. At clock frequencies above 14 MHz, the system clock cycle becomes short enough that the one-shot timer no longer provides a power benefit. Disabling the one-shot timer at higher frequencies reduces power consumption. The one-shot is enabled by default, and it can be disabled (bypassed) by setting the BYPASS bit (FLSCL.6) to logic 1. To re-enable the one-shot, clear the BYPASS bit to logic 0.

- 3. Flash read current depends on the number of address lines that toggle between sequential Flash read operations. In most cases, the difference in power is relatively small (on the order of 5%).

The Flash memory is organized in rows of 64 bytes. A substantial current increase can be detected when the read address jumps from one row in the Flash memory to another. Consider a 3-cycle loop (e.g., SJMP \$, or while(1);) which straddles a Flash row boundary. The Flash address jumps from one row to another on two of every three clock cycles. This can result in a current increase of up 30% when compared to the same 3-cycle loop contained entirely within a single row.

To minimize the power consumption of small loops, it is best to locate them within a single row, if possible. To check if a loop is contained within a Flash row, divide the starting address of the first instruction in the loop by 64. If the remainder (result of modulo operation) plus the length of the loop is less than 63, then the loop fits inside a single Flash row. Otherwise, the loop will be straddling two adjacent Flash rows. If a loop executes in 20 or more clock cycles, then the transitions from one row to another will occur on relatively few clock cycles, and any resulting increase in operating current will be negligible.

### SFR Definition 14.4. FLKEY: Flash Lock and Key

| Bit   | 7             | 6                                                                                                                                                                                                                                  | 5                                                                                                                                                                             | 4                                                                                                                                                   | 3                                                                                                                                                   | 2                                                                                                            | 1                                                                                     | 0                                                                   |  |  |  |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|

| Name  | ;             | FLKEY[7:0]                                                                                                                                                                                                                         |                                                                                                                                                                               |                                                                                                                                                     |                                                                                                                                                     |                                                                                                              |                                                                                       |                                                                     |  |  |  |

| Туре  |               | R/W                                                                                                                                                                                                                                |                                                                                                                                                                               |                                                                                                                                                     |                                                                                                                                                     |                                                                                                              |                                                                                       |                                                                     |  |  |  |

| Reset | t 0           | 0                                                                                                                                                                                                                                  | 0                                                                                                                                                                             | 0                                                                                                                                                   | 0                                                                                                                                                   | 0                                                                                                            | 0                                                                                     | 0                                                                   |  |  |  |

| SFR P | age = All; SF | R Address =                                                                                                                                                                                                                        | 0xB7                                                                                                                                                                          | L                                                                                                                                                   |                                                                                                                                                     |                                                                                                              |                                                                                       | 1                                                                   |  |  |  |

| Bit   | Name          |                                                                                                                                                                                                                                    |                                                                                                                                                                               |                                                                                                                                                     | Function                                                                                                                                            |                                                                                                              |                                                                                       |                                                                     |  |  |  |

| 7:0   | FLKEY[7:0]    | Flash Lock                                                                                                                                                                                                                         | and Key Re                                                                                                                                                                    | gister.                                                                                                                                             |                                                                                                                                                     |                                                                                                              |                                                                                       |                                                                     |  |  |  |

|       |               | Write:                                                                                                                                                                                                                             |                                                                                                                                                                               |                                                                                                                                                     |                                                                                                                                                     |                                                                                                              |                                                                                       |                                                                     |  |  |  |

|       |               | This register<br>writes and ei<br>ter. Flash wri<br>complete. If a<br>operation is a<br>nently locked<br>never writes<br>FLKEY from<br>Read:<br>When read, I<br>00: Flash is o<br>01: The first<br>10: Flash is o<br>11: Flash wri | ases are en<br>tes and eras<br>any writes to<br>attempted w<br>from writes<br>to Flash, it c<br>software.<br>bits 1–0 indi-<br>write/erase li-<br>key code ha<br>unlocked (wr | abled by wr<br>ses are auto<br>FLKEY are<br>hile these of<br>or erasures<br>an intention<br>cate the curr<br>ocked.<br>s been writt<br>rites/erases | iting 0xA5 fol<br>matically dis<br>performed in<br>perations are<br>s until the nex<br>ally lock the l<br>rent Flash loc<br>en (0xA5).<br>allowed). | llowed by 02<br>abled after t<br>ncorrectly, or<br>disabled, t<br>xt device res<br>Flash by wri<br>ck state. | xF1 to the FL<br>the next write<br>r if a Flash wi<br>he Flash will<br>set. If an app | KEY regis-<br>or erase is<br>rite or erase<br>be perma-<br>lication |  |  |  |

### SFR Definition 18.1. VDM0CN: VDD Supply Monitor Control

| Bit   | 7     | 6       | 5      | 4 | 3       | 2 | 1 | 0 |

|-------|-------|---------|--------|---|---------|---|---|---|

| Name  | VDMEN | VDDSTAT | VDDOK  |   | VDDOKIE |   |   |   |

| Туре  | R/W   | R       | R      | R | R/W     | R | R | R |

| Reset | 1     | Varies  | Varies | 0 | 1       | 0 | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xFF

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                               |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Supply Monitor Enable.                                                                                                                                                                                                                                                                                                 |

|     |         | <ul> <li>This bit turns the V<sub>DD</sub> supply monitor circuit on/off. The VDD Supply Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 18.2).</li> <li>0: V<sub>DD</sub> Supply Monitor Disabled.</li> <li>1: V<sub>DD</sub> Supply Monitor Enabled.</li> </ul> |

| 6   | VDDSTAT | V <sub>DD</sub> Supply Status.                                                                                                                                                                                                                                                                                                         |

|     |         | This bit indicates the current power supply status.<br>0: $V_{DD}$ is at or below the $V_{RST}$ threshold.<br>1: $V_{DD}$ is above the $V_{RST}$ threshold.                                                                                                                                                                            |

| 5   | VDDOK   | V <sub>DD</sub> Supply Status (Early Warning).                                                                                                                                                                                                                                                                                         |

|     |         | This bit indicates the current V <sub>DD</sub> power supply status.<br>0: V <sub>DD</sub> is at or below the VDD <sub>WARN</sub> threshold.<br>1: V <sub>DD</sub> is above the VDD <sub>WARN</sub> threshold.                                                                                                                          |

| 4   | Unused  | Read = 0b. Write = Don't Care.                                                                                                                                                                                                                                                                                                         |

| 3   | VDDOKIE | V <sub>DD</sub> Early Warning Interrupt Enable.                                                                                                                                                                                                                                                                                        |

|     |         | Enables the V <sub>DD</sub> Early Warning Interrupt.<br>0: V <sub>DD</sub> Early Warning Interrupt is disabled.<br>1: V <sub>DD</sub> Early Warning Interrupt is enabled.                                                                                                                                                              |

| 2:0 | Unused  | Read = 000b. Write = Don't Care.                                                                                                                                                                                                                                                                                                       |

#### 18.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 4.4 for complete RST pin specifications. The external reset remains functional even when the device is in the low power suspend and sleep modes. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### SFR Definition 21.13. P1: Port1

| Bit   | 7 | 6       | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---------|---|---|---|---|---|---|

| Name  |   | P1[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W     |   |   |   |   |   |   |

| Reset | 1 | 1       | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = All; SFR Address = 0x90; Bit-Addressable

| Bit | Name    | Description | Write                                                                         | Read |

|-----|---------|-------------|-------------------------------------------------------------------------------|------|

| 7:0 | P1[6:0] |             | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW. |

### SFR Definition 21.14. P1SKIP: Port1 Skip

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-------------|---|---|---|---|---|---|--|

| Name  |   | P1SKIP[7:0] |   |   |   |   |   |   |  |

| Туре  |   | R/W         |   |   |   |   |   |   |  |

| Reset | 0 | 0           | 0 | 0 | 0 | 0 | 0 | 0 |  |

#### SFR Page = 0x0; SFR Address = 0xD5

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP[6:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P1.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P1.n pin is skipped by the Crossbar.</li> </ul> |

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 22.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                                                          | Minimum SDA Setup Time             | Minimum SDA Hold Time |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|--|--|--|

|                                                                                                                                                                                                                                                                                                                  | T <sub>low</sub> – 4 system clocks |                       |  |  |  |

| 0                                                                                                                                                                                                                                                                                                                | or                                 | 3 system clocks       |  |  |  |

|                                                                                                                                                                                                                                                                                                                  | 1 system clock + s/w delay*        |                       |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                | 11 system clocks                   | 12 system clocks      |  |  |  |

| *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                                    |                       |  |  |  |

Table 22.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "22.3.4. SCL Low Timeout" on page 238). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 22.4).

| Parameter Description     |                                                                     | Min                                            | Max                     | Units |  |

|---------------------------|---------------------------------------------------------------------|------------------------------------------------|-------------------------|-------|--|

| Master Mode               | Timing (See Figure 24.8 and Figure 24.9)                            |                                                |                         | 1     |  |

| Т <sub>МСКН</sub>         | SCK High Time                                                       | 1 x T <sub>SYSCLK</sub>                        | —                       | ns    |  |

| T <sub>MCKL</sub>         | SCK Low Time 1 x T <sub>SYSCLK</sub> -                              |                                                |                         | ns    |  |

| T <sub>MIS</sub>          | MISO Valid to SCK Shift Edge                                        | 1 x T <sub>SYSCLK</sub> + 20                   | —                       | ns    |  |

| Т <sub>МІН</sub>          | SCK Shift Edge to MISO Change                                       | 0                                              |                         | ns    |  |

| Slave Mode 1              | Fiming (See Figure 24.10 and Figure 24.11)                          |                                                |                         | 1     |  |

| T <sub>SE</sub>           | NSS Falling to First SCK Edge                                       | 2 x T <sub>SYSCLK</sub>                        |                         | ns    |  |

| T <sub>SD</sub>           | Last SCK Edge to NSS Rising 2 x T <sub>SY</sub>                     |                                                | —                       | ns    |  |

| T <sub>SEZ</sub>          | NSS Falling to MISO Valid                                           | —                                              | 4 x T <sub>SYSCLK</sub> | ns    |  |

| T <sub>SDZ</sub>          | NSS Rising to MISO High-Z                                           | NSS Rising to MISO High-Z — 4 x T <sub>S</sub> |                         | ns    |  |

| Т <sub>СКН</sub>          | SCK High Time                                                       | 5 x T <sub>SYSCLK</sub>                        | —                       | ns    |  |

| T <sub>CKL</sub>          | SCK Low Time                                                        | 5 x T <sub>SYSCLK</sub>                        | —                       | ns    |  |

| T <sub>SIS</sub>          | MOSI Valid to SCK Sample Edge                                       | 2 x T <sub>SYSCLK</sub>                        | —                       | ns    |  |

| T <sub>SIH</sub>          | SCK Sample Edge to MOSI Change                                      | 2 x T <sub>SYSCLK</sub>                        | —                       | ns    |  |

| T <sub>SOH</sub>          | SCK Shift Edge to MISO Change —                                     |                                                | 4 x T <sub>SYSCLK</sub> | ns    |  |

| T <sub>SLH</sub>          | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)                    | 6 x T <sub>SYSCLK</sub>                        | 8 x T <sub>SYSCLK</sub> | ns    |  |

| Note: T <sub>SYSCLk</sub> | $\frac{1}{\zeta}$ is equal to one period of the device system clock | (SYSCLK).                                      | 1                       |       |  |

### Table 24.1. SPI Slave Timing Parameters

277

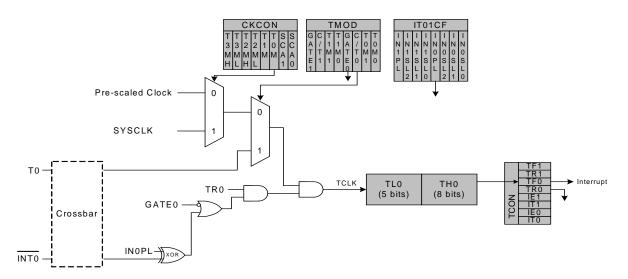

Figure 25.1. T0 Mode 0 Block Diagram

#### 25.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

### SFR Definition 25.4. TL0: Timer 0 Low Byte

| Bit                                | 7          | 6             | 5     | 4 | 3 | 2 | 1 | 0 |

|------------------------------------|------------|---------------|-------|---|---|---|---|---|

| Name                               | 9          | TL0[7:0]      |       |   |   |   |   |   |

| Туре                               | •          | R/W           |       |   |   |   |   |   |

| Reset                              | <b>t</b> 0 | 0             | 0     | 0 | 0 | 0 | 0 | 0 |

| SFR Page = 0x0; SFR Address = 0x8A |            |               |       |   |   |   |   |   |

| Bit                                | Name       | Name Function |       |   |   |   |   |   |

| 7.0                                |            | Timer OI e    | Durte |   |   |   |   |   |

| 7:0 | TL0[7:0] | Timer 0 Low Byte.                                       |

|-----|----------|---------------------------------------------------------|

|     |          | The TL0 register is the low byte of the 16-bit Timer 0. |

### SFR Definition 25.5. TL1: Timer 1 Low Byte

| Bit   | 7             | 6                                                       | 5        | 4 | 3 | 2 | 1 | 0 |

|-------|---------------|---------------------------------------------------------|----------|---|---|---|---|---|

| Nam   | e             | 1                                                       | TL1[7:0] |   |   |   |   |   |

| Туре  | •             | R/W                                                     |          |   |   |   |   |   |

| Rese  | et 0          | 0 0 0 0 0 0 0                                           |          |   |   |   |   |   |

| SFR F | Page = 0x0; S | FR Address =                                            | = 0x8B   |   |   |   |   |   |

| Bit   | Name          | Function                                                |          |   |   |   |   |   |

| 7:0   | TL1[7:0]      | Timer 1 Low Byte.                                       |          |   |   |   |   |   |

|       |               | The TL1 register is the low byte of the 16-bit Timer 1. |          |   |   |   |   |   |

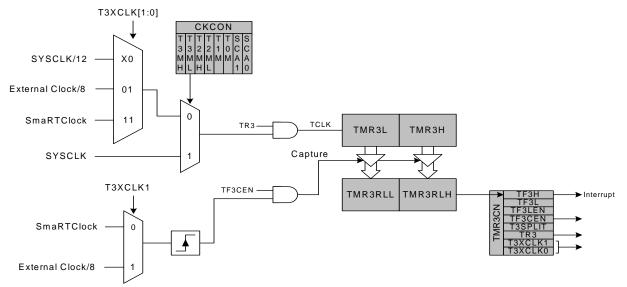

#### 25.3.3. SmaRTClock/External Oscillator Capture Mode

The Capture Mode in Timer 3 allows either SmaRTClock or the external oscillator period to be measured against the system clock or the system clock divided by 12. SmaRTClock and the external oscillator period can also be compared against each other.

Setting TF3CEN to 1 enables the SmaRTClock/External Oscillator Capture Mode for Timer 3. In this mode, T3SPLIT should be set to 0, as the full 16-bit timer is used.

When Capture Mode is enabled, a capture event will be generated either every SmaRTClock rising edge or every 8 external clock cycles, depending on the T3XCLK1 setting. When the capture event occurs, the contents of Timer 3 (TMR3H:TMR3L) are loaded into the Timer 3 reload registers (TMR3RLH:TMR3RLL) and the TF3H flag is set (triggering an interrupt if Timer 3 interrupts are enabled). By recording the difference between two successive timer capture values, the SmaRTClock or external clock period can be determined with respect to the Timer 3 clock. The Timer 3 clock should be much faster than the capture clock to achieve an accurate reading.

For example, if T3ML = 1b, T3XCLK1 = 0b, and TF3CEN = 1b, Timer 3 will clock every SYSCLK and capture every SmaRTClock rising edge. If SYSCLK is 24.5 MHz and the difference between two successive captures is 350 counts, then the SmaRTClock period is as follows:

350 x (1 / 24.5 MHz) = 14.2 μs.

This mode allows software to determine the exact frequency of the external oscillator in C and RC mode or the time between consecutive SmaRTClock rising edges, which is useful for determining the SmaRTClock frequency.

Figure 25.9. Timer 3 Capture Mode Block Diagram