# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

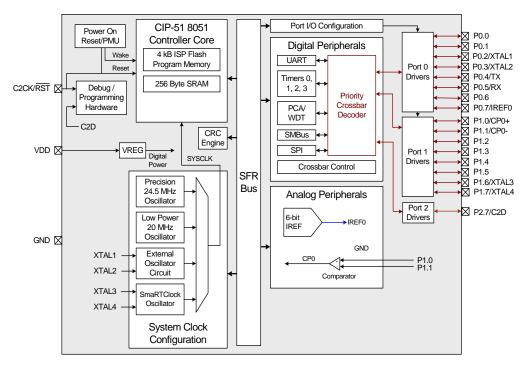

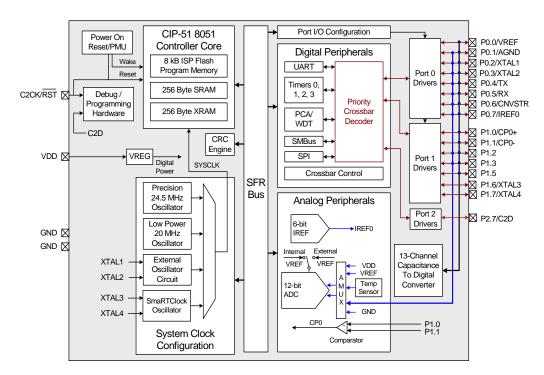

| Core Processor             | CIP-51 8051                                                      |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 17                                                               |

| Program Memory Size        | 4KB (4K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 512 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                      |

| Data Converters            | A/D 10x10b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                   |

| Supplier Device Package    | 24-QSOP                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f988-c-gu |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

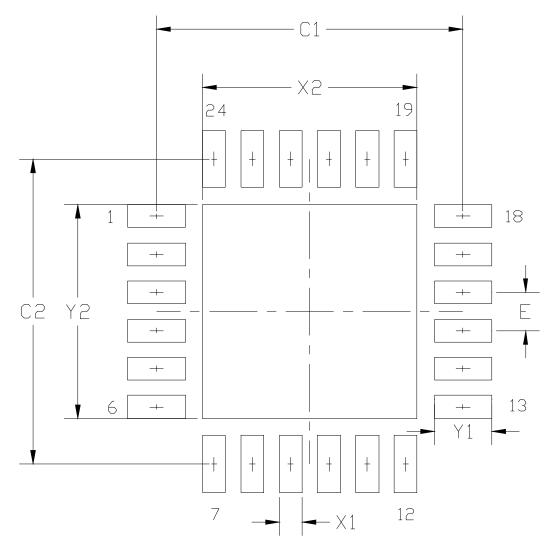

Figure 3.10. Typical QFN-24 Landing Diagram

### SFR Definition 5.1. ADC0CN: ADC0 Control

| Bit   | 7     | 6       | 5      | 4       | 3       | 2           | 1 | 0 |

|-------|-------|---------|--------|---------|---------|-------------|---|---|

| Name  | AD0EN | BURSTEN | AD0INT | AD0BUSY | AD0WINT | ADC0CM[2:0] |   |   |

| Туре  | R/W   | R/W     | R/W    | W       | R/W     | R/W         |   |   |

| Reset | 0     | 0       | 0      | 0       | 0       | 0           | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xE8; bit-addressable;

| Bit | Name        | Function                                                                                                                                                                                 |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AD0EN       | ADC0 Enable.                                                                                                                                                                             |

|     |             | 0: ADC0 Disabled (low-power shutdown).<br>1: ADC0 Enabled (active and ready for data conversions).                                                                                       |

| 6   | BURSTEN     | ADC0 Burst Mode Enable.<br>0: ADC0 Burst Mode Disabled.                                                                                                                                  |

|     |             | 1: ADC0 Burst Mode Enabled.                                                                                                                                                              |

| 5   | AD0INT      | ADC0 Conversion Complete Interrupt Flag.                                                                                                                                                 |

|     |             | Set by hardware upon completion of a data conversion (BURSTEN=0), or a burst of conversions (BURSTEN=1). Can trigger an interrupt. Must be cleared by software.                          |

| 4   | AD0BUSY     | ADC0 Busy.                                                                                                                                                                               |

|     |             | Writing 1 to this bit initiates an ADC conversion when ADC0CM[2:0] = 000.                                                                                                                |

| 3   | AD0WINT     | ADC0 Window Compare Interrupt Flag.                                                                                                                                                      |

|     |             | Set by hardware when the contents of ADC0H:ADC0L fall within the window speci-<br>fied by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL. Can trigger an interrupt.<br>Must be cleared by software. |

| 2:0 | ADC0CM[2:0] | ADC0 Start of Conversion Mode Select.                                                                                                                                                    |

|     |             | Specifies the ADC0 start of conversion source.                                                                                                                                           |

|     |             | 000: ADC0 conversion initiated on write of 1 to AD0BUSY.<br>001: ADC0 conversion initiated on overflow of Timer 0.                                                                       |

|     |             | 010: ADC0 conversion initiated on overflow of Timer 0.                                                                                                                                   |

|     |             | 011: ADC0 conversion initiated on overflow of Timer 3.                                                                                                                                   |

|     |             | 1xx: ADC0 conversion initiated on rising edge of CNVSTR.                                                                                                                                 |

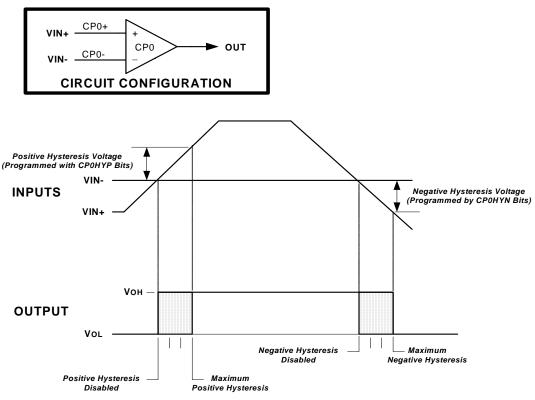

Figure 7.2. Comparator Hysteresis Plot

### 7.5. Comparator Register Descriptions

The SFRs used to enable and configure the comparator are described in the following register descriptions. The comparator must be enabled by setting the CP0EN bit to logic 1 before it can be used. From an enabled state, a comparator can be disabled and placed in a low power state by clearing the CP0EN bit to logic 0.

**Important Note About Comparator Settings:** False rising and falling edges can be detected by the Comparator while powering on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed. The Comparator Power Up Time is specified in Section "Table 4.14. Comparator Electrical Characteristics" on page 63.

### 8.11. CS0 Conversion Accumulator

CS0 can be configured to accumulate multiple conversions on an input channel. The number of samples to be accumulated is configured using the CS0ACU2:0 bits (CS0CF2:0). The accumulator can accumulate 1, 4, 8, 16, 32, or 64 samples. After the defined number of samples have been accumulated, the result is divided by either 1, 4, 8, 16, 32, or 64 (depending on the CS0ACU[2:0] setting) and copied to the CS0DH:CS0DL SFRs.

| Auto-Scan Enabled | Accumulator Enabled | CS0 Conversion<br>Complete<br>Interrupt<br>Behavior                      | CS0 Greater Than Interrupt<br>Behavior                                                                                                                                          | CS0MX Behavior                                                                                                                                                                                                                     |

|-------------------|---------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N                 | Ν                   | CS0INT Interrupt<br>serviced after 1<br>conversion com-<br>pletes        | Interrupt serviced after 1 con-<br>version completes if value in<br>CS0DH:CS0DL is greater than<br>CS0THH:CS0THL                                                                | CS0MX unchanged.                                                                                                                                                                                                                   |

| N                 | Y                   | CS0INT Interrupt<br>serviced after <i>M</i><br>conversions com-<br>plete | Interrupt serviced after <i>M</i> conversions complete if value in CS0DH:CS0DL (post accumulate and divide) is greater than CS0THH:CS0THL                                       | CS0MX unchanged.                                                                                                                                                                                                                   |

| Y                 | Ν                   | CS0INT Interrupt<br>serviced after 1<br>conversion com-<br>pletes        | Interrupt serviced after con-<br>version completes if value in<br>CS0DH:CS0DL is greater than<br>CS0THH:CS0THL;<br>Auto-Scan stopped                                            | If greater-than comparator detects conver-<br>sion value is greater than<br>CS0THH:CS0THL, CS0MX is left<br>unchanged; otherwise, CS0MX updates to<br>the next channel (CS0MX + 1) and wraps<br>back to CS0SS after passing CS0SE. |

| Y                 | Y                   | CS0INT Interrupt<br>serviced after <i>M</i><br>conversions com-<br>plete | Interrupt serviced after <i>M</i> con-<br>versions complete if value in<br>CS0DH:CS0DL (post accumu-<br>late and divide) is greater than<br>CS0THH:CS0THL; Auto-Scan<br>stopped | If greater-than comparator detects conver-<br>sion value is greater than<br>CS0THH:CS0THL, CS0MX is left<br>unchanged; otherwise, CS0MX updates to<br>the next channel (CS0MX + 1) and wraps<br>back to CS0SS after passing CS0SE. |

Table 8.1. Operation with Auto-scan and Accumulate

### SFR Definition 8.9. CS0THH: Capacitive Sense Comparator Threshold High Byte

| Bit   | 7   | 6           | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------------|-----|-----|-----|-----|-----|-----|

| Name  |     | CS0THH[7:0] |     |     |     |     |     |     |

| Туре  | R/W | R/W         | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0           | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Page = 0x0; SFR Address = 0xFE

| Bit | Name        | Description                                                                       |

|-----|-------------|-----------------------------------------------------------------------------------|

| 7:0 | CS0THH[7:0] | CS0 Comparator Threshold High Byte.                                               |

|     |             | High byte of the 16-bit value compared to the Capacitive Sense conversion result. |

### SFR Definition 8.10. CS0THL: Capacitive Sense Comparator Threshold Low Byte

| Bit                                | 7   | 6   | 5          | 4     | 3       | 2   | 1   | 0   |

|------------------------------------|-----|-----|------------|-------|---------|-----|-----|-----|

| Name                               |     |     |            | CS0TH | HL[7:0] |     |     |     |

| Туре                               | R/W | R/W | R/W        | R/W   | R/W     | R/W | R/W | R/W |

| Reset                              | 0   | 0   | 0          | 0     | 0       | 0   | 0   | 0   |

| SFR Page = 0x0; SFR Address = 0xFD |     |     |            |       |         |     |     |     |

| Bit Name                           |     |     | Descriptio | n     |         |     |     |     |

| BIt | Name        | Description                                                                      |

|-----|-------------|----------------------------------------------------------------------------------|

| 7:0 | CS0THL[7:0] | CS0 Comparator Threshold Low Byte.                                               |

|     |             | Low byte of the 16-bit value compared to the Capacitive Sense conversion result. |

112

### SFR Definition 9.6. PSW: Program Status Word

| Bit   | 7             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                         | 4                             | 3             | 2              | 1              | 0            |

|-------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------|---------------|----------------|----------------|--------------|

| Nam   | e CY          | AC                                                                                                                                                                                                                                                                                                                                                                                                                                                | F0                                                        | RS                            | [1:0]         | OV             | F1             | PARITY       |

| Туре  | R/W           | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W                                                       | R/                            | /W            | R/W            | R/W            | R            |

| Rese  | et O          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                         | 0                             | 0             | 0              | 0              | 0            |

| SFR F | Page = All; S | SFR Address =                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0xD0; Bit-A                                               | ddressable                    | •             |                |                |              |

| Bit   | Name          |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                           |                               | Function      |                |                |              |

| 7     | CY            | <b>Carry Flag.</b><br>This bit is set<br>row (subtraction                                                                                                                                                                                                                                                                                                                                                                                         |                                                           |                               |               |                |                | n) or a bor- |

| 6     | AC            | Auxiliary Car<br>This bit is set<br>borrow from (s<br>metic operatio                                                                                                                                                                                                                                                                                                                                                                              | when the las<br>subtraction)                              |                               |               |                |                |              |

| 5     | F0            | <b>User Flag 0.</b><br>This is a bit-ad                                                                                                                                                                                                                                                                                                                                                                                                           | ddressable,                                               | general purp                  | ose flag for  | use under so   | oftware contr  | ol.          |

| 4:3   | RS[1:0]       | Register Ban<br>These bits sel<br>00: Bank 0, Ao<br>01: Bank 1, Ao<br>10: Bank 2, Ao<br>11: Bank 3, Ao                                                                                                                                                                                                                                                                                                                                            | ect which re<br>ddresses 0x<br>ddresses 0x<br>ddresses 0x | 00-0x07<br>08-0x0F<br>10-0x17 | s used durin  | ig register ac | cesses.        |              |

| 2     | OV            | <ul> <li>Overflow Flag.</li> <li>This bit is set to 1 under the following circumstances: <ul> <li>An ADD, ADDC, or SUBB instruction causes a sign-change overflow.</li> <li>A MUL instruction results in an overflow (result is greater than 255).</li> <li>A DIV instruction causes a divide-by-zero condition.</li> </ul> </li> <li>The OV bit is cleared to 0 by the ADD, ADDC, SUBB, MUL, and DIV instructions in all other cases.</li> </ul> |                                                           |                               |               |                | ctions in all  |              |

| 1     | F1            | <b>User Flag 1.</b><br>This is a bit-ad                                                                                                                                                                                                                                                                                                                                                                                                           | ddressable,                                               | general purp                  | ose flag for  | use under so   | oftware contr  | ol.          |

| 0     | PARITY        | <b>Parity Flag.</b><br>This bit is set t<br>if the sum is e                                                                                                                                                                                                                                                                                                                                                                                       | •                                                         | ne sum of the                 | eight bits in | the accumu     | lator is odd a | and cleared  |

### 13. Interrupt Handler

The C8051F99x-C8051F98x microcontroller family includes an extended interrupt system supporting multiple interrupt sources and two priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Refer to Table 13.1, "Interrupt Summary," on page 140 for a detailed listing of all interrupt sources supported by the device. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR or an indirect register. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1. If both global interrupts and the specific interrupt source is enabled, a CPU interrupt request is generated when the interrupt-pending flag is set.

As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Some interrupt-pending flags are automatically cleared by hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

### 13.1. Enabling Interrupt Sources

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in the Interrupt Enable and Extended Interrupt Enable SFRs. However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings. Note that interrupts which occur when the EA bit is set to logic 0 will be held in a pending state, and will not be serviced until the EA bit is set back to logic 1.

### 13.2. MCU Interrupt Sources and Vectors

The CPU services interrupts by generating an LCALL to a predetermined address (the interrupt vector address) to begin execution of an interrupt service routine (ISR). The interrupt vector addresses associated with each interrupt source are listed in Table 13.1 on page 140. Software should ensure that the interrupt vector for each enabled interrupt source contains a valid interrupt service routine.

Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag.

### SFR Definition 14.4. FLKEY: Flash Lock and Key

| Bit   | 7             | 6                                                                                                                                                                                                                                  | 5                                                                                                                                                                             | 4                                                                                                                                                   | 3                                                                                                                                                   | 2                                                                                                            | 1                                                                                     | 0                                                                   |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Name  | ;             | FLKEY[7:0]                                                                                                                                                                                                                         |                                                                                                                                                                               |                                                                                                                                                     |                                                                                                                                                     |                                                                                                              |                                                                                       |                                                                     |

| Туре  |               |                                                                                                                                                                                                                                    |                                                                                                                                                                               | R                                                                                                                                                   | /W                                                                                                                                                  |                                                                                                              |                                                                                       |                                                                     |

| Reset | t 0           | 0                                                                                                                                                                                                                                  | 0                                                                                                                                                                             | 0                                                                                                                                                   | 0                                                                                                                                                   | 0                                                                                                            | 0                                                                                     | 0                                                                   |

| SFR P | age = All; SF | R Address =                                                                                                                                                                                                                        | 0xB7                                                                                                                                                                          | L                                                                                                                                                   |                                                                                                                                                     |                                                                                                              |                                                                                       | 1                                                                   |

| Bit   | Name          |                                                                                                                                                                                                                                    |                                                                                                                                                                               |                                                                                                                                                     | Function                                                                                                                                            |                                                                                                              |                                                                                       |                                                                     |

| 7:0   | FLKEY[7:0]    | Flash Lock                                                                                                                                                                                                                         | and Key Re                                                                                                                                                                    | gister.                                                                                                                                             |                                                                                                                                                     |                                                                                                              |                                                                                       |                                                                     |

|       |               | Write:                                                                                                                                                                                                                             |                                                                                                                                                                               |                                                                                                                                                     |                                                                                                                                                     |                                                                                                              |                                                                                       |                                                                     |

|       |               | This register<br>writes and ei<br>ter. Flash wri<br>complete. If a<br>operation is a<br>nently locked<br>never writes<br>FLKEY from<br>Read:<br>When read, I<br>00: Flash is o<br>01: The first<br>10: Flash is o<br>11: Flash wri | ases are en<br>tes and eras<br>any writes to<br>attempted w<br>from writes<br>to Flash, it c<br>software.<br>bits 1–0 indi-<br>write/erase li-<br>key code ha<br>unlocked (wr | abled by wr<br>ses are auto<br>FLKEY are<br>hile these of<br>or erasures<br>an intention<br>cate the curr<br>ocked.<br>s been writt<br>rites/erases | iting 0xA5 fol<br>matically dis<br>performed in<br>perations are<br>s until the nex<br>ally lock the l<br>rent Flash loc<br>en (0xA5).<br>allowed). | llowed by 02<br>abled after t<br>ncorrectly, or<br>disabled, t<br>xt device res<br>Flash by wri<br>ck state. | xF1 to the FL<br>the next write<br>r if a Flash wi<br>he Flash will<br>set. If an app | KEY regis-<br>or erase is<br>rite or erase<br>be perma-<br>lication |

### SFR Definition 19.4. OSCXCN: External Oscillator Control

| Bit   | 7       | 6   | 5           | 4   | 3   | 2         | 1   | 0   |  |

|-------|---------|-----|-------------|-----|-----|-----------|-----|-----|--|

| Name  | XCLKVLD | Х   | XOSCMD[2:0] |     |     | XFCN[2:0] |     |     |  |

| Туре  | R       | R/W | R/W         | R/W | R/W | R/W       | R/W | R/W |  |

| Reset | 0       | 0   | 0           | 0   | 0   | 0         | 0   | 0   |  |

SFR Page = 0x0; SFR Address = 0xB1

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | XCLKVLD  | External Oscillator Valid Flag.                                                                                                                                                                                                                                                                                                                           |

|     |          | <ul> <li>Provides External Oscillator status and is valid at all times for all modes of operation except External CMOS Clock Mode and External CMOS Clock Mode with divide by</li> <li>In these modes, XCLKVLD always returns 0.</li> <li>External Oscillator is unused or not yet stable.</li> <li>External Oscillator is running and stable.</li> </ul> |

| 6:4 | XOSCMD   | External Oscillator Mode Bits.                                                                                                                                                                                                                                                                                                                            |

|     |          | Configures the external oscillator circuit to the selected mode.<br>00x: External Oscillator circuit disabled.<br>010: External CMOS Clock Mode.<br>011: External CMOS Clock Mode with divide by 2 stage.<br>100: RC Oscillator Mode.<br>101: Capacitor Oscillator Mode.<br>110: Crystal Oscillator Mode.                                                 |

| 2   | Decerved | 111: Crystal Oscillator Mode with divide by 2 stage.                                                                                                                                                                                                                                                                                                      |

| 3   | Reserved | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                                                 |

| 2:0 | XFCN     | External Oscillator Frequency Control Bits.                                                                                                                                                                                                                                                                                                               |

|     |          | Controls the external oscillator bias current.<br>000-111: See Table 19.1 on page 190 (Crystal Mode) or Table 19.2 on page 191 (RC<br>or C Mode) for recommended settings.                                                                                                                                                                                |

### SFR Definition 20.1. RTC0KEY: SmaRTClock Lock and Key

| Bit   | 7 | 6           | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-------------|---|----|---|---|---|---|--|--|--|

| Name  |   | RTC0ST[7:0] |   |    |   |   |   |   |  |  |  |

| Туре  |   |             |   | R/ | W |   |   |   |  |  |  |

| Reset | 0 | 0           | 0 | 0  | 0 | 0 | 0 | 0 |  |  |  |

SFR Page = 0x0; SFR Address = 0xAE

| Bit | Name   | Function                                         |

|-----|--------|--------------------------------------------------|

| 7:0 | RTC0ST | SmaRTClock Interface Status.                     |

|     |        | Provides lock status when read.                  |

|     |        | Read:<br>0x02: SmaRTClock Interface is unlocked. |

|     |        | Write:<br>Writes to RTC0KEY have no effect.      |

### SFR Definition 21.1. XBR0: Port I/O Crossbar Register 0

| Bit   | 7   | 6   | 5     | 4    | 3      | 2     | 1     | 0     |

|-------|-----|-----|-------|------|--------|-------|-------|-------|

| Name  |     |     | CP0AE | CP0E | SYSCKE | SMB0E | SPI0E | URT0E |

| Туре  | R/W | R/W | R/W   | R/W  | R/W    | R/W   | R/W   | R/W   |

| Reset | 0   | 0   | 0     | 0    | 0      | 0     | 0     | 0     |

### SFR Page = 0x0; SFR Address = 0xE1

| Bit     | Name          | Function                                                                                                                                                                                                                            |

|---------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6     | Unused        | Read = 00b. Write = Don't Care.                                                                                                                                                                                                     |

| 5       | CP0AE         | Comparator0 Asynchronous Output Enable.<br>0: Asynchronous CP0 output unavailable at Port pin.<br>1: Asynchronous CP0 output routed to Port pin.                                                                                    |

| 4       | CP0E          | Comparator0 Output Enable.<br>0: CP1 output unavailable at Port pin.<br>1: CP1 output routed to Port pin.                                                                                                                           |

| 3       | SYSCKE        | SYSCLK Output Enable.         0: SYSCLK output unavailable at Port pin.         1: SYSCLK output routed to Port pin.                                                                                                                |

| 2       | SMB0E         | SMBus I/O Enable.<br>0: SMBus I/O unavailable at Port pin.<br>1: SDA and SCL routed to Port pins.                                                                                                                                   |

| 1       | SPIOE         | <ul> <li>SPI0 I/O Enable.</li> <li>0: SPI0 I/O unavailable at Port pin.</li> <li>1: SCK, MISO, and MOSI (for SPI0) routed to Port pins.<br/>NSS (for SPI0) routed to Port pin only if SPI0 is configured to 4-wire mode.</li> </ul> |

| 0       | URT0E         | UART0 Output Enable.<br>0: UART I/O unavailable at Port pin.<br>1: TX0 and RX0 routed to Port pins P0.4 and P0.5.                                                                                                                   |

| Note: S | SPI0 can be a | ssigned either 3 or 4 Port I/O pins.                                                                                                                                                                                                |

### SFR Definition 21.12. P0DRV: Port0 Drive Strength

| Bit                                | 7    | 6          | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|------------------------------------|------|------------|---|----|---|---|---|---|--|--|--|

| Nam                                | 9    | P0DRV[7:0] |   |    |   |   |   |   |  |  |  |

| Туре                               | •    |            |   | R/ | W |   |   |   |  |  |  |

| Rese                               | t 0  | 0          | 0 | 0  | 0 | 0 | 0 | 0 |  |  |  |

| SFR Page = 0xF; SFR Address = 0x99 |      |            |   |    |   |   |   |   |  |  |  |

| Bit                                | Name |            |   |    |   |   |   |   |  |  |  |

| 2.0 | Hamo       | i unotioni                                                                                                                                                                                             |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0DRV[7:0] | Drive Strength Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P0.n Output has low output drive strength.<br>1: Corresponding P0.n Output has high output drive strength. |

### SFR Definition 22.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7     | 6   | 5    | 4       | 3      | 2      | 1          | 0 |

|-------|-------|-----|------|---------|--------|--------|------------|---|

| Name  | ENSMB | INH | BUSY | EXTHOLD | SMBTOE | SMBFTE | SMBCS[1:0] |   |

| Туре  | R/W   | R/W | R    | R/W     | R/W    | R/W    | R/W        |   |

| Reset | 0     | 0   | 0    | 0       | 0      | 0      | 0          | 0 |

### SFR Page = 0x0; SFR Address = 0xC1

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENSMB      | SMBus Enable.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit enables the SMBus interface when set to 1. When enabled, the interface constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                                                                                                             |

| 6   | INH        | SMBus Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the SMBus does not generate an interrupt when slave events occur. This effectively removes the SMBus slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                    |

| 5   | BUSY       | SMBus Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                |

| 4   | EXTHOLD    | SMBus Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | This bit controls the SDA setup and hold times according to Table 22.2.<br>0: SDA Extended Setup and Hold Times disabled.<br>1: SDA Extended Setup and Hold Times enabled.                                                                                                                                                                                                                                                            |

| 3   | SMBTOE     | SMBus SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | This bit enables SCL low timeout detection. If set to logic 1, the SMBus forces<br>Timer 3 to reload while SCL is high and allows Timer 3 to count when SCL goes low.<br>If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in reload<br>while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms,<br>and the Timer 3 interrupt service routine should reset SMBus communication. |

| 2   | SMBFTE     | SMBus Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                              |

| 1:0 | SMBCS[1:0] | SMBus Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | These two bits select the SMBus clock source, which is used to generate the SMBus<br>bit rate. The selected device should be configured according to Equation 22.1.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10:Timer 2 High Byte Overflow                                                                                                                                                                                  |

|     |            | 11: Timer 2 Low Byte Overflow                                                                                                                                                                                                                                                                                                                                                                                                         |

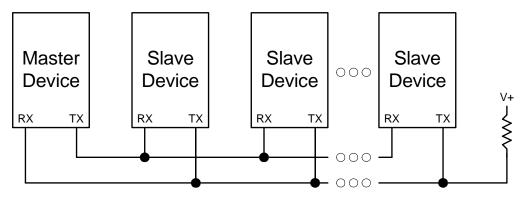

Figure 23.6. UART Multi-Processor Mode Interconnect Diagram

### 25.1. Timer 0 and Timer 1

Each timer is implemented as a 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register ("Interrupt Register Descriptions" on page 141); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register ("Interrupt Register Descriptions" on page 141). Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently. Each operating mode is described below.

#### 25.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 (TCON.5) is set and an interrupt will occur if Timer 0 interrupts are enabled.

The C/T0 bit (TMOD.2) selects the counter/timer's clock source. When C/T0 is set to logic 1, high-to-low transitions at the selected Timer 0 input pin (T0) increment the timer register (Refer to Section "21.3. Priority Crossbar Decoder" on page 219 for information on selecting and configuring external I/O pins). Clearing C/T selects the clock defined by the T0M bit (CKCON.3). When T0M is set, Timer 0 is clocked by the system clock. When T0M is cleared, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON (see SFR Definition 25.1).

Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see SFR Definition 13.7). Setting GATE0 to 1 allows the timer to be controlled by the external input signal INT0 (see Section "13.5. Interrupt Register Descriptions" on page 141), facilitating pulse width measurements

| TR0             | GATE0 | INTO     | Counter/Timer |

|-----------------|-------|----------|---------------|

| 0               | Х     | X X Disa |               |

| 1               | 0     | Х        | Enabled       |

| 1               | 1     | 0        | Disabled      |

| 1               | 1     | 1        | Enabled       |

| Note: X = Don't | Care  | ·        |               |

Table 25.1. Timer 0 Running Modes

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal INT1 is used with Timer 1; the INT1 polarity is defined by bit IN1PL in register IT01CF (see SFR Definition 13.7).

### SFR Definition 25.4. TL0: Timer 0 Low Byte

| Bit   | 7             | 6             | 5      | 4  | 3        | 2 | 1 | 0 |  |  |  |

|-------|---------------|---------------|--------|----|----------|---|---|---|--|--|--|

| Name  | 9             | TL0[7:0]      |        |    |          |   |   |   |  |  |  |

| Туре  |               |               |        | R/ | W        |   |   |   |  |  |  |

| Reset | <b>t</b> 0    | 0             | 0      | 0  | 0        | 0 | 0 | 0 |  |  |  |

| SFR P | age = 0x0; SI | FR Address :  | = 0x8A |    |          |   |   |   |  |  |  |

| Bit   | Name          |               |        |    | Function |   |   |   |  |  |  |

| 7.0   |               | Time or O L o | Durta  |    |          |   |   |   |  |  |  |

| 7:0 | TL0[7:0] | Timer 0 Low Byte.                                       |

|-----|----------|---------------------------------------------------------|

|     |          | The TL0 register is the low byte of the 16-bit Timer 0. |

### SFR Definition 25.5. TL1: Timer 1 Low Byte

| Bit   | 7                 | 6            | 5                | 4             | 3             | 2     | 1 | 0 |  |  |

|-------|-------------------|--------------|------------------|---------------|---------------|-------|---|---|--|--|

| Nam   | <b>e</b> TL1[7:0] |              |                  |               |               |       |   |   |  |  |

| Туре  | •                 | R/W          |                  |               |               |       |   |   |  |  |

| Rese  | et 0              | 0            | 0                | 0             | 0             | 0     | 0 | 0 |  |  |

| SFR F | Page = 0x0; SI    | FR Address = | = 0x8B           |               |               |       |   |   |  |  |

| Bit   | Name              |              |                  |               | Function      |       |   |   |  |  |

| 7:0   | TL1[7:0]          | Timer 1 Lo   | ïmer 1 Low Byte. |               |               |       |   |   |  |  |

|       |                   | The TL1 reg  | gister is the I  | ow byte of th | ie 16-bit Tim | er 1. |   |   |  |  |

### SFR Definition 25.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1           | 0 |

|-------|------|------|--------|--------|---------|-----|-------------|---|

| Name  | TF3H | TF3L | TF3LEN | TF3CEN | T3SPLIT | TR3 | T3XCLK[1:0] |   |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R/W         |   |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0           | 0 |

#### SFR Page = 0x0; SFR Address = 0x91

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | TF3H        | Timer 3 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|     |             | Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 6   | TF3L        | Timer 3 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|     |             | Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 5   | TF3LEN      | Timer 3 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|     |             | When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 4   | TF3CEN      | Timer 3 SmaRTClock/External Oscillator Capture Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|     |             | When set to 1, this bit enables Timer 3 Capture Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 3   | T3SPLIT     | Timer 3 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|     |             | When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|     |             | 0: Timer 3 operates in 16-bit auto-reload mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|     |             | 1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 2   | TR3         | Timer 3 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|     |             | Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 1:0 | T3XCLK[1:0] | Timer 3 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|     |             | This bit selects the "external" and "capture trigger" clock sources for Timer 3. If<br>Timer 3 is in 8-bit mode, this bit selects the "external" clock source for both timer<br>bytes. Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be<br>used to select between the "external" clock and the system clock for either timer.<br>Note: External clock sources are synchronized with the system clock.<br>00: External Clock is SYSCLK /12. Capture trigger is SmaRTClock.<br>01: External Clock is External Oscillator/8. Capture trigger is SmaRTClock.<br>10: External Clock is SYSCLK/12. Capture trigger is External Oscillator/8.<br>11: External Clock is SmaRTClock. Capture trigger is External Oscillator/8. |  |  |

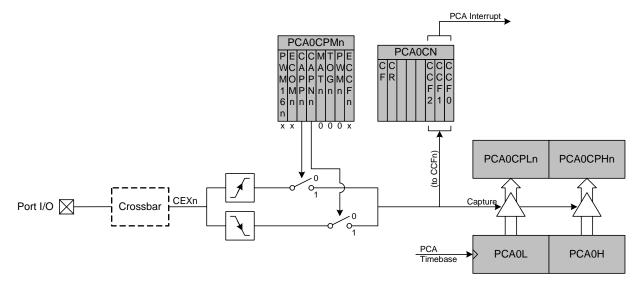

#### 26.3.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 26.4. PCA Capture Mode Diagram

Note: The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

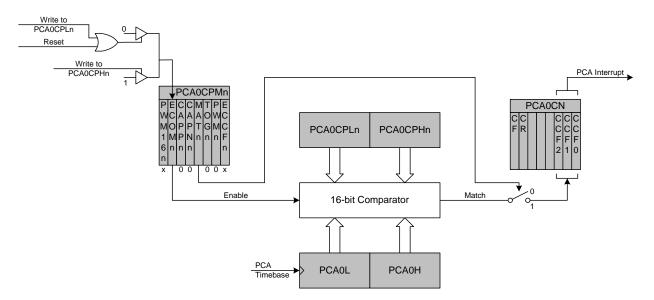

#### 26.3.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 26.5. PCA Software Timer Mode Diagram