Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                    |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 17                                                             |

| Program Memory Size        | 4KB (4K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 10x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-WFQFN Exposed Pad                                           |

| Supplier Device Package    | 24-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f988-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| OF 0.4.40 hit Time an with Auto Dalaged                             | 004 |

|---------------------------------------------------------------------|-----|

| 25.3.1.16-bit Timer with Auto-Reload                                |     |

| 25.3.2.8-Bit Timers with Auto-Reload                                |     |

| 25.3.3.SmaRTClock/External Oscillator Capture Mode                  | 296 |

| 26. Programmable Counter Array                                      | 300 |

| 26.1.PCA Counter/Timer                                              | 301 |

| 26.2.PCA0 Interrupt Sources                                         | 302 |

| 26.3.Capture/Compare Modules                                        | 303 |

| 26.3.1.Edge-triggered Capture Mode                                  | 304 |

| 26.3.2.Software Timer (Compare) Mode                                |     |

| 26.3.3.High-Speed Output Mode                                       | 306 |

| 26.3.4. Frequency Output Mode                                       | 306 |

| 26.3.5. 8-bit, 9-bit, 10-bit and 11-bit Pulse Width Modulator Modes | 307 |

| 26.3.6. 16-Bit Pulse Width Modulator Mode                           | 310 |

| 26.4.Watchdog Timer Mode                                            | 311 |

| 26.4.1.Watchdog Timer Operation                                     |     |

| 26.4.2.Watchdog Timer Usage                                         | 312 |

| 26.5.Register Descriptions for PCA0                                 | 313 |

| 27.C2 Interface                                                     |     |

| 27.1.C2 Interface Registers                                         | 319 |

| 27.2.C2 Pin Sharing                                                 |     |

| Document Change List                                                |     |

| Contact Information                                                 | 325 |

# 3. Pinout and Package Definitions

|                       | Pin                                                                        | Number                               | S                                    |                  |                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------|--------------------------------------|--------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name                  | <sup>•</sup> F980/1/2<br><sup>•</sup> F983/5<br><sup>•</sup> F990/1<br>-GM | 'F986/7<br>'F988/9<br>'F996/7<br>-GM | 'F986/7<br>'F988/9<br>'F996/7<br>-GU | Туре             | Description                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| V <sub>DD</sub>       | 4                                                                          | 3                                    | 6                                    | P In             | Power Supply Voltage. Must be 1.8 to 3.6 V.                                                                                                                                                                                                                                                                   |  |  |  |  |

| GND                   | 3, 12                                                                      | 2                                    | 5                                    | G                | Required Ground.                                                                                                                                                                                                                                                                                              |  |  |  |  |

| RST/                  | 5                                                                          | 6                                    | 9                                    | D I/O            | Device Reset. Open-drain output of internal POR or $V_D$ monitor. An external source can initiate a system reset by driving this pin low for at least 15 µs. A 1 k $\Omega$ to 5 k $\Omega$ pullup to $V_{DD}$ is recommended. See Section "18. Rese Sources" on page 181 Section for a complete description. |  |  |  |  |

| C2CK                  |                                                                            |                                      |                                      | D I/O            | Clock signal for the C2 Debug Interface.                                                                                                                                                                                                                                                                      |  |  |  |  |

| P2.7/                 | 6                                                                          | 7                                    | 10                                   | D I/O            | Port 2.7. This pin can only be used as GPIO. The<br>Crossbar cannot route signals to this pin and it cannot to<br>configured as an analog input. See Port I/O Section for<br>complete description.                                                                                                            |  |  |  |  |

| C2D                   |                                                                            |                                      |                                      | D I/O            | Bi-directional data signal for the C2 Debug Interface.                                                                                                                                                                                                                                                        |  |  |  |  |

| P1.6/                 | 8                                                                          | 9                                    | 12                                   | D I/O            | Port 1.6. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                    |  |  |  |  |

| XTAL3                 |                                                                            |                                      |                                      | A In             | SmaRTClock Oscillator Crystal Input.<br>See Section 20 for a complete description.                                                                                                                                                                                                                            |  |  |  |  |

| P1.7/                 | 7                                                                          | 8                                    | 11                                   | D I/O            | Port 1.7. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                    |  |  |  |  |

| XTAL4                 |                                                                            |                                      |                                      | A Out            | SmaRTClock Oscillator Crystal Output.<br>See Section 20 for a complete description.                                                                                                                                                                                                                           |  |  |  |  |

| P0.0/                 | 2                                                                          | 24                                   | 3                                    | D I/O or<br>A In | Port 0.0. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                    |  |  |  |  |

| V <sub>REF</sub> *    |                                                                            |                                      |                                      | A In             | External V <sub>REF</sub> Input.<br>See Section "5.9. Voltage and Ground Reference<br>Options" on page 88.                                                                                                                                                                                                    |  |  |  |  |

| * <b>Note:</b> Availa | ble only on t                                                              | he C805′                             | 1F980/2/6                            | 6/8 and C8       | 051F990/6 devices.                                                                                                                                                                                                                                                                                            |  |  |  |  |

## Table 3.1. Pin Definitions for the C8051F99x-C8051F98x

### Table 4.4. Reset Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameter                                                    | Conditions                                                                                 | Min                   | Тур     | Max                 | Units |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|---------|---------------------|-------|

| RST Output Low Voltage                                       | I <sub>OL</sub> = 1.4 mA,                                                                  | _                     | _       | 0.6                 | V     |

| RST Input High Voltage                                       | V <sub>DD</sub> = 12.0 to 3.6 V                                                            | V <sub>DD</sub> – 0.6 |         | _                   | V     |

|                                                              | $V_{DD}$ = 10.9 to 2.0 V                                                                   | $0.7 \times V_{DD}$   | _       | —                   | V     |

| RST Input Low Voltage                                        | V <sub>DD</sub> = 12.0 to 3.6 V                                                            | _                     | _       | 0.6                 | V     |

|                                                              | V <sub>DD</sub> = 10.9 to 2.0 V                                                            | —                     | _       | $0.3 \times V_{DD}$ | V     |

| RST Input Pullup Current                                     | <del>RST</del> = 10.0 V, V <sub>DD</sub> = 1.8 V<br>RST = 10.0 V, V <sub>DD</sub> = 13.6 V | _                     | 4<br>20 | —<br>30             | μA    |

| V <sub>DD</sub> Monitor Threshold                            | Early Warning                                                                              | 1.8                   | 1.85    | 1.9                 | V     |

| (V <sub>RST</sub> )                                          | Reset Trigger<br>(all power modes except Sleep)                                            | 1.7                   | 1.75    | 1.8                 |       |

| V <sub>DD</sub> Ramp Time for Power<br>On                    | V <sub>DD</sub> Ramp from 0–1.8 V                                                          | _                     |         | 3                   | ms    |

| POR Monitor Threshold                                        | Brownout Condition (V <sub>DD</sub> Falling)                                               | 0.75                  | 1.0     | 1.3                 | V     |

| (V <sub>POR</sub> )                                          | Recovery from Brownout (V <sub>DD</sub> Rising)                                            |                       | 1.75    |                     | v     |

| Missing Clock Detector<br>Timeout                            | Time from last system clock rising edge to reset initiation                                | 100                   | 650     | 1000                | μs    |

| Minimum System Clock w/<br>Missing Clock Detector<br>Enabled | System clock frequency which triggers<br>a missing clock detector timeout                  | _                     | 7       | 10                  | kHz   |

| Reset Time Delay                                             | Delay between release of any reset<br>source and code<br>execution at location 0x0000      | _                     | 10      | _                   | μs    |

| Minimum $\overline{RST}$ Low Time to Generate a System Reset |                                                                                            | 15                    | _       | _                   | μs    |

| V <sub>DD</sub> Monitor Turn-on Time                         |                                                                                            | _                     | 300     | _                   | ns    |

| V <sub>DD</sub> Monitor Supply<br>Current                    |                                                                                            | _                     | 7       | _                   | μA    |

# SFR Definition 5.2. ADC0CF: ADC0 Configuration

| Bit   | 7               | 6                                                                                              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4            | 3           | 2       | 1   | 0 |  |  |  |  |  |

|-------|-----------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|---------|-----|---|--|--|--|--|--|

| Nam   | e               | AD0SC[4:0] AD08BE AD0TM AMP                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |             |         |     |   |  |  |  |  |  |

| Туре  | •               |                                                                                                | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | R/W         | R/W     | R/W |   |  |  |  |  |  |

| Rese  | t 1             | 1                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1            | 1           | 0       | 0   | 0 |  |  |  |  |  |

| SFR F | age = 0x0; SI   | R Address =                                                                                    | = 0x97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |             | •       |     |   |  |  |  |  |  |

| Bit   | Name            |                                                                                                | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |             |         |     |   |  |  |  |  |  |

| 7:3   | AD0SC[4:0]      | SAR Conve<br>AD0SC refe<br>requiremen<br>BURSTEN<br>BURSTEN<br>clock.<br>AD0SC =<br>*Round the | ADC0 SAR Conversion Clock Divider.<br>SAR Conversion clock is derived from FCLK by the following equation, where<br><i>AD0SC</i> refers to the 5-bit value held in bits AD0SC[4:0]. SAR Conversion clock<br>requirements are given in Table 4.10.<br>BURSTEN = 0: FCLK is the current system clock.<br>BURSTEN = 1: FCLK is the 20 MHz low power oscillator, independent of the system<br>clock.<br>$AD0SC = \frac{FCLK}{CLK_{SAR}} - 1 *$<br>*Round the result up.<br>or<br>$CLK_{SAR} = \frac{FCLK}{AD0SC + 1}$ |              |             |         |     |   |  |  |  |  |  |

| 2     | AD08BE          | 0: ADC0 op                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -bit mode (n | ormal opera | ation). |     |   |  |  |  |  |  |

| 1     | AD0TM<br>AMP0GN | Selects betw<br>0: Normal T<br>lowing the s<br>1: Delayed<br>cycles follow<br>this time.       | ADC0 operates in 8-bit mode.     ADC0 Track Mode.     Selects between Normal or Delayed Tracking Modes.     Normal Track Mode: When ADC0 is enabled, conversion begins immediately fol-<br>owing the start-of-conversion signal.     Delayed Track Mode: When ADC0 is enabled, conversion begins 3 SAR clock cycles following the start-of-conversion signal. The ADC is allowed to track during his time.     ADC0 Gain Control.                                                                                 |              |             |         |     |   |  |  |  |  |  |

|       |                 | 0: The on-c                                                                                    | hip PGA gai<br>hip PGA gai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |             |         |     |   |  |  |  |  |  |

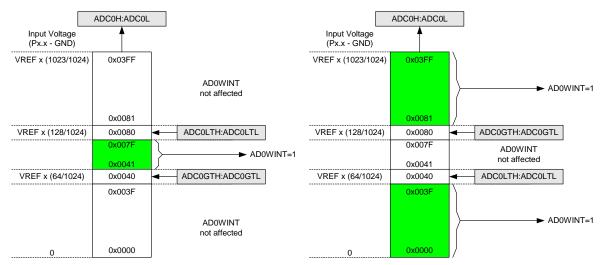

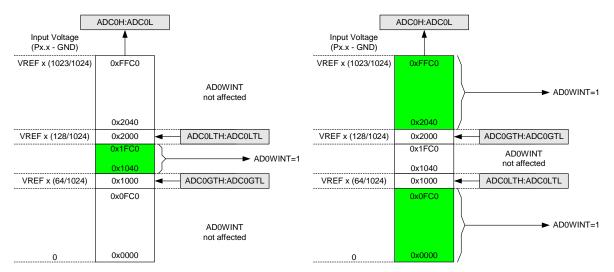

#### 5.6.1. Window Detector In Single-Ended Mode

Figure 5.5 shows two example window comparisons for right-justified data. with ADC0LTH:ADC0LTL = 0x0080 (128d) and ADC0GTH:ADC0GTL = 0x0040 (64d). The input voltage can range from 0 to VREF x (1023/1024) with respect to GND, and is represented by a 10-bit unsigned integer value. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0040 < ADC0H:ADC0L < 0x0080). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0040 or ADC0H:ADC0L > 0x0080). Figure 5.6 shows an example using leftjustified data with the same comparison values.

Figure 5.5. ADC Window Compare Example: Right-Justified Single-Ended Data

Figure 5.6. ADC Window Compare Example: Left-Justified Single-Ended Data

#### 5.6.2. ADC0 Specifications

See "4. Electrical Characteristics" on page 48 for a detailed listing of ADC0 specifications.

# 7. Comparator

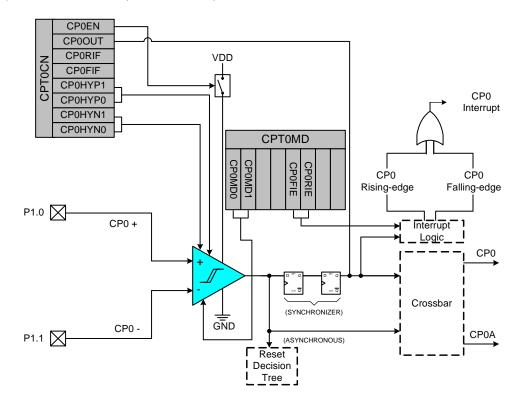

C8051F99x-C8051F98x devices include an on-chip programmable voltage comparator: Comparator 0 (CPT0) shown in Figure 7.1.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a digital synchronous "latched" output (CP0), or a digital asynchronous "raw" output (CP0A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output when the device is in some low power modes.

#### 7.1. Comparator Inputs

Each Comparator performs an analog comparison of the voltage levels at its positive (CP0+) and negative (CP0-) input. The analog input multiplexers are completely under software control and configured using SFR registers. See Section "7.6. Comparator0 Analog Multiplexer" on page 98 for details on how to select and configure Comparator inputs.

**Important Note About Comparator Inputs:** The Port pins selected as Comparator inputs should be configured as analog inputs and skipped by the Crossbar. See the Port I/O chapter for more details on how to configure Port I/O pins as Analog Inputs. The Comparator may also be used to compare the logic level of digital signals, however, Port I/O pins configured as digital inputs must be driven to a valid logic state (HIGH or LOW) to avoid increased power consumption.

Figure 7.1. Comparator 0 Functional Block Diagram

## SFR Definition 8.5. CS0SCAN0: Capacitive Sense Channel Scan Mask 0

| Bit   | 7   | 6             | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------|-----|---------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Name  |     | CS0SCAN0[7:0] |     |     |     |     |     |     |  |  |  |

| Туре  | R/W | R/W           | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Reset | 0   | 0             | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

SFR Page = 0x0; SFR Address = 0xD2

| Bit | Name         | Description                                                                                     |  |  |  |  |  |

|-----|--------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0 | CS0SCAN[7:0] | Capacitive Sense Channel Scan Mask for Port 0.                                                  |  |  |  |  |  |

|     |              | The selected channels are included in the Auto Scan when scan masking is enabled (CS0SMEN = 1). |  |  |  |  |  |

### SFR Definition 8.6. CS0SCAN1: Capacitive Sense Channel Scan Mask 1

| Bit   | 7 | 6 | 5   | 4            | 3   | 2   | 1   | 0   |  |  |

|-------|---|---|-----|--------------|-----|-----|-----|-----|--|--|

| Name  |   |   |     | CS0SCAN[5:0] |     |     |     |     |  |  |

| Туре  | R | R | R/W | R/W          | R/W | R/W | R/W | R/W |  |  |

| Reset | 0 | 0 | 0   | 0            | 0   | 0   | 0   | 0   |  |  |

SFR Page = 0x0; SFR Address = 0xD3

| Bit | Name         | Description                                                                                     |  |  |  |  |  |

|-----|--------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:6 | Unused       | Read = 00b; Write = Don't care                                                                  |  |  |  |  |  |

| 5:0 | CS0SCAN[5:0] | pacitive Sense Channel Scan Mask for Port 0.                                                    |  |  |  |  |  |

|     |              | The selected channels are included in the Auto Scan when scan masking is enabled (CS0SMEN = 1). |  |  |  |  |  |

# SFR Definition 9.6. PSW: Program Status Word

| Bit   | 7                                                   | 6                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                             | 3             | 2              | 1              | 0           |  |  |  |  |  |

|-------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|----------------|----------------|-------------|--|--|--|--|--|

| Nam   | e CY                                                | AC                                                                                                     | F0                                                                                                                                                                                                                                                                                                                                                                                                                                   | RS                            | [1:0]         | OV             | F1             | PARITY      |  |  |  |  |  |

| Туре  | R/W                                                 | R/W                                                                                                    | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/                            | /W            | R/W            | R/W            | R           |  |  |  |  |  |

| Rese  | et O                                                | 0                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                             | 0             | 0              | 0              | 0           |  |  |  |  |  |

| SFR F | SFR Page = All; SFR Address = 0xD0; Bit-Addressable |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               |               |                |                |             |  |  |  |  |  |

| Bit   | Bit Name Function                                   |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               |               |                |                |             |  |  |  |  |  |

| 7     | CY                                                  |                                                                                                        | Carry Flag.<br>This bit is set when the last arithmetic operation resulted in a carry (addition) or a bor-<br>row (subtraction). It is cleared to logic 0 by all other arithmetic operations.                                                                                                                                                                                                                                        |                               |               |                |                |             |  |  |  |  |  |

| 6     | AC                                                  | This bit is set<br>borrow from (s                                                                      | Auxiliary Carry Flag.<br>This bit is set when the last arithmetic operation resulted in a carry into (addition) or a<br>porrow from (subtraction) the high order nibble. It is cleared to logic 0 by all other arith-<br>netic operations.                                                                                                                                                                                           |                               |               |                |                |             |  |  |  |  |  |

| 5     | F0                                                  | <b>User Flag 0.</b><br>This is a bit-ad                                                                | ddressable,                                                                                                                                                                                                                                                                                                                                                                                                                          | general purp                  | ose flag for  | use under so   | oftware contr  | ol.         |  |  |  |  |  |

| 4:3   | RS[1:0]                                             | Register Ban<br>These bits sel<br>00: Bank 0, Ao<br>01: Bank 1, Ao<br>10: Bank 2, Ao<br>11: Bank 3, Ao | ect which re<br>ddresses 0x<br>ddresses 0x<br>ddresses 0x                                                                                                                                                                                                                                                                                                                                                                            | 00-0x07<br>08-0x0F<br>10-0x17 | s used durin  | ig register ac | cesses.        |             |  |  |  |  |  |

| 2     | OV                                                  | This bit is set<br>• An ADD,<br>• A MUL in<br>• A DIV ins                                              | <ul> <li>Overflow Flag.</li> <li>This bit is set to 1 under the following circumstances: <ul> <li>An ADD, ADDC, or SUBB instruction causes a sign-change overflow.</li> <li>A MUL instruction results in an overflow (result is greater than 255).</li> <li>A DIV instruction causes a divide-by-zero condition.</li> </ul> </li> <li>The OV bit is cleared to 0 by the ADD, ADDC, SUBB, MUL, and DIV instructions in all</li> </ul> |                               |               |                |                |             |  |  |  |  |  |

| 1     | F1                                                  | <b>User Flag 1.</b><br>This is a bit-ad                                                                | ddressable,                                                                                                                                                                                                                                                                                                                                                                                                                          | general purp                  | ose flag for  | use under so   | oftware contr  | ol.         |  |  |  |  |  |

| 0     | PARITY                                              | <b>Parity Flag.</b><br>This bit is set t<br>if the sum is e                                            | •                                                                                                                                                                                                                                                                                                                                                                                                                                    | ne sum of the                 | eight bits in | the accumu     | lator is odd a | and cleared |  |  |  |  |  |

#### Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register | Address | SFR Page | Description                       | Page |

|----------|---------|----------|-----------------------------------|------|

| P1SKIP   | 0xD5    | 0x0      | Port 1 Skip                       | 231  |

| P2       | 0xA0    | All      | Port 2 Latch                      | 233  |

| P2DRV    | 0x9D    | 0xF      | Port 2 Drive Strength             | 234  |

| P2MDOUT  | 0xA6    | 0x0      | Port 2 Output Mode Configuration  | 234  |

| PCA0CN   | 0xD8    | 0x0      | PCA0 Control                      | 313  |

| PCA0CPH0 | 0xFC    | 0x0      | PCA0 Capture 0 High               | 318  |

| PCA0CPH1 | 0xEA    | 0x0      | PCA0 Capture 1 High               | 318  |

| PCA0CPH2 | 0xEC    | 0x0      | PCA0 Capture 2 High               | 318  |

| PCA0CPL0 | 0xFB    | 0x0      | PCA0 Capture 0 Low                | 318  |

| PCA0CPL1 | 0xE9    | 0x0      | PCA0 Capture 1 Low                | 318  |

| PCA0CPL2 | 0xEB    | 0x0      | PCA0 Capture 2 Low                | 318  |

| PCA0CPM0 | 0xDA    | 0x0      | PCA0 Module 0 Mode Register       | 316  |

| PCA0CPM1 | 0xDB    | 0x0      | PCA0 Module 1 Mode Register       | 316  |

| PCA0CPM2 | 0xDC    | 0x0      | PCA0 Module 2 Mode Register       | 316  |

| PCA0H    | 0xFA    | 0x0      | PCA0 Counter High                 | 317  |

| PCA0L    | 0xF9    | 0x0      | PCA0 Counter Low                  | 317  |

| PCA0MD   | 0xD9    | 0x0      | PCA0 Mode                         | 314  |

| PCA0PWM  | 0xDF    | 0x0      | PCA0 PWM Configuration            | 315  |

| PCON     | 0x87    | All      | Power Control                     | 171  |

| PMU0CF   | 0xB5    | 0x0      | PMU0 Configuration                | 168  |

| PMU0FL   | 0xCE    | 0x0      | PMU0 Flag Register                | 169  |

| PMU0MD   | 0xB5    | 0xF      | PMU0 Mode                         | 170  |

| PSCTL    | 0x8F    | All      | Program Store R/W Control         | 159  |

| PSW      | 0xD0    | All      | Program Status Word               | 127  |

| REF0CN   | 0xD1    | 0x0      | Voltage Reference Control         | 90   |

| REG0CN   | 0xC9    | 0x0      | Voltage Regulator (REG0) Control  | 180  |

| REVID    | 0xE2    | 0xF      | Revision ID                       | 155  |

| RSTSRC   | 0xEF    | 0x0      | Reset Source Configuration/Status | 187  |

| RTC0ADR  | 0xAC    | 0x0      | RTC0 Address                      | 202  |

| RTC0DAT  | 0xAD    | 0x0      | RTC0 Data                         | 202  |

| RTC0KEY  | 0xAE    | 0x0      | RTC0 Key                          | 201  |

| SBUF0    | 0x99    | 0x0      | UART0 Data Buffer                 | 263  |

| SCON0    | 0x98    | 0x0      | UART0 Control                     | 262  |

| SFRPAGE  | 0xA7    | All      | SFR Page                          | 134  |

| SMB0ADM  | 0xF5    | 0x0      | SMBus Slave Address Mask          | 247  |

| SMB0ADR  | 0xF4    | 0x0      | SMBus Slave Address               | 247  |

| SMB0CF   | 0xC1    | 0x0      | SMBus0 Configuration              | 242  |

| SMB0CN   | 0xC0    | 0x0      | SMBus0 Control                    | 244  |

| SMB0DAT  | 0xC2    | 0x0      | SMBus0 Data                       | 248  |

| SP       | 0x81    | All      | Stack Pointer                     | 126  |

| SPI0CFG  | 0xA1    | 0x0      | SPI0 Configuration                | 272  |

| SPI0CKR  | 0xA2    | 0x0      | SPI0 Clock Rate Control           | 274  |

| SPI0CN   | 0xF8    | 0x0      | SPI0 Control                      | 273  |

| SPI0DAT  | 0xA3    | 0x0      | SPI0 Data                         | 274  |

# 13. Interrupt Handler

The C8051F99x-C8051F98x microcontroller family includes an extended interrupt system supporting multiple interrupt sources and two priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Refer to Table 13.1, "Interrupt Summary," on page 140 for a detailed listing of all interrupt sources supported by the device. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR or an indirect register. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1. If both global interrupts and the specific interrupt source is enabled, a CPU interrupt request is generated when the interrupt-pending flag is set.

As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Some interrupt-pending flags are automatically cleared by hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

### 13.1. Enabling Interrupt Sources

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in the Interrupt Enable and Extended Interrupt Enable SFRs. However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings. Note that interrupts which occur when the EA bit is set to logic 0 will be held in a pending state, and will not be serviced until the EA bit is set back to logic 1.

#### 13.2. MCU Interrupt Sources and Vectors

The CPU services interrupts by generating an LCALL to a predetermined address (the interrupt vector address) to begin execution of an interrupt service routine (ISR). The interrupt vector addresses associated with each interrupt source are listed in Table 13.1 on page 140. Software should ensure that the interrupt vector for each enabled interrupt source contains a valid interrupt service routine.

Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag.

## SFR Definition 16.4. CRC0AUTO: CRC0 Automatic Control

| Bit   | 7      | 6       | 5 | 4           | 3 | 2 | 1 | 0 |  |

|-------|--------|---------|---|-------------|---|---|---|---|--|

| Name  | AUTOEN | CRCDONE |   | CRC0ST[4:0] |   |   |   |   |  |

| Туре  | R/W    | R       | R | R/W         |   |   |   |   |  |

| Reset | 0      | 1       | 0 | 0           | 0 | 0 | 0 | 0 |  |

#### SFR Page = All; SFR Address = 0x9E

| Bit | Name        | Function                                                                                                                                                                                                                                |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AUTOEN      | Automatic CRC Calculation Enable.                                                                                                                                                                                                       |

|     |             | When AUTOEN is set to 1, any write to CRC0CN will initiate an automatic CRC starting at Flash sector CRC0ST and continuing for CRC0CNT sectors.                                                                                         |

| 6   | CRCDONE     | CRCDONE Automatic CRC Calculation Complete.                                                                                                                                                                                             |

|     |             | Set to 0 when a CRC calculation is in progress. Code execution is stopped during a CRC calculation; therefore, reads from firmware will always return 1.                                                                                |

| 5   | Unused      | Read = 0b; Write = Don't Care.                                                                                                                                                                                                          |

| 4:0 | CRC0ST[4:0] | Automatic CRC Calculation Starting Block.                                                                                                                                                                                               |

|     |             | These bits specify the Flash block to start the automatic CRC calculation. The starting address of the first Flash block included in the automatic CRC calculation is CRC0ST x Block Size.<br><b>Note:</b> The block size is 256 bytes. |

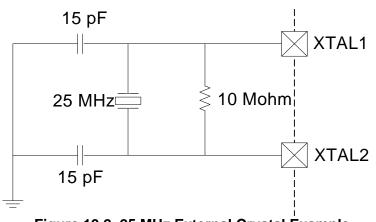

Figure 19.2. 25 MHz External Crystal Example

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

When using an external crystal, the external oscillator drive circuit must be configured by software for *Crystal Oscillator Mode* or *Crystal Oscillator Mode with divide by 2 stage*. The divide by 2 stage ensures that the clock derived from the external oscillator has a duty cycle of 50%. The External Oscillator Frequency Control value (XFCN) must also be specified based on the crystal frequency. The selection should be based on Table 19.1. For example, a 25 MHz crystal requires an XFCN setting of 111b.

| XFCN | Crystal Frequency                         | Bias Current | Typical Supply Current<br>(VDD = 2.4 V) |

|------|-------------------------------------------|--------------|-----------------------------------------|

| 000  | f ≤ 20 kHz                                | 0.5 µA       | 3.0 μA, f = 32.768 kHz                  |

| 001  | 20 kHz < f ≤ 58 kHz                       | 1.5 µA       | 4.8 μA, f = 32.768 kHz                  |

| 010  | 58 kHz < f ≤ 155 kHz                      | 4.8 µA       | 9.6 μA, f = 32.768 kHz                  |

| 011  | 155 kHz < f ≤ 415 kHz                     | 14 µA        | 28 µA, f = 400 kHz                      |

| 100  | 415 kHz $<$ f $\leq$ 1.1 MHz              | 40 µA        | 71 µA, f = 400 kHz                      |

| 101  | $1.1 \text{ MHz} < f \le 3.1 \text{ MHz}$ | 120 µA       | 193 µA, f = 400 kHz                     |

| 110  | $3.1 \text{ MHz} < f \le 8.2 \text{ MHz}$ | 550 µA       | 940 µA, f = 8 MHz                       |

| 111  | 8.2 MHz < f ≤ 25 MHz                      | 2.6 mA       | 3.9 mA, f = 25 MHz                      |

Table 19.1. Recommended XFCN Settings for Crystal Mode

When the crystal oscillator is first enabled, the external oscillator valid detector allows software to determine when the external system clock has stabilized. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure for starting the crystal is as follows:

- 1. Configure XTAL1 and XTAL2 for analog I/O and disable the digital output drivers.

- 2. Configure and enable the external oscillator.

- 3. Poll for XTLVLD  $\geq$  1.

- 4. Switch the system clock to the external oscillator.

| Mode           | Setting                  | Power<br>Consumption |

|----------------|--------------------------|----------------------|

| Crystal        | Bias Double Off, AGC On  | Lowest<br>600 nA     |

|                | Bias Double Off, AGC Off | Low<br>800 nA        |

|                | Bias Double On, AGC On   | High                 |

|                | Bias Double On, AGC Off  | Highest              |

| Self-Oscillate | Bias Double Off          | Low                  |

|                | Bias Double On           | High                 |

# Table 20.3. SmaRTClock Bias Settings

Registers XBR0, XBR1, and XBR2 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when either UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

#### Notes:

- 1. The Crossbar must be enabled (XBARE = 1) before any Port pin is used as a digital output. Port output drivers are disabled while the Crossbar is disabled.

- 2. When SMBus is selected in the Crossbar, the pins associated with SDA and SCL will automatically be forced into open-drain output mode regardless of the PnMDOUT setting.

- 3. SPI0 can be operated in either 3-wire or 4-wire modes, depending on the state of the NSSMD1-NSSMD0 bits in register SPI0CN. The NSS signal is only routed to a Port pin when 4-wire mode is selected. When SPI0 is selected in the Crossbar, the SPI0 mode (3-wire or 4-wire) will affect the pinout of all digital functions lower in priority than SPI0.

- 4. For given XBRn, PnSKIP, and SPInCN register settings, one can determine the I/O pin-out of the device using Figure 21.3.

- 5. On 20-pin devices, P1.4 should be skipped in the Crossbar. It is not available as a device pin.

## SFR Definition 21.8. P0: Port0

| Bit   | 7       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|

| Name  | P0[7:0] |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |   |   |   |   |   |  |  |

| Туре  |         | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   |   |   |   |  |  |

| Reset | 1       | 1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 |   |   |   |   |   |   |  |  |

SFR Page = All; SFR Address = 0x80; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW. |

### SFR Definition 21.9. P0SKIP: Port0 Skip

| Bit   | 7           | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-------------|-----------------|---|---|---|---|---|---|--|--|

| Name  | P0SKIP[7:0] |                 |   |   |   |   |   |   |  |  |

| Туре  |             | R/W             |   |   |   |   |   |   |  |  |

| Reset | 0           | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |

#### SFR Page= 0x0; SFR Address = 0xD4

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0SKIP[7:0] | Port 0 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 0 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P0.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P0.n pin is skipped by the Crossbar.</li> </ul> |

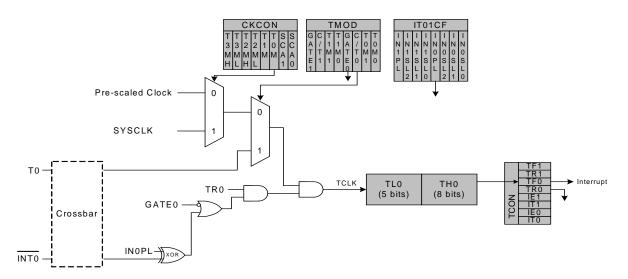

Figure 25.1. T0 Mode 0 Block Diagram

#### 25.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

## SFR Definition 25.6. TH0: Timer 0 High Byte

|               |                | T                |          |   |   |   |   |   |

|---------------|----------------|------------------|----------|---|---|---|---|---|

| Bit           | 7              | 6                | 5        | 4 | 3 | 2 | 1 | 0 |

| Name TH0[7:0] |                |                  |          |   |   |   |   |   |

| Type R/W      |                |                  |          |   |   |   |   |   |

| Rese          | et 0           | 0                | 0        | 0 | 0 | 0 | 0 | 0 |

| SFR F         | Page = 0x0; SI | -<br>R Address = | = 0x8C   |   |   |   |   |   |

| Bit           | Name           | Function         |          |   |   |   |   |   |

| 7:0           | TH0[7:0]       | Timer 0 Hig      | jh Byte. |   |   |   |   |   |

## SFR Definition 25.7. TH1: Timer 1 High Byte

| Bit   | 7              | 6                                                        | 5      | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|----------------|----------------------------------------------------------|--------|---|---|---|---|---|--|--|--|

| Nam   | e              | TH1[7:0]                                                 |        |   |   |   |   |   |  |  |  |

| Туре  | Type R/W       |                                                          |        |   |   |   |   |   |  |  |  |

| Rese  | et O           | 0                                                        | 0      | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR F | Page = 0x0; SI | R Address :                                              | = 0x8D |   |   |   |   |   |  |  |  |

| Bit   | Name           | Name Function                                            |        |   |   |   |   |   |  |  |  |

| 7:0   | TH1[7:0]       | Timer 1 High Byte.                                       |        |   |   |   |   |   |  |  |  |

|       |                | The TH1 register is the high byte of the 16-bit Timer 1. |        |   |   |   |   |   |  |  |  |

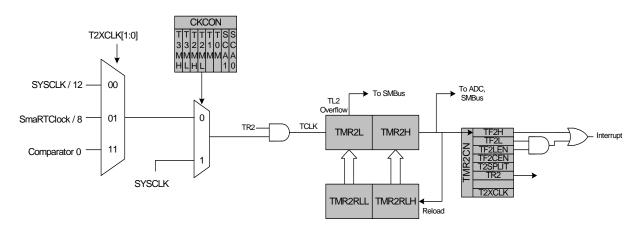

### 25.2. Timer 2

Timer 2 is a 16-bit timer formed by two 8-bit SFRs: TMR2L (low byte) and TMR2H (high byte). Timer 2 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T2SPLIT bit (TMR2CN.3) defines the Timer 2 operation mode. Timer 2 can also be used in Capture Mode to measure the SmaRTClock or the Comparator 0 period with respect to another oscillator. The ability to measure the Comparator 0 period with respect to the system clock is makes using Touch Sense Switches very easy.

Timer 2 may be clocked by the system clock, the system clock divided by 12, SmaRTClock divided by 8, or Comparator 0 output. Note that the SmaRTClock divided by 8 and Comparator 0 output is synchronized with the system clock.

#### 25.2.1. 16-bit Timer with Auto-Reload

When T2SPLIT (TMR2CN.3) is zero, Timer 2 operates as a 16-bit timer with auto-reload. Timer 2 can be clocked by SYSCLK, SYSCLK divided by 12, SmaRTClock divided by 8, or Comparator 0 output. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 2 reload registers (TMR2RLH and TMR2RLL) is loaded into the Timer 2 register as shown in Figure 25.4, and the Timer 2 High Byte Overflow Flag (TMR2CN.7) is set. If Timer 2 interrupts are enabled (if IE.5 is set), an interrupt will be generated on each Timer 2 overflow. Additionally, if Timer 2 interrupts are enabled and the TF2LEN bit is set (TMR2CN.5), an interrupt will be generated each time the lower 8 bits (TMR2L) overflow from 0xFF to 0x00.

Figure 25.4. Timer 2 16-Bit Mode Block Diagram

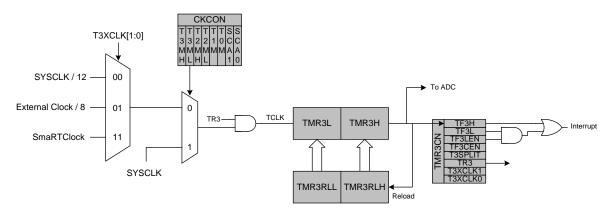

### 25.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T3SPLIT bit (TMR2CN.3) defines the Timer 3 operation mode. Timer 3 can also be used in Capture Mode to measure the external oscillator source or the SmaRTClock oscillator period with respect to another oscillator.

Timer 3 may be clocked by the system clock, the system clock divided by 12, external oscillator source divided by 8, or the SmaRTClock oscillator. The external oscillator source divided by 8 and SmaRTClock oscillator is synchronized with the system clock.

#### 25.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, external oscillator clock source divided by 8, or SmaRTClock oscillator. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TMR3RLL) is loaded into the Timer 3 register as shown in Figure 25.7, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x00.

Figure 25.7. Timer 3 16-Bit Mode Block Diagram