Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                     |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 4KB (4K × 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 10x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                            |

| Supplier Device Package    | 24-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f988-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

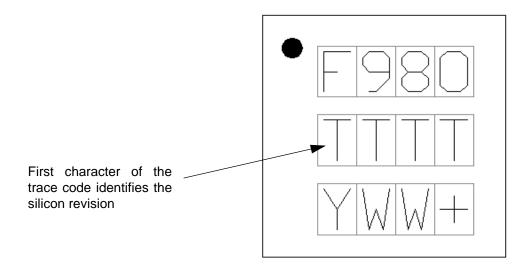

Figure 3.4. QFN-20 Package Marking Diagram

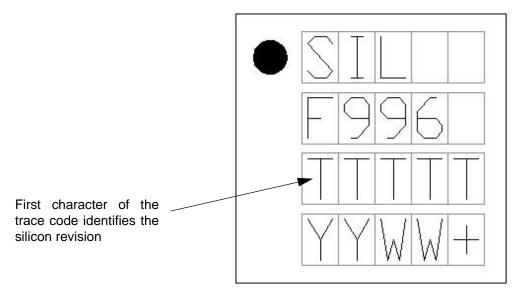

Figure 3.5. QFN-24 Package Marking Diagram

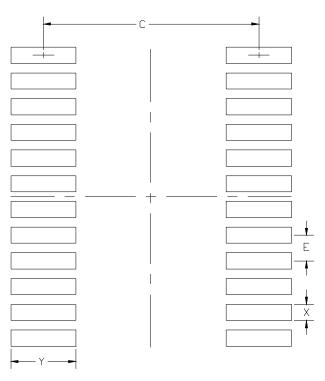

### Table 3.7. PCB Land Pattern

| Dimension | MIN   | MAX  |  |

|-----------|-------|------|--|

| С         | 5.20  | 5.30 |  |

| E         | 0.635 | BSC  |  |

| X         | 0.30  | 0.40 |  |

| Y         | 1.50  | 1.60 |  |

#### Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

3. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

#### Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## SFR Definition 5.1. ADC0CN: ADC0 Control

| Bit   | 7     | 6       | 5      | 4       | 3       | 2           | 1 | 0 |

|-------|-------|---------|--------|---------|---------|-------------|---|---|

| Name  | AD0EN | BURSTEN | AD0INT | AD0BUSY | AD0WINT | ADC0CM[2:0] |   |   |

| Туре  | R/W   | R/W     | R/W    | W       | R/W     | R/W         |   |   |

| Reset | 0     | 0       | 0      | 0       | 0       | 0           | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xE8; bit-addressable;

| Bit | Name        | Function                                                                                                                                                                                 |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AD0EN       | ADC0 Enable.                                                                                                                                                                             |

|     |             | 0: ADC0 Disabled (low-power shutdown).<br>1: ADC0 Enabled (active and ready for data conversions).                                                                                       |

| 6   | BURSTEN     | ADC0 Burst Mode Enable.<br>0: ADC0 Burst Mode Disabled.                                                                                                                                  |

|     |             | 1: ADC0 Burst Mode Enabled.                                                                                                                                                              |

| 5   | AD0INT      | ADC0 Conversion Complete Interrupt Flag.                                                                                                                                                 |

|     |             | Set by hardware upon completion of a data conversion (BURSTEN=0), or a burst of conversions (BURSTEN=1). Can trigger an interrupt. Must be cleared by software.                          |

| 4   | AD0BUSY     | ADC0 Busy.                                                                                                                                                                               |

|     |             | Writing 1 to this bit initiates an ADC conversion when ADC0CM[2:0] = 000.                                                                                                                |

| 3   | AD0WINT     | ADC0 Window Compare Interrupt Flag.                                                                                                                                                      |

|     |             | Set by hardware when the contents of ADC0H:ADC0L fall within the window speci-<br>fied by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL. Can trigger an interrupt.<br>Must be cleared by software. |

| 2:0 | ADC0CM[2:0] | ADC0 Start of Conversion Mode Select.                                                                                                                                                    |

|     |             | Specifies the ADC0 start of conversion source.                                                                                                                                           |

|     |             | 000: ADC0 conversion initiated on write of 1 to AD0BUSY.<br>001: ADC0 conversion initiated on overflow of Timer 0.                                                                       |

|     |             | 010: ADC0 conversion initiated on overflow of Timer 0.                                                                                                                                   |

|     |             | 011: ADC0 conversion initiated on overflow of Timer 3.                                                                                                                                   |

|     |             | 1xx: ADC0 conversion initiated on rising edge of CNVSTR.                                                                                                                                 |

## SFR Definition 7.2. CPT0MD: Comparator 0 Mode Selection

| Bit   | 7   | 6 | 5      | 4      | 3 | 2 | 1    | 0       |

|-------|-----|---|--------|--------|---|---|------|---------|

| Name  |     |   | CP0RIE | CP0FIE |   |   | CP0M | ID[1:0] |

| Туре  | R/W | R | R/W    | R/W    | R | R | R/W  |         |

| Reset | 1   | 0 | 0      | 0      | 0 | 0 | 1    | 0       |

## SFR Page = 0x0; SFR Address = 0x9D

| Bit | Name       | Function                                                                                                                                                                                                                                                           |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved   | Read = 1b, Must Write 1b.                                                                                                                                                                                                                                          |

| 6   | Unused     | Read = 0b, Write = don't care.                                                                                                                                                                                                                                     |

| 5   | CPORIE     | Comparator0 Rising-Edge Interrupt Enable.<br>0: Comparator0 Rising-edge interrupt disabled.<br>1: Comparator0 Rising-edge interrupt enabled.                                                                                                                       |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.<br>0: Comparator0 Falling-edge interrupt disabled.<br>1: Comparator0 Falling-edge interrupt enabled.                                                                                                                    |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                    |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

## 8.8. Automatic Scanning (Method 1—CS0SMEN = 0)

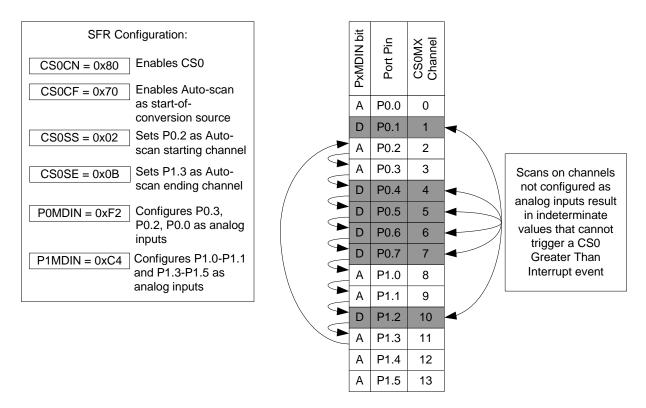

CS0 can be configured to automatically scan a sequence of contiguous CS0 input channels by configuring and enabling auto-scan. Using auto-scan with the CS0 comparator interrupt enabled allows a system to detect a change in measured capacitance without requiring any additional dedicated MCU resources.

Auto-scan is enabled by setting the CS0 start-of-conversion bits (CS0CF6:4) to 111b. After enabling autoscan, the starting and ending channels should be set to appropriate values in CS0SS and CS0SE, respectively. Writing to CS0SS when auto-scan is enabled will cause the value written to CS0SS to be copied into CS0MX. After being enabled, writing a 1 to CS0BUSY will start auto-scan conversions. When auto-scan completes the number of conversions defined in the CS0 accumulator bits (CS0CF1:0), autoscan configures CS0MX to the next sequential port pin configured as an analog input and begins a conversion on that channel. All other pins between CS0SS and CS0SE which are set as analog inputs are grounded during the conversion. This scan sequence continues until CS0MX reaches the ending input channel value defined in CS0SE. After one or more conversions have been taken at this channel, autoscan configures CS0MX back to the starting input channel. For an example system configured to use autoscan, please see Figure "8.2 Auto-Scan Example" on page 103.

**Note:** Auto-scan attempts one conversion on a CS0MX channel regardless of whether that channel's port pin has been configured as an analog input. Auto-scan will also complete the current rotation when the device is halted for debugging.

If auto-scan is enabled when the device enters suspend mode, auto-scan will remain enabled and running. This feature allows the device to wake from suspend through CS0 greater-than comparator event on any configured capacitive sense input included in the auto-scan sequence of inputs.

Figure 8.2. Auto-Scan Example

## 8.11. CS0 Conversion Accumulator

CS0 can be configured to accumulate multiple conversions on an input channel. The number of samples to be accumulated is configured using the CS0ACU2:0 bits (CS0CF2:0). The accumulator can accumulate 1, 4, 8, 16, 32, or 64 samples. After the defined number of samples have been accumulated, the result is divided by either 1, 4, 8, 16, 32, or 64 (depending on the CS0ACU[2:0] setting) and copied to the CS0DH:CS0DL SFRs.

| Auto-Scan Enabled | Accumulator Enabled | CS0 Conversion<br>Complete<br>Interrupt<br>Behavior                      | CS0 Greater Than Interrupt<br>Behavior                                                                                                                                          | CS0MX Behavior                                                                                                                                                                                                                     |

|-------------------|---------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N                 | Ν                   | CS0INT Interrupt<br>serviced after 1<br>conversion com-<br>pletes        | Interrupt serviced after 1 con-<br>version completes if value in<br>CS0DH:CS0DL is greater than<br>CS0THH:CS0THL                                                                | CS0MX unchanged.                                                                                                                                                                                                                   |

| N                 | Y                   | CS0INT Interrupt<br>serviced after <i>M</i><br>conversions com-<br>plete | Interrupt serviced after <i>M</i> conversions complete if value in CS0DH:CS0DL (post accumulate and divide) is greater than CS0THH:CS0THL                                       | CS0MX unchanged.                                                                                                                                                                                                                   |

| Y                 | Ν                   | CS0INT Interrupt<br>serviced after 1<br>conversion com-<br>pletes        | Interrupt serviced after con-<br>version completes if value in<br>CS0DH:CS0DL is greater than<br>CS0THH:CS0THL;<br>Auto-Scan stopped                                            | If greater-than comparator detects conver-<br>sion value is greater than<br>CS0THH:CS0THL, CS0MX is left<br>unchanged; otherwise, CS0MX updates to<br>the next channel (CS0MX + 1) and wraps<br>back to CS0SS after passing CS0SE. |

| Y                 | Y                   | CS0INT Interrupt<br>serviced after <i>M</i><br>conversions com-<br>plete | Interrupt serviced after <i>M</i> con-<br>versions complete if value in<br>CS0DH:CS0DL (post accumu-<br>late and divide) is greater than<br>CS0THH:CS0THL; Auto-Scan<br>stopped | If greater-than comparator detects conver-<br>sion value is greater than<br>CS0THH:CS0THL, CS0MX is left<br>unchanged; otherwise, CS0MX updates to<br>the next channel (CS0MX + 1) and wraps<br>back to CS0SS after passing CS0SE. |

Table 8.1. Operation with Auto-scan and Accumulate

| Bit   | 7 | 6 | 5 | 4   | 3   | 2          | 1   | 0   |

|-------|---|---|---|-----|-----|------------|-----|-----|

| Name  |   |   |   |     |     | CS0SS[4:0] |     |     |

| Туре  | R | R | R | R/W | R/W | R/W        | R/W | R/W |

| Reset | 0 | 0 | 0 | 0   | 0   | 0          | 0   | 0   |

SFR Page = 0x0; SFR Address = 0xDD

| Bit | Name       | Description                                                                                                                                                                                                                                                                                          |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused     | Read = 000b; Write = Don't care                                                                                                                                                                                                                                                                      |

| 4:0 | CS0SS[4:0] | Starting Channel for Auto-Scan.                                                                                                                                                                                                                                                                      |

|     |            | Sets the first CS0 channel to be selected by the mux for Capacitive Sense conver-<br>sion when auto-scan is enabled and active. All channels detailed in CS0MX SFR<br>Definition 8.15 are possible choices for this register.<br>When auto-scan is enabled, a write to CS0SS will also update CS0MX. |

## SFR Definition 8.8. CS0SE: Capacitive Sense Auto-Scan End Channel

| Bit   | 7 | 6 | 5 | 4   | 3   | 2          | 1   | 0   |

|-------|---|---|---|-----|-----|------------|-----|-----|

| Name  |   |   |   |     |     | CS0SE[4:0] |     |     |

| Туре  | R | R | R | R/W | R/W | R/W        | R/W | R/W |

| Reset | 0 | 0 | 0 | 0   | 0   | 0          | 0   | 0   |

#### SFR Page = 0x0; SFR Address = 0xDE

| Bit | Name       | Description                                                                                                                                                                                                          |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused     | Read = 000b; Write = Don't care                                                                                                                                                                                      |

| 4:0 | CS0SE[4:0] | Ending Channel for Auto-Scan.                                                                                                                                                                                        |

|     |            | Sets the last CS0 channel to be selected by the mux for Capacitive Sense conversion when auto-scan is enabled and active. All channels detailed in CS0MX SFR Definition 8.15 are possible choices for this register. |

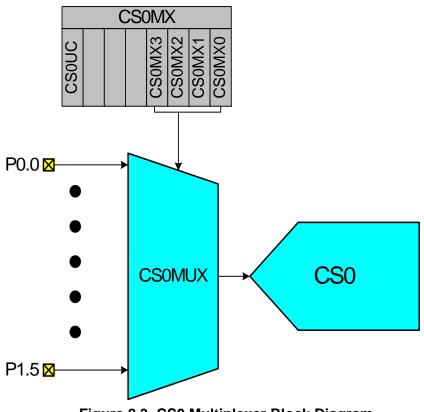

## 8.14. Capacitive Sense Multiplexer

The input multiplexer can be controlled through two methods. The CS0MX register can be written to through firmware, or the register can be configured automatically using the modules auto-scan functionality (see "8.8. Automatic Scanning (Method 1—CS0SMEN = 0)").

Figure 8.3. CS0 Multiplexer Block Diagram

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |

| JC rel               | Jump if Carry is set                                | 2     | 2/3             |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/3             |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/4             |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/4             |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3     | 3/4             |

|                      | Program Branching                                   | ·     |                 |

| ACALL addr11         | Absolute subroutine call                            | 2     | 3               |

| LCALL addr16         | Long subroutine call                                | 3     | 4               |

| RET                  | Return from subroutine                              | 1     | 5               |

| RETI                 | Return from interrupt                               | 1     | 5               |

| AJMP addr11          | Absolute jump                                       | 2     | 3               |

| LJMP addr16          | Long jump                                           | 3     | 4               |

| SJMP rel             | Short jump (relative address)                       | 2     | 3               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 3               |

| JZ rel               | Jump if A equals zero                               | 2     | 2/3             |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 3/4             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/4             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/3             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/4             |

| NOP                  | No operation                                        | 1     | 1               |

## Table 9.1. CIP-51 Instruction Set Summary (Continued)

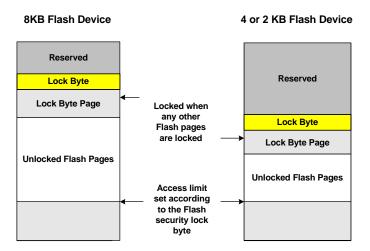

## 14.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. See **Section "10. Memory Organization" on page 128** for the location of the security byte. The Flash security mechanism allows the user to lock *n* 512-byte Flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where *n* is the 1s complement number represented by the Security Lock Byte. **The page containing the Flash Security Lock Byte is unlocked when no other Flash pages are locked (all bits of the Lock Byte are 1) and locked when any other Flash pages are locked (any bit of the Lock Byte is 0).**

| Security Lock Byte: | 1111 1011b                                  |

|---------------------|---------------------------------------------|

| ones Complement:    | 0000 0100b                                  |

| Flash pages locked: | 5 (First four Flash pages + Lock Byte Page) |

Figure 14.1. Flash Program Memory Map (8 kB and smaller devices)

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 14.1 summarizes the Flash security features of the C8051F99x-C8051F98x devices.

### 15.2. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

**Note:** To ensure the MCU enters a low power state upon entry into Idle Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "18.6. PCA Watchdog Timer Reset" on page 185 for more information on the use and configuration of the WDT.

#### 15.3. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter stop mode as soon as the instruction that sets the bit completes execution. In stop mode the precision internal oscillator and CPU are stopped; the state of the low power oscillator and the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout.

Stop mode is a legacy 8051 power mode; it will not result in optimal power savings. Sleep or suspend mode will provide more power savings if the MCU needs to be inactive for a long period of time.

**Note:** To ensure the MCU enters a low power state upon entry into Stop Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

## 15.7. Determining the Event that Caused the Last Wakeup

When waking from idle mode, the CPU will vector to the interrupt which caused it to wake up. When waking from stop mode, the RSTSRC register may be read to determine the cause of the last reset.

Upon exit from suspend or sleep mode, the wake-up flags in the PMU0CF and PMU0FL registers can be read to determine the event which caused the device to wake up. After waking up, the wake-up flags will continue to be updated if any of the wake-up events occur. Wake-up flags are always updated, even if they are not enabled as wake-up sources.

All wake-up flags enabled as wake-up sources in PMU0CF and PMU0FL must be cleared before the device can enter suspend or sleep mode. After clearing the wake-up flags, each of the enabled wake-up events should be checked in the individual peripherals to ensure that a wake-up event did not occur while the wake-up flags were being cleared.

## SFR Definition 16.4. CRC0AUTO: CRC0 Automatic Control

| Bit   | 7      | 6       | 5 | 4           | 3 | 2 | 1 | 0 |

|-------|--------|---------|---|-------------|---|---|---|---|

| Name  | AUTOEN | CRCDONE |   | CRC0ST[4:0] |   |   |   |   |

| Туре  | R/W    | R       | R | R/W         |   |   |   |   |

| Reset | 0      | 1       | 0 | 0           | 0 | 0 | 0 | 0 |

#### SFR Page = All; SFR Address = 0x9E

| Bit | Name        | Function                                                                                                                                                                                                                                |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AUTOEN      | Automatic CRC Calculation Enable.                                                                                                                                                                                                       |

|     |             | When AUTOEN is set to 1, any write to CRC0CN will initiate an automatic CRC starting at Flash sector CRC0ST and continuing for CRC0CNT sectors.                                                                                         |

| 6   | CRCDONE     | CRCDONE Automatic CRC Calculation Complete.                                                                                                                                                                                             |

|     |             | Set to 0 when a CRC calculation is in progress. Code execution is stopped during a CRC calculation; therefore, reads from firmware will always return 1.                                                                                |

| 5   | Unused      | Read = 0b; Write = Don't Care.                                                                                                                                                                                                          |

| 4:0 | CRC0ST[4:0] | Automatic CRC Calculation Starting Block.                                                                                                                                                                                               |

|     |             | These bits specify the Flash block to start the automatic CRC calculation. The starting address of the first Flash block included in the automatic CRC calculation is CRC0ST x Block Size.<br><b>Note:</b> The block size is 256 bytes. |

Notes:

## SFR Definition 16.5. CRC0CNT: CRC0 Automatic Flash Sector Count

| Bit   | 7               | 6         | 5                                      | 4         | 3   | 2         | 1  | 0 |  |  |

|-------|-----------------|-----------|----------------------------------------|-----------|-----|-----------|----|---|--|--|

| Nam   | e               |           |                                        |           | C   | RC0CNT[4: | 0] |   |  |  |

| Туре  | e R             | R         | R                                      |           | R/W |           |    |   |  |  |

| Rese  | et O            | 0         | 0                                      | 0 0 0 0 0 |     |           |    |   |  |  |

| SFR F | Page = All; SFR | Address = | 0x9A                                   |           |     |           |    |   |  |  |

| Bit   | Name            |           | Function                               |           |     |           |    |   |  |  |

| 7:5   | Unused          | Read = 0  | Read = 000b; Write = Don't Care.       |           |     |           |    |   |  |  |

| 4:0   | CRC0CNT[4:0]    | Automa    | Automatic CRC Calculation Block Count. |           |     |           |    |   |  |  |

calculation is (CRC0ST+CRC0CNT) x Block Size - 1.

1. The block size is 256 bytes.

These bits specify the number of Flash blocks to include in an automatic CRC calculation. The last address of the last Flash block included in the automatic CRC

2. The maximum number of blocks that may be computed in a single operation is 31. To compute a CRC on all 32 blocks, perform one operation on 31 blocks, then perform a second operation on 1 block without clearing the CRC result.

| S       | Y    |

|---------|------|

| SILICON | LABS |

## **19.4.** Special Function Registers for Selecting and Configuring the System Clock

The clocking sources on C8051F99x-C8051F98x devices are enabled and configured using the OSCICN, OSCICL, OSCXCN and the SmaRTClock internal registers. See Section "20. SmaRTClock (Real Time Clock)" on page 197 for SmaRTClock register descriptions. The system clock source for the MCU can be selected using the CLKSEL register. To minimize active mode current, the oneshot timer which sets Flash read time should by bypassed when the system clock is greater than 10 MHz. See the FLSCL register description for details.

The clock selected as the system clock can be divided by 1, 2, 4, 8, 16, 32, 64, or 128. When switching between two clock divide values, the transition may take up to 128 cycles of the undivided clock source. The CLKRDY flag can be polled to determine when the new clock divide value has been applied. The clock divider must be set to "divide by 1" when entering Suspend or Sleep Mode.

The system clock source may also be switched on-the-fly. The switchover takes effect after one clock period of the slower oscillator.

| Bit   | 7      | 6           | 5 | 4 | 3   | 2           | 1   | 0 |

|-------|--------|-------------|---|---|-----|-------------|-----|---|

| Name  | CLKRDY | CLKDIV[2:0] |   |   |     | CLKSEL[2:0] |     |   |

| Туре  | R      | R/W         |   |   | R/W |             | R/W |   |

| Reset | 1      | 0 0 0       |   |   | 0   | 0           | 1   | 0 |

#### SFR Page = All; SFR Address = 0xA9

| Name        | Function                                                                       |

|-------------|--------------------------------------------------------------------------------|

| CLKRDY      | System Clock Divider Clock Ready Flag.                                         |

|             | 0: The selected clock divide setting has not been applied to the system clock. |

|             | 1: The selected clock divide setting has been applied to the system clock.     |

| CLKDIV[2:0] | System Clock Divider Bits.                                                     |

|             | Selects the clock division to be applied to the undivided system clock source. |

|             | 000: System clock is divided by 1.                                             |

|             | 001: System clock is divided by 2.                                             |

|             | 010: System clock is divided by 4.                                             |

|             | 011: System clock is divided by 8.                                             |

|             | 100: System clock is divided by 16.                                            |

|             | 101: System clock is divided by 32.                                            |

|             | 110: System clock is divided by 64.                                            |

|             | 111: System clock is divided by 128.                                           |

|             | Read = 0b. Must Write 0b.                                                      |

| CLKSEL[2:0] | System Clock Select.                                                           |

|             | Selects the oscillator to be used as the undivided system clock source.        |

|             | 000: Precision Internal Oscillator.                                            |

|             | 001: External Oscillator.                                                      |

|             | 010: Low Power Oscillator divided by 8.<br>011: SmaRTClock Oscillator.         |

|             | 100: Low Power Oscillator.                                                     |

|             | All other values reserved.                                                     |

|             | CLKRDY                                                                         |

#### 20.3.2. Setting a SmaRTClock Alarm

The SmaRTClock alarm function compares the 32-bit value of SmaRTClock Timer to the value of the ALARMn registers. An alarm event is triggered if the SmaRTClock timer is **equal to** the ALARMn registers. If Auto Reset is enabled, the 32-bit timer will be cleared to zero one SmaRTClock cycle after the alarm event.

The SmaRTClock alarm event can be configured to reset the MCU, wake it up from a low power mode, or generate an interrupt. See Section "13. Interrupt Handler" on page 138, Section "15. Power Management" on page 162, and Section "18. Reset Sources" on page 181 for more information.

The following steps can be used to set up a SmaRTClock Alarm:

- 1. Disable SmaRTClock Alarm Events (RTC0AEN = 0).

- 2. Set the ALARMn registers to the desired value.

- 3. Enable SmaRTClock Alarm Events (RTC0AEN = 1).

#### Notes:

- 1. The ALRM bit, which is used as the SmaRTClock Alarm Event flag, is cleared by disabling SmaRTClock Alarm Events (RTC0AEN = 0).

- If AutoReset is disabled, disabling (RTC0AEN = 0) then Re-enabling Alarm Events (RTC0AEN = 1) after a SmaRTClock Alarm without modifying ALARMn registers will automatically schedule the next alarm after 2^32 SmaRTClock cycles (approximately 36 hours using a 32.768 kHz crystal).

- 3. The SmaRTClock Alarm Event flag will remain asserted for a maximum of one SmaRTClock cycle. See Section "15. Power Management" on page 162 for information on how to capture a SmaRTClock Alarm event using a flag which is not automatically cleared by hardware.

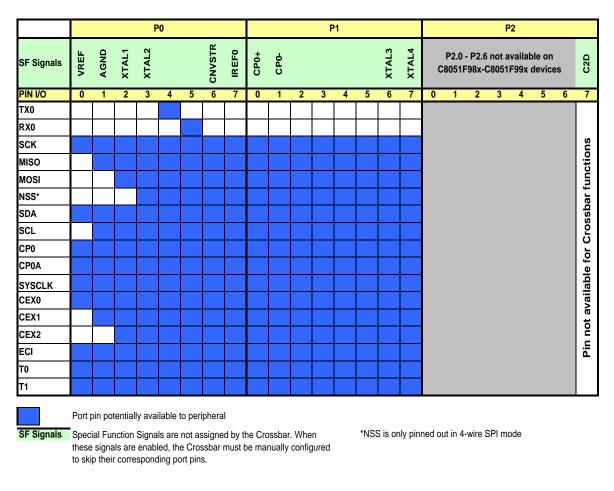

### 21.3. Priority Crossbar Decoder

The Priority Crossbar Decoder (Figure 21.3) assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that resource (excluding UART0, which is always at pins 4 and 5). If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that are to be used for analog input, dedicated functions, or GPIO.

**Important Note on Crossbar Configuration:** If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding PnSKIP bit should be set. This applies to the VREF signal, external oscillator pins (XTAL1, XTAL2), the ADC's external conversion start signal (CNVSTR), EMIF control signals, and any selected ADC or Comparator inputs. The PnSKIP registers may also be used to skip pins to be used as GPIO. The Crossbar skips selected pins as if they were already assigned, and moves to the next unassigned pin. Figure 21.3 shows all the possible pins available to each peripheral. Figure 21.4 shows the Crossbar Decoder priority in an example configuration with no Port pins skipped. Figure 21.5 shows the same Crossbar example with pins P0.2, P0.3, P1.0, and P1.1 skipped.

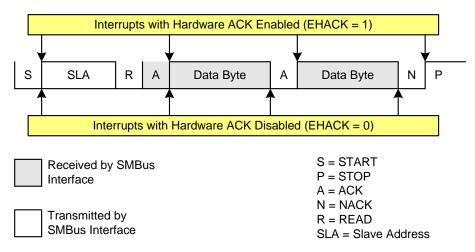

#### 22.5.2. Read Sequence (Master)

During a read sequence, an SMBus master reads data from a slave device. The master in this transfer will be a transmitter during the address byte, and a receiver during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

Writing a 1 to the ACK bit generates an ACK; writing a 0 generates a NACK. Software should write a 0 to the ACK bit for the last data transfer, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. The interface will switch to Master Transmitter Mode if SMB0-DAT is written while an active Master Receiver. Figure 22.6 shows a typical master read sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 22.6. Typical Master Read Sequence

| Parameter                 | Description                                                         | Min                          | Max                     | Units |

|---------------------------|---------------------------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mode               | Timing (See Figure 24.8 and Figure 24.9)                            |                              |                         | 1     |

| Т <sub>МСКН</sub>         | SCK High Time                                                       | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MCKL</sub>         | SCK Low Time                                                        | 1 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>MIS</sub>          | MISO Valid to SCK Shift Edge                                        | 1 x T <sub>SYSCLK</sub> + 20 | —                       | ns    |

| Т <sub>МІН</sub>          | SCK Shift Edge to MISO Change                                       | 0                            |                         | ns    |

| Slave Mode 1              | Fiming (See Figure 24.10 and Figure 24.11)                          |                              |                         | 1     |

| T <sub>SE</sub>           | NSS Falling to First SCK Edge                                       | 2 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SD</sub>           | Last SCK Edge to NSS Rising                                         | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SEZ</sub>          | NSS Falling to MISO Valid                                           | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>          | NSS Rising to MISO High-Z                                           | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| Т <sub>СКН</sub>          | SCK High Time                                                       | 5 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>CKL</sub>          | SCK Low Time                                                        | 5 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SIS</sub>          | MOSI Valid to SCK Sample Edge                                       | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SIH</sub>          | SCK Sample Edge to MOSI Change                                      | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SOH</sub>          | SCK Shift Edge to MISO Change                                       | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>          | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)                    | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

| Note: T <sub>SYSCLk</sub> | $\frac{1}{\zeta}$ is equal to one period of the device system clock | (SYSCLK).                    | 1                       |       |

## Table 24.1. SPI Slave Timing Parameters

277

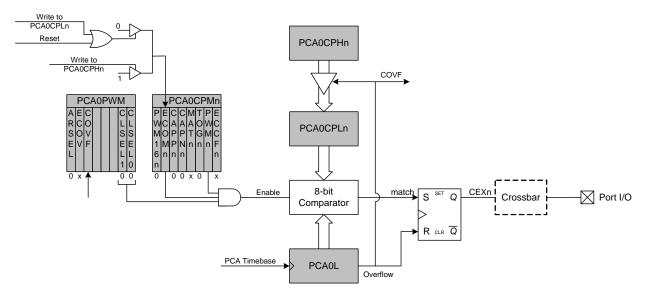

#### 26.3.5.1. 8-Bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 8-bit PWM mode is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 26.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to 00b enables 8-Bit Pulse Width Modulator mode. If the MATn bit is set to 1, the CCFn flag for the module will be set each time an 8-bit comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 256 PCA clock cycles. The duty cycle for 8-Bit PWM Mode is given in Equation 26.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(256 - PCA0CPHn)}{256}$$

#### Equation 26.2. 8-Bit PWM Duty Cycle

Using Equation 26.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 26.8. PCA 8-Bit PWM Mode Diagram