Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

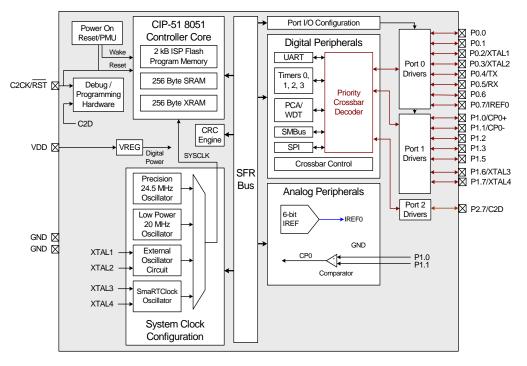

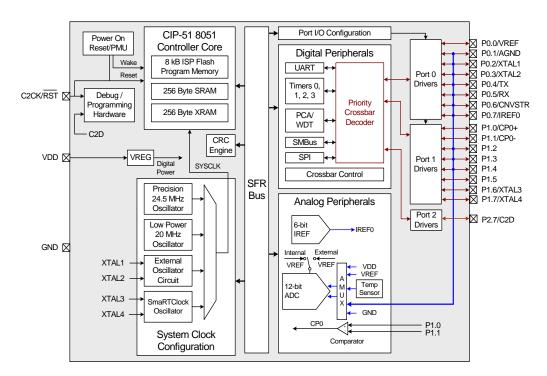

| Core Processor             | CIP-51 8051                                                      |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                            |

| Number of I/O              | 17                                                               |

| Program Memory Size        | 4KB (4K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 512 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                      |

| Data Converters            | · .                                                              |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 24-WFQFN Exposed Pad                                             |

| Supplier Device Package    | 24-QFN (4x4)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f989-c-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | 19.2.Low Power Internal Oscillator                                              | 189 |

|-------------|---------------------------------------------------------------------------------|-----|

|             | 19.3.External Oscillator Drive Circuit                                          | 189 |

|             | 19.3.1.External Crystal Mode                                                    | 189 |

|             | 19.3.2.External RC Mode                                                         |     |

|             | 19.3.3.External Capacitor Mode                                                  |     |

|             |                                                                                 |     |

|             | 19.3.4.External CMOS Clock Mode                                                 |     |

|             | 19.4. Special Function Registers for Selecting and Configuring the System Clock |     |

| 20.         | SmaRTClock (Real Time Clock)                                                    |     |

|             | 20.1.SmaRTClock Interface                                                       | 198 |

|             | 20.1.1.SmaRTClock Lock and Key Functions                                        | 198 |

|             | 20.1.2. Using RTC0ADR and RTC0DAT to Access SmaRTClock Internal Regis           |     |

|             |                                                                                 |     |

|             | 20.1.3.RTC0ADR Short Strobe Feature                                             |     |

|             | 20.1.4.SmaRTClock Interface Autoread Feature                                    |     |

|             |                                                                                 |     |

|             | 20.1.5.RTC0ADR Autoincrement Feature                                            |     |

|             | 20.2.SmaRTClock Clocking Sources                                                |     |

|             | 20.2.1. Using the SmaRTClock Oscillator with a Crystal or External CMOS Clo     | ock |

|             |                                                                                 | 203 |

|             | 20.2.2.Using the SmaRTClock Oscillator in Self-Oscillate Mode                   | 204 |

|             | 20.2.3.Using the Low Frequency Oscillator (LFO)                                 |     |

|             | 20.2.4.Programmable Load Capacitance                                            |     |

|             | 20.2.5. Automatic Gain Control (Crystal Mode Only) and SmaRTClock Bias Do       |     |

|             |                                                                                 |     |

|             | bling                                                                           |     |

|             | 20.2.6.Missing SmaRTClock Detector                                              |     |

|             | 20.2.7.SmaRTClock Oscillator Crystal Valid Detector                             |     |

|             | 20.3.SmaRTClock Timer and Alarm Function                                        |     |

|             | 20.3.1.Setting and Reading the SmaRTClock Timer Value                           | 208 |

|             | 20.3.2.Setting a SmaRTClock Alarm                                               | 209 |

|             | 20.3.3.Software Considerations for using the SmaRTClock Timer and Alarm .       |     |

| 21.         | Port Input/Output                                                               |     |

|             | 21.1.Port I/O Modes of Operation                                                |     |

|             | 21.1.1.Port Pins Configured for Analog I/O                                      |     |

|             |                                                                                 |     |

|             | 21.1.2.Port Pins Configured For Digital I/O                                     |     |

|             | 21.1.3.Interfacing Port I/O to 5 V Logic                                        |     |

|             | 21.1.4.Increasing Port I/O Drive Strength                                       |     |

|             | 21.2.Assigning Port I/O Pins to Analog and Digital Functions                    |     |

|             | 21.2.1.Assigning Port I/O Pins to Analog Functions                              | 217 |

|             | 21.2.2.Assigning Port I/O Pins to Digital Functions                             | 218 |

|             | 21.2.3.Assigning Port I/O Pins to External Digital Event Capture Functions      |     |

|             | 21.3.Priority Crossbar Decoder                                                  |     |

|             | 21.4.Port Match                                                                 |     |

|             | 21.5.Special Function Registers for Accessing and Configuring Port I/O          |     |

| <b></b>     |                                                                                 |     |

| <b>ZZ</b> . | SMBus                                                                           |     |

|             | 22.1.Supporting Documents                                                       |     |

|             | 22.2.SMBus Configuration                                                        | 236 |

## 1.3. Serial Ports

The C8051F99x-C8051F98x Family includes an SMBus/I<sup>2</sup>C interface, a full-duplex UART with enhanced baud rate configuration, and an Enhanced SPI interface. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little CPU intervention.

### 1.4. Programmable Counter Array

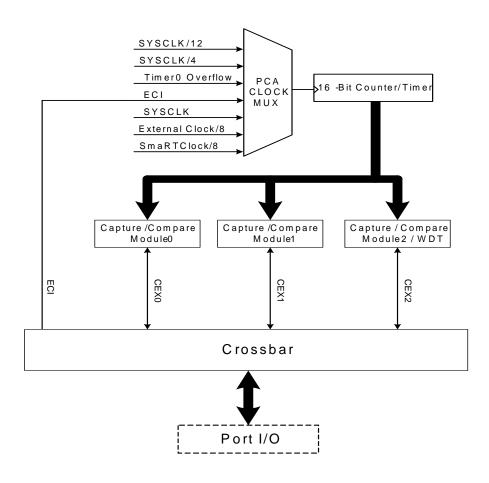

An on-chip programmable counter/timer array (PCA) is included in addition to the four 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with three programmable capture/compare modules. The PCA clock is derived from one of seven sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflows, an External Clock Input (ECI), the system clock, the external oscillator clock source divided by 8, or the SmaRTClock divided by 8.

Each capture/compare module can be configured to operate in a variety of modes: edge-triggered capture, software timer, high-speed output, pulse width modulator (8, 9, 10, 11, or 16-bit), or frequency output. Additionally, Capture/Compare Module 2 offers watchdog timer (WDT) capabilities. Following a system reset, Module 2 is configured and enabled in WDT mode. The PCA Capture/Compare Module I/O and External Clock Input may be routed to Port I/O via the Digital Crossbar.

Figure 1.15. PCA Block Diagram

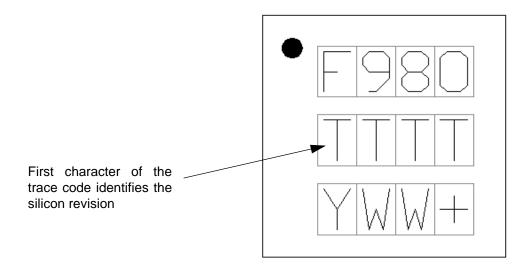

Figure 3.4. QFN-20 Package Marking Diagram

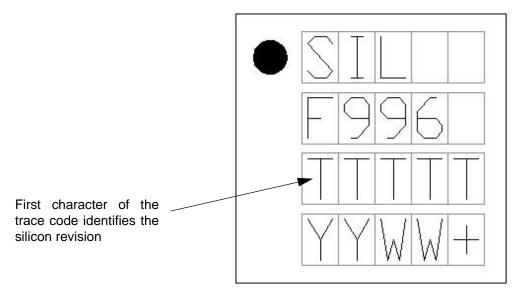

Figure 3.5. QFN-24 Package Marking Diagram

### Table 4.2. Global Electrical Characteristics (Continued)

-40 to +85 °C, 25 MHz system clock unless otherwise specified. See "AN358: Optimizing Low Power Operation of the 'F9xx" for details on how to achieve the supply current specifications listed in this table.

| Parameter | Conditions | Min | Тур | Max | Units |

|-----------|------------|-----|-----|-----|-------|

| Notes:    |            |     |     |     |       |

| 1 | Based on devic | e characterization | n data: Not | production tested. |

|---|----------------|--------------------|-------------|--------------------|

|   | Dased on devic |                    | ruala, not  | production tested. |

- 2. SYSCLK must be at least 32 kHz to enable debugging.

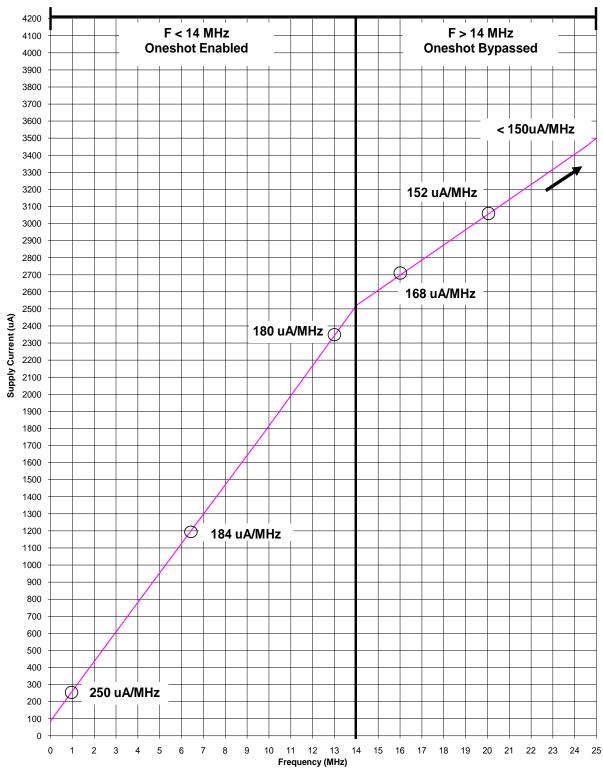

- **3.** Digital Supply Current depends upon the particular code being executed. The values in this table are obtained with the CPU executing an "simp \$" loop, which is the compiled form of a while(1) loop in C. One iteration requires 3 CPU clock cycles, and the Flash memory is read on each cycle. The supply current will vary slightly based on the physical location of the simp instruction and the number of Flash address lines that toggle as a result. In the worst case, current can increase by up to 30% if the simp loop straddles a 64-byte Flash address boundary (e.g., 0x007F to 0x0080). Real-world code with larger loops and longer linear sequences will have few transitions across the 64-byte address boundaries.

- 4. Includes oscillator and regulator supply current.

- 5. IDD can be estimated for frequencies < 14 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range, then adding an offset of 84 μA. When using these numbers to estimate I<sub>DD</sub> for > 14 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 3.0 V; F = 20 MHz, I<sub>DD</sub> = 3.6 mA (25 MHz 20 MHz) x 0.088 mA/MHz = 3.16 mA assuming the same oscillator setting.

- 6. Idle IDD can be estimated by taking the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 3.0 V; F = 5 MHz, Idle I<sub>DD</sub> = 1.75 mA (25 MHz 5 MHz) x 0.067 mA/MHz = 0.41 mA.

Figure 4.1. Active Mode Current (External CMOS Clock)

## Table 4.4. Reset Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameter                                                    | Conditions                                                                                 | Min                   | Тур     | Max                 | Units |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|---------|---------------------|-------|

| RST Output Low Voltage                                       | I <sub>OL</sub> = 1.4 mA,                                                                  | _                     | _       | 0.6                 | V     |

| RST Input High Voltage                                       | V <sub>DD</sub> = 12.0 to 3.6 V                                                            | V <sub>DD</sub> – 0.6 |         | _                   | V     |

|                                                              | $V_{DD}$ = 10.9 to 2.0 V                                                                   | $0.7 \times V_{DD}$   | _       | —                   | V     |

| RST Input Low Voltage                                        | V <sub>DD</sub> = 12.0 to 3.6 V                                                            | _                     | _       | 0.6                 | V     |

|                                                              | V <sub>DD</sub> = 10.9 to 2.0 V                                                            | —                     | _       | $0.3 \times V_{DD}$ | V     |

| RST Input Pullup Current                                     | <del>RST</del> = 10.0 V, V <sub>DD</sub> = 1.8 V<br>RST = 10.0 V, V <sub>DD</sub> = 13.6 V | _                     | 4<br>20 | —<br>30             | μA    |

| V <sub>DD</sub> Monitor Threshold                            | Early Warning                                                                              | 1.8                   | 1.85    | 1.9                 | V     |

| (V <sub>RST</sub> )                                          | Reset Trigger<br>(all power modes except Sleep)                                            | 1.7                   | 1.75    | 1.8                 |       |

| V <sub>DD</sub> Ramp Time for Power<br>On                    | V <sub>DD</sub> Ramp from 0–1.8 V                                                          | _                     |         | 3                   | ms    |

| POR Monitor Threshold                                        | Brownout Condition (V <sub>DD</sub> Falling)                                               | 0.75                  | 1.0     | 1.3                 | V     |

| (V <sub>POR</sub> )                                          | Recovery from Brownout (V <sub>DD</sub> Rising)                                            |                       | 1.75    |                     |       |

| Missing Clock Detector<br>Timeout                            | Time from last system clock rising edge to reset initiation                                | 100                   | 650     | 1000                | μs    |

| Minimum System Clock w/<br>Missing Clock Detector<br>Enabled | System clock frequency which triggers<br>a missing clock detector timeout                  | _                     | 7       | 10                  | kHz   |

| Reset Time Delay                                             | Delay between release of any reset<br>source and code<br>execution at location 0x0000      | _                     | 10      | _                   | μs    |

| Minimum $\overline{RST}$ Low Time to Generate a System Reset |                                                                                            | 15                    | _       | _                   | μs    |

| V <sub>DD</sub> Monitor Turn-on Time                         |                                                                                            | _                     | 300     | _                   | ns    |

| V <sub>DD</sub> Monitor Supply<br>Current                    |                                                                                            | _                     | 7       | _                   | μA    |

|                                                        | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rmal Power           | Mode                    | L I                  | ow Power N           | lode                    |  |  |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------|----------------------|----------------------|-------------------------|--|--|--|--|--|

|                                                        | 8 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10 bit               | 12 bit                  | 8 bit                | 10 bit               | 12 bit                  |  |  |  |  |  |

| Highest nominal<br>SAR clock<br>frequency              | 8.17 MHz<br>(24.5/3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8.17 MHz<br>(24.5/3) | 6.67 MHz<br>(20.0/3)    | 4.08 MHz<br>(24.5/6) | 4.08 MHz<br>(24.5/6) | 4.00 MHz<br>(20.0/5)    |  |  |  |  |  |

| Total number of<br>conversion<br>clocks required       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                   | 52 (13 x 4)             | 11                   | 13                   | 52 (13*4)               |  |  |  |  |  |

| Total tracking<br>time (min)                           | 1.5 µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1.5 µs               | 4.8 μs<br>(1.5+3 x 1.1) | 1.5 µs               | 1.5 µs               | 4.8 μs<br>(1.5+3 x 1.1) |  |  |  |  |  |

| Total time for one conversion                          | 2.85 µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.09 µs              | 12.6 µs                 | 4.19 µs              | 4.68 µs              | 17.8 µs                 |  |  |  |  |  |

| ADC Throughput                                         | 351 ksps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 323 ksps             | 79 ksps                 | 238 ksps             | 214 ksps             | 56 ksps                 |  |  |  |  |  |

| Energy per conversion                                  | 8.2 nJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8.9 nJ               | 36.5 nJ                 | 6.5 nJ               | 7.3 nJ               | 27.7 nJ                 |  |  |  |  |  |

| low power oscil<br>nominal frequer<br>frequencies of 2 | conversion Image: Second s |                      |                         |                      |                      |                         |  |  |  |  |  |

# Table 5.1. Representative Conversion Times and Energy Consumption for the SARADC with 1.65 V High-Speed VREF

CPU current. 12-bit mode is only available on C8051F980/6 and C8051F990/6 devices.

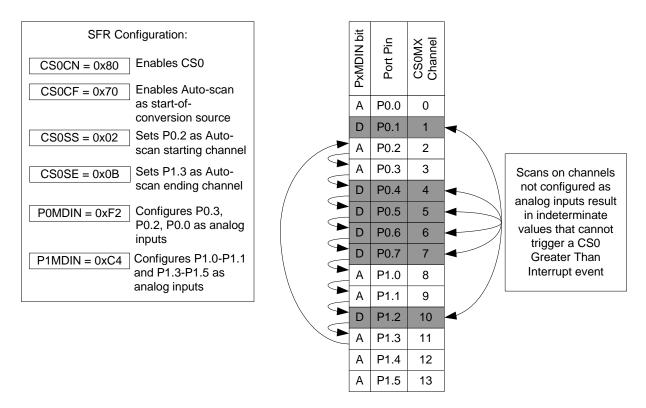

## 8.8. Automatic Scanning (Method 1—CS0SMEN = 0)

CS0 can be configured to automatically scan a sequence of contiguous CS0 input channels by configuring and enabling auto-scan. Using auto-scan with the CS0 comparator interrupt enabled allows a system to detect a change in measured capacitance without requiring any additional dedicated MCU resources.

Auto-scan is enabled by setting the CS0 start-of-conversion bits (CS0CF6:4) to 111b. After enabling autoscan, the starting and ending channels should be set to appropriate values in CS0SS and CS0SE, respectively. Writing to CS0SS when auto-scan is enabled will cause the value written to CS0SS to be copied into CS0MX. After being enabled, writing a 1 to CS0BUSY will start auto-scan conversions. When auto-scan completes the number of conversions defined in the CS0 accumulator bits (CS0CF1:0), autoscan configures CS0MX to the next sequential port pin configured as an analog input and begins a conversion on that channel. All other pins between CS0SS and CS0SE which are set as analog inputs are grounded during the conversion. This scan sequence continues until CS0MX reaches the ending input channel value defined in CS0SE. After one or more conversions have been taken at this channel, autoscan configures CS0MX back to the starting input channel. For an example system configured to use autoscan, please see Figure "8.2 Auto-Scan Example" on page 103.

**Note:** Auto-scan attempts one conversion on a CS0MX channel regardless of whether that channel's port pin has been configured as an analog input. Auto-scan will also complete the current rotation when the device is halted for debugging.

If auto-scan is enabled when the device enters suspend mode, auto-scan will remain enabled and running. This feature allows the device to wake from suspend through CS0 greater-than comparator event on any configured capacitive sense input included in the auto-scan sequence of inputs.

Figure 8.2. Auto-Scan Example

## SFR Definition 8.9. CS0THH: Capacitive Sense Comparator Threshold High Byte

| Bit   | 7   | 6           | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|-------------|-----|-----|-----|-----|-----|-----|--|--|

| Name  |     | CS0THH[7:0] |     |     |     |     |     |     |  |  |

| Туре  | R/W | R/W         | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset | 0   | 0           | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

SFR Page = 0x0; SFR Address = 0xFE

| Bit | Name        | Description                                                                       |  |  |  |  |  |

|-----|-------------|-----------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0 | CS0THH[7:0] | 60 Comparator Threshold High Byte.                                                |  |  |  |  |  |

|     |             | High byte of the 16-bit value compared to the Capacitive Sense conversion result. |  |  |  |  |  |

## SFR Definition 8.10. CS0THL: Capacitive Sense Comparator Threshold Low Byte

| Bit                                | 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|------------------------------------|---------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Name                               | e CS0THL[7:0] |     |     |     |     |     |     |     |  |  |

| Туре                               | R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset                              | 0             | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| SFR Page = 0x0; SFR Address = 0xFD |               |     |     |     |     |     |     |     |  |  |

| Bit                                | Name          |     |     |     |     |     |     |     |  |  |

| BIt | Name        | Description                                                                      |

|-----|-------------|----------------------------------------------------------------------------------|

| 7:0 | CS0THL[7:0] | CS0 Comparator Threshold Low Byte.                                               |

|     |             | Low byte of the 16-bit value compared to the Capacitive Sense conversion result. |

112

## **13.3.** Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. If a high priority interrupt preempts a low priority interrupt, the low priority interrupt will finish execution after the high priority interrupt completes. Each interrupt has an associated interrupt priority bit in in the Interrupt Priority and Extended Interrupt Priority registers used to configure its priority level. Low priority is the default.

If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate. See Table 13.1 on page 140 to determine the fixed priority order used to arbitrate between simultaneously recognized interrupts.

### 13.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 7 system clock cycles: 1 clock cycle to detect the interrupt, 1 clock cycle to execute a single instruction, and 5 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 19 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 5 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

| Interrupt Source                | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                               | Bit<br>addressable? | Cleared<br>by HW? | Enable Flag        | Priority<br>Control |

|---------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|---------------------|-------------------|--------------------|---------------------|

| Reset                           | 0x0000              | Тор               | None                                                                       | N/A                 | N/A               | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0 (INT0)     | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Y                   | Y                 | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow                | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Y                   | Y                 | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1 (INT1)     | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Y                   | Y                 | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow                | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Y                   | Y                 | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                           | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                   | Ν                 | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow                | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                   | N                 | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                            | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                   | N                 | ESPI0 (IE.6)       | PSPI0 (IP.6)        |

| SMB0                            | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Y                   | Ν                 | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| SmaRTClock Alarm                | 0x0043              | 8                 | ALRM (RTC0CN.2) <sup>2</sup>                                               | Ν                   | Ν                 | EARTC0<br>(EIE1.1) | PARTC0<br>(EIP1.1)  |

| ADC0 Window Comparator          | 0x004B              | 9                 | AD0WINT (ADC0CN.3)                                                         | Y                   | Ν                 | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| ADC0 End of Conversion          | 0x0053              | 10                | AD0INT (ADC0CN.5)                                                          | Υ                   | Ν                 | EADC0<br>(EIE1.3)  | PADC0<br>(EIP1.3)   |

| Programmable Counter<br>Array   | 0x005B              | 11                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                           | Υ                   | Ν                 | EPCA0<br>(EIE1.4)  | PPCA0<br>(EIP1.4)   |

| Comparator0                     | 0x0063              | 12                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | Ν                   | Ν                 | ECP0<br>(EIE1.5)   | PCP0<br>(EIP1.5)    |

| Reserved                        | 0x006B              | 13                |                                                                            |                     |                   |                    |                     |

| Timer 3 Overflow                | 0x0073              | 14                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | Ν                   | Ν                 | ET3<br>(EIE1.7)    | PT3<br>(EIP1.7)     |

| Supply Monitor Early<br>Warning | 0x007B              | 15                | VDDOK (VDM0CN.5) <sup>1</sup>                                              | Ν                   | Ν                 | EWARN<br>(EIE2.0)  | PWARN<br>(EIP2.0)   |

| Port Match                      | 0x0083              | 16                | None                                                                       |                     |                   | EMAT<br>(EIE2.1)   | PMAT<br>(EIP2.1)    |

| SmaRTClock Oscillator Fail      | 0x008B              | 17                | OSCFAIL (RTC0CN.5) <sup>2</sup>                                            | Ν                   | Ν                 | ERTC0F<br>(EIE2.2) | PFRTC0F<br>(EIP2.2) |

| Reserved                        | 0x0093              | 18                |                                                                            |                     |                   |                    |                     |

| CS0 Conversion Complete         | 0x009B              | 19                | CS0INT (CS0CN.5)                                                           | Y                   | Ν                 | ECSCPT<br>(EIE2.4) | PCSCPT<br>(EIP2.4)  |

| CS0 Digital Comparator          | 0x00A3              | 20                | CS0CMPF (CS0CN.0)                                                          | Y                   | N                 | ECSDC<br>(EIE2.5)  | PCSDC<br>(EIP2.5)   |

| CS0 End of Scan                 | 0x00AB              | 21                | CS0EOS (CS0CN.6)                                                           | Y                   | Ν                 | ECSEOS<br>(EIE2.6) | PCSEOS<br>(EIP2.6)  |

Table 13.1. Interrupt Summary

Notes:

1. Indicates a read-only interrupt pending flag. The interrupt enable may be used to prevent software from vectoring to the associated interrupt service routine.

2. Indicates a register located in an indirect memory space.

## SFR Definition 20.2. RTC0ADR: SmaRTClock Address

| Bit   | 7    | 6      | 5 | 4     | 3         | 2 | 1 | 0 |

|-------|------|--------|---|-------|-----------|---|---|---|

| Name  | BUSY | AUTORD |   | SHORT | ADDR[3:0] |   |   |   |

| Туре  | R/W  | R/W    | R | R/W   | R/W       |   |   |   |

| Reset | 0    | 0      | 0 | 0     | 0         | 0 | 0 | 0 |

## SFR Page = 0x0; SFR Address = 0xAC

| Bit | Name                                                                                                                                   | Function                                                                                 |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7   | BUSY                                                                                                                                   | SmaRTClock Interface Busy Indicator.                                                     |  |  |  |  |  |

|     |                                                                                                                                        | Indicates SmaRTClock interface status. Writing 1 to this bit initiates an indirect read. |  |  |  |  |  |

| 6   | AUTORD                                                                                                                                 | SmaRTClock Interface Autoread Enable.                                                    |  |  |  |  |  |

|     |                                                                                                                                        | Enables/disables Autoread.                                                               |  |  |  |  |  |

|     |                                                                                                                                        | 0: Autoread Disabled.                                                                    |  |  |  |  |  |

|     |                                                                                                                                        | 1: Autoread Enabled.                                                                     |  |  |  |  |  |

| 5   | Unused                                                                                                                                 | Read = 0b; Write = Don't Care.                                                           |  |  |  |  |  |

| 4   | SHORT                                                                                                                                  | Short Strobe Enable.                                                                     |  |  |  |  |  |

|     |                                                                                                                                        | Enables/disables the Short Strobe Feature.                                               |  |  |  |  |  |

|     |                                                                                                                                        | 0: Short Strobe disabled.                                                                |  |  |  |  |  |

|     |                                                                                                                                        | 1: Short Strobe enabled.                                                                 |  |  |  |  |  |

| 3:0 | ADDR[3:0]                                                                                                                              | SmaRTClock Indirect Register Address.                                                    |  |  |  |  |  |

|     |                                                                                                                                        | Sets the currently selected SmaRTClock register.                                         |  |  |  |  |  |

|     |                                                                                                                                        | See Table 20.1 for a listing of all SmaRTClock indirect registers.                       |  |  |  |  |  |

|     | Note: The ADDR bits increment after each indirect read/write operation that targets a CAPTUREn or ALARMn internal SmaRTClock register. |                                                                                          |  |  |  |  |  |

## SFR Definition 20.3. RTC0DAT: SmaRTClock Data

| Bit   | 7            | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|--------------|---|---|----|---|---|---|---|--|--|

| Name  | RTC0DAT[7:0] |   |   |    |   |   |   |   |  |  |

| Туре  |              |   |   | R/ | W |   |   |   |  |  |

| Reset | 0            | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

#### SFR Page= 0x0; SFR Address = 0xAD

| Bit     | Name                                                                                       | Function                                                                             |  |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:0     | RTC0DAT                                                                                    | SmaRTClock Data Bits.                                                                |  |  |  |  |  |  |  |

|         |                                                                                            | Holds data transferred to/from the internal SmaRTClock register selected by RTC0ADR. |  |  |  |  |  |  |  |

| Note: F | Note: Read-modify-write instructions (orl, anl, etc.) should not be used on this register. |                                                                                      |  |  |  |  |  |  |  |

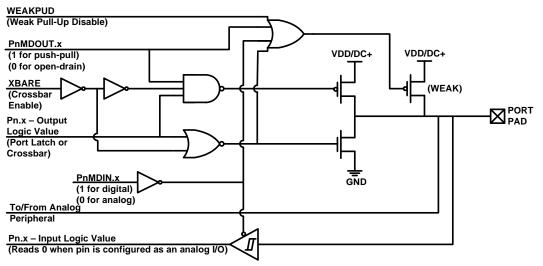

### 21.1. Port I/O Modes of Operation

Port pins P0.0–P1.7 use the Port I/O cell shown in Figure 21.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN registers. On reset, all Port I/O cells default to a digital high impedance state with weak pull-ups enabled.

### 21.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, oscillator input/output, or AGND, VREF, or Current Reference output should be configured for analog I/O (PnMDIN.n = 0). When a pin is configured for analog I/O, its weak pullup and digital receiver are disabled. In most cases, software should also disable the digital output drivers. Port pins configured for analog I/O will always read back a value of 0 regardless of the actual voltage on the pin.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

### 21.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high and low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user must ensure that digital I/O are always internally or externally pulled or driven to a valid logic state. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

Figure 21.2. Port I/O Cell Block Diagram

## SFR Definition 21.17. P1DRV: Port1 Drive Strength

| Bit   | 7          | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|----|---|---|---|---|--|

| Name  | P1DRV[7:0] |   |   |    |   |   |   |   |  |

| Туре  |            |   |   | R/ | W |   |   |   |  |

| Reset | 0          | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |

SFR Page = 0xF; SFR Address = 0x9B

| Bit | Name       | Function                                                                                                                                                                                               |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |  |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |  |

## SFR Definition 21.18. P2: Port2

| Bit   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|---|---|---|---|---|---|---|

| Name  | P2  |   |   |   |   |   |   |   |

| Туре  | R/W | R | R | R | R | R | R | R |

| Reset | 1   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = All; SFR Address = 0xA0; Bit-Addressable

| Bit | Name   | Description                                                                                                                                   | Read                                                                          | Write |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------|

| 7   | P2     | <b>Port 2 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW.  |

| 6:0 | Unused | Read = 0000000b; Write = D                                                                                                                    | on't Care.                                                                    |       |

## SFR Definition 24.2. SPI0CN: SPI0 Control

| Bit   | 7    | 6    | 5    | 4      | 3          | 2 | 1     | 0     |

|-------|------|------|------|--------|------------|---|-------|-------|

| Name  | SPIF | WCOL | MODF | RXOVRN | NSSMD[1:0] |   | TXBMT | SPIEN |

| Туре  | R/W  | R/W  | R/W  | R/W    | R/W        |   | R     | R/W   |

| Reset | 0    | 0    | 0    | 0      | 0          | 1 | 1     | 0     |

## SFR Page = 0x0; SFR Address = 0xF8; Bit-Addressable

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF       | SPI0 Interrupt Flag.                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit is set to logic 1 by hardware at the end of a data transfer. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                                                                                     |

| 6   | WCOL       | Write Collision Flag.                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | This bit is set to logic 1 if a write to SPI0DAT is attempted when TXBMT is 0. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                       |

| 5   | MODF       | Mode Fault Flag.                                                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01). If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                             |

| 4   | RXOVRN     | Receive Overrun Flag (valid in slave mode only).                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI0 shift register. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                         |

| 3:2 | NSSMD[1:0] | Slave Select Mode.                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | Selects between the following NSS operation modes:<br>(See Section 24.2 and Section 24.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |

| 1   | TXBMT      | Transmit Buffer Empty.                                                                                                                                                                                                                                                                                                                                                                       |

|     |            | This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer.                                                                                                              |

| 0   | SPIEN      | SPI0 Enable.                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | 0: SPI disabled.<br>1: SPI enabled.                                                                                                                                                                                                                                                                                                                                                          |

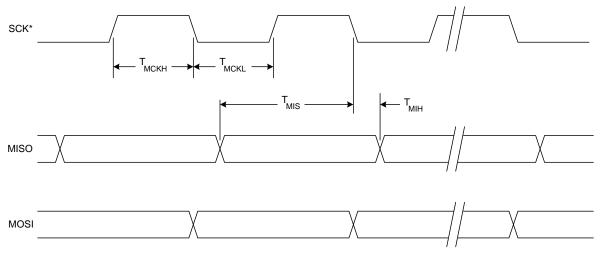

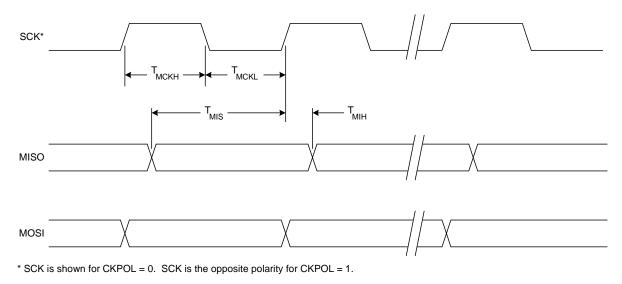

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

## Figure 24.9. SPI Master Timing (CKPHA = 1)

## SFR Definition 25.6. TH0: Timer 0 High Byte

|       |                | Г           |          |   |   |   |   |   |  |  |

|-------|----------------|-------------|----------|---|---|---|---|---|--|--|

| Bit   | 7              | 6           | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

| Nam   | e              | TH0[7:0]    |          |   |   |   |   |   |  |  |

| Туре  | Type R/W       |             |          |   |   |   |   |   |  |  |

| Rese  | et 0           | 0           | 0        | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR F | Page = 0x0; SI | R Address = | = 0x8C   |   |   |   |   |   |  |  |

| Bit   | Name           |             | Function |   |   |   |   |   |  |  |

| 7:0   | TH0[7:0]       | Timer 0 Hig | jh Byte. |   |   |   |   |   |  |  |

## SFR Definition 25.7. TH1: Timer 1 High Byte

| Bit   | 7              | 6           | 5                  | 4            | 3             | 2      | 1 | 0 |  |

|-------|----------------|-------------|--------------------|--------------|---------------|--------|---|---|--|

| Nam   | TH1[7:0]       |             |                    |              |               |        |   |   |  |

| Туре  | 9              | R/W         |                    |              |               |        |   |   |  |

| Rese  | et O           | 0           | 0                  | 0            | 0             | 0      | 0 | 0 |  |

| SFR F | Page = 0x0; SI | R Address = | = 0x8D             |              |               |        |   |   |  |

| Bit   | Name           |             |                    |              | Function      |        |   |   |  |

| 7:0   | TH1[7:0]       | Timer 1 Hig | Timer 1 High Byte. |              |               |        |   |   |  |

|       |                | The TH1 re  | gister is the      | high byte of | the 16-bit Ti | mer 1. |   |   |  |

## SFR Definition 26.7. PCA0CPLn: PCA Capture Module Low Byte

| Bit   | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0CPn[7:0] |     |     |     |     |     |     |     |

| Туре  | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Addresses: PCA0CPL0 = 0xFB, PCA0CPL1 = 0xE9, PCA0CPL2 = 0xEB

#### SFR Pages: PCA0CPL0 = 0x0, PCA0CPL1 = 0x0, PCA0CPL2 = 0x0,

| Bit   | Name                                                                     | Function                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0   | PCA0CPn[7:0]                                                             | PCA Capture Module Low Byte.                                                                                                                                                                                                                                                                                |  |  |  |  |

|       |                                                                          | The PCA0CPLn register holds the low byte (LSB) of the 16-bit capture module n.<br>This register address also allows access to the low byte of the corresponding<br>PCA channel's auto-reload value for 9, 10, or 11-bit PWM mode. The ARSEL bit<br>in register PCA0PWM controls which register is accessed. |  |  |  |  |

| Note: | Note: A write to this register will clear the module's ECOMn bit to a 0. |                                                                                                                                                                                                                                                                                                             |  |  |  |  |

## SFR Definition 26.8. PCA0CPHn: PCA Capture Module High Byte

| Bit   | 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0CPn[15:8] |     |     |     |     |     |     |     |

| Туре  | R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0             | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Addresses: PCA0CPH0 = 0xFC, PCA0CPH1 = 0xEA, PCA0CPH2 = 0xEC

### SFR Pages: PCA0CPH0 = 0x0, PCA0CPH1 = 0x0, PCA0CPH2 = 0x0,

| Bit  | Name                                                                   | Function                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0  | PCA0CPn[15:8]                                                          | PCA Capture Module High Byte.                                                                                                                                                                                                                                                                                 |  |  |  |  |

|      |                                                                        | The PCA0CPHn register holds the high byte (MSB) of the 16-bit capture module n.<br>This register address also allows access to the high byte of the corresponding<br>PCA channel's auto-reload value for 9, 10, or 11-bit PWM mode. The ARSEL bit in<br>register PCA0PWM controls which register is accessed. |  |  |  |  |

| Note | Note: A write to this register will set the module's ECOMn bit to a 1. |                                                                                                                                                                                                                                                                                                               |  |  |  |  |

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Laboratories and "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

## http://www.silabs.com