Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Active                                                            |

| Core Processor             | CIP-51 8051                                                       |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                             |

| Number of I/O              | 17                                                                |

| Program Memory Size        | 4KB (4K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-WFQFN Exposed Pad                                              |

| Supplier Device Package    | 24-QFN (4x4)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f989-c-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 5.10 Voltage Reference Functional Block Diagram                          | 00   |

|---------------------------------------------------------------------------------|------|

| Figure 5.10. Voltage Reference Functional Block Diagram                         |      |

| Figure 7.1. Comparator 0 Functional Block Diagram                               |      |

| Figure 7.2. Comparator Hysteresis Plot                                          |      |

| Figure 7.3. CP0 Multiplexer Block Diagram                                       |      |

| Figure 8.1. CS0 Block Diagram                                                   |      |

| Figure 8.2. Auto-Scan Example                                                   | 103  |

| Figure 8.3. CS0 Multiplexer Block Diagram                                       |      |

| Figure 9.1. CIP-51 Block Diagram                                                |      |

| Figure 10.1. C8051F99x-C8051F98x Memory Map                                     |      |

| Figure 10.2. Flash Program Memory Map                                           |      |

| Figure 14.1. Flash Program Memory Map (8 kB and smaller devices)                |      |

| Figure 15.1. C8051F99x-C8051F98x Power Distribution                             | 163  |

| Figure 16.1. CRC0 Block Diagram                                                 | 172  |

| Figure 16.2. Bit Reverse Register                                               | 179  |

| Figure 18.1. Reset Sources                                                      | 181  |

| Figure 18.2. Power-Fail Reset Timing Diagram                                    | 182  |

| Figure 19.1. Clocking Sources Block Diagram                                     | 188  |

| Figure 19.2. 25 MHz External Crystal Example                                    | 190  |

| Figure 20.1. SmaRTClock Block Diagram                                           | 197  |

| Figure 20.2. Interpreting Oscillation Robustness (Duty Cycle) Test Results      |      |

| Figure 21.1. Port I/O Functional Block Diagram                                  |      |

| Figure 21.2. Port I/O Cell Block Diagram                                        |      |

| Figure 21.3. Peripheral Availability on Port I/O Pins                           |      |

| Figure 21.4. Crossbar Priority Decoder in Example Configuration (No Pins Skippe | ed). |

| 220                                                                             | ,    |

| Figure 21.5. Crossbar Priority Decoder in Example Configuration (4 Pins Skipped | 3)   |

| · · · · · · · · · · · · · · · · · · ·                                           |      |

| Figure 22.1. SMBus Block Diagram                                                |      |

| Figure 22.2. Typical SMBus Configuration                                        |      |

| Figure 22.3. SMBus Transaction                                                  |      |

| Figure 22.4. Typical SMBus SCL Generation                                       |      |

| Figure 22.5. Typical Master Write Sequence                                      |      |

| Figure 22.6. Typical Master Read Sequence                                       |      |

| Figure 22.7. Typical Slave Write Sequence                                       |      |

| Figure 22.8. Typical Slave Read Sequence                                        |      |

| Figure 23.1. UART0 Block Diagram                                                |      |

| Figure 23.2. UART0 Baud Rate Logic                                              |      |

| Figure 23.3. UART Interconnect Diagram                                          |      |

| Figure 23.4. 8-Bit UART Timing Diagram                                          |      |

| Figure 23.5. 9-Bit UART Timing Diagram                                          |      |

| Figure 23.6. UART Multi-Processor Mode Interconnect Diagram                     |      |

| Figure 24.1. SPI Block Diagram                                                  |      |

| Figure 24.2. Multiple-Master Mode Connection Diagram                            |      |

| Figure 24.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diag  |      |

| 267                                                                             | num  |

|                                                                                 |      |

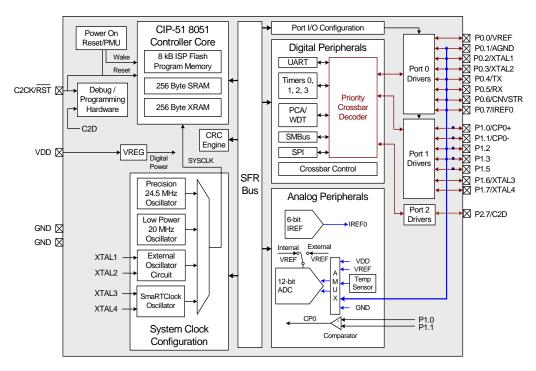

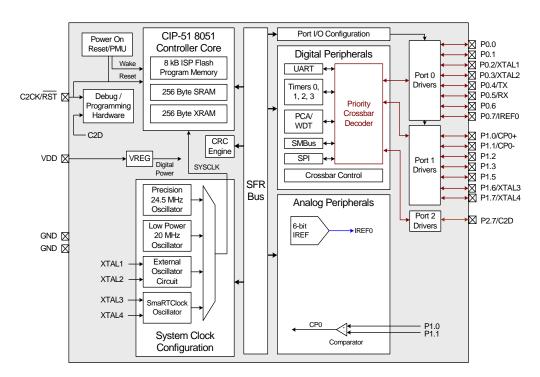

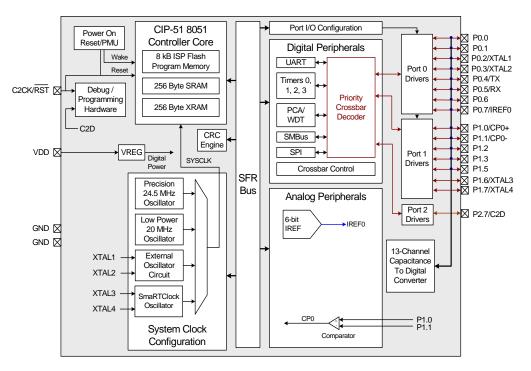

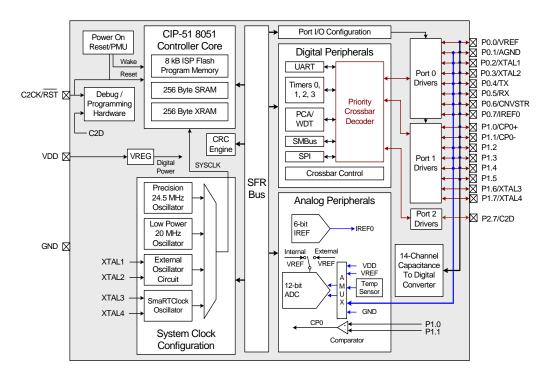

Figure 1.2. C8051F981 Block Diagram

## 1.3. Serial Ports

The C8051F99x-C8051F98x Family includes an SMBus/I<sup>2</sup>C interface, a full-duplex UART with enhanced baud rate configuration, and an Enhanced SPI interface. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little CPU intervention.

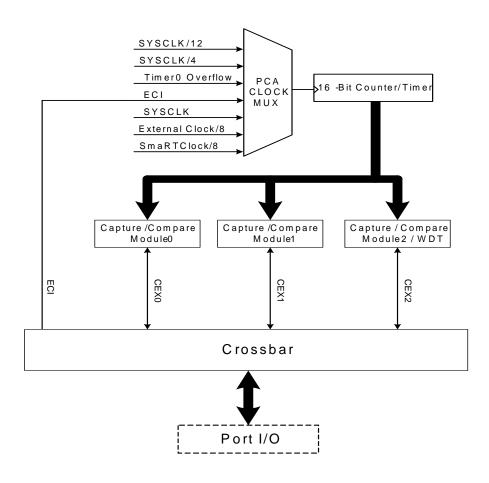

## 1.4. Programmable Counter Array

An on-chip programmable counter/timer array (PCA) is included in addition to the four 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with three programmable capture/compare modules. The PCA clock is derived from one of seven sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflows, an External Clock Input (ECI), the system clock, the external oscillator clock source divided by 8, or the SmaRTClock divided by 8.

Each capture/compare module can be configured to operate in a variety of modes: edge-triggered capture, software timer, high-speed output, pulse width modulator (8, 9, 10, 11, or 16-bit), or frequency output. Additionally, Capture/Compare Module 2 offers watchdog timer (WDT) capabilities. Following a system reset, Module 2 is configured and enabled in WDT mode. The PCA Capture/Compare Module I/O and External Clock Input may be routed to Port I/O via the Digital Crossbar.

Figure 1.15. PCA Block Diagram

## 2. Ordering Information

| Ordering Part Number | MIPS (Peak) | Flash Memory (kB) | RAM (bytes) | SmaRTClock Real Time Clock | SMBus/I <sup>2</sup> C, UART, Enhanced SPI | Timers (16-bit) | Programmable Counter Array | Digital Port I/Os | Analog to Digital Converter Inputs | ADC with internal voltage reference<br>and temperature sensor | Capacitive Touch Inputs | Programmable Current Reference | Analog Comparators | Lead-free (RoHS Compliant) | Package |

|----------------------|-------------|-------------------|-------------|----------------------------|--------------------------------------------|-----------------|----------------------------|-------------------|------------------------------------|---------------------------------------------------------------|-------------------------|--------------------------------|--------------------|----------------------------|---------|

| C8051F980-C-GM       | 25          | 8                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 16                | 9                                  | 12-bit                                                        | —                       | $\checkmark$                   | 1                  | $\checkmark$               | QFN-20  |

| C8051F981-C-GM       | 25          | 8                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 16                |                                    |                                                               | —                       | $\checkmark$                   | 1                  | $\checkmark$               | QFN-20  |

| C8051F982-C-GM       | 25          | 4                 | 512         | ~                          | ~                                          | 4               | $\checkmark$               | 16                | 9                                  | 10-bit                                                        | _                       | $\checkmark$                   | 1                  | $\checkmark$               | QFN-20  |

| C8051F983-C-GM       | 25          | 4                 | 512         | ~                          | $\checkmark$                               | 4               | $\checkmark$               | 16                | _                                  | _                                                             | _                       | $\checkmark$                   | 1                  | $\checkmark$               | QFN-20  |

| C8051F985-C-GM       | 25          | 2                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | ~                          | 16                |                                    | _                                                             | —                       | $\checkmark$                   | 1                  | $\checkmark$               | QFN-20  |

| C8051F986-C-GM       | 25          | 8                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 17                | 10                                 | 12-bit                                                        | —                       | $\checkmark$                   | 1                  | $\checkmark$               | QFN-24  |

| C8051F986-C-GU       | 25          | 8                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 17                | 10                                 | 12-bit                                                        | —                       | $\checkmark$                   | 1                  | $\checkmark$               | QSOP-24 |

| C8051F987-C-GM       | 25          | 8                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 17                | -                                  |                                                               | —                       | $\checkmark$                   | 1                  | ~                          | QFN-24  |

| C8051F987-C-GU       | 25          | 8                 | 512         | $\checkmark$               | ~                                          | 4               | $\checkmark$               | 17                |                                    |                                                               | —                       | $\checkmark$                   | 1                  | ~                          | QSOP-24 |

| C8051F988-C-GM       | 25          | 4                 | 512         | $\checkmark$               | ~                                          | 4               | $\checkmark$               | 17                | 10                                 | 10-bit                                                        | —                       | $\checkmark$                   | 1                  | $\checkmark$               | QFN-24  |

| C8051F988-C-GU       | 25          | 4                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 17                | 10                                 | 10-bit                                                        | —                       | $\checkmark$                   | 1                  | $\checkmark$               | QSOP-24 |

| C8051F989-C-GM       | 25          | 4                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 17                | —                                  |                                                               | —                       | $\checkmark$                   | 1                  | $\checkmark$               | QFN-24  |

| C8051F989-C-GU       | 25          | 4                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 17                | _                                  |                                                               | —                       | $\checkmark$                   | 1                  | $\checkmark$               | QSOP-24 |

| C8051F990-C-GM       | 25          | 8                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 16                | 9                                  | 12-bit                                                        | 13                      | $\checkmark$                   | 1                  | $\checkmark$               | QFN-20  |

| C8051F991-C-GM       | 25          | 8                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 16                | _                                  |                                                               | 13                      | $\checkmark$                   | 1                  | $\checkmark$               | QFN-20  |

| C8051F996-C-GM       | 25          | 8                 | 512         | $\checkmark$               | ~                                          | 4               | $\checkmark$               | 17                | 10                                 | 12-bit                                                        | 14                      | $\checkmark$                   | 1                  | $\checkmark$               | QFN-24  |

| C8051F996-C-GU       | 25          | 8                 | 512         | $\checkmark$               | ~                                          | 4               | $\checkmark$               | 17                | 10                                 | 12-bit                                                        | 14                      | $\checkmark$                   | 1                  | $\checkmark$               | QSOP-24 |

| C8051F997-C-GM       | 25          | 8                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 17                | —                                  | —                                                             | 14                      | $\checkmark$                   | 1                  | $\checkmark$               | QFN-24  |

| C8051F997-C-GU       | 25          | 8                 | 512         | $\checkmark$               | $\checkmark$                               | 4               | $\checkmark$               | 17                | —                                  |                                                               | 14                      | $\checkmark$                   | 1                  | $\checkmark$               | QSOP-24 |

### Table 2.1. Product Selection Guide

**Note:** Starting with silicon revision C, the ordering part numbers have been updated to include the silicon revision and use this format: "C8051F990-C-GM". Package marking diagrams are included as Figure 3.4, Figure 3.5, and Figure 3.6 to identify the silicon revision.

### **Table 4.5. Power Management Electrical Specifications**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                 | Conditions                  | Min | Тур | Max | Units   |

|---------------------------|-----------------------------|-----|-----|-----|---------|

| Idle Mode Wake-up Time    |                             | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time | CLKDIV = 0x00               |     | 400 | _   | ns      |

|                           | Low Power or Precision Osc. |     |     |     |         |

| Sleep Mode Wake-up Time   |                             |     | 2   | _   | μs      |

|                           |                             |     |     |     |         |

#### Table 4.6. Flash Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameter        | Conditions                       | Min  | Тур  | Max | Units                 |

|------------------|----------------------------------|------|------|-----|-----------------------|

| Flash Size       | C8051F980/1/6/7, C8051F990/1/6/7 | 8192 | _    |     | bytes                 |

|                  | C8051F982/3/8/9                  | 4096 | —    | _   | bytes                 |

|                  | C8051F985                        | 2048 | —    | _   | bytes                 |

| Endurance        |                                  | 20 k | 100k | _   | Erase/Write<br>Cycles |

| Erase Cycle Time |                                  | 28   | 32   | 36  | ms                    |

| Write Cycle Time |                                  | 57   | 64   | 71  | μs                    |

### **Table 4.7. Internal Precision Oscillator Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                                                           | Conditions                                    | Min | Тур  | Max | Units |  |

|---------------------------------------------------------------------|-----------------------------------------------|-----|------|-----|-------|--|

| Oscillator Frequency                                                | −40 to +85 °C,<br>V <sub>DD</sub> = 1.8−3.6 V | 24  | 24.5 | 25  | MHz   |  |

| Oscillator Supply Current<br>(from V <sub>DD</sub> )                | 25 °C; includes bias current<br>of 90–100 μA  | _   | 300* | _   | μA    |  |

| *Note: Does not include clock divider or clock tree supply current. |                                               |     |      |     |       |  |

### Table 4.8. Internal Low-Power Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                                            | Conditions                                    | Min | Тур  | Max | Units |

|------------------------------------------------------|-----------------------------------------------|-----|------|-----|-------|

| Oscillator Frequency                                 | −40 to +85 °C,<br>V <sub>DD</sub> = 1.8−3.6 V | 18  | 20   | 22  | MHz   |

| Oscillator Supply Current<br>(from V <sub>DD</sub> ) | 25 °C<br>No separate bias current<br>required | _   | 100* | _   | μA    |

| *Note: Does not include clock di                     | vider or clock tree supply current.           | •   | •    | •   | •     |

## Table 4.10. ADC0 Electrical Characteristics (Continued)

$V_{DD}$  = 1.8 to 3.6 V, VREF = 1.65 V (REFSL[1:0] = 11), -40 to +85 °C unless otherwise specified.

| Parameter                                                  | Conditions                                                                                                                                            | Min | Тур                      | Max  | Units    |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------|------|----------|

| Analog Inputs                                              |                                                                                                                                                       |     |                          |      |          |

| ADC Input Voltage Range                                    | Single Ended (AIN+ – GND)                                                                                                                             | 0   | —                        | VREF | V        |

| Absolute Pin Voltage with respect to GND                   | Single Ended                                                                                                                                          | 0   | _                        | VDD  | V        |

| Sampling Capacitance                                       | 1x Gain<br>0.5x Gain                                                                                                                                  | _   | 16<br>13                 | —    | pF       |

| Input Multiplexer Impedance                                |                                                                                                                                                       | —   | 5                        |      | kΩ       |

| Power Specifications                                       |                                                                                                                                                       |     |                          | 11   |          |

| Power Supply Current<br>(V <sub>DD</sub> supplied to ADC0) | Normal Power Mode:<br>Conversion Mode (300 ksps)<br>Tracking Mode (0 ksps)<br>Low Power Mode:<br>Conversion Mode (150 ksps)<br>Tracking Mode (0 ksps) |     | 650<br>740<br>370<br>400 |      | μA       |

| Power Supply Rejection                                     | Internal High Speed VREF<br>External VREF                                                                                                             |     | 67<br>74                 | —    | dB       |

| •                                                          | 12-bit mode do not include the first on the first of the first of the full Scale Error                                                                |     |                          |      | um code. |

**3.** Performance in 8-bit mode is similar to 10-bit mode.

### Table 4.11. Temperature Sensor Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                           | Conditions           | Min | Тур  | Max | Units |

|-------------------------------------|----------------------|-----|------|-----|-------|

| Linearity                           |                      | —   | ±1   | _   | °C    |

| Slope                               |                      | _   | 3.40 | —   | mV/°C |

| Slope Error*                        |                      | _   | 40   | _   | µV/°C |

| Offset                              | Temp = 25 °C         | _   | 1025 | _   | mV    |

| Offset Error*                       | Temp = 25 °C         | _   | 18   | —   | mV    |

| Temperature Sensor Turn-On<br>Time  |                      | —   | 1.7  |     | μs    |

| Supply Current                      |                      | —   | 35   | _   | μA    |

| *Note: Represents one standard devi | ation from the mean. | •   |      |     |       |

## 5.2. Modes of Operation

ADC0 has a maximum conversion speed of 300 ksps in 10-bit mode. The ADC0 conversion clock (SARCLK) is a divided version of the system clock when burst mode is disabled (BURSTEN = 0), or a divided version of the low power oscillator when burst mode is enabled (BURSEN = 1). The clock divide value is determined by the AD0SC bits in the ADC0CF register.

### 5.2.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2–0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a 1 to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 3 overflow

- 5. A rising edge on the CNVSTR input signal (pin P0.6)

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. When Timer 2 or Timer 3 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2/3 is in 16-bit mode. See "25. Timers" on page 278 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.6. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.6 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.6, set to 1 Bit 6 in register P0SKIP. See "21. Port Input/Output" on page 215 for details on Port I/O configuration.

## SFR Definition 5.2. ADC0CF: ADC0 Configuration

| Bit   | 7               | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                      | 4 | 3        | 2      | 1     | 0       |  |

|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|--------|-------|---------|--|

| Nam   | e               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | AD0SC[4:0]                                                                                                                                                                                                                                                                                                                                                             |   |          | AD08BE | AD0TM | AMP0GN  |  |

| Туре  | •               | R/W R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                        |   |          |        |       |         |  |

| Rese  | t 1             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                      | 1 | 1        | 0      | 0     | 0       |  |

| SFR F | age = 0x0; SI   | R Address =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | = 0x97                                                                                                                                                                                                                                                                                                                                                                 |   |          | •      | •     |         |  |

| Bit   | Name            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                        |   | Functior | 1      |       |         |  |

| 7:3   | AD0SC[4:0]      | ADC0 SAR Conversion Clock Divider.<br>SAR Conversion clock is derived from FCLK by the following equation, where<br>AD0SC refers to the 5-bit value held in bits AD0SC[4:0]. SAR Conversion clock<br>requirements are given in Table 4.10.<br>BURSTEN = 0: FCLK is the current system clock.<br>BURSTEN = 1: FCLK is the 20 MHz low power oscillator, independent of the syste<br>clock.<br>$AD0SC = \frac{FCLK}{CLK_{SAR}} - 1 *$<br>*Round the result up.<br>or<br>$CLK_{SAR} = \frac{FCLK}{AD0SC + 1}$ |                                                                                                                                                                                                                                                                                                                                                                        |   |          |        |       | n clock |  |

| 2     | AD08BE          | 0: ADC0 op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC0 8-Bit Mode Enable.<br>0: ADC0 operates in 10-bit mode (normal operation).<br>1: ADC0 operates in 8-bit mode.                                                                                                                                                                                                                                                      |   |          |        |       |         |  |

| 1     | AD0TM<br>AMP0GN | Selects betw<br>0: Normal T<br>lowing the s<br>1: Delayed<br>cycles follow<br>this time.                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC0 Track Mode.<br>Selects between Normal or Delayed Tracking Modes.<br>0: Normal Track Mode: When ADC0 is enabled, conversion begins immediately fol-<br>lowing the start-of-conversion signal.<br>1: Delayed Track Mode: When ADC0 is enabled, conversion begins 3 SAR clock<br>cycles following the start-of-conversion signal. The ADC is allowed to track during |   |          |        |       |         |  |

|       |                 | 0: The on-c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | hip PGA gai<br>hip PGA gai                                                                                                                                                                                                                                                                                                                                             |   |          |        |       |         |  |

## SFR Definition 8.3. CS0DH: Capacitive Sense Data High Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| Name  |   | CS0DH[7:0] |   |   |   |   |   |   |

| Туре  | R | R          | R | R | R | R | R | R |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xEE

| Bit | Name  | Description                                                                    |

|-----|-------|--------------------------------------------------------------------------------|

| 7:0 | CS0DH | CS0 Data High Byte.                                                            |

|     |       | Stores the high byte of the last completed 16-bit Capacitive Sense conversion. |

## SFR Definition 8.4. CS0DL: Capacitive Sense Data Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|------------|---|---|---|---|---|---|--|

| Name  |   | CS0DL[7:0] |   |   |   |   |   |   |  |

| Туре  | R | R          | R | R | R | R | R | R |  |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Page = 0x0; SFR Address = 0xED

| Bit | Name  | Description                                                                   |

|-----|-------|-------------------------------------------------------------------------------|

| 7:0 | CS0DL | CS0 Data Low Byte.                                                            |

|     |       | Stores the low byte of the last completed 16-bit Capacitive Sense conversion. |

## SFR Definition 13.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

### SFR Page = All; SFR Address = 0xA8; Bit-Addressable

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

## SFR Definition 13.7. IT01CF: INT0/INT1 Configuration

| Bit   | 7     | 6   | 5          | 4 | 3   | 2          | 1   | 0 |

|-------|-------|-----|------------|---|-----|------------|-----|---|

| Name  | IN1PL |     | IN1SL[2:0] |   |     | IN0SL[2:0] |     |   |

| Туре  | R/W   | R/W |            |   | R/W |            | R/W |   |

| Reset | 0     | 0   | 0          | 0 | 0   | 0          | 0   | 1 |

#### SFR Page = 0x0; SFR Address = 0xE4

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IN1PL      | INT1 Polarity.         0: INT1 input is active low.         1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6:4 | IN1SL[2:0] | INT1 Port Pin Selection Bits.         These bits select which Port pin is assigned to INT1. Note that this pin assignment is independent of the Crossbar; INT1 will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.         000: Select P0.0         001: Select P0.1         010: Select P0.2         011: Select P0.3         100: Select P0.4         101: Select P0.5         111: Select P0.7 |

| 3   | IN0PL      | INTO Polarity.<br>0: INTO input is active low.<br>1: INTO input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2:0 | IN0SL[2:0] | <b>INTO</b> Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INTO. Note that this pin assignment is independent of the Crossbar; INTO will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P0.0<br>001: Select P0.1<br>010: Select P0.2<br>011: Select P0.3<br>100: Select P0.4<br>101: Select P0.5<br>110: Select P0.6<br>111: Select P0.7              |

## SFR Definition 14.3. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

| Name  |   |   |   |   |   |   | PSEE | PSWE |

| Туре  | R | R | R | R | R | R | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

### SFR Page =All; SFR Address = 0x8F

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1   | PSEE   | Program Store Erase Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit (in combination with PSWE) allows an entire page of Flash program memory to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> <li>1: Flash program memory erasure enabled.</li> </ul> |

| 0   | PSWE   | Program Store Write Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul>                                                                                                                                                     |

## SFR Definition 19.4. OSCXCN: External Oscillator Control

| Bit   | 7       | 6   | 5           | 4   | 3   | 2         | 1   | 0   |

|-------|---------|-----|-------------|-----|-----|-----------|-----|-----|

| Name  | XCLKVLD | Х   | XOSCMD[2:0] |     |     | XFCN[2:0] |     |     |

| Туре  | R       | R/W | R/W         | R/W | R/W | R/W       | R/W | R/W |

| Reset | 0       | 0   | 0           | 0   | 0   | 0         | 0   | 0   |

SFR Page = 0x0; SFR Address = 0xB1

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | XCLKVLD  | External Oscillator Valid Flag.                                                                                                                                                                                                                                                                                                                           |

|     |          | <ul> <li>Provides External Oscillator status and is valid at all times for all modes of operation except External CMOS Clock Mode and External CMOS Clock Mode with divide by</li> <li>In these modes, XCLKVLD always returns 0.</li> <li>External Oscillator is unused or not yet stable.</li> <li>External Oscillator is running and stable.</li> </ul> |

| 6:4 | XOSCMD   | External Oscillator Mode Bits.                                                                                                                                                                                                                                                                                                                            |

|     |          | Configures the external oscillator circuit to the selected mode.<br>00x: External Oscillator circuit disabled.<br>010: External CMOS Clock Mode.<br>011: External CMOS Clock Mode with divide by 2 stage.<br>100: RC Oscillator Mode.<br>101: Capacitor Oscillator Mode.<br>110: Crystal Oscillator Mode.                                                 |

| 2   | Decerved | 111: Crystal Oscillator Mode with divide by 2 stage.                                                                                                                                                                                                                                                                                                      |

| 3   | Reserved | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                                                 |

| 2:0 | XFCN     | External Oscillator Frequency Control Bits.                                                                                                                                                                                                                                                                                                               |

|     |          | Controls the external oscillator bias current.<br>000-111: See Table 19.1 on page 190 (Crystal Mode) or Table 19.2 on page 191 (RC<br>or C Mode) for recommended settings.                                                                                                                                                                                |

### 20.1.5. RTC0ADR Autoincrement Feature

For ease of reading and writing the 32-bit CAPTURE and ALARM values, RTC0ADR automatically increments after each read or write to a CAPTUREn or ALARMn register. This speeds up the process of setting an alarm or reading the current SmaRTClock timer value. Autoincrement is always enabled.

Recommended Instruction Timing for a multi-byte register read with short strobe and auto read enabled:

Recommended Instruction Timing for a multi-byte register write with short strobe enabled:

mov RTCOADR, #010h

mov RTCODAT, #05h

nop

mov RTCODAT, #06h

nop

mov RTCODAT, #07h

nop

mov RTCODAT, #08h

nop

### 20.3.3. Software Considerations for using the SmaRTClock Timer and Alarm

The SmaRTClock timer and alarm have two operating modes to suit varying applications. The two modes are described below:

#### Mode 1:

The first mode uses the SmaRTClock timer as a perpetual timebase which is never reset to zero. Every 36 hours, the timer is allowed to overflow without being stopped or disrupted. The alarm interval is software managed and is added to the ALRMn registers by software after each alarm. This allows the alarm match value to always stay ahead of the timer by one software managed interval. If software uses 32-bit unsigned addition to increment the alarm match value, then it does not need to handle overflows since both the timer and the alarm match value will overflow in the same manner.

This mode is ideal for applications which have a long alarm interval (e.g., 24 or 36 hours) and/or have a need for a perpetual timebase. An example of an application that needs a perpetual timebase is one whose wake-up interval is constantly changing. For these applications, software can keep track of the number of timer overflows in a 16-bit variable, extending the 32-bit (36 hour) timer to a 48-bit (272 year) perpetual timebase.

#### Mode 2:

The second mode uses the SmaRTClock timer as a general purpose up counter which is auto reset to zero by hardware after each alarm. The alarm interval is managed by hardware and stored in the ALRMn registers. Software only needs to set the alarm interval once during device initialization. After each alarm, software should keep a count of the number of alarms that have occurred in order to keep track of time.

This mode is ideal for applications that require minimal software intervention and/or have a fixed alarm interval. This mode is the most power efficient since it requires less CPU time per alarm.

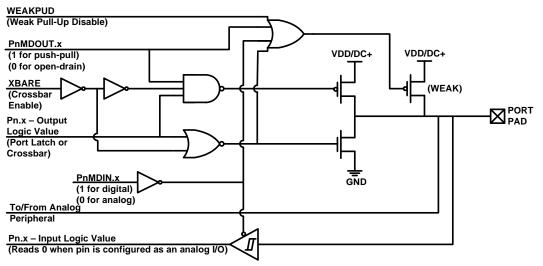

## 21.1. Port I/O Modes of Operation

Port pins P0.0–P1.7 use the Port I/O cell shown in Figure 21.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN registers. On reset, all Port I/O cells default to a digital high impedance state with weak pull-ups enabled.

### 21.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, oscillator input/output, or AGND, VREF, or Current Reference output should be configured for analog I/O (PnMDIN.n = 0). When a pin is configured for analog I/O, its weak pullup and digital receiver are disabled. In most cases, software should also disable the digital output drivers. Port pins configured for analog I/O will always read back a value of 0 regardless of the actual voltage on the pin.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

### 21.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high and low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user must ensure that digital I/O are always internally or externally pulled or driven to a valid logic state. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

Figure 21.2. Port I/O Cell Block Diagram

## SFR Definition 22.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7     | 6   | 5    | 4       | 3      | 2      | 1    | 0          |  |

|-------|-------|-----|------|---------|--------|--------|------|------------|--|

| Name  | ENSMB | INH | BUSY | EXTHOLD | SMBTOE | SMBFTE | SMBC | SMBCS[1:0] |  |

| Туре  | R/W   | R/W | R    | R/W     | R/W    | R/W    | R/   | R/W        |  |

| Reset | 0     | 0   | 0    | 0       | 0      | 0      | 0    | 0          |  |

## SFR Page = 0x0; SFR Address = 0xC1

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENSMB      | SMBus Enable.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit enables the SMBus interface when set to 1. When enabled, the interface constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                                                                                                             |

| 6   | INH        | SMBus Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the SMBus does not generate an interrupt when slave events occur. This effectively removes the SMBus slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                    |

| 5   | BUSY       | SMBus Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                |

| 4   | EXTHOLD    | SMBus Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | This bit controls the SDA setup and hold times according to Table 22.2.<br>0: SDA Extended Setup and Hold Times disabled.<br>1: SDA Extended Setup and Hold Times enabled.                                                                                                                                                                                                                                                            |

| 3   | SMBTOE     | SMBus SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | This bit enables SCL low timeout detection. If set to logic 1, the SMBus forces<br>Timer 3 to reload while SCL is high and allows Timer 3 to count when SCL goes low.<br>If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in reload<br>while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms,<br>and the Timer 3 interrupt service routine should reset SMBus communication. |

| 2   | SMBFTE     | SMBus Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                              |

| 1:0 | SMBCS[1:0] | SMBus Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | These two bits select the SMBus clock source, which is used to generate the SMBus<br>bit rate. The selected device should be configured according to Equation 22.1.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10:Timer 2 High Byte Overflow                                                                                                                                                                                  |

|     |            | 11: Timer 2 Low Byte Overflow                                                                                                                                                                                                                                                                                                                                                                                                         |

## SFR Definition 25.8. TMR2CN: Timer 2 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1           | 0 |

|-------|------|------|--------|--------|---------|-----|-------------|---|

| Name  | TF2H | TF2L | TF2LEN | TF2CEN | T2SPLIT | TR2 | T2XCLK[1:0] |   |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R/W         |   |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0           | 0 |

### SFR Page = 0x0; SFR Address = 0xC8; Bit-Addressable

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF2H        | <b>Timer 2 High Byte Overflow Flag.</b><br>Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                          |

| 6   | TF2L        | Timer 2 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |             | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5   | TF2LEN      | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |             | When set to 1, this bit enables Timer 2 Low Byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 over-flows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4   | TF2CEN      | Timer 2 Capture Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |             | When set to 1, this bit enables Timer 2 Capture Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3   | T2SPLIT     | Timer 2 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |             | When set to 1, Timer 2 operates as two 8-bit timers with auto-reload. Otherwise, Timer 2 operates in 16-bit auto-reload mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2   | TR2         | Timer 2 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |             | Timer 2 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR2H only; TMR2L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |