# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status     Active       Core Processor     CIP-51 8051       Core Size     8-Bit |  |

|------------------------------------------------------------------------------------------|--|

|                                                                                          |  |

| Core Size 8-Bit                                                                          |  |

|                                                                                          |  |

| Speed 25MHz                                                                              |  |

| Connectivity SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                            |  |

| Peripherals Brown-out Detect/Reset, POR, PWM, WDT                                        |  |

| Number of I/O 17                                                                         |  |

| Program Memory Size 4KB (4K x 8)                                                         |  |

| Program Memory Type FLASH                                                                |  |

| EEPROM Size -                                                                            |  |

| RAM Size 512 x 8                                                                         |  |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6V                                                    |  |

| Data Converters -                                                                        |  |

| Oscillator Type Internal                                                                 |  |

| Operating Temperature -40°C ~ 85°C (TA)                                                  |  |

| Mounting Type Surface Mount                                                              |  |

| Package / Case 24-SSOP (0.154", 3.90mm Width)                                            |  |

| Supplier Device Package 24-QSOP                                                          |  |

| Purchase URL https://www.e-xfl.com/product-detail/silicon-labs/c8051f989-c-gur           |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 22.2 CMDue Operation                                   | 007 |

|-----|--------------------------------------------------------|-----|

|     | 22.3.SMBus Operation                                   |     |

|     | 22.3.1.Transmitter vs. Receiver                        |     |

|     | 22.3.2. Arbitration                                    |     |

|     | 22.3.3.Clock Low Extension                             |     |

|     | 22.3.4.SCL Low Timeout                                 |     |

|     | 22.3.5.SCL High (SMBus Free) Timeout                   |     |

|     | 22.4.Using the SMBus                                   |     |

|     | 22.4.1.SMBus Configuration Register                    |     |

|     | 22.4.2.SMB0CN Control Register                         |     |

|     | 22.4.3.Hardware Slave Address Recognition              | 246 |

|     | 22.4.4.Data Register                                   | 248 |

|     | 22.5.SMBus Transfer Modes                              | 249 |

|     | 22.5.1.Write Sequence (Master)                         |     |

|     | 22.5.2.Read Sequence (Master)                          | 250 |

|     | 22.5.3.Write Sequence (Slave)                          | 251 |

|     | 22.5.4.Read Sequence (Slave)                           |     |

|     | 22.6.SMBus Status Decoding                             | 252 |

| 23. | UART0                                                  | 257 |

|     | 23.1.Enhanced Baud Rate Generation                     | 258 |

|     | 23.2.Operational Modes                                 |     |

|     | 23.2.1.8-Bit UART                                      |     |

|     | 23.2.2.9-Bit UART                                      | 260 |

|     | 23.3.Multiprocessor Communications                     | 260 |

| 24. | Enhanced Serial Peripheral Interface (SPI0)            | 265 |

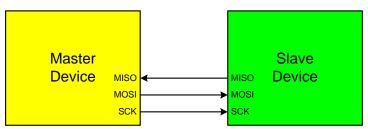

|     | 24.1.Signal Descriptions                               | 266 |

|     | 24.1.1.Master Out, Slave In (MOSI)                     | 266 |

|     | 24.1.2.Master In, Slave Out (MISO)                     | 266 |

|     | 24.1.3.Serial Clock (SCK)                              |     |

|     | 24.1.4.Slave Select (NSS)                              | 266 |

|     | 24.2.SPI0 Master Mode Operation                        | 266 |

|     | 24.3.SPI0 Slave Mode Operation                         | 268 |

|     | 24.4.SPI0 Interrupt Sources                            | 269 |

|     | 24.5.Serial Clock Phase and Polarity                   | 269 |

|     | 24.6.SPI Special Function Registers                    | 271 |

| 25. | Timers                                                 |     |

|     | 25.1.Timer 0 and Timer 1                               | 280 |

|     | 25.1.1.Mode 0: 13-bit Counter/Timer                    | 280 |

|     | 25.1.2.Mode 1: 16-bit Counter/Timer                    | 281 |

|     | 25.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload    | 282 |

|     | 25.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) | 283 |

|     | 25.2.Timer 2                                           | 288 |

|     | 25.2.1.16-bit Timer with Auto-Reload                   | 288 |

|     | 25.2.2.8-bit Timers with Auto-Reload                   | 289 |

|     | 25.2.3.Comparator 0/SmaRTClock Capture Mode            | 290 |

|     | 25.3.Timer 3                                           | 294 |

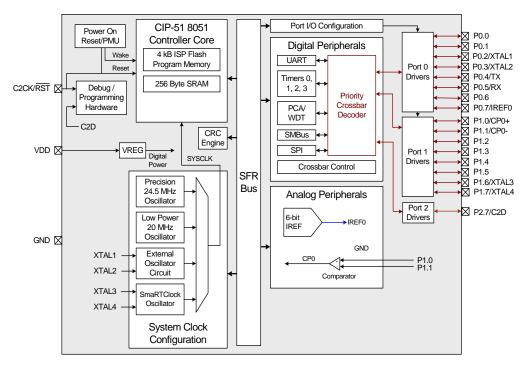

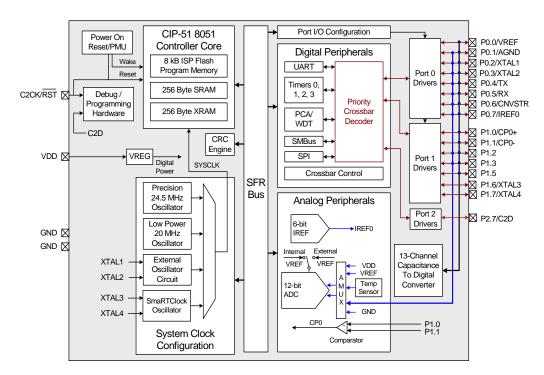

#### 1.1. CIP-51<sup>™</sup> Microcontroller Core

#### 1.1.1. Fully 8051 Compatible

The C8051F99x-C8051F98x family utilizes Silicon Labs' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The CIP-51 core offers all the peripherals included with a standard 8052.

#### 1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12-to-24 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS.

#### 1.1.3. Additional Features

The C8051F99x-C8051F98x SoC family includes several key enhancements to the CIP-51 core and peripherals to improve performance and ease of use in end applications.

The extended interrupt handler provides multiple interrupt sources into the CIP-51 allowing numerous analog and digital peripherals to interrupt the controller. An interrupt driven system requires less intervention by the MCU, giving it more effective throughput. The extra interrupt sources are very useful when building multi-tasking, real-time systems.

Eight reset sources are available: power-on reset circuitry (POR), an on-chip V<sub>DD</sub> monitor (forces reset when power supply voltage drops below safe levels), a Watchdog Timer, a Missing Clock Detector, SmaRTClock oscillator fail or alarm, a voltage level detection from Comparator0, a forced software reset, an external reset pin, and an illegal Flash access protection circuit. Each reset source except for the POR, Reset Input Pin, or Flash error may be disabled by the user in software. The WDT may be permanently disabled in software after a power-on reset during MCU initialization.

The internal oscillator is factory calibrated to 24.5 MHz and is accurate to ±2% over the full temperature and supply range. The internal oscillator period can also be adjusted by user firmware. An additional 20 MHz low power oscillator is also available which facilitates low-power operation. An external oscillator drive circuit is included, allowing an external crystal, ceramic resonator, capacitor, RC, or CMOS clock source to generate the system clock. If desired, the system clock source may be switched on-the-fly between both internal and external oscillator circuits. An external oscillator can also be extremely useful in low power applications, allowing the MCU to run from a slow (power saving) source, while periodically switching to the fast (up to 25 MHz) internal oscillator as needed.

|                       | Pin                                    | Number                               | S                                    |                  |                                                                                                                                |  |  |

|-----------------------|----------------------------------------|--------------------------------------|--------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name                  | 'F980/1/2<br>'F983/5<br>'F990/1<br>-GM | 'F986/7<br>'F988/9<br>'F996/7<br>-GM | 'F986/7<br>'F988/9<br>'F996/7<br>-GU | Туре             | Description                                                                                                                    |  |  |

| P0.6/                 | 16                                     | 18                                   | 21                                   | D I/O or<br>A In | Port 0.6. See Section "21. Port Input/Output" on page 215 for a complete description.                                          |  |  |

| CNVSTR*               |                                        |                                      |                                      | D In             | External Convert Start Input for ADC0. See Section<br>"5.7. ADC0 Analog Multiplexer" on page 83 for a<br>complete description. |  |  |

| P0.7/                 | 15                                     | 17                                   | 20                                   | A In             | Port 0.7. See Section "21. Port Input/Output" on page 215 for a complete description.                                          |  |  |

| IREF0                 |                                        |                                      |                                      | A Out            | IREF0 Output. See IREF Section for complete description.                                                                       |  |  |

| P1.0                  | 14                                     | 16                                   | 19                                   | D I/O or<br>A In | Port 1.0. See Section "21. Port Input/Output" on page 215 for a complete description. May also be used as SCK for SPI1.        |  |  |

| CP0+                  |                                        |                                      |                                      | A In             | Comparator0 positive input. See Comparator Section for complete description.                                                   |  |  |

| P1.1                  | 13                                     | 15                                   | 18                                   | D I/O or<br>A In | Port 1.1. See Section "21. Port Input/Output" on page 215 for a complete description.                                          |  |  |

| CP0-                  |                                        |                                      |                                      | A In             | Comparator0 negative input. See Comparator Section for complete description.                                                   |  |  |

| P1.2                  | 11                                     | 14                                   | 17                                   | D I/O or<br>A In | Port 1.2. See Section "21. Port Input/Output" on page 215 for a complete description.                                          |  |  |

| P1.3                  | 10                                     | 13                                   | 16                                   | D I/O or<br>A In | Port 1.3. See Section "21. Port Input/Output" on page 215 for a complete description.                                          |  |  |

| P1.4                  | —                                      | 12                                   | 15                                   | D I/O or<br>A In | Port 1.4. See Section "21. Port Input/Output" on page 215 for a complete description.                                          |  |  |

| P1.5                  | 9                                      | 11                                   | 14                                   | D I/O or<br>A In | Port 1.5. See Section "21. Port Input/Output" on page 215 for a complete description.                                          |  |  |

| * <b>Note:</b> Availa | ble only on t                          | he C805′                             | 1F980/2/6                            | 6/8 and C8       | 051F990/6 devices.                                                                                                             |  |  |

### Table 3.1. Pin Definitions for the C8051F99x-C8051F98x (Continued)

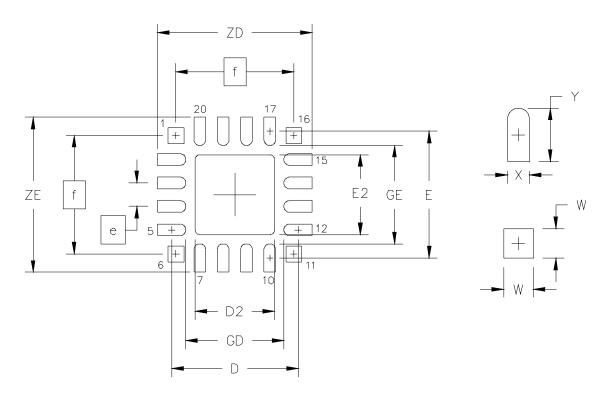

Figure 3.8. Typical QFN-20 Landing Diagram

### SFR Definition 5.5. ADC0TK: ADC0 Burst Mode Track Time

| Bit   | 7        | 6 | 5          | 4   | 3 | 2 | 1 | 0 |  |

|-------|----------|---|------------|-----|---|---|---|---|--|

| Name  | Reserved |   | AD0TK[5:0] |     |   |   |   |   |  |

| Туре  | R        | R |            | R/W |   |   |   |   |  |

| Reset | 0        | 0 | 0          | 1   | 1 | 1 | 1 | 0 |  |

#### SFR Page = All; SFR Address = 0xBC

| Bit         | Name       | Function                                                                                            |

|-------------|------------|-----------------------------------------------------------------------------------------------------|

| 7           | Reserved   | Read = 0b; Write = Must Write 0b.                                                                   |

| 6           | Unused     | Read = 0b; Write = Don't Care.                                                                      |

| 5:0         | AD0TK[5:0] | ADC0 Burst Mode Track Time.                                                                         |

|             |            | Sets the time delay between consecutive conversions performed in Burst Mode.                        |

|             |            | The ADC0 Burst Mode Track time is programmed according to the following equa-<br>tion:              |

|             |            | $AD0TK = 63 - \left(\frac{Ttrack}{50ns} - 1\right)$<br>or                                           |

|             |            | Ttrack = (64 - AD0TK)50ns                                                                           |

| Notes<br>1. |            | I<br>et to 1, an additional 3 SAR clock cycles of Track time will be inserted prior to starting the |

1. If AD0TM is set to 1, an additional 3 SAR clock cycles of Track time will be inserted prior to starting the conversion.

2. The Burst Mode Track delay is not inserted prior to the first conversion. The required tracking time for the first conversion should be met by the Burst Mode Power-Up Time.

### SFR Definition 5.12. ADC0MX: ADC0 Input Channel Select

| Bit   | 7 | 6 | 5 | 4     | 3   | 2   | 1   | 0   |  |

|-------|---|---|---|-------|-----|-----|-----|-----|--|

| Name  |   |   |   | ADOMX |     |     |     |     |  |

| Туре  | R | R | R | R/W   | R/W | R/W | R/W | R/W |  |

| Reset | 0 | 0 | 0 | 1     | 1   | 1   | 1   | 1   |  |

#### SFR Page = 0x0; SFR Address = 0x96

| Bit | Name   |             | Fu                                          | nction |                                |  |  |  |  |  |

|-----|--------|-------------|---------------------------------------------|--------|--------------------------------|--|--|--|--|--|

| 7:5 | Unused | Read = 000  | o; Write = Don't Care.                      |        |                                |  |  |  |  |  |

| 4:0 | AD0MX  | AMUX0 Pos   | sitive Input Selection.                     |        |                                |  |  |  |  |  |

|     |        | Selects the | elects the positive input channel for ADC0. |        |                                |  |  |  |  |  |

|     |        | 00000:      | Reserved.                                   | 10000: | Reserved.                      |  |  |  |  |  |

|     |        | 00001:      | P0.1                                        | 10001: | Reserved.                      |  |  |  |  |  |

|     |        | 00010:      | P0.2                                        | 10010: | Reserved.                      |  |  |  |  |  |

|     |        | 00011:      | P0.3                                        | 10011: | Reserved.                      |  |  |  |  |  |

|     |        | 00100:      | P0.4                                        | 10100: | Reserved.                      |  |  |  |  |  |

|     |        | 00101:      | P0.5                                        | 10101: | Reserved.                      |  |  |  |  |  |

|     |        | 00110:      | P0.6                                        | 10110: | Reserved.                      |  |  |  |  |  |

|     |        | 00111:      | P0.7                                        | 10111: | Reserved.                      |  |  |  |  |  |

|     |        | 01000:      | Reserved.                                   | 11000: | Reserved.                      |  |  |  |  |  |

|     |        | 01001:      | Reserved.                                   | 11001: | Reserved.                      |  |  |  |  |  |

|     |        | 01010:      | P1.2                                        | 11010: | Reserved.                      |  |  |  |  |  |

|     |        | 01011:      | P1.3                                        | 11011: | Temperature Sensor             |  |  |  |  |  |

|     |        | 01100:      | P1.4 (only available on 24-pin devices)     | 11100: | V <sub>DD</sub> Supply Voltage |  |  |  |  |  |

|     |        | 01101:      | Reserved.                                   | 11101: | Digital Supply Voltage         |  |  |  |  |  |

|     |        | 01110:      | Reserved.                                   |        | (VREG0 Output, 1.7 V Typical)  |  |  |  |  |  |

|     |        | 01111:      | Reserved.                                   | 11110: | V <sub>DD</sub> Supply Voltage |  |  |  |  |  |

|     |        |             |                                             | 11111: | Ground                         |  |  |  |  |  |

#### 5.10. External Voltage Reference

To use an external voltage reference, REFSL[1:0] should be set to 00. Bypass capacitors should be added as recommended by the manufacturer of the external voltage reference. If the manufacturer does not provide recommendations, a 4.7  $\mu$ F in parallel with a 0.1  $\mu$ F capacitor is recommended.

#### 5.11. Internal Voltage Reference

For applications requiring the maximum number of port I/O pins, or very short VREF turn-on time, the 1.65 V high-speed reference will be the best internal reference option to choose. The high speed internal reference is selected by setting REFSL[1:0] to 11. When selected, the high speed internal reference will be automatically enabled/disabled on an as-needed basis by ADC0.

For applications with a non-varying power supply voltage, using the power supply as the voltage reference can provide ADC0 with added dynamic range at the cost of reduced power supply noise rejection. To use the 1.8 to 3.6 V power supply voltage ( $V_{DD}$ ) or the 1.8 V regulated digital supply voltage as the reference source, REFSL[1:0] should be set to 01 or 10, respectively.

#### 5.12. Analog Ground Reference

To prevent ground noise generated by switching digital logic from affecting sensitive analog measurements, a separate analog ground reference option is available. When enabled, the ground reference for ADC0 during both the tracking/sampling and the conversion periods is taken from the P0.1/AGND pin. Any external sensors sampled by ADC0 should be referenced to the P0.1/AGND pin. This pin should be connected to the ground terminal of any external sensors sampled by ADC0. If an external voltage reference is used, the P0.1/AGND pin should be connected to the ground reference and its associated decoupling capacitor. The separate analog ground reference option is enabled by setting REFGND to 1. Note that when sampling the internal temperature sensor, the internal chip ground is always used for the sampling operation, regardless of the setting of the REFGND bit. Similarly, whenever the internal 1.65 V high-speed reference is selected, the internal chip ground is always used during the conversion period, regardless of the setting of the REFGND bit.

#### 5.13. Temperature Sensor Enable

The TEMPE bit in register REF0CN enables/disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data. See Section "5.8. Temperature Sensor" on page 85 for details on temperature sensor characteristics when it is enabled.

#### 8.12. CS0 Pin Monitor

The CS0 module provides accurate conversions in all operating modes of the CPU, peripherals and I/O ports. Pin monitoring circuits are provided to improve interference immunity from high-current output pin switching. The CS0 Pin Monitor register (CS0PM, SFR Definition 8.14) controls the operation of these pin monitors.

Conversions in the CS0 module are immune to any change on digital inputs and immune to most output switching. Even high-speed serial data transmission will not affect CS0 operation as long as the output load is limited. Output changes that switch large loads such as LEDs and heavily-loaded communications lines can affect conversion accuracy. For this reason, the CS0 module includes pin monitoring circuits that will, if enabled, automatically adjust conversion timing if necessary to eliminate any effect from high-current output pin switching.

The pin monitor enable bit should be set for any output signal that is expected to drive a large load.

Example: The SMBus in a system is heavily loaded with multiple slaves and a long PCB route. Set the SMBus pin monitor enable, SMBPM = 1.

Example: Timer2 controls an LED on Port 1, pin 3 to provide variable dimming. Set the Port SFR write monitor enable, PIOPM = 1.

Example: The SPI bus is used to communicate to a nearby host. The pin monitor is not needed because the output is not heavily loaded, SPIPM remains = 0, the default reset state.

Pin monitors should not be enabled unless they are required. The pin monitor works by repeating any portion of a conversion that may have been corrupted by a change on an output pin. Setting pin monitor enables bits will slow CS0 conversions.

The frequency of CS0 retry operations can be limited by setting the CSPMMD bits. In the default (reset) state, all converter retry requests will be performed. This is the recommended setting for all applications. The number of retries per conversion can be limited to either two or four retries by changing CSPMMD. Limiting the number of retries per conversion ensures that even in circumstances where extremely frequent high-power output switching occurs, conversions will be completed, though there may be some loss of accuracy due to switching noise.

Activity of the pin monitor circuit can be detected by reading the Pin Monitor Event bit, CS0PME, in register CS0CN. This bit will be set if any CS0 converter retries have occurred. It remains set until cleared by software or a device reset.

#### 8.13. Adjusting CS0 For Special Situations

There are several configuration options in the CS0 module designed to modify the operation of the circuit and address special situations. In particular, any circuit with more than 500 ohms of series impedance between the sensor and the device pin may require adjustments for optimal performance. Typical applications which may require adjustments include:

- Touch panel sensors fabricated using a resistive conductor such as indium-tin-oxide (ITO).

- Circuits using a high-value series resistor to isolate the sensor element for high ESD protection.

Most systems will require no fine tuning, and the default settings for CS0DT, CS0DR, CS0IA, CS0RP and CS0LP should be used.

### SFR Definition 8.1. CS0CN: Capacitive Sense Control

| Bit   | 7             | 6                                            | 5                                                                                                | 4                              | 3                                                 | 2             | 1             | 0        |  |

|-------|---------------|----------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------|---------------|---------------|----------|--|

| Name  | e CS0EN       | CS0EOS                                       | CS0INT                                                                                           | CS0BUSY                        | CS0CMPEN                                          | Reserved      | CS0PME        | CS0CMPF  |  |

| Туре  | R/W           | R                                            | R/W                                                                                              | R/W                            | R/W                                               | R             | R             | R        |  |

| Rese  | <b>t</b> 0    | 0                                            | 0                                                                                                | 0                              | 0                                                 | 0             | 0             | 0        |  |

| SFR P | age = 0x0; SF | R Address                                    | = 0xB0                                                                                           |                                |                                                   |               | •             | ·        |  |

| Bit   | Name          |                                              |                                                                                                  |                                | Description                                       | n             |               |          |  |

| 7     | CS0EN         |                                              | lisabled an                                                                                      | d in low-pow<br>d ready to co  |                                                   |               |               |          |  |

| 6     | CS0EOS        | 0: CS0 h<br>1: CS0 h                         | has not com<br>has complet                                                                       | ted a scan.                    | i <b>g.</b><br>an since the las<br>ared by hardwa |               | EOS was cle   | ared.    |  |

| 5     | CSOINT        | 0: CS0 h<br>cleared.<br>1: CS0 h             | CS0 Interrupt Flag.<br>0: CS0 has not completed a data conversion since the last time CS0INT was |                                |                                                   |               |               |          |  |

| 4     | CSOBUSY       | 1: CS0 c<br>Write:<br>0: No eff              | conversion<br>conversion                                                                         | is in progres                  | or a conversior<br>s.<br>60CM[2:0] = 00           |               |               | ess.     |  |

| 3     | CS0CMPEN      | Enables<br>output to<br>0: CS0 o<br>1: CS0 o | the digital<br>the value<br>ligital comp<br>ligital comp                                         |                                | which compare<br>0THH:CS0THI<br>led.              |               | ated CS0 cor  | nversion |  |

| 2     | Reserved      | Read = '                                     | Varies.                                                                                          |                                |                                                   |               |               |          |  |

| 1     | CS0PME        | CS0 Pin                                      | Monitor E                                                                                        | vent.                          |                                                   |               |               |          |  |

|       |               |                                              |                                                                                                  | re-tries have<br>eared by firm | e occurred due<br>ware.                           | e to a pin mo | onitor event. | This bit |  |

| 0     | CS0CMPF       | CS0 Dig                                      | ital Compa                                                                                       | arator Interr                  | upt Flag.                                         |               |               |          |  |

|       |               | time CS<br>1: CS0 r                          | OCMPF wa                                                                                         | s cleared.<br>ater than the    | value set by C                                    |               |               |          |  |

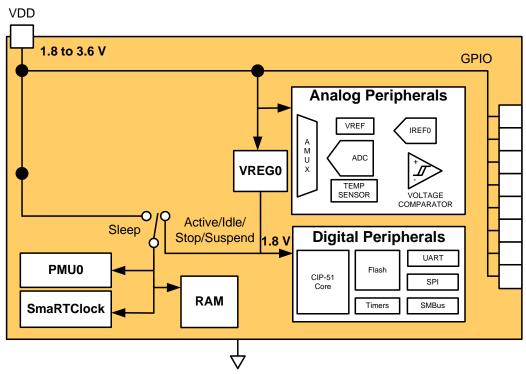

#### 15.1. Normal Mode

The MCU is fully functional in normal mode. Figure 15.1 shows the on-chip power distribution to various peripherals. There are two supply voltages powering various sections of the chip:  $V_{DD}$  and the 1.8 V internal core supply. All analog peripherals are directly powered from the  $V_{DD}$  pin. All digital peripherals and the CIP-51 core are powered from the 1.8 V internal core supply. RAM, PMU0 and the SmaRTClock are always powered directly from the  $V_{DD}$  pin in sleep mode and powered from the core supply in all other power modes.

Figure 15.1. C8051F99x-C8051F98x Power Distribution

#### 18.4. Missing Clock Detector Reset

The missing clock detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The missing clock detector reset is automatically disabled when the device is in the low power suspend or sleep mode. Upon exit from either low power state, the enabled/disabled state of this reset source is restored to its previous value. The state of the RST pin is unaffected by this reset.

#### 18.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The Comparator0 reset source remains functional even when the device is in the low power <u>susp</u>end and sleep states as long as Comparator0 is also enabled as a wake-up source. The state of the RST pin is unaffected by this reset.

#### 18.6. PCA Watchdog Timer Reset

The programmable watchdog timer (WDT) function of the programmable counter array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "26.4. Watchdog Timer Mode" on page 311; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The PCA Watchdog Timer reset source is automatically disabled when the device is in the low power suspend or sleep mode. Upon exit from either low power state, the enabled/disabled state of this reset source is restored to its previous value. The state of the RST pin is unaffected by this reset.

#### 18.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above the Lock Byte address.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above the Lock Byte address.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above the Lock Byte address.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "14.3. Security Options" on page 152).

- A Flash write or erase is attempted while the V<sub>DD</sub> Monitor is disabled.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

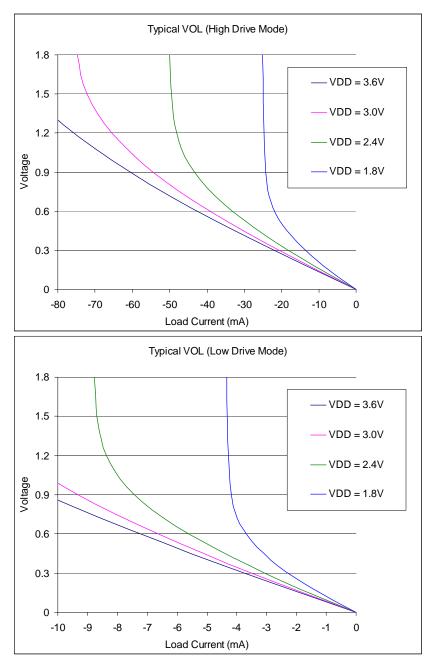

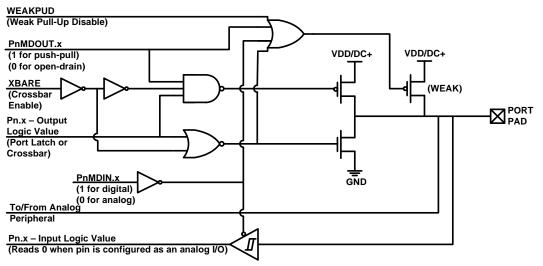

#### 21.1. Port I/O Modes of Operation

Port pins P0.0–P1.7 use the Port I/O cell shown in Figure 21.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN registers. On reset, all Port I/O cells default to a digital high impedance state with weak pull-ups enabled.

#### 21.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, oscillator input/output, or AGND, VREF, or Current Reference output should be configured for analog I/O (PnMDIN.n = 0). When a pin is configured for analog I/O, its weak pullup and digital receiver are disabled. In most cases, software should also disable the digital output drivers. Port pins configured for analog I/O will always read back a value of 0 regardless of the actual voltage on the pin.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

#### 21.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high and low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user must ensure that digital I/O are always internally or externally pulled or driven to a valid logic state. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

Figure 21.2. Port I/O Cell Block Diagram

#### SFR Definition 21.6. P1MASK: Port1 Mask Register

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-----------------|---|---|---|---|---|---|--|--|--|

| Name  |   | P1MASK[7:0]     |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |

SFR Page= 0x0; SFR Address = 0xBF

| Bit | Name        | Function                                                                                                                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MASK[7:0] | Port 1 Mask Value.                                                                                                                                                                                  |

|     |             | Selects P1 pins to be compared to the corresponding bits in P1MAT.<br>0: P1.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P1.n pin logic value is compared to P1MAT.n. |

### SFR Definition 21.7. P1MAT: Port1 Match Register

| Bit   | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|---------------|---|---|---|---|---|---|--|--|--|

| Name  |   | P1MAT[7:0]    |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W           |   |   |   |   |   |   |  |  |  |

| Reset | 1 | 1 1 1 1 1 1 1 |   |   |   |   |   |   |  |  |  |

SFR Page = 0x0; SFR Address = 0xCF

| Bit | Name       | Function                                                                                                                                                                                    |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MAT[7:0] | Port 1 Match Value.                                                                                                                                                                         |

|     |            | Match comparison value used on Port 1 for bits in P1MASK which are set to 1.<br>0: P1.n pin logic value is compared with logic LOW.<br>1: P1.n pin logic value is compared with logic HIGH. |

|                              | Frequency: 24.5 MHz          |                      |                                  |                       |                                                 |                  |                                  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | -0.32%               | 106                              | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |

| ۲.<br>۲.                     | 115200                       | -0.32%               | 212                              | SYSCLK                | XX                                              | 1                | 0x96                             |

|                              | 57600                        | 0.15%                | 426                              | SYSCLK                | XX                                              | 1                | 0x2B                             |

|                              | 28800                        | -0.32%               | 848                              | SYSCLK/4              | 01                                              | 0                | 0x96                             |

| C fr                         | 14400                        | 0.15%                | 1704                             | SYSCLK/12             | 00                                              | 0                | 0xB9                             |

| SYSCLK from<br>Internal Osc. | 9600                         | -0.32%               | 2544                             | SYSCLK/12             | 00                                              | 0                | 0x96                             |

|                              | 2400                         | -0.32%               | 10176                            | SYSCLK/48             | 10                                              | 0                | 0x96                             |

| Sy<br>Int                    | 1200                         | 0.15%                | 20448                            | SYSCLK/48             | 10                                              | 0                | 0x2B                             |

| Notes:                       |                              |                      |                                  |                       |                                                 |                  |                                  |

#### Table 23.1. Timer Settings for Standard Baud Rates Using The Internal 24.5 MHz Oscillator

SCA1–SCA0 and T1M bit definitions can be found in Section 25.1.

2. X = Don't care.

#### Table 23.2. Timer Settings for Standard Baud Rates Using an External 22.1184 MHz Oscillator

|                              | Frequency: 22.1184 MHz       |                      |                                  |                       |                                                 |                  |                                  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | 0.00%                | 96                               | SYSCLK                | XX <b>2</b>                                     | 1                | 0xD0                             |

|                              | 115200                       | 0.00%                | 192                              | SYSCLK                | XX                                              | 1                | 0xA0                             |

|                              | 57600                        | 0.00%                | 384                              | SYSCLK                | XX                                              | 1                | 0x40                             |

| from<br>Osc.                 | 28800                        | 0.00%                | 768                              | SYSCLK / 12           | 00                                              | 0                | 0xE0                             |

| ( fro<br>Os                  | 14400                        | 0.00%                | 1536                             | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |

| SYSCLK  <br>External 0       | 9600                         | 0.00%                | 2304                             | SYSCLK / 12           | 00                                              | 0                | 0xA0                             |

| SC                           | 2400                         | 0.00%                | 9216                             | SYSCLK / 48           | 10                                              | 0                | 0xA0                             |

| S Х                          | 1200                         | 0.00%                | 18432                            | SYSCLK / 48           | 10                                              | 0                | 0x40                             |

| SYSCLK from<br>Internal Osc. | 230400                       | 0.00%                | 96                               | EXTCLK / 8            | 11                                              | 0                | 0xFA                             |

|                              | 115200                       | 0.00%                | 192                              | EXTCLK / 8            | 11                                              | 0                | 0xF4                             |

|                              | 57600                        | 0.00%                | 384                              | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |

|                              | 28800                        | 0.00%                | 768                              | EXTCLK / 8            | 11                                              | 0                | 0xD0                             |

|                              | 14400                        | 0.00%                | 1536                             | EXTCLK / 8            | 11                                              | 0                | 0xA0                             |

| SY<br>Inte                   | 9600                         | 0.00%                | 2304                             | EXTCLK / 8            | 11                                              | 0                | 0x70                             |

| Notes:                       |                              |                      |                                  |                       |                                                 |                  |                                  |

1. SCA1–SCA0 and T1M bit definitions can be found in Section 25.1.

**2.** X = Don't care.

1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

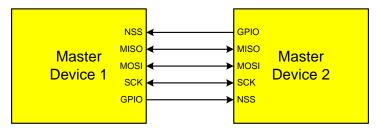

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 24.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 24.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 24.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

Figure 24.2. Multiple-Master Mode Connection Diagram

Figure 24.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

#### 25.2.3. Comparator 0/SmaRTClock Capture Mode

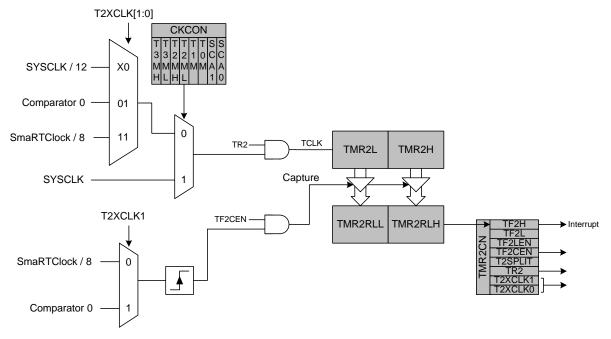

The Capture Mode in Timer 2 allows either Comparator 0 or the SmaRTClock period to be measured against the system clock or the system clock divided by 12. Comparator 0 and the SmaRTClock period can also be compared against each other. Timer 2 Capture Mode is enabled by setting TF2CEN to 1. Timer 2 should be in 16-bit auto-reload mode when using Capture Mode.

When Capture Mode is enabled, a capture event will be generated either every Comparator 0 rising edge or every 8 SmaRTClock clock cycles, depending on the T2XCLK1 setting. When the capture event occurs, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set (triggering an interrupt if Timer 2 interrupts are enabled). By recording the difference between two successive timer capture values, the Comparator 0 or SmaRT-Clock period can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading.

For example, if T2ML = 1b, T2XCLK1 = 0b, and TF2CEN = 1b, Timer 2 will clock every SYSCLK and capture every SmaRTClock clock divided by 8. If the SYSCLK is 24.5 MHz and the difference between two successive captures is 5984, then the SmaRTClock clock is as follows:

24.5 MHz/(5984/8) = 0.032754 MHz or 32.754 kHz.

This mode allows software to determine the exact SmaRTClock frequency in self-oscillate mode and the time between consecutive Comparator 0 rising edges, which is useful for detecting changes in the capacitance of a Touch Sense Switch.

Figure 25.6. Timer 2 Capture Mode Block Diagram

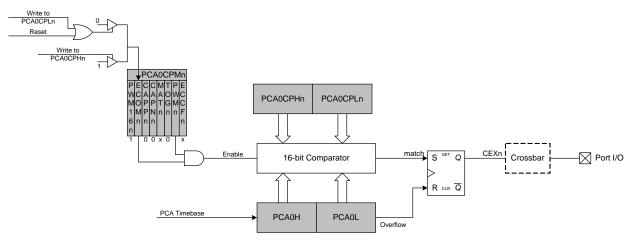

#### 26.3.6. 16-Bit Pulse Width Modulator Mode

A PCA module may also be operated in 16-Bit PWM mode. 16-bit PWM mode is independent of the other (8/9/10/11-bit) PWM modes. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. If the MATn bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF flag in PCA0CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 26.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

$$Duty Cycle = \frac{(65536 - PCA0CPn)}{65536}$$

Equation 26.4. 16-Bit PWM Duty Cycle

Using Equation 26.4, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

310

### SFR Definition 26.3. PCA0PWM: PCA PWM Configuration

| Bit   | 7     | 6    | 5    | 4 | 3 | 2 | 1          | 0 |

|-------|-------|------|------|---|---|---|------------|---|

| Name  | ARSEL | ECOV | COVF |   |   |   | CLSEL[1:0] |   |

| Туре  | R/W   | R/W  | R/W  | R | R | R | R/W        |   |

| Reset | 0     | 0    | 0    | 0 | 0 | 0 | 0          | 0 |

#### SFR Page = 0x0; SFR Address = 0xDF

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ARSEL      | Auto-Reload Register Select.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | This bit selects whether to read and write the normal PCA capture/compare registers (PCA0CPn), or the Auto-Reload registers at the same SFR addresses. This function is used to define the reload value for 9, 10, and 11-bit PWM modes. In all other modes, the Auto-Reload registers have no function.<br>0: Read/Write Capture/Compare Registers at PCA0CPHn and PCA0CPLn.<br>1: Read/Write Auto-Reload Registers at PCA0CPHn and PCA0CPLn.               |

| 6   | ECOV       | Cycle Overflow Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit sets the masking of the Cycle Overflow Flag (COVF) interrupt.<br>0: COVF will not generate PCA interrupts.                                                                                                                                                                                                                                                                                                                                          |

|     |            | 1: A PCA interrupt will be generated when COVF is set.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5   | COVF       | Cycle Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | <ul> <li>This bit indicates an overflow of the 8th, 9th, 10th, or 11th bit of the main PCA counter (PCA0). The specific bit used for this flag depends on the setting of the Cycle Length Select bits. The bit can be set by hardware or software, but must be cleared by software.</li> <li>0: No overflow has occurred since the last time this bit was cleared.</li> <li>1: An overflow has occurred since the last time this bit was cleared.</li> </ul> |

| 4:2 | Unused     | Read = 000b; Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1:0 | CLSEL[1:0] | <b>Cycle Length Select.</b><br>When 16-bit PWM mode is not selected, these bits select the length of the PWM cycle, between 8, 9, 10, or 11 bits. This affects all channels configured for PWM which                                                                                                                                                                                                                                                         |

|     |            | are not using 16-bit PWM mode. These bits are ignored for individual channels configured to16-bit PWM mode.                                                                                                                                                                                                                                                                                                                                                  |

|     |            | 00: 8 bits.<br>01: 9 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | 10: 10 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | 11: 11 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |