Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                     |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                           |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 4KB (4K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                            |

| Supplier Device Package    | 24-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f989-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F99x-C8051F98x

| 40.4 latermust later ex                                            | 400 |

|--------------------------------------------------------------------|-----|

| 13.4.Interrupt Latency                                             | 139 |

| 13.5.Interrupt Register Descriptions                               | 141 |

| 13.6.External Interrupts INTO and INT1                             |     |

| 14. Flash Memory                                                   |     |

| 14.1.Programming the Flash Memory                                  |     |

| 14.1.1.Flash Lock and Key Functions                                |     |

| 14.1.2.Flash Erase Procedure                                       |     |

| 14.1.3.Flash Write Procedure                                       |     |

| 14.2.Non-volatile Data Storage                                     |     |

| 14.3.Security Options                                              |     |

| 14.4.Determining the Device Part Number at Run Time                |     |

| 14.5.Flash Write and Erase Guidelines                              |     |

| 14.5.1.V <sub>DD</sub> Maintenance and the V <sub>DD</sub> Monitor | 156 |

| 14.5.2.PSWE Maintenance                                            | 157 |

| 14.5.3.System Clock                                                | 157 |

| 14.6.Minimizing Flash Read Current                                 |     |

| 15. Power Management                                               |     |

| 15.1.Normal Mode                                                   | 163 |

| 15.2.Idle Mode                                                     | 164 |

| 15.3.Stop Mode                                                     | 164 |

| 15.4.Suspend Mode                                                  | 165 |

| 15.5.Sleep Mode                                                    | 165 |

| 15.6.Configuring Wakeup Sources                                    | 166 |

| 15.7.Determining the Event that Caused the Last Wakeup             |     |

| 15.8.Power Management Specifications                               |     |

| 16. Cyclic Redundancy Check Unit (CRC0)                            | 172 |

| 16.1.CRC Algorithm.                                                |     |

| 16.2. Preparing for a CRC Calculation                              | 174 |

| 16.3.Performing a CRC Calculation                                  |     |

| 16.4.Accessing the CRC0 Result                                     |     |

| 16.5.CRC0 Bit Reverse Feature                                      |     |

| 17. Voltage Regulator (VREG0)                                      | 180 |

| 17.1. Voltage Regulator Electrical Specifications                  | 180 |

| 18. Reset Sources.                                                 |     |

| 18.1.Power-On Reset                                                |     |

| 18.2.Power-Fail Reset                                              | 183 |

| 18.3.External Reset                                                | 184 |

| 18.4.Missing Clock Detector Reset                                  | 185 |

| 18.5.Comparator0 Reset                                             |     |

| 18.6.PCA Watchdog Timer Reset                                      |     |

| 18.7.Flash Error Reset                                             |     |

| 18.8.SmaRTClock (Real Time Clock) Reset                            |     |

| 18.9.Software Reset                                                |     |

| 19. Clocking Sources                                               |     |

| 19.1.Programmable Precision Internal Oscillator                    |     |

# C8051F99x-C8051F98x

| OF 0.4.40 hit Time an with Auto Dalaged                             | 004 |

|---------------------------------------------------------------------|-----|

| 25.3.1.16-bit Timer with Auto-Reload                                |     |

| 25.3.2.8-Bit Timers with Auto-Reload                                |     |

| 25.3.3.SmaRTClock/External Oscillator Capture Mode                  | 296 |

| 26. Programmable Counter Array                                      | 300 |

| 26.1.PCA Counter/Timer                                              | 301 |

| 26.2.PCA0 Interrupt Sources                                         | 302 |

| 26.3.Capture/Compare Modules                                        | 303 |

| 26.3.1.Edge-triggered Capture Mode                                  | 304 |

| 26.3.2.Software Timer (Compare) Mode                                |     |

| 26.3.3.High-Speed Output Mode                                       | 306 |

| 26.3.4. Frequency Output Mode                                       | 306 |

| 26.3.5. 8-bit, 9-bit, 10-bit and 11-bit Pulse Width Modulator Modes | 307 |

| 26.3.6. 16-Bit Pulse Width Modulator Mode                           | 310 |

| 26.4.Watchdog Timer Mode                                            | 311 |

| 26.4.1.Watchdog Timer Operation                                     |     |

| 26.4.2.Watchdog Timer Usage                                         | 312 |

| 26.5.Register Descriptions for PCA0                                 | 313 |

| 27.C2 Interface                                                     |     |

| 27.1.C2 Interface Registers                                         | 319 |

| 27.2.C2 Pin Sharing                                                 |     |

| Document Change List                                                |     |

| Contact Information                                                 | 325 |

# List of Registers

| SFR | Definition #            | 5.1. ADC0CN: ADC0 Control                                      | . 74 |

|-----|-------------------------|----------------------------------------------------------------|------|

| SFR | Definition #            | 5.2. ADC0CF: ADC0 Configuration                                | . 75 |

| SFR | Definition #            | 5.3. ADC0AC: ADC0 Accumulator Configuration                    | . 76 |

|     |                         | 5.4. ADC0PWR: ADC0 Burst Mode Power-Up Time                    |      |

| SFR | Definition #            | 5.5. ADC0TK: ADC0 Burst Mode Track Time                        | . 78 |

| SFR | Definition #            | 5.6. ADC0H: ADC0 Data Word High Byte                           | . 79 |

| SFR | Definition \$           | 5.7. ADC0L: ADC0 Data Word Low Byte                            | . 79 |

| SFR | Definition \$           | 5.8. ADC0GTH: ADC0 Greater-Than High Byte                      | . 80 |

| SFR | Definition \$           | 5.9. ADC0GTL: ADC0 Greater-Than Low Byte                       | . 80 |

|     |                         | 5.10. ADC0LTH: ADC0 Less-Than High Byte                        |      |

|     |                         | 5.11. ADC0LTL: ADC0 Less-Than Low Byte                         |      |

|     |                         | 5.12. ADC0MX: ADC0 Input Channel Select                        |      |

| SFR | Definition \$           | 5.13. TOFFH: ADC0 Data Word High Byte                          | . 87 |

|     |                         | 5.14. TOFFL: ADC0 Data Word Low Byte                           |      |

|     |                         | 5.15. REF0CN: Voltage Reference Control                        |      |

|     |                         | 6.1. IREF0CN: Current Reference Control                        |      |

|     |                         | 6.2. IREF0CF: Current Reference Configuration                  |      |

|     |                         | 7.1. CPT0CN: Comparator 0 Control                              |      |

| SFR | Definition              | 7.2. CPT0MD: Comparator 0 Mode Selection                       | . 97 |

| SFR | Definition              | 7.3. CPT0MX: Comparator0 Input Channel Select                  | . 99 |

| SFR | Definition 8            | 8.1. CS0CN: Capacitive Sense Control                           | 107  |

|     |                         | 8.2. CS0CF: Capacitive Sense Configuration                     |      |

|     |                         | 8.3. CS0DH: Capacitive Sense Data High Byte                    |      |

|     |                         | 8.4. CS0DL: Capacitive Sense Data Low Byte                     |      |

|     |                         | 8.5. CS0SCAN0: Capacitive Sense Channel Scan Mask 0            |      |

|     |                         | 8.6. CS0SCAN1: Capacitive Sense Channel Scan Mask 1            |      |

|     |                         | 8.7. CS0SS: Capacitive Sense Auto-Scan Start Channel           |      |

|     |                         | 8.8. CS0SE: Capacitive Sense Auto-Scan End Channel             |      |

|     |                         | 8.9. CS0THH: Capacitive Sense Comparator Threshold High Byte   |      |

|     |                         | 8.10. CS0THL: Capacitive Sense Comparator Threshold Low Byte . |      |

|     |                         | 8.11. CS0MD1: Capacitive Sense Mode 1                          |      |

|     |                         | 8.12. CS0MD2: Capacitive Sense Mode 2                          |      |

|     |                         | 8.13. CS0MD3: Capacitive Sense Mode 3                          |      |

|     |                         | 8.14. CS0PM: Capacitive Sense Pin Monitor                      |      |

|     |                         | 8.15. CS0MX: Capacitive Sense Mux Channel Select               |      |

|     |                         | 9.1. DPL: Data Pointer Low Byte                                |      |

|     |                         | 9.2. DPH: Data Pointer High Byte                               |      |

|     |                         | 9.3. SP: Stack Pointer                                         |      |

|     |                         | 9.4. ACC: Accumulator                                          |      |

|     |                         | 9.5. B: B Register                                             |      |

|     |                         | 9.6. PSW: Program Status Word                                  |      |

|     |                         | 12.1. SFR Page: SFR Page                                       |      |

| SFR | Definition <sup>2</sup> | 13.1. IE: Interrupt Enable                                     | 142  |

# C8051F99x-C8051F98x

# C8051F99x-C8051F98x

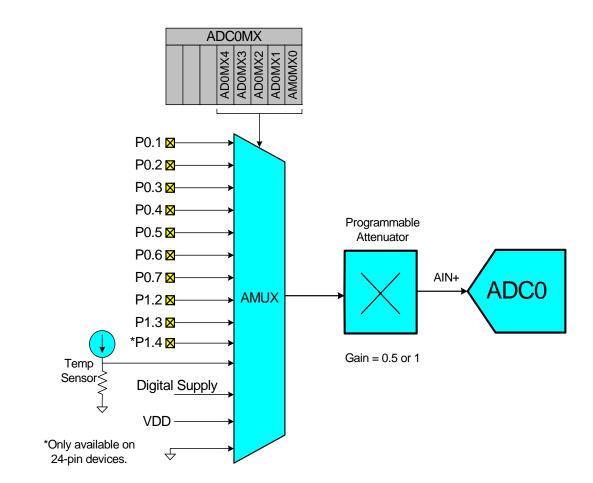

Figure 1.17. ADC0 Multiplexer Block Diagram

## 1.6. Programmable Current Reference (IREF0)

C8051F99x-C8051F98x devices include an on-chip programmable current reference (source or sink) with two output current settings: low power mode and high current mode. The maximum current output in low power mode is 63  $\mu$ A (1  $\mu$ A steps) and the maximum current output in high current mode is 504  $\mu$ A (8  $\mu$ A steps).

### 1.7. Comparator

C8051F99x-C8051F98x devices include an on-chip programmable voltage comparator: Comparator 0 (CPT0) which is shown in Figure 1.18.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0), or an asynchronous "raw" output (CP0A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output when the device is in some low power modes.

The comparator inputs may be connected to Port I/O pins or to other internal signals. Port pins may also be used to directly sense capacitive touch switches.

| Pin Numbers    |                                        | S                                      |                                      |                  |                                                                                                                                                    |  |  |

|----------------|----------------------------------------|----------------------------------------|--------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name           | 'F980/1/2<br>'F983/5<br>'F990/1<br>-GM | <pre>'F986/7 'F988/9 'F996/7 -GM</pre> | 'F986/7<br>'F988/9<br>'F996/7<br>-GU | Туре             | Description                                                                                                                                        |  |  |

| P0.1/          | 1                                      | 23                                     | 2                                    | D I/O or<br>A In | Port 0.1. See Port I/O Section for a complete description.                                                                                         |  |  |

| AGND*          |                                        |                                        |                                      | G                | Optional Analog Ground. See Section "5.9. Voltage and Ground Reference Options" on page 88.                                                        |  |  |

| P0.2/          | 20                                     | 22                                     | 1                                    | D I/O or<br>A In | Port 0.2. See Port I/O Section for a complete description.                                                                                         |  |  |

| XTAL1/         |                                        |                                        |                                      | A In             | External Clock Input. This pin is the external oscillator<br>return for a crystal or resonator. See Section<br>"19. Clocking Sources" on page 188. |  |  |

| RTCOUT         |                                        |                                        |                                      | D Out            | Buffered SmaRTClock oscillator output.                                                                                                             |  |  |

| P0.3/          | 19                                     | 21                                     | 24                                   | D I/O or<br>A In | Port 0.3. See Section "21. Port Input/Output" on page 215 for a complete description.                                                              |  |  |

| XTAL2/         |                                        |                                        |                                      | A Out            | External Clock Output. This pin is the excitation driver for an external crystal or resonator.                                                     |  |  |

|                |                                        |                                        |                                      | D In             | External Clock Input. This pin is the external clock input in external CMOS clock mode.                                                            |  |  |

|                |                                        |                                        |                                      | A In             | External Clock Input. This pin is the external clock input in capacitor or RC oscillator configurations.                                           |  |  |

|                |                                        |                                        |                                      |                  | See Section "19. Clocking Sources" on page 188 for<br>complete details.                                                                            |  |  |

| WAKEOUT        |                                        |                                        |                                      | D Out            | Wake-up request signal to wake up external devices.                                                                                                |  |  |

| P0.4/          | 18                                     | 20                                     | 23                                   | D I/O or<br>A In | Port 0.4. See Section "21. Port Input/Output" on page 215 for a complete description.                                                              |  |  |

| ТΧ             |                                        |                                        |                                      | D Out            | UART TX Pin. See Section "21. Port Input/Output" on page 215.                                                                                      |  |  |

| P0.5/          | 17                                     | 19                                     | 22                                   | D I/O or<br>A In | Port 0.5. See Section "21. Port Input/Output" on page 215 for a complete description.                                                              |  |  |

| RX             |                                        |                                        |                                      | D In             | UART RX Pin. See Section "21. Port Input/Output" on page 215.                                                                                      |  |  |

| *Note: Availal | ble only on t                          | he C805 <sup>-</sup>                   | 1F980/2/6                            | 6/8 and C80      | 051F990/6 devices.                                                                                                                                 |  |  |

## Table 3.1. Pin Definitions for the C8051F99x-C8051F98x (Continued)

\*Note: Signal only available on 'F986, 'F988, and 'F996 devices.

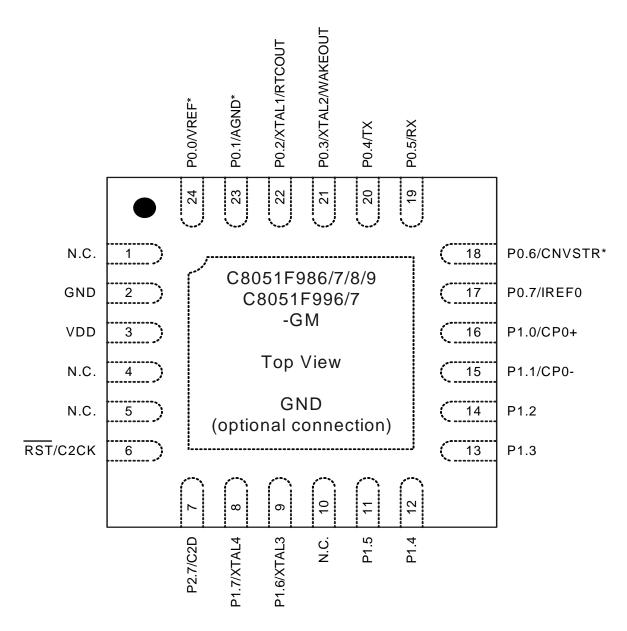

Figure 3.2. QFN-24 Pinout Diagram (Top View)

# 4. Electrical Characteristics

Throughout the Electrical Characteristics chapter, "VDD" refers to the Supply Voltage.

## 4.1. Absolute Maximum Specifications

#### Table 4.1. Absolute Maximum Ratings

| Conditions | Min        | Тур             | Max                                                    | Units                                                  |

|------------|------------|-----------------|--------------------------------------------------------|--------------------------------------------------------|

|            | -55        | _               | 125                                                    | °C                                                     |

|            | -65        |                 | 150                                                    | °C                                                     |

|            | -0.3       |                 | V <sub>DD</sub> + 0.3                                  | V                                                      |

|            | -0.3       | _               | 4.0                                                    | V                                                      |

|            | —          | _               | 500                                                    | mA                                                     |

|            | _          | _               | 100                                                    | mA                                                     |

|            | _          |                 | 200                                                    | mA                                                     |

|            | Conditions | 55<br>65<br>0.3 | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

te: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 5.8.1. Calibration

The uncalibrated temperature sensor output is extremely linear and suitable for relative temperature measurements (see Table 4.11 for linearity specifications). For absolute temperature measurements, offset and/or gain calibration is recommended. Typically a 1-point (offset) calibration includes the following steps:

- 1. Control/measure the ambient temperature (this temperature must be known).

- 2. Power the device, and delay for a few seconds to allow for self-heating.

- 3. Perform an ADC conversion with the temperature sensor selected as the positive input and GND selected as the negative input.

- 4. Calculate the offset characteristics, and store this value in non-volatile memory for use with subsequent temperature sensor measurements.

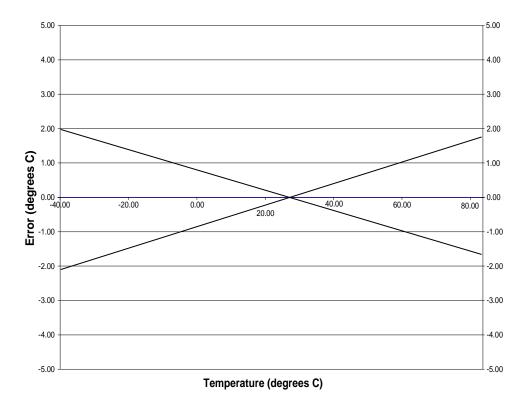

Figure 5.9 shows the typical temperature sensor error assuming a 1-point calibration at 25 °C. **Parameters that affect ADC measurement, in particular the voltage reference value, will also affect temperature measurement.**

A single-point offset measurement of the temperature sensor is performed on each device during production test. The measurement is performed at 25 °C  $\pm$ 5 °C, using the ADC with the internal high speed reference buffer selected as the Voltage Reference. The direct ADC result of the measurement is stored in the SFR registers TOFFH and TOFFL, shown in SFR Definition 5.13 and SFR Definition 5.14.

Figure 5.9. Temperature Sensor Error with 1-Point Calibration (V<sub>REF</sub> = 1.65 V)

# 6. Programmable Current Reference (IREF0)

C8051F99x-C8051F98x devices include an on-chip programmable current reference (source or sink) with two output current settings: Low Power Mode and High Current Mode. The maximum current output in Low Power Mode is 63  $\mu$ A (1  $\mu$ A steps) and the maximum current output in High Current Mode is 504  $\mu$ A (8  $\mu$ A steps).

The current source/sink is controlled though the IREF0CN special function register. It is enabled by setting the desired output current to a non-zero value. It is disabled by writing 0x00 to IREF0CN. The port I/O pin associated with ISRC0 should be configured as an analog input and skipped in the Crossbar. See Section "21. Port Input/Output" on page 215 for more details.

## SFR Definition 6.1. IREF0CN: Current Reference Control

| Bit   | 7    | 6    | 5   | 4 | 3    | 2    | 1 | 0 |

|-------|------|------|-----|---|------|------|---|---|

| Name  | SINK | MODE |     |   | IREF | 0DAT |   |   |

| Туре  | R/W  | R/W  | R/W |   |      |      |   |   |

| Reset | 0    | 0    | 0   | 0 | 0    | 0    | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xD6

| Bit | Name          | Function                                                                                                                            |

|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SINK          | IREF0 Current Sink Enable.                                                                                                          |

|     |               | Selects if IREF0 is a current source or a current sink.                                                                             |

|     |               | 0: IREF0 is a current source.                                                                                                       |

|     |               | 1: IREF0 is a current sink.                                                                                                         |

| 6   | MDSEL         | IREF0 Output Mode Select.                                                                                                           |

|     |               | Selects Low Power or High Current Mode.                                                                                             |

|     |               | 0: Low Power Mode is selected (step size = 1 $\mu$ A).                                                                              |

|     |               | 1: High Current Mode is selected (step size = $8 \mu A$ ).                                                                          |

| 5:0 | IREF0DAT[5:0] | IREF0 Data Word.                                                                                                                    |

|     |               | Specifies the number of steps required to achieve the desired output current.<br>Output current = direction x step size x IREF0DAT. |

|     |               | IREF0 is in a low power state when IREF0DAT is set to 0x00.                                                                         |

### 6.1. PWM Enhanced Mode

The precision of the current reference can be increased by fine tuning the IREF0 output using a PWM signal generated by the PCA. This mode allows the IREF0DAT bits to perform a course adjustment on the IREF0 output. Any available PCA channel can perform a fine adjustment on the IREF0 output. When enabled (PWMEN = 1), the CEX signal selected using the PWMSS bit field is internally routed to IREF0 to control the on time of a current source having the weight of 2 LSBs. With the two least significant bits of IREF0DAT set to 00b, applying a 100% duty cycle on the CEX signal will be equivalent to setting the two LSBs of IREF0DAT to 10b. PWM enhanced mode is enabled and setup using the IREF0CF register.

#### Notes on Registers, Operands and Addressing Modes:

**Rn**—Register R0–R7 of the currently selected register bank.

@Ri—Data RAM location addressed indirectly through R0 or R1.

**rel**—8-bit, signed (twos complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct**—8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data—8-bit constant

#data16—16-bit constant

**bit**—Direct-accessed bit in Data RAM or SFR

**addr11**—11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16**—16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

# 13. Interrupt Handler

The C8051F99x-C8051F98x microcontroller family includes an extended interrupt system supporting multiple interrupt sources and two priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Refer to Table 13.1, "Interrupt Summary," on page 140 for a detailed listing of all interrupt sources supported by the device. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR or an indirect register. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1. If both global interrupts and the specific interrupt source is enabled, a CPU interrupt request is generated when the interrupt-pending flag is set.

As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Some interrupt-pending flags are automatically cleared by hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

## 13.1. Enabling Interrupt Sources

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in the Interrupt Enable and Extended Interrupt Enable SFRs. However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings. Note that interrupts which occur when the EA bit is set to logic 0 will be held in a pending state, and will not be serviced until the EA bit is set back to logic 1.

### 13.2. MCU Interrupt Sources and Vectors

The CPU services interrupts by generating an LCALL to a predetermined address (the interrupt vector address) to begin execution of an interrupt service routine (ISR). The interrupt vector addresses associated with each interrupt source are listed in Table 13.1 on page 140. Software should ensure that the interrupt vector for each enabled interrupt source contains a valid interrupt service routine.

Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag.

### 14.5. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

To help prevent the accidental modification of Flash by firmware, the  $V_{DD}$  Monitor must be enabled and enabled as a reset source on C8051F99x-C8051F98x devices for the Flash to be successfully modified. If either the  $V_{DD}$  Monitor or the  $V_{DD}$  Monitor reset source is not enabled, a Flash Error Device Reset will be generated when the firmware attempts to modify the Flash.

The following guidelines are recommended for any system that contains routines which write or erase Flash from code.

#### 14.5.1. $V_{DD}$ Maintenance and the $V_{DD}$ Monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. Make certain that the minimum  $V_{DD}$  rise time specification of 1 ms is met. If the system cannot meet this rise time specification, then add an external  $V_{DD}$  brownout circuit to the RST pin of the device that holds the device in reset until  $V_{DD}$  reaches the minimum device operating voltage and re-asserts RST if  $V_{DD}$  drops below the minimum device operating voltage.

- 3. Keep the on-chip V<sub>DD</sub> Monitor enabled and enable the V<sub>DD</sub> Monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> Monitor and enabling the V<sub>DD</sub> Monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories website.

#### Notes:

- On C8051F99x-C8051F98x devices, both the V<sub>DD</sub> Monitor and the V<sub>DD</sub> Monitor reset source must be enabled to write or erase Flash without generating a Flash Error Device Reset.

- 2. On C8051F99x-C8051F98x devices, both the  $V_{DD}$  Monitor and the  $V_{DD}$  Monitor reset source are enabled by hardware after a power-on reset.

- 4. As an added precaution, explicitly enable the V<sub>DD</sub> Monitor and enable the V<sub>DD</sub> Monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> Monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct, but "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

# SFR Definition 16.1. CRC0CN: CRC0 Control

| Bit   | 7 | 6 | 5 | 4 | 3        | 2       | 1 | 0       |

|-------|---|---|---|---|----------|---------|---|---------|

| Name  |   |   |   |   | CRC0INIT | CRC0VAL |   | CRC0PNT |

| Туре  | R | R | R | R | R/W      | R/W     | R | R/W     |

| Reset | 0 | 0 | 0 | 1 | 0        | 0       | 0 | 0       |

#### SFR Page = All; SFR Address = 0x84

| Bit   | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Function                                                                      |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| 7:4   | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Read = 0001b; Write = Don't Care.                                             |  |  |  |  |

| 3     | CRC0INIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CRC0 Result Initialization Bit.                                               |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Writing a 1 to this bit initializes the entire CRC result based on CRC0VAL.   |  |  |  |  |

| 2     | CRC0VAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CRC0 Set Value Initialization Bit.                                            |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This bit selects the set value of the CRC result.                             |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0: CRC result is set to 0x00000000 on write of 1 to CRC0INIT.                 |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1: CRC result is set to 0xFFFFFFF on write of 1 to CRC0INIT.                  |  |  |  |  |

| 1     | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Read = 0b; Write = Don't Care.                                                |  |  |  |  |

| 0     | CRC0PNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CRC0 Result Pointer.                                                          |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Specifies the byte of the CRC result to be read/written on the next access to |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CRC0DAT. The value of these bits will auto-increment upon each read or write. |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0: CRC0DAT accesses bits 7–0 of the 16-bit CRC result.                        |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1: CRC0DAT accesses bits 15–8 of the 16-bit CRC result.                       |  |  |  |  |

| Note: | <ul> <li>te: Upon initiation of an automatic CRC calculation, the three cycles following a write to CRC0CN that initiate a CRC operation must only contain instructions which execute in the same number of cycles as the number of bytes in the instruction. An example of such an instruction is a 3-byte MOV that targets the CRC0FLIP register. When programming in C, the dummy value written to CRC0FLIP should be a non-zero value to prevent the compiler from generating a 2-byte MOV instruction.</li> </ul> |                                                                               |  |  |  |  |

# 17. Voltage Regulator (VREG0)

C8051F99x-C8051F98x devices include an internal voltage regulator (VREG0) to regulate the internal core supply to 1.8 V from a VDD supply of 1.8 to 3.6 V. Electrical characteristics for the on-chip regulator are specified in the Electrical Specifications chapter.

The REGOCN register allows the Precision Oscillator Bias to be disabled, reducing supply current in all non-Sleep power modes. This bias should only be disabled when the precision oscillator is not being used.

The internal regulator (VREG0) is disabled when the device enters Sleep Mode and remains enabled when the device enters Suspend Mode. See Section "15. Power Management" on page 162 for complete details about low power modes.

### SFR Definition 17.1. REG0CN: Voltage Regulator Control

| Bit   | 7 | 6        | 5        | 4       | 3 | 2 | 1 | 0        |

|-------|---|----------|----------|---------|---|---|---|----------|

| Name  |   | Reserved | Reserved | OSCBIAS |   |   |   | Reserved |

| Туре  | R | R/W      | R/W      | R/W     | R | R | R | R/W      |

| Reset | 0 | 0        | 0        | 0       | 0 | 0 | 0 | 0        |

#### SFR Page = 0x0; SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused   | Read = 0b. Write = Don't care.                                                                                                                                                                            |

| 6:5 | Reserved | Read = 00b. Must Write 00b.                                                                                                                                                                               |

| 4   | OSCBIAS  | Precision Oscillator Bias.                                                                                                                                                                                |

|     |          | When set to 1, the bias used by the precision oscillator is forced on. If the precision oscillator is not being used, this bit may be cleared to 0 to reduce supply current in all non-Sleep power modes. |

| 3:1 | Unused   | Read = 000b. Write = Don't care.                                                                                                                                                                          |

| 0   | Reserved | Read = 0b. Must Write 0b.                                                                                                                                                                                 |

### 17.1. Voltage Regulator Electrical Specifications

See Table 4.15 on page 64 for detailed Voltage Regulator Electrical Specifications.

## 18.8. SmaRTClock (Real Time Clock) Reset

The SmaRTClock can generate a system reset on two events: SmaRTClock Oscillator Fail or SmaRTClock Alarm. The SmaRTClock Oscillator Fail event occurs when the SmaRTClock Missing Clock Detector is enabled and the SmaRTClock clock is below approximately 20 kHz. A SmaRTClock alarm event occurs when the SmaRTClock Alarm is enabled and the SmaRTClock timer value matches the ALARMn registers. The SmaRTClock can be configured as a reset source by writing a 1 to the RTCORE flag (RSTSRC.7). The SmaRTClock reset remains functional even when the device is in the low power Suspend or Sleep mode. The state of the RST pin is unaffected by this reset.

#### 18.9. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

#### 20.2.5. Automatic Gain Control (Crystal Mode Only) and SmaRTClock Bias Doubling

Automatic Gain Control allows the SmaRTClock oscillator to trim the oscillation amplitude of a crystal in order to achieve the lowest possible power consumption. Automatic Gain Control automatically detects when the oscillation amplitude has reached a point where it safe to reduce the drive current, therefore, it may be enabled during crystal startup. It is recommended to enable Automatic Gain Control in most systems which use the SmaRTClock oscillator in Crystal Mode. The following are recommended crystal specifications and operating conditions when Automatic Gain Control is enabled:

- ESR < 50 kΩ</p>

- Load Capacitance < 10 pF</p>

- Supply Voltage < 3.0 V</li>

- Temperature > -20 °C

When using Automatic Gain Control, it is recommended to perform an oscillation robustness test to ensure that the chosen crystal will oscillate under the worst case condition to which the system will be exposed. The worst case condition that should result in the least robust oscillation is at the following system conditions: lowest temperature, highest supply voltage, highest ESR, highest load capacitance, and lowest bias current (AGC enabled, Bias Double Disabled).

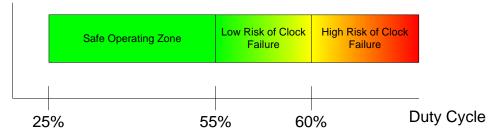

To perform the oscillation robustness test, the SmaRTClock oscillator should be enabled and selected as the system clock source. Next, the SYSCLK signal should be routed to a port pin configured as a push-pull digital output. The positive duty cycle of the output clock can be used as an indicator of oscillation robustness. As shown in Figure 20.2, duty cycles less than 55% indicate a robust oscillation. As the duty cycle approaches 60%, oscillation becomes less reliable and the risk of clock failure increases. Increasing the bias current (by disabling AGC) will always improve oscillation robustness and will reduce the output clock's duty cycle. This test should be performed at the worst case system conditions, as results at very low temperatures or high supply voltage will vary from results taken at room temperature or low supply voltage.

As an alternative to performing the oscillation robustness test, Automatic Gain Control may be disabled at the cost of increased power consumption (approximately 200 nA). Disabling Automatic Gain Control will provide the crystal oscillator with higher immunity against external factors which may lead to clock failure. Automatic Gain Control must be disabled if using the SmaRTClock oscillator in self-oscillate mode.

Table 20.3 shows a summary of the oscillator bias settings. The SmaRTClock Bias Doubling feature allows the self-oscillation frequency to be increased (almost doubled) and allows a higher crystal drive strength in crystal mode. High crystal drive strength is recommended when the crystal is exposed to poor environmental conditions such as excessive moisture. SmaRTClock Bias Doubling is enabled by setting BIASX2 (RTC0XCN.5) to 1.

#### 20.3.3. Software Considerations for using the SmaRTClock Timer and Alarm

The SmaRTClock timer and alarm have two operating modes to suit varying applications. The two modes are described below:

#### Mode 1:

The first mode uses the SmaRTClock timer as a perpetual timebase which is never reset to zero. Every 36 hours, the timer is allowed to overflow without being stopped or disrupted. The alarm interval is software managed and is added to the ALRMn registers by software after each alarm. This allows the alarm match value to always stay ahead of the timer by one software managed interval. If software uses 32-bit unsigned addition to increment the alarm match value, then it does not need to handle overflows since both the timer and the alarm match value will overflow in the same manner.

This mode is ideal for applications which have a long alarm interval (e.g., 24 or 36 hours) and/or have a need for a perpetual timebase. An example of an application that needs a perpetual timebase is one whose wake-up interval is constantly changing. For these applications, software can keep track of the number of timer overflows in a 16-bit variable, extending the 32-bit (36 hour) timer to a 48-bit (272 year) perpetual timebase.

#### Mode 2:

The second mode uses the SmaRTClock timer as a general purpose up counter which is auto reset to zero by hardware after each alarm. The alarm interval is managed by hardware and stored in the ALRMn registers. Software only needs to set the alarm interval once during device initialization. After each alarm, software should keep a count of the number of alarms that have occurred in order to keep track of time.

This mode is ideal for applications that require minimal software intervention and/or have a fixed alarm interval. This mode is the most power efficient since it requires less CPU time per alarm.

# SFR Definition 21.8. P0: Port0

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P0[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = All; SFR Address = 0x80; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW. |

## SFR Definition 21.9. P0SKIP: Port0 Skip

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P0SKIP[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Page= 0x0; SFR Address = 0xD4

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0SKIP[7:0] | Port 0 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 0 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P0.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P0.n pin is skipped by the Crossbar.</li> </ul> |

#### 22.4.4. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

#### SFR Definition 22.5. SMB0DAT: SMBus Data

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | SMB0DAT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xC2

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SMB0DAT[7:0] | SMBus Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | The SMB0DAT register contains a byte of data to be transmitted on the SMBus serial interface or a byte that has just been received on the SMBus serial interface. The CPU can read from or write to this register whenever the SI serial interrupt flag (SMB0CN.0) is set to logic 1. The serial data in the register remains stable as long as the SI flag is set. When the SI flag is not set, the system may be in the process of shifting data in/out and the CPU should not attempt to access this register. |