Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                       |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, POR, PWM, WDT                  |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-UFQFN Exposed Pad                                              |

| Supplier Device Package    | 20-QFN (3x3)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f991-c-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 22.1. SMBus Clock Source Selection       24         Table 22.4. SMBus Clock Source Selection       24 |    |

|-------------------------------------------------------------------------------------------------------------|----|

| Table 22.2. Minimum SDA Setup and Hold Times       24                                                       |    |

| Table 22.3. Sources for Hardware Changes to SMB0CN                                                          | 45 |

| Table 22.4. Hardware Address Recognition Examples (EHACK = 1)                                               | 46 |

| Table 22.5. SMBus Status Decoding With Hardware ACK Generation Disabled                                     |    |

| (EHACK = 0)                                                                                                 | 53 |

| Table 22.6. SMBus Status Decoding With Hardware ACK Generation Enabled                                      |    |

| (EHACK = 1)                                                                                                 | 55 |

| Table 23.1. Timer Settings for Standard Baud Rates                                                          |    |

| Using The Internal 24.5 MHz Oscillator                                                                      | 64 |

| Table 23.2. Timer Settings for Standard Baud Rates                                                          |    |

| Using an External 22.1184 MHz Oscillator                                                                    | 64 |

| Table 24.1. SPI Slave Timing Parameters                                                                     | 77 |

| Table 25.1. Timer 0 Running Modes       28                                                                  | 80 |

| Table 26.1. PCA Timebase Input Options                                                                      | 01 |

| Table 26.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare                                        |    |

| Modules                                                                                                     | 03 |

| Table 26.3. Watchdog Timer Timeout Intervals1                                                               | 12 |

# 1. System Overview

C8051F99x-C8051F98x devices are fully integrated mixed-signal system-on-a-chip MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- Ultra low power consumption in active and sleep modes.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- 10-bit 300 ksps or 12-bit 75 ksps single-ended ADC with analog multiplexer

- 6-bit programmable current reference (resolution can be increased with PWM)

- Precision programmable 24.5 MHz internal oscillator with spread spectrum technology.

- 8 kB, 4 kB, or 2 kB of on-chip Flash memory

- 512 bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable counter/timer array (PCA) with three capture/compare modules and watchdog timer function

- On-chip power-on reset, V<sub>DD</sub> monitor, and temperature sensor

- One on-chip voltage comparator

- Up to 14 Capacitive Touch Inputs

- Up to 17 Port I/O

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051F99x-C8051F98x devices are truly stand-alone system-on-a-chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

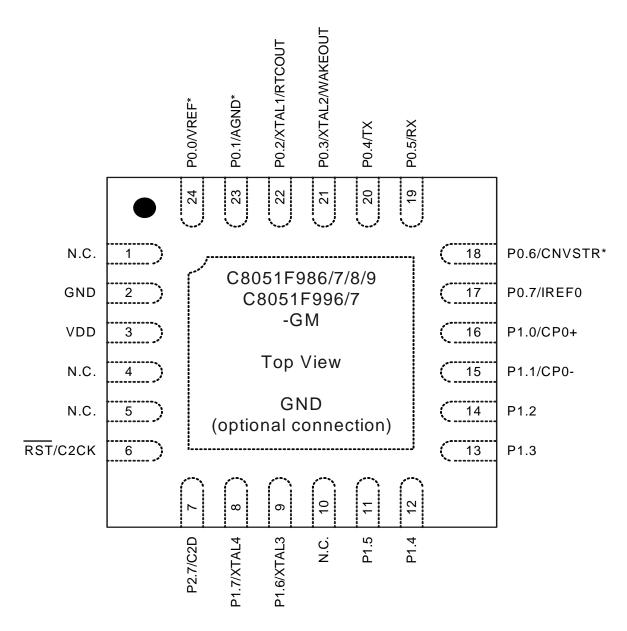

Each device is specified for 1.8 to 3.6 V operation over the industrial temperature range (-40 to +85 °C). The Port I/O and RST pins are powered from the supply voltage. The C8051F99x-C8051F98x devices are available in 20-pin or 24-pin QFN or 24-pin QSOP packages. All package options are lead-free and RoHS compliant. See Table 2.1 for ordering information. Block diagrams are included in Figure 1.1 through Figure 1.9.

\*Note: Signal only available on 'F986, 'F988, and 'F996 devices.

Figure 3.2. QFN-24 Pinout Diagram (Top View)

## Table 4.13. IREF0 Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C, unless otherwise specified.

| Static PerformanceResolution6bitsOutput Compliance RangeLow Power Mode, Source<br>High Current Mode, Source<br>Low Power Mode, Sink0 $V_{DD} - 0.4$<br>$V_{DD} - 0.8$<br>$V_{DD} - 0.8$ Integral Nonlinearity<±0.2±1.0LSBDifferential Nonlinearity<±0.2±1.0LSBOffset Error±5%High Current Mode, Source±6%Integral Nonlinearity<±0.1±0.5LSBDifferential Nonlinearity<±0.1±0.5LSBFull Scale ErrorLow Power Mode, Source±6High Current Mode, Source±8%How Power Mode, Sink±8%Absolute Current ErrorLow Power Mode, Sink±8Output Settling Time to 1/2 LSB300nsStartup Time1 $\mu A$ Net Power Supply Current<br>(Vop Supplied to IREFO minus<br>any output source current)IREFODAT = 00000110IREFODAT = 100100110 $\mu A$ IREFODAT = 111111 $\mu A$ IREFODAT = 00000111 $\mu A$ IREFODAT = 00000110IREFODAT = 00000110 $\mu A$ IREFODAT = 00000110 $\mu A$ IREFODAT = 0000011 $\mu A$ <th>Parameter</th> <th>Conditions</th> <th>Min</th> <th>Тур</th> <th>Max</th> <th>Units</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Parameter                                | Conditions                                        | Min      | Тур   | Max                                      | Units |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------|----------|-------|------------------------------------------|-------|

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Static Performance                       |                                                   |          |       |                                          |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Resolution                               |                                                   |          | 6     |                                          | bits  |

| $\begin{array}{ c c c c c } \hline Differential Nonlinearity & < < \pm 0.2 & \pm 1.0 & LSB \\ \hline Offset Error & - & < \pm 0.1 & \pm 0.5 & LSB \\ \hline Low Power Mode, Source & & & \pm 5 & \% \\ \hline High Current Mode, Source & & & \pm 6 & \% \\ \hline Low Power Mode, Sink & & & \pm 8 & \% \\ \hline Low Power Mode, Sink & & & \pm 8 & \% \\ \hline Low Power Mode, Sink & & & \pm 8 & \% \\ \hline High Current Mode, Sink & & & \pm 8 & \% \\ \hline Absolute Current Error & Low Power Mode & & < \pm 1 & \pm 3 & \% \\ \hline Dynamic Performance & & & & & & & \\ \hline Output Settling Time to 1/2 LSB & & 300 & & ns \\ \hline Startup Time & & 1 & & \mus \\ \hline Power Consumption & & & & & \\ Net Power Supply Current & & & & & \\ (Vop Supplied to IREF0 minus any output source current) & Low Power Mode, Source & & & & \\ IREF0DAT = 000001 & & 10 & & \muA \\ IREF0DAT = 000001 & & 10 & & \muA \\ IREF0DAT = 111111 & & 10 & & \muA \\ IREF0DAT = 111111 & & 10 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 1000001 & & 1 & & \muA \\ IREF0DAT = 1000001 & & 1 & & \muA \\ IREF0DAT = 000001 & & 1 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 12 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & & & & $                                                                                                                                                                                                                                                                                                                                                                                                                                    | Output Compliance Range                  | High Current Mode, Source<br>Low Power Mode, Sink | 0<br>0.3 |       | V <sub>DD</sub> – 0.8<br>V <sub>DD</sub> | V     |

| $\begin{array}{ c c c c c } \hline \label{eq:constraint} Offset Error & & - & - & \pm 0.1 & \pm 0.5 & LSB \\ \hline \mbox{Low Power Mode, Source} & & - & \pm 5 & \% \\ \hline \mbox{High Current Mode, Source} & & - & \pm 6 & \% \\ \hline \mbox{Low Power Mode, Sink} & & - & \pm 8 & \% \\ \hline \mbox{High Current Mode, Sink} & & - & \pm 8 & \% \\ \hline \mbox{High Current Mode, Sink} & & - & \pm 8 & \% \\ \hline \mbox{Absolute Current Error} & Low Power Mode & & <\pm 1 & \pm 3 & \% \\ \hline \mbox{Dynamic Performance} & & 1 & & \pm 8 & \% \\ \hline \mbox{Dynamic Performance} & & - & \pm 8 & \% \\ \hline \mbox{Dynamic Performance} & & - & \pm 8 & \% \\ \hline \mbox{Dynamic Performance} & & & \pm 8 & \% \\ \hline \mbox{Output Settling Time to 1/2 LSB} & & 300 & & ns \\ \hline \mbox{Startup Time} & & 1 & & \mu s \\ \hline \mbox{Power Consumption} \\ \hline \mbox{Net Power Supply Current} & Low Power Mode, Source \\ \mbox{IREF0DAT = 000001} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 11 & & \mu A \\ \hline \mbox{IREF0DAT = 1000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 12 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline IREF0DAT =$                                                                     | Integral Nonlinearity                    |                                                   | _        | <±0.2 | ±1.0                                     | LSB   |

| $\begin{tabular}{ c c c c c c c } \hline Low Power Mode, Source & - & - & \pm 5 & \% \\ \hline High Current Mode, Source & - & - & \pm 6 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline Absolute Current Error & Low Power Mode & - & <\pm 1 & \pm 3 & \% \\ \hline Dynamic Performance & & & & & & & \\ \hline Output Settling Time to 1/2 LSB & - & 300 & - & ns \\ \hline Startup Time & - & 1 & - & \mus \\ \hline Power Consumption & & & & & & & \\ Net Power Supply Current (V_{DD} supplied to IREF0 minus any output source current) & Low Power Mode, Source IREF0DAT = 000001 & - & 10 & - & \muA \\ IREF0DAT = 111111 & - & 10 & - & \muA \\ IREF0DAT = 111111 & - & 10 & - & \muA \\ IREF0DAT = 111111 & - & 10 & - & \muA \\ IREF0DAT = 1000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 111111 & - & 11 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 111111 & - & 11 & - & \muA \\ IREF0DAT = 000001 & - & 12 & - & \muA \\ IREF0DAT = 000001 & - & 12 & - & \muA \\ IREF0DAT = 000001 & - & 12 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & & \muA \\ IREF0DAT = 1111111 & - & 81 & - $ | Differential Nonlinearity                |                                                   | —        | <±0.2 | ±1.0                                     | LSB   |

| Full Scale Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Offset Error                             |                                                   | _        | <±0.1 | ±0.5                                     | LSB   |

| Full Scale ErrorImage: Sink intermediate inter                                                                                                                                                                                                                                                          |                                          | Low Power Mode, Source                            |          | —     | ±5                                       | %     |

| $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Full Scole Error                         | High Current Mode, Source                         |          | —     | ±6                                       | %     |

| Absolute Current ErrorLow Power Mode<br>Sourcing 20 $\mu$ A-<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          | Low Power Mode, Sink                              | —        | —     | ±8                                       | %     |

| Absolute Current ErrorSourcing 20 $\mu$ AImage: Constraint of the second se                                                                                                                                                                                                                                        |                                          | High Current Mode, Sink                           |          | —     | ±8                                       | %     |

| Output Settling Time to 1/2 LSB         —         300         —         ns           Startup Time         —         1         —         µs           Power Consumption         —         1         —         µs           Net Power Supply Current<br>(V <sub>DD</sub> supplied to IREF0 minus<br>any output source current)         Low Power Mode, Source<br>IREF0DAT = 000001         —         10         —         µA           High Current Mode, Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Absolute Current Error                   |                                                   | _        | <±1   | ±3                                       | %     |

| Startup Time         —         1         —         μs           Power Consumption         Net Power Supply Current (V <sub>DD</sub> supplied to IREF0 minus any output source current)         Low Power Mode, Source         10         —         μA           IREF0DAT = 000001         —         10         —         μA           IREF0DAT = 111111         —         10         —         μA           IREF0DAT = 000001         —         10         —         μA           IREF0DAT = 000001         —         10         —         μA           IREF0DAT = 111111         —         10         —         μA           IREF0DAT = 000001         —         1         —         μA           IREF0DAT = 111111         —         11         —         μA           IREF0DAT = 000001         —         12         —         μA           IREF0DAT = 111111         —         81         —         μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Dynamic Performance                      |                                                   |          |       |                                          |       |

| Power ConsumptionNet Power Supply Current<br>(V <sub>DD</sub> supplied to IREF0 minus<br>any output source current)Low Power Mode, Source<br>IREF0DAT = 00000110µAIREF0DAT = 11111110µAHigh Current Mode, Source<br>IREF0DAT = 00000110µAIREF0DAT = 00000110µAIREF0DAT = 00000110µAIREF0DAT = 00000110µAIREF0DAT = 11111110µAIREF0DAT = 0000011µAIREF0DAT = 11111111µAIREF0DAT = 00000112µAIREF0DAT = 00000112µAIREF0DAT = 11111181µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output Settling Time to 1/2 LSB          |                                                   | —        | 300   | —                                        | ns    |

| Net Power Supply Current<br>(V <sub>DD</sub> supplied to IREF0 minus<br>any output source current)Low Power Mode, Source<br>IREF0DAT = 00000110 $ \mu A$ IREF0DAT = 111111-10- $\mu A$ High Current Mode, Source<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Startup Time                             |                                                   | —        | 1     | —                                        | μs    |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Power Consumption                        |                                                   |          |       |                                          |       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (V <sub>DD</sub> supplied to IREF0 minus | IREF0DAT = 000001<br>IREF0DAT = 111111            | —        |       |                                          | •     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                          | IREF0DAT = 000001<br>IREF0DAT = 111111            | —        |       | _                                        |       |

| IREF0DAT = 111111 — 81 — µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          | IREF0DAT = 111111<br>High Current Mode, Sink      | _        | 11    | _                                        | μA    |

| Note: Refer to "PWM Enhanced Mode" on page 91 for information on how to improve IREF0 resolution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Note: Refer to "PW/M Enhanced My         | IREF0DAT = 111111                                 |          | 81    | resolution                               |       |

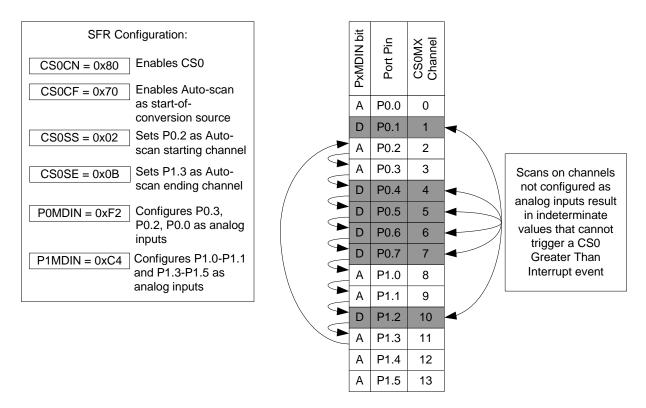

# 8.8. Automatic Scanning (Method 1—CS0SMEN = 0)

CS0 can be configured to automatically scan a sequence of contiguous CS0 input channels by configuring and enabling auto-scan. Using auto-scan with the CS0 comparator interrupt enabled allows a system to detect a change in measured capacitance without requiring any additional dedicated MCU resources.

Auto-scan is enabled by setting the CS0 start-of-conversion bits (CS0CF6:4) to 111b. After enabling autoscan, the starting and ending channels should be set to appropriate values in CS0SS and CS0SE, respectively. Writing to CS0SS when auto-scan is enabled will cause the value written to CS0SS to be copied into CS0MX. After being enabled, writing a 1 to CS0BUSY will start auto-scan conversions. When auto-scan completes the number of conversions defined in the CS0 accumulator bits (CS0CF1:0), autoscan configures CS0MX to the next sequential port pin configured as an analog input and begins a conversion on that channel. All other pins between CS0SS and CS0SE which are set as analog inputs are grounded during the conversion. This scan sequence continues until CS0MX reaches the ending input channel value defined in CS0SE. After one or more conversions have been taken at this channel, autoscan configures CS0MX back to the starting input channel. For an example system configured to use autoscan, please see Figure "8.2 Auto-Scan Example" on page 103.

**Note:** Auto-scan attempts one conversion on a CS0MX channel regardless of whether that channel's port pin has been configured as an analog input. Auto-scan will also complete the current rotation when the device is halted for debugging.

If auto-scan is enabled when the device enters suspend mode, auto-scan will remain enabled and running. This feature allows the device to wake from suspend through CS0 greater-than comparator event on any configured capacitive sense input included in the auto-scan sequence of inputs.

Figure 8.2. Auto-Scan Example

## 9.4. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic I. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

## SFR Definition 9.1. DPL: Data Pointer Low Byte

| Bit                                | 7             | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------|---------------|-----|---|---|---|---|---|---|

| Name                               | DPL[7:0]      |     |   |   |   |   |   |   |

| Туре                               |               | R/W |   |   |   |   |   |   |

| Reset                              | 0             | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Page = All; SFR Address = 0x82 |               |     |   |   |   |   |   |   |

| Bit                                | Name Function |     |   |   |   |   |   |   |

| Bit | Name     | Function                                                                                                                    |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------|

| 7:0 | DPL[7:0] | Data Pointer Low.                                                                                                           |

|     |          | The DPL register is the low byte of the 16-bit DPTR. DPTR is used to access indi-<br>rectly addressed Flash memory or XRAM. |

# SFR Definition 9.2. DPH: Data Pointer High Byte

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|---|---|---|---|---|---|---|

| Name  | DPH[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W      |   |   |   |   |   |   |   |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Page = All; SFR Address = 0x83

| Bit | Name     | Function                                                                                                                     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | DPH[7:0] | Data Pointer High.                                                                                                           |

|     |          | The DPH register is the high byte of the 16-bit DPTR. DPTR is used to access indi-<br>rectly addressed Flash memory or XRAM. |

space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 10.1 illustrates the data memory organization of the C8051F99x-C8051F98x.

#### 10.2.1.1.General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 9.6). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 10.2.1.2.Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 10.2.1.3.Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

#### 10.2.2. External RAM

There are 256 bytes of on-chip RAM mapped into the external data memory space. All of these address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using MOVX indirect addressing mode (such as @R1).

### 14.1.2. Flash Erase Procedure

The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire Flash page, perform the following steps:

- 1. Save current interrupt state and disable interrupts.

- 2. Set the PSEE bit (register PSCTL).

- 3. Set the PSWE bit (register PSCTL).

- 4. Write the first key code to FLKEY: 0xA5.

- 5. Write the second key code to FLKEY: 0xF1.

- 6. Using the MOVX instruction, write a data byte to any location within the page to be erased.

- 7. Clear the PSWE and PSEE bits.

- 8. Restore previous interrupt state.

Steps 4–6 must be repeated for each 512-byte page to be erased.

#### Notes:

- 1. Flash security settings may prevent erasure of some Flash pages, such as the reserved area and the page containing the lock bytes. For a summary of Flash security settings and restrictions affecting Flash erase operations, please see Section "14.3. Security Options" on page 152.

- 2. 8-bit MOVX instructions cannot be used to erase or write to Flash memory at addresses higher than 0x00FF.

#### 14.1.3. Flash Write Procedure

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. A byte location to be programmed should be erased before a new value is written.

The recommended procedure for writing a single byte in Flash is as follows:

- 1. Save current interrupt state and disable interrupts.

- 2. Ensure that the Flash byte has been erased (has a value of 0xFF).

- 3. Set the PSWE bit (register PSCTL).

- 4. Clear the PSEE bit (register PSCTL).

- 5. Write the first key code to FLKEY: 0xA5.

- 6. Write the second key code to FLKEY: 0xF1.

- 7. Using the MOVX instruction, write a single data byte to the desired location within the 1024-byte sector.

- 8. Clear the PSWE bit.

- 9. Restore previous interrupt state.

Steps 5–7 must be repeated for each byte to be written.

#### Notes:

- 1. Flash security settings may prevent writes to some areas of Flash, such as the reserved area. For a summary of Flash security settings and restrictions affecting Flash write operations, please see Section "14.3. Security Options" on page 152.

- 2. 8-bit MOVX instructions cannot be used to erase or write to Flash memory at addresses higher than 0x00FF.

#### 14.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. MOVX read instructions always target XRAM.

# SFR Definition 14.4. FLKEY: Flash Lock and Key

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7              | 6           | 5          | 4       | 3        | 2                                                                   | 1 | 0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|------------|---------|----------|---------------------------------------------------------------------|---|---|

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ame FLKEY[7:0] |             |            |         |          |                                                                     |   |   |

| Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |             |            | R       | /W       |                                                                     |   |   |

| Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t 0            | 0           | 0          | 0       | 0        | 0                                                                   | 0 | 0 |

| SFR P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | age = All; SF  | R Address = | 0xB7       | L       |          |                                                                     |   | 1 |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Name           |             |            |         | Function |                                                                     |   |   |

| 7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FLKEY[7:0]     | Flash Lock  | and Key Re | gister. |          |                                                                     |   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                | Write:      |            |         |          |                                                                     |   |   |

| <ul> <li>Write:</li> <li>This register provides a lock and key function for Flash erasures and writes. Flawrites and erases are enabled by writing 0xA5 followed by 0xF1 to the FLKEY referses and erases are automatically disabled after the next write or eracomplete. If any writes to FLKEY are performed incorrectly, or if a Flash write or operation is attempted while these operations are disabled, the Flash will be penently locked from writes or erasures until the next device reset. If an application never writes to Flash, it can intentionally lock the Flash by writing a non-0xA5 va FLKEY from software.</li> <li>Read:</li> <li>When read, bits 1–0 indicate the current Flash lock state.</li> <li>00: Flash is write/erase locked.</li> <li>01: The first key code has been written (0xA5).</li> <li>10: Flash is unlocked (writes/erases allowed).</li> <li>11: Flash writes/erases disabled until the next reset.</li> </ul> |                |             |            |         |          | KEY regis-<br>or erase is<br>rite or erase<br>be perma-<br>lication |   |   |

# SFR Definition 15.1. PMU0CF: Power Management Unit Configuration<sup>1,2,3</sup>

| Bit   | 7     | 6       | 5     | 4      | 3      | 2      | 1      | 0      |

|-------|-------|---------|-------|--------|--------|--------|--------|--------|

| Name  | SLEEP | SUSPEND | CLEAR | RSTWK  | RTCFWK | RTCAWK | PMATWK | CPT0WK |

| Туре  | W     | W       | W     | R      | R/W    | R/W    | R/W    | R/W    |

| Reset | 0     | 0       | 0     | Varies | Varies | Varies | Varies | Varies |

SFR Page = 0x0; SFR Address = 0xB5

| Bit | Name    | Description                                                     | Write                                                                                                 | Read                                                               |

|-----|---------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 7   | SLEEP   | Sleep Mode Select                                               | Writing 1 places the device in Sleep Mode.                                                            | N/A                                                                |

| 6   | SUSPEND | Suspend Mode Select                                             | Writing 1 places the device in Suspend Mode.                                                          | N/A                                                                |

| 5   | CLEAR   | Wake-up Flag Clear                                              | Writing 1 clears all wake-<br>up flags.                                                               | N/A                                                                |

| 4   | RSTWK   | Reset Pin Wake-up Flag                                          | N/A                                                                                                   | Set to 1 if a glitch <u>has</u><br>been detected on RST.           |

| S   | RTCFWK  | SmaRTClock Oscillator<br>Fail Wake-up Source<br>Enable and Flag | 0: Disable wake-up on<br>SmaRTClock Osc. Fail.<br>1: Enable wake-up on<br>SmaRTClock Osc. Fail.       | Set to 1 if the SmaRT-<br>Clock Oscillator has failed.             |

| 2   | RTCAWK  | SmaRTClock Alarm<br>Wake-up Source Enable<br>and Flag           | 0: Disable wake-up on<br>SmaRTClock Alarm.<br>1: Enable wake-up on<br>SmaRTClock Alarm.               | Set to 1 if a SmaRTClock<br>Alarm has occurred.                    |

| 1   | PMATWK  | Port Match Wake-up<br>Source Enable and Flag                    | 0: Disable wake-up on<br>Port Match Event.<br>1: Enable wake-up on<br>Port Match Event.               | Set to 1 if a Port Match<br>Event has occurred.                    |

| 0   | CPTOWK  | Comparator0 Wake-up<br>Source Enable and Flag                   | 0: Disable wake-up on<br>Comparator0 rising edge.<br>1: Enable wake-up on<br>Comparator0 rising edge. | Set to 1 if Comparator0<br>rising edge caused the last<br>wake-up. |

Notes:

1. Read-modify-write operations (ORL, ANL, etc.) should not be used on this register. Wake-up sources must be re-enabled each time the SLEEP or SUSPEND bits are written to 1.

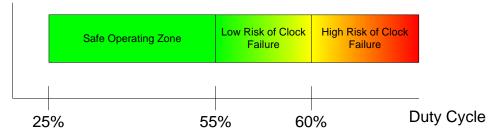

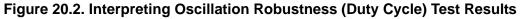

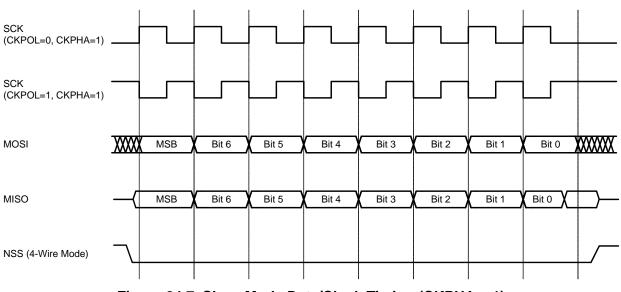

2. The Low Power Internal Oscillator cannot be disabled and the MCU cannot be placed in Suspend or Sleep Mode if any wake-up flags are set to 1. Software should clear all wake-up sources after each reset and after each wake-up from Suspend or Sleep Modes.