Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Obsolete                                                       |

| Core Processor             | CIP-51 8051                                                    |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, POR, PWM, WDT               |

| Number of I/O              | 16                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 20-UFQFN Exposed Pad                                           |

| Supplier Device Package    | 20-QFN (3x3)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f991-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 40.4 latermust later ex                                            | 400 |

|--------------------------------------------------------------------|-----|

| 13.4.Interrupt Latency                                             | 139 |

| 13.5.Interrupt Register Descriptions                               | 141 |

| 13.6.External Interrupts INTO and INT1                             |     |

| 14. Flash Memory                                                   |     |

| 14.1.Programming the Flash Memory                                  |     |

| 14.1.1.Flash Lock and Key Functions                                |     |

| 14.1.2.Flash Erase Procedure                                       |     |

| 14.1.3.Flash Write Procedure                                       |     |

| 14.2.Non-volatile Data Storage                                     |     |

| 14.3.Security Options                                              |     |

| 14.4.Determining the Device Part Number at Run Time                |     |

| 14.5.Flash Write and Erase Guidelines                              |     |

| 14.5.1.V <sub>DD</sub> Maintenance and the V <sub>DD</sub> Monitor | 156 |

| 14.5.2.PSWE Maintenance                                            | 157 |

| 14.5.3.System Clock                                                | 157 |

| 14.6.Minimizing Flash Read Current                                 |     |

| 15. Power Management                                               |     |

| 15.1.Normal Mode                                                   | 163 |

| 15.2.Idle Mode                                                     | 164 |

| 15.3.Stop Mode                                                     | 164 |

| 15.4.Suspend Mode                                                  | 165 |

| 15.5.Sleep Mode                                                    | 165 |

| 15.6.Configuring Wakeup Sources                                    | 166 |

| 15.7.Determining the Event that Caused the Last Wakeup             |     |

| 15.8.Power Management Specifications                               |     |

| 16. Cyclic Redundancy Check Unit (CRC0)                            | 172 |

| 16.1.CRC Algorithm.                                                |     |

| 16.2. Preparing for a CRC Calculation                              | 174 |

| 16.3.Performing a CRC Calculation                                  |     |

| 16.4.Accessing the CRC0 Result                                     |     |

| 16.5.CRC0 Bit Reverse Feature                                      |     |

| 17. Voltage Regulator (VREG0)                                      | 180 |

| 17.1. Voltage Regulator Electrical Specifications                  | 180 |

| 18. Reset Sources.                                                 |     |

| 18.1.Power-On Reset                                                |     |

| 18.2.Power-Fail Reset                                              | 183 |

| 18.3.External Reset                                                | 184 |

| 18.4.Missing Clock Detector Reset                                  | 185 |

| 18.5.Comparator0 Reset                                             |     |

| 18.6.PCA Watchdog Timer Reset                                      |     |

| 18.7.Flash Error Reset                                             |     |

| 18.8.SmaRTClock (Real Time Clock) Reset                            |     |

| 18.9.Software Reset                                                |     |

| 19. Clocking Sources                                               |     |

| 19.1.Programmable Precision Internal Oscillator                    |     |

# List of Registers

| SFR | Definition #            | 5.1. ADC0CN: ADC0 Control                                      | . 74 |

|-----|-------------------------|----------------------------------------------------------------|------|

| SFR | Definition #            | 5.2. ADC0CF: ADC0 Configuration                                | . 75 |

| SFR | Definition #            | 5.3. ADC0AC: ADC0 Accumulator Configuration                    | . 76 |

|     |                         | 5.4. ADC0PWR: ADC0 Burst Mode Power-Up Time                    |      |

| SFR | Definition #            | 5.5. ADC0TK: ADC0 Burst Mode Track Time                        | . 78 |

| SFR | Definition #            | 5.6. ADC0H: ADC0 Data Word High Byte                           | . 79 |

| SFR | Definition \$           | 5.7. ADC0L: ADC0 Data Word Low Byte                            | . 79 |

| SFR | Definition \$           | 5.8. ADC0GTH: ADC0 Greater-Than High Byte                      | . 80 |

| SFR | Definition \$           | 5.9. ADC0GTL: ADC0 Greater-Than Low Byte                       | . 80 |

|     |                         | 5.10. ADC0LTH: ADC0 Less-Than High Byte                        |      |

|     |                         | 5.11. ADC0LTL: ADC0 Less-Than Low Byte                         |      |

|     |                         | 5.12. ADC0MX: ADC0 Input Channel Select                        |      |

| SFR | Definition \$           | 5.13. TOFFH: ADC0 Data Word High Byte                          | . 87 |

|     |                         | 5.14. TOFFL: ADC0 Data Word Low Byte                           |      |

|     |                         | 5.15. REF0CN: Voltage Reference Control                        |      |

|     |                         | 6.1. IREF0CN: Current Reference Control                        |      |

|     |                         | 6.2. IREF0CF: Current Reference Configuration                  |      |

|     |                         | 7.1. CPT0CN: Comparator 0 Control                              |      |

| SFR | Definition              | 7.2. CPT0MD: Comparator 0 Mode Selection                       | . 97 |

| SFR | Definition              | 7.3. CPT0MX: Comparator0 Input Channel Select                  | . 99 |

| SFR | Definition 8            | 8.1. CS0CN: Capacitive Sense Control                           | 107  |

|     |                         | 8.2. CS0CF: Capacitive Sense Configuration                     |      |

|     |                         | 8.3. CS0DH: Capacitive Sense Data High Byte                    |      |

|     |                         | 8.4. CS0DL: Capacitive Sense Data Low Byte                     |      |

|     |                         | 8.5. CS0SCAN0: Capacitive Sense Channel Scan Mask 0            |      |

|     |                         | 8.6. CS0SCAN1: Capacitive Sense Channel Scan Mask 1            |      |

|     |                         | 8.7. CS0SS: Capacitive Sense Auto-Scan Start Channel           |      |

|     |                         | 8.8. CS0SE: Capacitive Sense Auto-Scan End Channel             |      |

|     |                         | 8.9. CS0THH: Capacitive Sense Comparator Threshold High Byte   |      |

|     |                         | 8.10. CS0THL: Capacitive Sense Comparator Threshold Low Byte . |      |

|     |                         | 8.11. CS0MD1: Capacitive Sense Mode 1                          |      |

|     |                         | 8.12. CS0MD2: Capacitive Sense Mode 2                          |      |

|     |                         | 8.13. CS0MD3: Capacitive Sense Mode 3                          |      |

|     |                         | 8.14. CS0PM: Capacitive Sense Pin Monitor                      |      |

|     |                         | 8.15. CS0MX: Capacitive Sense Mux Channel Select               |      |

|     |                         | 9.1. DPL: Data Pointer Low Byte                                |      |

|     |                         | 9.2. DPH: Data Pointer High Byte                               |      |

|     |                         | 9.3. SP: Stack Pointer                                         |      |

|     |                         | 9.4. ACC: Accumulator                                          |      |

|     |                         | 9.5. B: B Register                                             |      |

|     |                         | 9.6. PSW: Program Status Word                                  |      |

|     |                         | 12.1. SFR Page: SFR Page                                       |      |

| SFR | Definition <sup>2</sup> | 13.1. IE: Interrupt Enable                                     | 142  |

#### Table 4.2. Global Electrical Characteristics (Continued)

-40 to +85 °C, 25 MHz system clock unless otherwise specified. See "AN358: Optimizing Low Power Operation of the 'F9xx" for details on how to achieve the supply current specifications listed in this table.

| Parameter | Conditions | Min | Тур | Max | Units |

|-----------|------------|-----|-----|-----|-------|

| Notes:    |            |     |     |     |       |

| 1 | Based on devic | e characterization | n data: Not | production tested. |

|---|----------------|--------------------|-------------|--------------------|

|   | Dased on devic |                    | ruala, not  | production tested. |

- 2. SYSCLK must be at least 32 kHz to enable debugging.

- **3.** Digital Supply Current depends upon the particular code being executed. The values in this table are obtained with the CPU executing an "simp \$" loop, which is the compiled form of a while(1) loop in C. One iteration requires 3 CPU clock cycles, and the Flash memory is read on each cycle. The supply current will vary slightly based on the physical location of the simp instruction and the number of Flash address lines that toggle as a result. In the worst case, current can increase by up to 30% if the simp loop straddles a 64-byte Flash address boundary (e.g., 0x007F to 0x0080). Real-world code with larger loops and longer linear sequences will have few transitions across the 64-byte address boundaries.

- 4. Includes oscillator and regulator supply current.

- 5. IDD can be estimated for frequencies < 14 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range, then adding an offset of 84 μA. When using these numbers to estimate I<sub>DD</sub> for > 14 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 3.0 V; F = 20 MHz, I<sub>DD</sub> = 3.6 mA (25 MHz 20 MHz) x 0.088 mA/MHz = 3.16 mA assuming the same oscillator setting.

- 6. Idle IDD can be estimated by taking the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 3.0 V; F = 5 MHz, Idle I<sub>DD</sub> = 1.75 mA (25 MHz 5 MHz) x 0.067 mA/MHz = 0.41 mA.

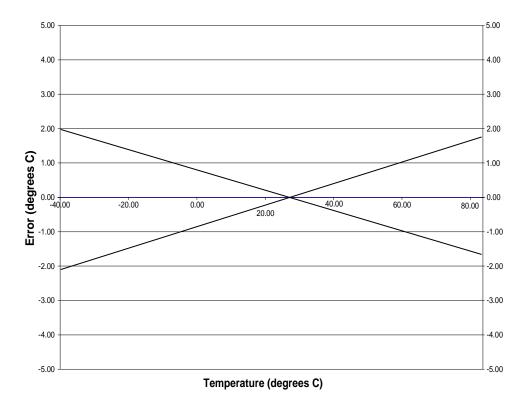

#### 5.8.1. Calibration

The uncalibrated temperature sensor output is extremely linear and suitable for relative temperature measurements (see Table 4.11 for linearity specifications). For absolute temperature measurements, offset and/or gain calibration is recommended. Typically a 1-point (offset) calibration includes the following steps:

- 1. Control/measure the ambient temperature (this temperature must be known).

- 2. Power the device, and delay for a few seconds to allow for self-heating.

- 3. Perform an ADC conversion with the temperature sensor selected as the positive input and GND selected as the negative input.

- 4. Calculate the offset characteristics, and store this value in non-volatile memory for use with subsequent temperature sensor measurements.

Figure 5.9 shows the typical temperature sensor error assuming a 1-point calibration at 25 °C. **Parameters that affect ADC measurement, in particular the voltage reference value, will also affect temperature measurement.**

A single-point offset measurement of the temperature sensor is performed on each device during production test. The measurement is performed at 25 °C  $\pm$ 5 °C, using the ADC with the internal high speed reference buffer selected as the Voltage Reference. The direct ADC result of the measurement is stored in the SFR registers TOFFH and TOFFL, shown in SFR Definition 5.13 and SFR Definition 5.14.

Figure 5.9. Temperature Sensor Error with 1-Point Calibration (V<sub>REF</sub> = 1.65 V)

# SFR Definition 7.1. CPT0CN: Comparator 0 Control

| Bit   | 7     | 6      | 5             | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|---------------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | <b>CP0RIF</b> | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W           | R/W    | R/W         |   | R/W         |   |

| Reset | 0     | 0      | 0             | 0      | 0           | 0 | 0           | 0 |

#### SFR Page= 0x0; SFR Address = 0x9B

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0                                                      |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3-2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = Hysteresis 1.                                       |

|     |             | 10: Positive Hysteresis = Hysteresis 2.                                       |

|     |             | 11: Positive Hysteresis = Hysteresis 3 (Maximum).                             |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = Hysteresis 1.                                       |

|     |             | 10: Negative Hysteresis = Hysteresis 2.                                       |

|     |             | 11: Negative Hysteresis = Hysteresis 3 (Maximum).                             |

space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 10.1 illustrates the data memory organization of the C8051F99x-C8051F98x.

#### 10.2.1.1.General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 9.6). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 10.2.1.2.Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 10.2.1.3.Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

#### 10.2.2. External RAM

There are 256 bytes of on-chip RAM mapped into the external data memory space. All of these address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using MOVX indirect addressing mode (such as @R1).

| Register | Address | SFR Page | Description                 | Page |

|----------|---------|----------|-----------------------------|------|

| TCON     | 0x88    | 0x0      | Timer/Counter Control       | 284  |

| TH0      | 0x8C    | 0x0      | Timer/Counter 0 High        | 287  |

| TH1      | 0x8D    | 0x0      | Timer/Counter 1 High        | 287  |

| TL0      | 0x8A    | 0x0      | Timer/Counter 0 Low         | 286  |

| TL1      | 0x8B    | 0x0      | Timer/Counter 1 Low         | 286  |

| TMOD     | 0x89    | 0x0      | Timer/Counter Mode          | 285  |

| TMR2CN   | 0xC8    | 0x0      | Timer/Counter 2 Control     | 291  |

| TMR2H    | 0xCD    | 0x0      | Timer/Counter 2 High        | 293  |

| TMR2L    | 0xCC    | 0x0      | Timer/Counter 2 Low         | 293  |

| TMR2RLH  | 0xCB    | 0x0      | Timer/Counter 2 Reload High | 292  |

| TMR2RLL  | 0xCA    | 0x0      | Timer/Counter 2 Reload Low  | 292  |

| TMR3CN   | 0x91    | 0x0      | Timer/Counter 3 Control     | 297  |

| TMR3H    | 0x95    | 0x0      | Timer/Counter 3 High        | 299  |

| TMR3L    | 0x94    | 0x0      | Timer/Counter 3 Low         | 299  |

| TMR3RLH  | 0x93    | 0x0      | Timer/Counter 3 Reload High | 298  |

| TMR3RLL  | 0x92    | 0x0      | Timer/Counter 3 Reload Low  | 298  |

| TOFFH    | 0x8E    | 0xF      | Temperature Offset High     | 87   |

| TOFFL    | 0x8D    | 0xF      | Temperature Offset Low      | 87   |

| VDM0CN   | 0xFF    | 0x0      | VDD Monitor Control         | 184  |

| XBR0     | 0xE1    | 0x0      | Port I/O Crossbar Control 0 | 222  |

| XBR1     | 0xE2    | 0x0      | Port I/O Crossbar Control 1 | 223  |

| XBR2     | 0xE3    | 0x0      | Port I/O Crossbar Control 2 | 224  |

#### Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

# 13. Interrupt Handler

The C8051F99x-C8051F98x microcontroller family includes an extended interrupt system supporting multiple interrupt sources and two priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Refer to Table 13.1, "Interrupt Summary," on page 140 for a detailed listing of all interrupt sources supported by the device. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR or an indirect register. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1. If both global interrupts and the specific interrupt source is enabled, a CPU interrupt request is generated when the interrupt-pending flag is set.

As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Some interrupt-pending flags are automatically cleared by hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

### 13.1. Enabling Interrupt Sources

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in the Interrupt Enable and Extended Interrupt Enable SFRs. However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings. Note that interrupts which occur when the EA bit is set to logic 0 will be held in a pending state, and will not be serviced until the EA bit is set back to logic 1.

### 13.2. MCU Interrupt Sources and Vectors

The CPU services interrupts by generating an LCALL to a predetermined address (the interrupt vector address) to begin execution of an interrupt service routine (ISR). The interrupt vector addresses associated with each interrupt source are listed in Table 13.1 on page 140. Software should ensure that the interrupt vector for each enabled interrupt source contains a valid interrupt service routine.

Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag.

# SFR Definition 13.7. IT01CF: INT0/INT1 Configuration

| Bit   | 7     | 6          | 5 | 4 | 3     | 2 | 1          | 0 |

|-------|-------|------------|---|---|-------|---|------------|---|

| Name  | IN1PL | IN1SL[2:0] |   |   | IN0PL |   | IN0SL[2:0] |   |

| Туре  | R/W   | R/W        |   |   | R/W   |   | R/W        |   |

| Reset | 0     | 0          | 0 | 0 | 0     | 0 | 0          | 1 |

#### SFR Page = 0x0; SFR Address = 0xE4

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IN1PL      | INT1 Polarity.   0: INT1 input is active low.   1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6:4 | IN1SL[2:0] | INT1 Port Pin Selection Bits.   These bits select which Port pin is assigned to INT1. Note that this pin assignment is independent of the Crossbar; INT1 will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.   000: Select P0.0   001: Select P0.1   010: Select P0.2   011: Select P0.3   100: Select P0.4   101: Select P0.5   111: Select P0.7                                    |

| 3   | IN0PL      | INTO Polarity.<br>0: INTO input is active low.<br>1: INTO input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2:0 | IN0SL[2:0] | <b>INTO</b> Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INTO. Note that this pin assignment is independent of the Crossbar; INTO will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P0.0<br>001: Select P0.1<br>010: Select P0.2<br>011: Select P0.3<br>100: Select P0.4<br>101: Select P0.5<br>110: Select P0.6<br>111: Select P0.7 |

### 15.2. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

**Note:** To ensure the MCU enters a low power state upon entry into Idle Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "18.6. PCA Watchdog Timer Reset" on page 185 for more information on the use and configuration of the WDT.

#### 15.3. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter stop mode as soon as the instruction that sets the bit completes execution. In stop mode the precision internal oscillator and CPU are stopped; the state of the low power oscillator and the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout.

Stop mode is a legacy 8051 power mode; it will not result in optimal power savings. Sleep or suspend mode will provide more power savings if the MCU needs to be inactive for a long period of time.

**Note:** To ensure the MCU enters a low power state upon entry into Stop Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

## SFR Definition 16.4. CRC0AUTO: CRC0 Automatic Control

| Bit   | 7      | 6       | 5 | 4   | 3 | 2          | 1 | 0 |

|-------|--------|---------|---|-----|---|------------|---|---|

| Name  | AUTOEN | CRCDONE |   |     | ( | CRC0ST[4:0 | ] |   |

| Туре  | R/W    | R       | R | R/W |   |            |   |   |

| Reset | 0      | 1       | 0 | 0   | 0 | 0          | 0 | 0 |

#### SFR Page = All; SFR Address = 0x9E

| Bit | Name        | Function                                                                                                                                                                                                                                |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AUTOEN      | Automatic CRC Calculation Enable.                                                                                                                                                                                                       |

|     |             | When AUTOEN is set to 1, any write to CRC0CN will initiate an automatic CRC starting at Flash sector CRC0ST and continuing for CRC0CNT sectors.                                                                                         |

| 6   | CRCDONE     | CRCDONE Automatic CRC Calculation Complete.                                                                                                                                                                                             |

|     |             | Set to 0 when a CRC calculation is in progress. Code execution is stopped during a CRC calculation; therefore, reads from firmware will always return 1.                                                                                |

| 5   | Unused      | Read = 0b; Write = Don't Care.                                                                                                                                                                                                          |

| 4:0 | CRC0ST[4:0] | Automatic CRC Calculation Starting Block.                                                                                                                                                                                               |

|     |             | These bits specify the Flash block to start the automatic CRC calculation. The starting address of the first Flash block included in the automatic CRC calculation is CRC0ST x Block Size.<br><b>Note:</b> The block size is 256 bytes. |

# 17. Voltage Regulator (VREG0)

C8051F99x-C8051F98x devices include an internal voltage regulator (VREG0) to regulate the internal core supply to 1.8 V from a VDD supply of 1.8 to 3.6 V. Electrical characteristics for the on-chip regulator are specified in the Electrical Specifications chapter.

The REGOCN register allows the Precision Oscillator Bias to be disabled, reducing supply current in all non-Sleep power modes. This bias should only be disabled when the precision oscillator is not being used.

The internal regulator (VREG0) is disabled when the device enters Sleep Mode and remains enabled when the device enters Suspend Mode. See Section "15. Power Management" on page 162 for complete details about low power modes.

### SFR Definition 17.1. REG0CN: Voltage Regulator Control

| Bit   | 7 | 6        | 5        | 4       | 3 | 2 | 1 | 0        |

|-------|---|----------|----------|---------|---|---|---|----------|

| Name  |   | Reserved | Reserved | OSCBIAS |   |   |   | Reserved |

| Туре  | R | R/W      | R/W      | R/W     | R | R | R | R/W      |

| Reset | 0 | 0        | 0        | 0       | 0 | 0 | 0 | 0        |

#### SFR Page = 0x0; SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused   | Read = 0b. Write = Don't care.                                                                                                                                                                            |

| 6:5 | Reserved | Read = 00b. Must Write 00b.                                                                                                                                                                               |

| 4   | OSCBIAS  | Precision Oscillator Bias.                                                                                                                                                                                |

|     |          | When set to 1, the bias used by the precision oscillator is forced on. If the precision oscillator is not being used, this bit may be cleared to 0 to reduce supply current in all non-Sleep power modes. |

| 3:1 | Unused   | Read = 000b. Write = Don't care.                                                                                                                                                                          |

| 0   | Reserved | Read = 0b. Must Write 0b.                                                                                                                                                                                 |

### 17.1. Voltage Regulator Electrical Specifications

See Table 4.15 on page 64 for detailed Voltage Regulator Electrical Specifications.

# Internal Register Definition 20.4. RTC0CN: SmaRTClock Control

| Bit   | 7          | 6                                                                                        | 5                                                                                                                                                                                | 4                    | 3                                                          | 2                | 1                               | 0             |  |  |  |

|-------|------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------|------------------|---------------------------------|---------------|--|--|--|

| Name  | RTCOEN     | MCLKEN                                                                                   | OSCFAIL                                                                                                                                                                          | RTC0TR               | RTC0AEN                                                    | ALRM             | <b>RTC0SET</b>                  | RTC0CAP       |  |  |  |

| Туре  | R/W        | R/W                                                                                      | R/W                                                                                                                                                                              | R/W                  | R/W                                                        | R/W              | R/W                             | R/W           |  |  |  |

| Rese  | t 0        | 0                                                                                        | Varies                                                                                                                                                                           | 0                    | 0                                                          | 0                | 0                               | 0             |  |  |  |

| SmaR  | TClock Add | ress = 0x04                                                                              |                                                                                                                                                                                  |                      |                                                            |                  |                                 |               |  |  |  |

| Bit   | Name       |                                                                                          |                                                                                                                                                                                  |                      | Function                                                   |                  |                                 |               |  |  |  |

| 7     | RTC0EN     | SmaRTClock Enable.                                                                       |                                                                                                                                                                                  |                      |                                                            |                  |                                 |               |  |  |  |

|       |            | 0: SmaRTCloc                                                                             | Enables/disables the SmaRTClock oscillator and associated bias currents.<br>): SmaRTClock oscillator disabled.<br>: SmaRTClock oscillator enabled.                               |                      |                                                            |                  |                                 |               |  |  |  |

| 6     | MCLKEN     | Missing SmaR                                                                             | TClock Dete                                                                                                                                                                      | ctor Enable.         |                                                            |                  |                                 |               |  |  |  |

|       |            | Enables/disable<br>0: Missing Sma<br>1: Missing Sma                                      | RTClock dete                                                                                                                                                                     | ector disabled       | l.                                                         |                  |                                 |               |  |  |  |

| 5     | OSCFAIL    | SmaRTClock                                                                               | Oscillator Fai                                                                                                                                                                   | il Event Flag        | •                                                          |                  |                                 |               |  |  |  |

|       |            | software. The v                                                                          | Set by hardware when a missing SmaRTClock detector timeout occurs. Must be cleared by software. The value of this bit is not defined when the SmaRTClock oscillator is disabled. |                      |                                                            |                  |                                 |               |  |  |  |

| 4     | RTC0TR     | SmaRTClock                                                                               | Timer Run Co                                                                                                                                                                     | ontrol.              |                                                            |                  |                                 |               |  |  |  |

|       |            | Controls if the S<br>0: SmaRTClock<br>1: SmaRTClock                                      | k timer is stop                                                                                                                                                                  | ped.                 | ng or stopped                                              | (holds currer    | nt value).                      |               |  |  |  |

| 3     | RTC0AEN    | SmaRTClock                                                                               |                                                                                                                                                                                  |                      |                                                            |                  |                                 |               |  |  |  |

|       |            | Enables/disabl<br>0: SmaRTCloc<br>1: SmaRTCloc                                           | k alarm disabl                                                                                                                                                                   | ed.                  | function. Also                                             | clears the Al    | ₋RM flag.                       |               |  |  |  |

| 2     | ALRM       | SmaRTClock                                                                               |                                                                                                                                                                                  | Read:                |                                                            | Wr               |                                 |               |  |  |  |

|       |            | Flag and Auto<br>Reads return th<br>alarm event fla<br>Writes enable/o<br>Auto Reset fun | ne state of the<br>g.<br>disable the                                                                                                                                             | flag is d<br>1: Smal | RTClock alarm<br>le-asserted.<br>RTClock alarm<br>sserted. | 1: E             | Disable Auto R<br>Enable Auto R |               |  |  |  |

| 1     | RTC0SET    | SmaRTClock                                                                               | Timer Set.                                                                                                                                                                       |                      |                                                            |                  |                                 |               |  |  |  |

|       |            | Writing 1 initiate cate that the tir                                                     | ner set operat                                                                                                                                                                   | ion is comple        |                                                            | is bit is clear  | ed to 0 by hard                 | ware to indi- |  |  |  |

| 0     | RTC0CAP    | SmaRTClock                                                                               | -                                                                                                                                                                                |                      |                                                            |                  |                                 |               |  |  |  |

|       |            | Writing 1 initiate indicate that the                                                     |                                                                                                                                                                                  |                      |                                                            | n. This bit is c | leared to 0 by                  | hardware to   |  |  |  |

| Note: |            | ag will remain a                                                                         |                                                                                                                                                                                  |                      |                                                            | •                |                                 |               |  |  |  |

|       |            | it" on page 162 f<br>atically cleared                                                    |                                                                                                                                                                                  | on how to ca         | apture a SmaR                                              | TClock Aları     | n event using                   | a flag which  |  |  |  |

## SFR Definition 21.3. XBR2: Port I/O Crossbar Register 2

| Bit   | 7       | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------|-------|-----|-----|-----|-----|-----|-----|

| Name  | WEAKPUD | XBARE |     |     |     |     |     |     |

| Туре  | R/W     | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0       | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Page = 0x0; SFR Address = 0xE3

| Bit   | Name           | Function                                                                                                    |

|-------|----------------|-------------------------------------------------------------------------------------------------------------|

| 7     | WEAKPUD        | Port I/O Weak Pullup Disable.                                                                               |

|       |                | 0: Weak Pullups enabled (except for Port I/O pins configured for analog mode).<br>1: Weak Pullups disabled. |

| 6     | XBARE          | Crossbar Enable.                                                                                            |

|       |                | 0: Crossbar disabled.                                                                                       |

|       |                | 1: Crossbar enabled.                                                                                        |

| 5:0   | Unused         | Read = 000000b; Write = Don't Care.                                                                         |

| Note: | The Crossbar m | ust be enabled (XBARE = 1) to use any Port pin as a digital output.                                         |

## SFR Definition 21.15. P1MDIN: Port1 Input Mode

| Bit   | 7           | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-------|-------------|---|---|----|---|---|---|---|--|--|--|

| Name  | P1MDIN[7:0] |   |   |    |   |   |   |   |  |  |  |

| Туре  |             |   |   | R/ | W |   |   |   |  |  |  |

| Reset | 1           |   |   |    |   |   |   |   |  |  |  |

SFR Page = 0x0; SFR Address = 0xF2

| Bit | Name        | Function                                                                                                                                                                                                                                                                 |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDIN[7:0] | Analog Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                                                                  |

|     |             | Port pins configured for analog mode have their weak pullup and digital receiver<br>disabled. The digital driver is not explicitly disabled.<br>0: Corresponding P1.n pin is configured for analog mode.<br>1: Corresponding P1.n pin is not configured for analog mode. |

### SFR Definition 21.16. P1MDOUT: Port1 Output Mode

| Bit   | 7            | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|--------------|-----------------|---|---|---|---|---|---|--|--|--|

| Name  | P1MDOUT[7:0] |                 |   |   |   |   |   |   |  |  |  |

| Туре  |              | R/W             |   |   |   |   |   |   |  |  |  |

| Reset | 0            | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |

SFR Page = 0x0; SFR Address = 0xA5

| Bit | Name         | Function                                                                                             |

|-----|--------------|------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDOUT[7:0] | Output Configuration Bits for P1.7–P1.0 (respectively).                                              |

|     |              | These bits control the digital driver even when the corresponding bit in register P1MDIN is logic 0. |

|     |              | 0: Corresponding P1.n Output is open-drain.                                                          |

|     |              | 1: Corresponding P1.n Output is push-pull.                                                           |

## SFR Definition 21.17. P1DRV: Port1 Drive Strength

| Bit   | 7          | 6               | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|------------|-----------------|---|----|---|---|---|---|--|--|

| Name  | P1DRV[7:0] |                 |   |    |   |   |   |   |  |  |

| Туре  |            |                 |   | R/ | W |   |   |   |  |  |

| Reset | 0          | 0 0 0 0 0 0 0 0 |   |    |   |   |   |   |  |  |

SFR Page = 0xF; SFR Address = 0x9B

| Bit | Name       | Function                                                                                                                                                                                               |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |  |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |  |

### SFR Definition 21.18. P2: Port2

| Bit   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|---|---|---|---|---|---|---|

| Name  | P2  |   |   |   |   |   |   |   |

| Туре  | R/W | R | R | R | R | R | R | R |

| Reset | 1   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = All; SFR Address = 0xA0; Bit-Addressable

| Bit | Name   | Description                                                                                                                                   | Read                                                                          | Write |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------|

| 7   | P2     | <b>Port 2 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW.  |

| 6:0 | Unused | Read = 0000000b; Write = D                                                                                                                    | on't Care.                                                                    |       |

# SFR Definition 25.9. TMR2RLL: Timer 2 Reload Register Low Byte

| Bit                                | 7    | 6            | 5 | 4  | 3 | 2 | 1 | 0 |

|------------------------------------|------|--------------|---|----|---|---|---|---|

| Name                               |      | TMR2RLL[7:0] |   |    |   |   |   |   |

| Туре                               |      |              |   | R/ | W |   |   |   |

| Reset                              | 0    | 0            | 0 | 0  | 0 | 0 | 0 | 0 |

| SFR Page = 0x0; SFR Address = 0xCA |      |              |   |    |   |   |   |   |

| Bit                                | Name |              |   |    |   |   |   |   |

| Bit | Name         | Function                                                    |

|-----|--------------|-------------------------------------------------------------|

| 7:0 | TMR2RLL[7:0] | Timer 2 Reload Register Low Byte.                           |

|     |              | TMR2RLL holds the low byte of the reload value for Timer 2. |

## SFR Definition 25.10. TMR2RLH: Timer 2 Reload Register High Byte

| Bit   | 7                                               | 6           | 5                                                           | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------------------------------------------------|-------------|-------------------------------------------------------------|---|---|---|---|---|--|

| Nam   | Name TMR2RLH[7:0]                               |             |                                                             |   |   |   |   |   |  |

| Туре  | e                                               | R/W         |                                                             |   |   |   |   |   |  |

| Rese  | et O                                            | 0           | 0                                                           | 0 | 0 | 0 | 0 | 0 |  |

| SFR F | Page = 0x0; SF                                  | R Address : | = 0xCB                                                      |   |   |   | • |   |  |

| Bit   | Name                                            |             | Function                                                    |   |   |   |   |   |  |

| 7:0   | TMR2RLH[7:0] Timer 2 Reload Register High Byte. |             |                                                             |   |   |   |   |   |  |

|       |                                                 | TMR2RL      | MR2RLH holds the high byte of the reload value for Timer 2. |   |   |   |   |   |  |

## SFR Definition 25.16. TMR3L: Timer 3 Low Byte

| Bit   | 7 | 6               | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|----|---|---|---|---|--|

| Name  |   | TMR3L[7:0]      |   |    |   |   |   |   |  |

| Туре  |   |                 |   | R/ | W |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |    |   |   |   |   |  |

SFR Page = 0x0; SFR Address = 0x94

| Bit | Name       | Function                                                                                                       |

|-----|------------|----------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3L[7:0] | <b>Timer 3 Low Byte.</b><br>In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In |

|     |            | 8-bit mode, TMR3L contains the 8-bit low byte timer value.                                                     |

### SFR Definition 25.17. TMR3H Timer 3 High Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|------------|---|---|---|---|---|---|--|

| Name  |   | TMR3H[7:0] |   |   |   |   |   |   |  |

| Туре  |   | R/W        |   |   |   |   |   |   |  |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Page = 0x0; SFR Address = 0x95

| Bit | Name       | Function                                                                                                                                        |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3H[7:0] | Timer 3 High Byte.                                                                                                                              |

|     |            | In 16-bit mode, the TMR3H register contains the high byte of the 16-bit Timer 3. In 8-bit mode, TMR3H contains the 8-bit high byte timer value. |

## SFR Definition 26.5. PCA0L: PCA Counter/Timer Low Byte

| Bit   | 7   | 6   | 5   | 4   | 3      | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|--------|-----|-----|-----|

| Name  |     |     |     | PCA | D[7:0] |     |     |     |

| Туре  | R/W | R/W | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset | 0   | 0   | 0   | 0   | 0      | 0   | 0   | 0   |

SFR Page = 0x0; SFR Address = 0xF9

| Bit   | Name                                                                                                                                                                             | Function                                                                     |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0   | PCA0[7:0]                                                                                                                                                                        | PCA Counter/Timer Low Byte.                                                  |  |  |  |  |  |  |

|       |                                                                                                                                                                                  | The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. |  |  |  |  |  |  |

| Note: | Note: When the WDTE bit is set to 1, the PCA0L register cannot be modified by software. To change the contents of the PCA0L register, the Watchdog Timer must first be disabled. |                                                                              |  |  |  |  |  |  |

## SFR Definition 26.6. PCA0H: PCA Counter/Timer High Byte

| Bit   | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----|------------|-----|-----|-----|-----|-----|-----|--|

| Name  |     | PCA0[15:8] |     |     |     |     |     |     |  |

| Туре  | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |  |

SFR Page = 0x0; SFR Address = 0xFA

| Bit   | Name                                                                                                                                                                             | Function                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | PCA0[15:8]                                                                                                                                                                       | PCA Counter/Timer High Byte.                                                                                                                                                                                                                        |  |  |  |  |  |

|       |                                                                                                                                                                                  | The PCA0H register holds the high byte (MSB) of the 16-bit PCA Counter/Timer.<br>Reads of this register will read the contents of a "snapshot" register, whose contents<br>are updated only when the contents of PCA0L are read (see Section 26.1). |  |  |  |  |  |

| Note: | Note: When the WDTE bit is set to 1, the PCA0H register cannot be modified by software. To change the contents of the PCA0H register, the Watchdog Timer must first be disabled. |                                                                                                                                                                                                                                                     |  |  |  |  |  |

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Laboratories and "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

### http://www.silabs.com