# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                       |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, POR, PWM, Temp Sensor, WDT     |

| Number of I/O              | 17                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                       |

| Data Converters            | A/D 10x12b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                    |

| Supplier Device Package    | 24-QSOP                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f996-c-gur |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.2. Electrical Characteristics

### **Table 4.2. Global Electrical Characteristics**

-40 to +85 °C, 25 MHz system clock unless otherwise specified. See "AN358: Optimizing Low Power Operation of the 'F9xx" for details on how to achieve the supply current specifications listed in this table.

| Parameter                                                   | Conditions                                                                                                | Min      | Тур        | Max  | Units    |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------|------------|------|----------|

| Supply Voltage (V <sub>DD</sub> )                           |                                                                                                           | 1.8      | 2.4        | 3.6  | V        |

| Minimum RAM Data                                            | not in sleep mode                                                                                         | _        | 1.4        |      | V        |

| Retention Voltage <sup>1</sup>                              | in sleep mode                                                                                             | —        | 0.3        | 0.45 |          |

| SYSCLK (System Clock) <sup>2</sup>                          |                                                                                                           | 0        | _          | 25   | MHz      |

| T <sub>SYSH</sub> (SYSCLK High Time)                        |                                                                                                           | 18       | —          | _    | ns       |

| T <sub>SYSL</sub> (SYSCLK Low Time)                         |                                                                                                           | 18       | —          | _    | ns       |

| Specified Operating<br>Temperature Range                    |                                                                                                           | -40      | —          | +85  | °C       |

| Digital Supply Current—CP                                   | U Active (Normal Mode, fetching instruct                                                                  | tions fr | om Fla     | sh)  |          |

| I <sub>DD</sub> <sup>3, 4, 5</sup>                          | V <sub>DD</sub> = 1.8–3.6 V, F = 24.5 MHz<br>(includes precision oscillator current)                      |          | 3.6        | 4.5  | mA       |

|                                                             | V <sub>DD</sub> = 1.8–3.6 V, F = 20 MHz<br>(includes low power oscillator current)                        |          | 3.1        | _    | mA       |

|                                                             | $V_{DD}$ = 1.8 V, F = 1 MHz<br>$V_{DD}$ = 3.6 V, F = 1 MHz<br>(includes external oscillator/GPIO current) |          | 225<br>290 |      | μΑ<br>μΑ |

|                                                             | V <sub>DD</sub> = 1.8–3.6 V, F = 32.768 kHz<br>(includes SmaRTClock oscillator current)                   | _        | 84         | _    | μA       |

| I <sub>DD</sub> Frequency<br>Sensitivity <sup>1, 3, 5</sup> | $V_{DD}$ = 1.8–3.6 V, T = 25 °C, F < 14 MHz<br>(Flash oneshot active, see Section 14.6)                   | _        | 174        | —    | µA/MHz   |

|                                                             | V <sub>DD</sub> = 1.8–3.6 V, T = 25 °C, F > 14 MHz<br>(Flash oneshot bypassed, see Section<br>14.6)       |          | 88         |      | µA/MHz   |

| Mnemonic                      | Description                              | Bytes | Clock<br>Cycles |

|-------------------------------|------------------------------------------|-------|-----------------|

|                               | Arithmetic Operations                    |       |                 |

| ADD A, Rn                     | Add register to A                        | 1     | 1               |

| ADD A, direct                 | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri                    | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data                  | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn                    | Add register to A with carry             | 1     | 1               |

| ADDC A, direct                | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri                   | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data                 | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn                    | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct                | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri                   | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data                 | Subtract immediate from A with borrow    | 2     | 2               |

| INC A                         | Increment A                              | 1     | 1               |

| INC Rn                        | Increment register                       | 1     | 1               |

| INC direct                    | Increment direct byte                    | 2     | 2               |

| INC @Ri                       | Increment indirect RAM                   | 1     | 2               |

| DEC A                         | Decrement A                              | 1     | 1               |

| DEC Rn                        | Decrement register                       | 1     | 1               |

| DEC direct                    | Decrement direct byte                    | 2     | 2               |

| DEC @Ri                       | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR                      | Increment Data Pointer                   | 1     | 1               |

| MUL AB                        | Multiply A and B                         | 1     | 4               |

| DIV AB                        | Divide A by B                            | 1     | 8               |

| DAA                           | Decimal adjust A                         | 1     | 1               |

|                               | Logical Operations                       |       | ·               |

| ANL A, Rn                     | AND Register to A                        | 1     | 1               |

| ANL A, direct                 | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri                    | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data                  | AND immediate to A                       | 2     | 2               |

| ANL direct, A                 | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data             | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn                     | OR Register to A                         | 1     | 1               |

| ORL A, direct                 | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri                    | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data                  | OR immediate to A                        | 2     | 2               |

| ORL direct, A                 | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data             | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn                     | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct                 | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri                    | Exclusive-OR indirect RAM to A           | 1     | 2               |

| XRL A, @RI<br>XRL A, #data    | Exclusive-OR immediate to A              | 2     | 2               |

| XRL A, #data<br>XRL direct, A | Exclusive-OR A to direct byte            | 2     | 2               |

| XRL direct, #data             | Exclusive-OR A to direct byte            | 3     | 3               |

| ANE UIIECI, #Uala             |                                          | 3     | 3               |

## Table 9.1. CIP-51 Instruction Set Summary

## SFR Definition 12.1. SFR Page: SFR Page

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|--------------|---|---|---|---|---|---|

| Name  |   | SFRPAGE[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W          |   |   |   |   |   |   |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = All; SFR Address = 0xA7

| Bit | Name         | Function                                                                                    |

|-----|--------------|---------------------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page.                                                                                   |

|     |              | Specifies the SFR Page used when reading, writing, or modifying special function registers. |

## Table 12.3. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register | Address | SFR Page | Description                       | Page |

|----------|---------|----------|-----------------------------------|------|

| ACC      | 0xE0    | All      | Accumulator                       | 126  |

| ADC0AC   | 0xBA    | 0x0      | ADC0 Accumulator Configuration    | 76   |

| ADC0CF   | 0x97    | 0x0      | ADC0 Configuration                | 75   |

| ADC0CN   | 0xE8    | 0x0      | ADC0 Control                      | 74   |

| ADC0GTH  | 0xC4    | 0x0      | ADC0 Greater-Than Compare High    | 80   |

| ADC0GTL  | 0xC3    | 0x0      | ADC0 Greater-Than Compare Low     | 80   |

| ADC0H    | 0xBE    | 0x0      | ADC0 High                         | 79   |

| ADC0L    | 0xBD    | 0x0      | ADC0 Low                          | 79   |

| ADC0LTH  | 0xC6    | 0x0      | ADC0 Less-Than Compare Word High  | 81   |

| ADC0LTL  | 0xC5    | 0x0      | ADC0 Less-Than Compare Word Low   | 81   |

| ADC0MX   | 0x96    | 0x0      | AMUX0 Channel Select              | 84   |

| ADC0PWR  | 0xBB    | All      | ADC0 Burst Mode Power-Up Time     | 77   |

| ADC0TK   | 0xBC    | All      | ADC0 Tracking Control             | 78   |

| В        | 0xF0    | All      | B Register                        | 126  |

| CKCON    | 0x8E    | 0x0      | Clock Control                     | 279  |

| CLKSEL   | 0xA9    | All      | Clock Select                      | 193  |

| CPT0CN   | 0x9B    | 0x0      | Comparator0 Control               | 96   |

| CPT0MD   | 0x9D    | 0x0      | Comparator0 Mode Selection        | 97   |

| CPT0MX   | 0x9F    | 0x0      | Comparator0 Mux Selection         | 99   |

| CRC0AUTO | 0x9E    | All      | CRC0 Automatic Control            | 177  |

| CRC0CN   | 0x84    | All      | CRC0 Control                      | 175  |

| CRC0CNT  | 0x9A    | All      | CRC0 Automatic Flash Sector Count | 178  |

| CRC0DAT  | 0x86    | All      | CRC0 Data                         | 176  |

| CRC0FLIP | 0x9C    | All      | CRC0 Flip                         | 179  |

| CRC0IN   | 0x85    | All      | CRC0 Input                        | 176  |

| CS0CF    | 0xAA    | 0x0      | CS0 Configuration                 | 108  |

| CS0CN    | 0xB0    | 0x0      | CS0 Control                       | 107  |

| Register | Address | SFR Page | Description                 | Page |

|----------|---------|----------|-----------------------------|------|

| TCON     | 0x88    | 0x0      | Timer/Counter Control       | 284  |

| TH0      | 0x8C    | 0x0      | Timer/Counter 0 High        | 287  |

| TH1      | 0x8D    | 0x0      | Timer/Counter 1 High        | 287  |

| TL0      | 0x8A    | 0x0      | Timer/Counter 0 Low         | 286  |

| TL1      | 0x8B    | 0x0      | Timer/Counter 1 Low         | 286  |

| TMOD     | 0x89    | 0x0      | Timer/Counter Mode          | 285  |

| TMR2CN   | 0xC8    | 0x0      | Timer/Counter 2 Control     | 291  |

| TMR2H    | 0xCD    | 0x0      | Timer/Counter 2 High        | 293  |

| TMR2L    | 0xCC    | 0x0      | Timer/Counter 2 Low         | 293  |

| TMR2RLH  | 0xCB    | 0x0      | Timer/Counter 2 Reload High | 292  |

| TMR2RLL  | 0xCA    | 0x0      | Timer/Counter 2 Reload Low  | 292  |

| TMR3CN   | 0x91    | 0x0      | Timer/Counter 3 Control     | 297  |

| TMR3H    | 0x95    | 0x0      | Timer/Counter 3 High        | 299  |

| TMR3L    | 0x94    | 0x0      | Timer/Counter 3 Low         | 299  |

| TMR3RLH  | 0x93    | 0x0      | Timer/Counter 3 Reload High | 298  |

| TMR3RLL  | 0x92    | 0x0      | Timer/Counter 3 Reload Low  | 298  |

| TOFFH    | 0x8E    | 0xF      | Temperature Offset High     | 87   |

| TOFFL    | 0x8D    | 0xF      | Temperature Offset Low      | 87   |

| VDM0CN   | 0xFF    | 0x0      | VDD Monitor Control         | 184  |

| XBR0     | 0xE1    | 0x0      | Port I/O Crossbar Control 0 | 222  |

| XBR1     | 0xE2    | 0x0      | Port I/O Crossbar Control 1 | 223  |

| XBR2     | 0xE3    | 0x0      | Port I/O Crossbar Control 2 | 224  |

## Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

## 14.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

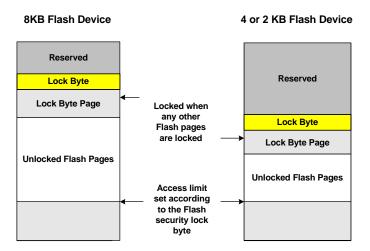

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. See **Section "10. Memory Organization" on page 128** for the location of the security byte. The Flash security mechanism allows the user to lock *n* 512-byte Flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where *n* is the 1s complement number represented by the Security Lock Byte. **The page containing the Flash Security Lock Byte is unlocked when no other Flash pages are locked (all bits of the Lock Byte are 1) and locked when any other Flash pages are locked (any bit of the Lock Byte is 0).**

| Security Lock Byte: | 1111 1011b                                  |

|---------------------|---------------------------------------------|

| ones Complement:    | 0000 0100b                                  |

| Flash pages locked: | 5 (First four Flash pages + Lock Byte Page) |

Figure 14.1. Flash Program Memory Map (8 kB and smaller devices)

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 14.1 summarizes the Flash security features of the C8051F99x-C8051F98x devices.

## SFR Definition 14.3. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

| Name  |   |   |   |   |   |   | PSEE | PSWE |

| Туре  | R | R | R | R | R | R | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

## SFR Page =All; SFR Address = 0x8F

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1   | PSEE   | Program Store Erase Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit (in combination with PSWE) allows an entire page of Flash program memory to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> <li>1: Flash program memory erasure enabled.</li> </ul> |

| 0   | PSWE   | Program Store Write Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul>                                                                                                                                                     |

## SFR Definition 19.3. OSCICL: Internal Oscillator Calibration

| Bit   | 7   | 6      | 5      | 4      | 3           | 2      | 1      | 0      |

|-------|-----|--------|--------|--------|-------------|--------|--------|--------|

| Name  | SSE |        |        |        | OSCICL[6:0] |        |        |        |

| Туре  | R/W | R/W    | R/W    | R/W    | R/W         | R/W    | R/W    | R/W    |

| Reset | 0   | Varies | Varies | Varies | Varies      | Varies | Varies | Varies |

SFR Page = 0x0; SFR Address = 0xB3

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                    | Name   | Function                                                                                                                                                                                                                                                                                                                      |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                      | SSE    | Spread Spectrum Enable.                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 0: Spread Spectrum clock dithering disabled.                                                                                                                                                                                                                                                                                  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 1: Spread Spectrum clock dithering enabled.                                                                                                                                                                                                                                                                                   |  |  |  |

| 6:0                                                                                                                                                                                                                                                                                                                                                                                                                                    | OSCICL | Internal Oscillator Calibration.                                                                                                                                                                                                                                                                                              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | Factory calibrated to obtain a frequency of 24.5 MHz. Incrementing this register decreases the oscillator frequency and decrementing this register increases the oscillator frequency. The step size is approximately 1% of the calibrated frequency. The recommended calibration frequency range is between 16 and 24.5 MHz. |  |  |  |

| <ul> <li>Note: If the Precision Internal Oscillator is selected as the system clock, the following procedure should be used when changing the value of the internal oscillator calibration bits.</li> <li>1. Switch to a different clock source.</li> <li>2. Disable the oscillator by writing OSCICN.7 to 0.</li> <li>3. Change OSCICL to the desired setting.</li> <li>4. Enable the oscillator by writing OSCICN.7 to 1.</li> </ul> |        |                                                                                                                                                                                                                                                                                                                               |  |  |  |

## 20.1.5. RTC0ADR Autoincrement Feature

For ease of reading and writing the 32-bit CAPTURE and ALARM values, RTC0ADR automatically increments after each read or write to a CAPTUREn or ALARMn register. This speeds up the process of setting an alarm or reading the current SmaRTClock timer value. Autoincrement is always enabled.

Recommended Instruction Timing for a multi-byte register read with short strobe and auto read enabled:

Recommended Instruction Timing for a multi-byte register write with short strobe enabled:

mov RTCOADR, #010h mov RTCODAT, #05h nop mov RTCODAT, #06h nop mov RTCODAT, #07h nop mov RTCODAT, #08h nop

## 20.2.4. Programmable Load Capacitance

The programmable load capacitance has 16 values to support crystal oscillators with a wide range of recommended load capacitance. If Automatic Load Capacitance Stepping is enabled, the crystal load capacitors start at the smallest setting to allow a fast startup time, then slowly increase the capacitance until the final programmed value is reached. The final programmed loading capacitor value is specified using the LOADCAP bits in the RTC0XCF register. The LOADCAP setting specifies the amount of on-chip load capacitance and does not include any stray PCB capacitance. Once the final programmed loading capacitor value is reached, the LOADRDY flag will be set by hardware to logic 1.

When using the SmaRTClock oscillator in Self-Oscillate mode, the programmable load capacitance can be used to fine tune the oscillation frequency. In most cases, increasing the load capacitor value will result in a decrease in oscillation frequency. Table 20.2 shows the crystal load capacitance for various settings of LOADCAP.

| LOADCAP | Crystal Load Capacitance | Equivalent Capacitance seen on XTAL3 and XTAL4 |

|---------|--------------------------|------------------------------------------------|

| 0000    | 4.0 pF                   | 8.0 pF                                         |

| 0001    | 4.5 pF                   | 9.0 pF                                         |

| 0010    | 5.0 pF                   | 10.0 pF                                        |

| 0011    | 5.5 pF                   | 11.0 pF                                        |

| 0100    | 6.0 pF                   | 12.0 pF                                        |

| 0101    | 6.5 pF                   | 13.0 pF                                        |

| 0110    | 7.0 pF                   | 14.0 pF                                        |

| 0111    | 7.5 pF                   | 15.0 pF                                        |

| 1000    | 8.0 pF                   | 16.0 pF                                        |

| 1001    | 8.5 pF                   | 17.0 pF                                        |

| 1010    | 9.0 pF                   | 18.0 pF                                        |

| 1011    | 9.5 pF                   | 19.0 pF                                        |

| 1100    | 10.5 pF                  | 21.0 pF                                        |

| 1101    | 11.5 pF                  | 23.0 pF                                        |

| 1110    | 12.5 pF                  | 25.0 pF                                        |

| 1111    | 13.5 pF                  | 27.0 pF                                        |

## Table 20.2. SmaRTClock Load Capacitance Settings

## 20.3.2. Setting a SmaRTClock Alarm

The SmaRTClock alarm function compares the 32-bit value of SmaRTClock Timer to the value of the ALARMn registers. An alarm event is triggered if the SmaRTClock timer is **equal to** the ALARMn registers. If Auto Reset is enabled, the 32-bit timer will be cleared to zero one SmaRTClock cycle after the alarm event.

The SmaRTClock alarm event can be configured to reset the MCU, wake it up from a low power mode, or generate an interrupt. See Section "13. Interrupt Handler" on page 138, Section "15. Power Management" on page 162, and Section "18. Reset Sources" on page 181 for more information.

The following steps can be used to set up a SmaRTClock Alarm:

- 1. Disable SmaRTClock Alarm Events (RTC0AEN = 0).

- 2. Set the ALARMn registers to the desired value.

- 3. Enable SmaRTClock Alarm Events (RTC0AEN = 1).

#### Notes:

- 1. The ALRM bit, which is used as the SmaRTClock Alarm Event flag, is cleared by disabling SmaRTClock Alarm Events (RTC0AEN = 0).

- If AutoReset is disabled, disabling (RTC0AEN = 0) then Re-enabling Alarm Events (RTC0AEN = 1) after a SmaRTClock Alarm without modifying ALARMn registers will automatically schedule the next alarm after 2^32 SmaRTClock cycles (approximately 36 hours using a 32.768 kHz crystal).

- 3. The SmaRTClock Alarm Event flag will remain asserted for a maximum of one SmaRTClock cycle. See Section "15. Power Management" on page 162 for information on how to capture a SmaRTClock Alarm event using a flag which is not automatically cleared by hardware.

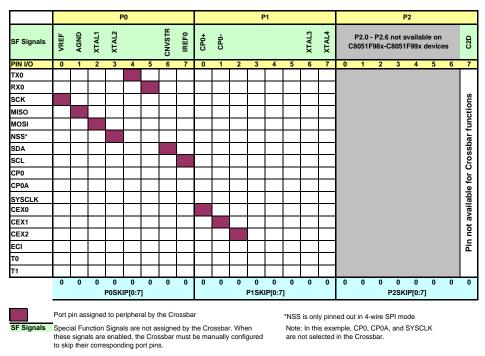

Figure 21.4. Crossbar Priority Decoder in Example Configuration (No Pins Skipped)

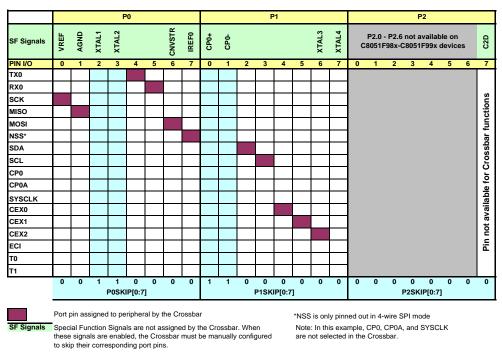

Figure 21.5. Crossbar Priority Decoder in Example Configuration (4 Pins Skipped)

## SFR Definition 21.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7   | 6   | 5   | 4   | 3    | 2           | 1   | 0   |  |  |  |  |

|-------|-----|-----|-----|-----|------|-------------|-----|-----|--|--|--|--|

| Name  |     |     | T1E | T0E | ECIE | PCA0ME[2:0] |     |     |  |  |  |  |

| Туре  | R/W | R/W | R/W | R/W | R/W  | R/W         | R/W | R/W |  |  |  |  |

| Reset | 0   | 0   | 0   | 0   | 0    | 0           | 0   | 0   |  |  |  |  |

## SFR Page = 0x0; SFR Address = 0xE2

| Bit | Name   | Function                                                |  |  |  |

|-----|--------|---------------------------------------------------------|--|--|--|

| 7:6 | Unused | Read = 00b; Write = Don't Care.                         |  |  |  |

| 5   | T1E    | limer1 Input Enable.                                    |  |  |  |

|     |        | 0: T1 input unavailable at Port pin.                    |  |  |  |

|     |        | 1: T1 input routed to Port pin.                         |  |  |  |

| 4   | T0E    | Timer0 Input Enable.                                    |  |  |  |

|     |        | 0: T0 input unavailable at Port pin.                    |  |  |  |

|     |        | 1: T0 input routed to Port pin.                         |  |  |  |

| 3   | ECIE   | PCA0 External Counter Input (ECI) Enable.               |  |  |  |

|     |        | 0: PCA0 external counter input unavailable at Port pin. |  |  |  |

|     |        | 1: PCA0 external counter input routed to Port pin.      |  |  |  |

| 2:0 | PCA0ME | PCA0 Module I/O Enable.                                 |  |  |  |

|     |        | 000: All PCA0 I/O unavailable at Port pin.              |  |  |  |

|     |        | 001: CEX0 routed to Port pin.                           |  |  |  |

|     |        | 010: CEX0, CEX1 routed to Port pins.                    |  |  |  |

|     |        | 011: CEX0, CEX1, CEX2 routed to Port pins.              |  |  |  |

|     |        | 100: Reserved.                                          |  |  |  |

|     |        | 101: Reserved.<br>110: Reserved.                        |  |  |  |

|     |        | 111: Reserved.                                          |  |  |  |

|     |        |                                                         |  |  |  |

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 22.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                                                                   | Minimum SDA Setup Time             | Minimum SDA Hold Time |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                           | T <sub>low</sub> – 4 system clocks |                       |  |  |  |  |  |  |

| 0                                                                                                                                                                                                                                                                                                                         | or                                 | 3 system clocks       |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                           | 1 system clock + s/w delay*        |                       |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                         | 11 system clocks                   | 12 system clocks      |  |  |  |  |  |  |

| *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When<br>using software acknowledgement, the s/w delay occurs between the time SMB0DAT<br>or ACK is written and when SI is cleared. Note that if SI is cleared in the same write<br>that defines the outgoing ACK value, s/w delay is zero. |                                    |                       |  |  |  |  |  |  |

Table 22.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "22.3.4. SCL Low Timeout" on page 238). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 22.4).

## 23.1. Enhanced Baud Rate Generation

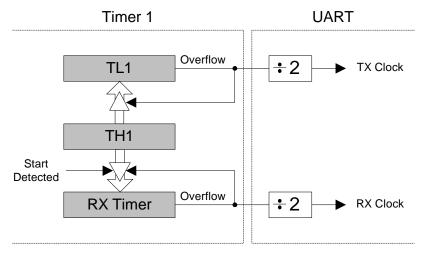

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 23.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 23.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 282). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, the external oscillator clock / 8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 23.1-A and Equation 23.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

## Equation 23.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "25.1. Timer 0 and Timer 1" on page 280. A quick reference for typical baud rates and system clock frequencies is given in Table 23.1 through Table 23.2. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

## 23.2. Operational Modes

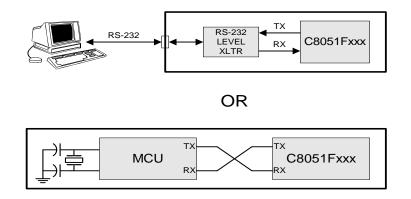

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown below.

Figure 23.3. UART Interconnect Diagram

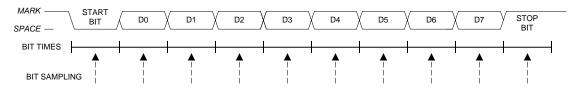

## 23.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 23.4. 8-Bit UART Timing Diagram

## SFR Definition 24.2. SPI0CN: SPI0 Control

| Bit   | 7    | 6    | 5    | 4      | 3    | 2       | 1     | 0     |   |   |

|-------|------|------|------|--------|------|---------|-------|-------|---|---|

| Name  | SPIF | WCOL | MODF | RXOVRN | NSSM | ID[1:0] | TXBMT | SPIEN |   |   |

| Туре  | R/W  | R/W  | R/W  | R/W    | R/   | W       | R     | R/W   |   |   |

| Reset | 0    | 0    | 0    | 0      | 0 1  |         | 0 1   |       | 1 | 0 |

## SFR Page = 0x0; SFR Address = 0xF8; Bit-Addressable

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF       | SPI0 Interrupt Flag.                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit is set to logic 1 by hardware at the end of a data transfer. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                                                                                     |

| 6   | WCOL       | Write Collision Flag.                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | This bit is set to logic 1 if a write to SPI0DAT is attempted when TXBMT is 0. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                       |

| 5   | MODF       | Mode Fault Flag.                                                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01). If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                             |

| 4   | RXOVRN     | Receive Overrun Flag (valid in slave mode only).                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI0 shift register. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                         |

| 3:2 | NSSMD[1:0] | Slave Select Mode.                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | Selects between the following NSS operation modes:<br>(See Section 24.2 and Section 24.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |

| 1   | TXBMT      | Transmit Buffer Empty.                                                                                                                                                                                                                                                                                                                                                                       |

|     |            | This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer.                                                                                                              |

| 0   | SPIEN      | SPI0 Enable.                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | 0: SPI disabled.<br>1: SPI enabled.                                                                                                                                                                                                                                                                                                                                                          |

## SFR Definition 25.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1           | 0 |  |  |

|-------|------|------|--------|--------|---------|-----|-------------|---|--|--|

| Name  | TF3H | TF3L | TF3LEN | TF3CEN | T3SPLIT | TR3 | T3XCLK[1:0] |   |  |  |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R/W         |   |  |  |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0           | 0 |  |  |

### SFR Page = 0x0; SFR Address = 0x91

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF3H        | Timer 3 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |             | Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6   | TF3L        | Timer 3 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |             | Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5   | TF3LEN      | Timer 3 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |             | When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | TF3CEN      | Timer 3 SmaRTClock/External Oscillator Capture Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |             | When set to 1, this bit enables Timer 3 Capture Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | T3SPLIT     | Timer 3 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |             | When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |             | 0: Timer 3 operates in 16-bit auto-reload mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |             | 1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2   | TR3         | Timer 3 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |             | Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1:0 | T3XCLK[1:0] | Timer 3 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |             | This bit selects the "external" and "capture trigger" clock sources for Timer 3. If<br>Timer 3 is in 8-bit mode, this bit selects the "external" clock source for both timer<br>bytes. Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be<br>used to select between the "external" clock and the system clock for either timer.<br>Note: External clock sources are synchronized with the system clock.<br>00: External Clock is SYSCLK /12. Capture trigger is SmaRTClock.<br>01: External Clock is External Oscillator/8. Capture trigger is SmaRTClock.<br>10: External Clock is SYSCLK/12. Capture trigger is External Oscillator/8.<br>11: External Clock is SmaRTClock. Capture trigger is External Oscillator/8. |

## 26.3. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: edge-triggered capture, software timer, high-speed output, frequency output, 8 to 11-bit pulse width modulator, or 16-bit pulse width modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation. Table 26.2 summarizes the bit settings in the PCA0CPMn and PCA0PWM registers used to select the PCA capture/compare module's operating mode. Note that all modules set to use 8, 9, 10, or 11-bit PWM mode must use the same cycle length (8–11 bits). Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt.

| Operational Mode                            | Γ |   | PC | :A0 | СР | Mn |   |   |   | Ρ | CA | 0PWN | 1   |

|---------------------------------------------|---|---|----|-----|----|----|---|---|---|---|----|------|-----|

| Bit Number                                  | 7 | 6 | 5  | 4   | 3  | 2  | 1 | 0 | 7 | 6 | 5  | 4–2  | 1–0 |

| Capture triggered by positive edge on CEXn  | Х | Х | 1  | 0   | 0  | 0  | 0 | А | 0 | Х | В  | XXX  | XX  |

| Capture triggered by negative edge on CEXn  | Х | Х | 0  | 1   | 0  | 0  | 0 | А | 0 | Х | В  | XXX  | XX  |

| Capture triggered by any transition on CEXn | Х | Х | 1  | 1   | 0  | 0  | 0 | А | 0 | Х | В  | XXX  | XX  |

| Software Timer                              | Х | С | 0  | 0   | 1  | 0  | 0 | А | 0 | Х | В  | XXX  | XX  |

| High Speed Output                           | Х | С | 0  | 0   | 1  | 1  | 0 | А | 0 | Х | В  | XXX  | XX  |

| Frequency Output                            | Х | С | 0  | 0   | 0  | 1  | 1 | А | 0 | Х | В  | XXX  | XX  |

| 8-Bit Pulse Width Modulator (Note 7)        | 0 | С | 0  | 0   | Е  | 0  | 1 | А | 0 | Х | В  | XXX  | 00  |

| 9-Bit Pulse Width Modulator (Note 7)        | 0 | С | 0  | 0   | Е  | 0  | 1 | А | D | Х | В  | XXX  | 01  |

| 10-Bit Pulse Width Modulator (Note 7)       | 0 | С | 0  | 0   | Е  | 0  | 1 | А | D | Х | В  | XXX  | 10  |

| 11-Bit Pulse Width Modulator (Note 7)       | 0 | С | 0  | 0   | Е  | 0  | 1 | А | D | Х | В  | XXX  | 11  |

| 16-Bit Pulse Width Modulator                | 1 | С | 0  | 0   | Е  | 0  | 1 | А | 0 | Х | В  | XXX  | XX  |

| Notes:                                      | - | • | -  | -   | -  |    | - | · |   |   |    |      |     |

### Table 26.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules

**1.** X = Don't Care (no functional difference for individual module if 1 or 0).

2. A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

3. B = Enable 8th, 9th, 10th or 11th bit overflow interrupt (Depends on setting of CLSEL[1:0]).

**4.** C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

5. D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated channel is accessed via addresses PCA0CPHn and PCA0CPLn.

6. E = When set, a match event will cause the CCFn flag for the associated channel to be set.

7. All modules set to 8, 9, 10 or 11-bit PWM mode use the same cycle length setting.

## SFR Definition 26.2. PCA0MD: PCA Mode

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                                                                                                                                                                                       | 4                           | 3    | 2    | 1               | 0        |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|------|-----------------|----------|--|--|--|--|--|

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e CIDL                             | WDTE                                                                                                                                                                                                                                                                                                                                                                                                                                                         | WDLCK                                                                                                                                                                                                                                                   |                             | CPS2 | CPS1 | CPS0            | ECF      |  |  |  |  |  |

| Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W                                | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W R/W R R/W R/W R/W                                                                                                                                                                                                                                   |                             |      |      |                 |          |  |  |  |  |  |

| Reset         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th>0</th> |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                         |                             |      |      |                 | 0        |  |  |  |  |  |