Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                     |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, POR, PWM, Temp Sensor, WDT   |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 10x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                            |

| Supplier Device Package    | 24-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f996-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                | Pin                                    | Number                                 | S                                    |                  |                                                                                                                                              |

|----------------|----------------------------------------|----------------------------------------|--------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Name           | 'F980/1/2<br>'F983/5<br>'F990/1<br>-GM | <pre>'F986/7 'F988/9 'F996/7 -GM</pre> | 'F986/7<br>'F988/9<br>'F996/7<br>-GU | Туре             | Description                                                                                                                                  |

| P0.1/          | 1                                      | 23                                     | 2                                    | D I/O or<br>A In | Port 0.1. See Port I/O Section for a complete description.                                                                                   |

| AGND*          |                                        |                                        |                                      | G                | Optional Analog Ground. See Section "5.9. Voltage and Ground Reference Options" on page 88.                                                  |

| P0.2/          | 20                                     | 22                                     | 1                                    | D I/O or<br>A In | Port 0.2. See Port I/O Section for a complete description.                                                                                   |

| XTAL1/         |                                        |                                        |                                      | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator. See Section "19. Clocking Sources" on page 188. |

| RTCOUT         |                                        |                                        |                                      | D Out            | Buffered SmaRTClock oscillator output.                                                                                                       |

| P0.3/          | 19                                     | 21                                     | 24                                   | D I/O or<br>A In | Port 0.3. See Section "21. Port Input/Output" on page 215 for a complete description.                                                        |

| XTAL2/         |                                        |                                        |                                      | A Out            | External Clock Output. This pin is the excitation driver for an external crystal or resonator.                                               |

|                |                                        |                                        |                                      | D In             | External Clock Input. This pin is the external clock input in external CMOS clock mode.                                                      |

|                |                                        |                                        |                                      | A In             | External Clock Input. This pin is the external clock input in capacitor or RC oscillator configurations.                                     |

|                |                                        |                                        |                                      |                  | See Section "19. Clocking Sources" on page 188 for<br>complete details.                                                                      |

| WAKEOUT        |                                        |                                        |                                      | D Out            | Wake-up request signal to wake up external devices.                                                                                          |

| P0.4/          | 18                                     | 20                                     | 23                                   | D I/O or<br>A In | Port 0.4. See Section "21. Port Input/Output" on page 215 for a complete description.                                                        |

| ТХ             |                                        |                                        |                                      | D Out            | UART TX Pin. See Section "21. Port Input/Output" on page 215.                                                                                |

| P0.5/          | 17                                     | 19                                     | 22                                   | D I/O or<br>A In | Port 0.5. See Section "21. Port Input/Output" on page 215 for a complete description.                                                        |

| RX             |                                        |                                        |                                      | D In             | UART RX Pin. See Section "21. Port Input/Output" on page 215.                                                                                |

| *Note: Availal | ble only on t                          | he C805 <sup>-</sup>                   | 1F980/2/6                            | 6/8 and C80      | 051F990/6 devices.                                                                                                                           |

## Table 3.1. Pin Definitions for the C8051F99x-C8051F98x (Continued)

## C8051F99x-C8051F98x

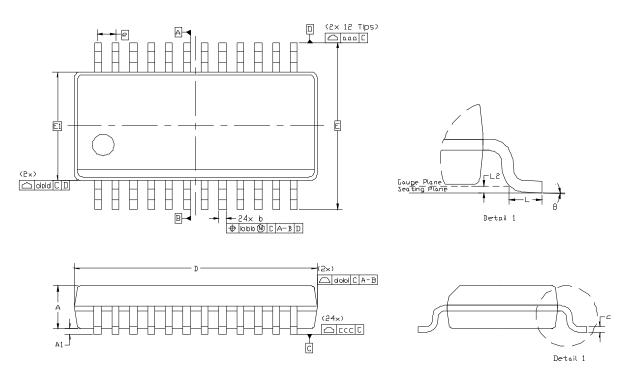

Figure 3.11. QSOP-24 Package Diagram

| Table | 3.6. | QSOP-24 | Package  | Dimensions |

|-------|------|---------|----------|------------|

| Table | 5.0. |         | I denage | Dimensions |

| Dimension | Min       | Тур       | Max  |  | Dimension | Min      | Тур  | Мах  |

|-----------|-----------|-----------|------|--|-----------|----------|------|------|

| A         | _         | —         | 1.75 |  | L         | 0.40     | —    | 1.27 |

| A1        | 0.10      | —         | 0.25 |  | L2        | 0.25 BSC |      |      |

| b         | 0.20      | —         | 0.30 |  | θ         | 0°       | —    | 8°   |

| С         | 0.10      | —         | 0.25 |  | aaa       | 0.20     |      |      |

| D         |           | 8.65 BSC. |      |  | bbb       |          | 0.18 |      |

| E         | 6.00 BSC  |           |      |  | CCC       |          | 0.10 |      |

| E1        | 3.90 BSC  |           |      |  | ddd       |          | 0.10 |      |

| е         | 0.635 BSC |           |      |  |           |          |      |      |

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MO-147, variation AE.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

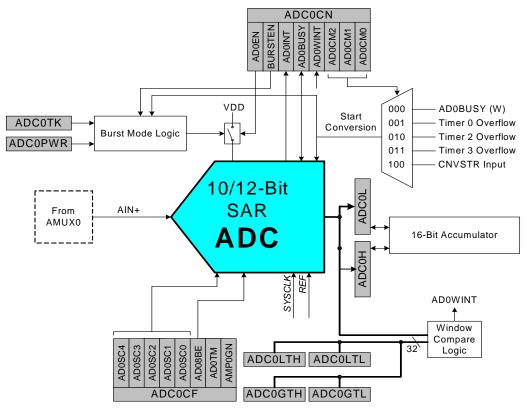

# 5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

The ADC0 on C8051F980/6 and C8051F990/6 devices is a 300 ksps, 10-bit or 75 ksps, 12-bit successiveapproximation-register (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically oversample and average the ADC results. See Section 5.4 for more details on using the ADC in 12-bit mode. C8051F982 and C8051F988 devices only support the 10-bit mode.

The ADC is fully configurable under software control via Special Function Registers. The ADC0 operates in Single-ended mode and may be configured to measure various different signals using the analog multiplexer described in "5.7. ADC0 Analog Multiplexer" on page 83. The voltage reference for the ADC is selected as described in "5.9. Voltage and Ground Reference Options" on page 88.

Figure 5.1. ADC0 Functional Block Diagram

## SFR Definition 5.2. ADC0CF: ADC0 Configuration

| Bit   | 7               | 6                                                                                              | 5                                                                                                              | 4                                                               | 3                                              | 2                                                          | 1           | 0        |  |  |  |

|-------|-----------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------|-------------|----------|--|--|--|

| Nam   | e               |                                                                                                | AD0SC[4:0]                                                                                                     |                                                                 |                                                | AD08BE                                                     | AD0TM       | AMP0GN   |  |  |  |

| Туре  | •               | R/W R/W                                                                                        |                                                                                                                |                                                                 |                                                |                                                            |             |          |  |  |  |

| Rese  | t 1             | 1                                                                                              | 1                                                                                                              | 1                                                               | 1                                              | 0                                                          | 0           | 0        |  |  |  |

| SFR F | age = 0x0; SI   | ; SFR Address = 0x97                                                                           |                                                                                                                |                                                                 |                                                |                                                            |             |          |  |  |  |

| Bit   | Name            |                                                                                                |                                                                                                                |                                                                 | Functior                                       | 1                                                          |             |          |  |  |  |

| 7:3   | AD0SC[4:0]      | SAR Conve<br>AD0SC refe<br>requiremen<br>BURSTEN<br>BURSTEN<br>clock.<br>AD0SC =<br>*Round the | ersion clock i<br>ers to the 5-t<br>ts are given<br>= 0: FCLK is<br>= 1: FCLK is<br>= $\frac{FCLK}{CLK_{SAR}}$ | bit value held<br>in Table 4.1<br>s the current<br>s the 20 MHz | om FCLK by<br>d in bits AD<br>0.<br>system clo | / the following<br>DSC[4:0]. SAF<br>ck.<br>oscillator, ind | R Conversio | n clock  |  |  |  |

| 2     | AD08BE          | 0: ADC0 op                                                                                     | t <b>Mode Ena</b> l<br>erates in 10<br>erates in 8-l                                                           | -bit mode (n                                                    | ormal opera                                    | ation).                                                    |             |          |  |  |  |

| 1     | AD0TM<br>AMP0GN | 0: Normal T<br>lowing the s<br>1: Delayed                                                      | ween Norma<br>rack Mode:<br>start-of-conv<br>Track Mode<br>wing the sta                                        | ersion signa<br>: When ADC                                      | ) is enablec<br>I.<br>:0 is enable             | Nodes.<br>I, conversion I<br>d, conversion<br>The ADC is a | begins 3 S/ | AR clock |  |  |  |

|       |                 | 0: The on-c                                                                                    | hip PGA gai<br>hip PGA gai                                                                                     |                                                                 |                                                |                                                            |             |          |  |  |  |

## C8051F99x-C8051F98x

## SFR Definition 7.2. CPT0MD: Comparator 0 Mode Selection

| Bit   | 7   | 6 | 5      | 4      | 3 | 2 | 1          | 0 |

|-------|-----|---|--------|--------|---|---|------------|---|

| Name  |     |   | CP0RIE | CP0FIE |   |   | CP0MD[1:0] |   |

| Туре  | R/W | R | R/W    | R/W    | R | R | R/W        |   |

| Reset | 1   | 0 | 0      | 0      | 0 | 0 | 1          | 0 |

## SFR Page = 0x0; SFR Address = 0x9D

| Bit | Name       | Function                                                                                                                                                                                                                                                           |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved   | Read = 1b, Must Write 1b.                                                                                                                                                                                                                                          |

| 6   | Unused     | Read = 0b, Write = don't care.                                                                                                                                                                                                                                     |

| 5   | CPORIE     | Comparator0 Rising-Edge Interrupt Enable.<br>0: Comparator0 Rising-edge interrupt disabled.<br>1: Comparator0 Rising-edge interrupt enabled.                                                                                                                       |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.<br>0: Comparator0 Falling-edge interrupt disabled.<br>1: Comparator0 Falling-edge interrupt enabled.                                                                                                                    |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                    |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

## SFR Definition 9.3. SP: Stack Pointer

| Bit     | 7             | 6               | 5    | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|---------|---------------|-----------------|------|---|---|---|---|---|--|--|--|--|

| Name    |               | SP[7:0]         |      |   |   |   |   |   |  |  |  |  |

| Туре    |               | R/W             |      |   |   |   |   |   |  |  |  |  |

| Reset   | 0             | 0 0 0 0 0 1 1 1 |      |   |   |   |   |   |  |  |  |  |

| SFR Pag | ge = All; SFF | R Address =     | 0x81 |   |   |   |   |   |  |  |  |  |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

## SFR Definition 9.4. ACC: Accumulator

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|---|---|---|---|---|--|

| Name  |   | ACC[7:0]        |   |   |   |   |   |   |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |

|       |   |                 |   |   |   |   |   |   |  |

SFR Page = All; SFR Address = 0xE0; Bit-Addressable

| Bit | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

## SFR Definition 9.5. B: B Register

| Bit   | 7               | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|-----------------|--------|---|---|---|---|---|---|--|--|--|

| Name  |                 | B[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  |                 | R/W    |   |   |   |   |   |   |  |  |  |

| Reset | 0 0 0 0 0 0 0 0 |        |   |   |   |   |   |   |  |  |  |

SFR Page = All; SFR Address = 0xF0; Bit-Addressable

| Bit | Name   | Function                                                                        |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

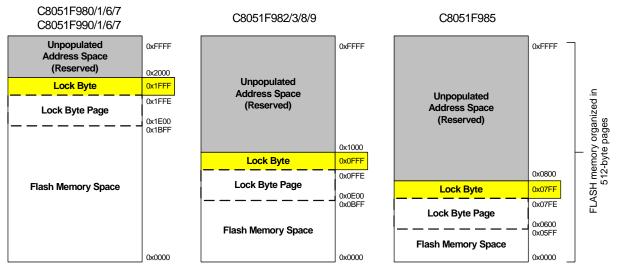

### 10.1. Program Memory

The CIP-51 core has a 64 kB program memory space. The C8051F99x-C8051F98x devices implement 8 kB (C8051F980/1/6/7, C8051F990/1/6/7), 4 kB (C8051F982/3/8/9), or 2 kB (C8051F985) of this program memory space as in-system, re-programmable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x1FFF (8 kB devices), 0x0FFF (4 kB devices), or 0x07FF (2 kB devices). The last byte of this contiguous block of addresses serves as the security lock byte for the device. Any addresses above the lock byte are reserved.

Figure 10.2. Flash Program Memory Map

#### **10.1.1. MOVX Instruction and Program Memory**

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F99x-C8051F98x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access feature provides a mechanism for the C8051F99x-C8051F98x to update program code and use the program memory space for non-volatile data storage. Refer to Section "14. Flash Memory" on page 150 for further details.

#### 10.2. Data Memory

The C8051F99x-C8051F98x device family include 512 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. The remainder of this memory is on-chip "external" memory. The data memory map is shown in Figure 10.1 for reference.

#### 10.2.1. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR

## C8051F99x-C8051F98x

space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 10.1 illustrates the data memory organization of the C8051F99x-C8051F98x.

#### 10.2.1.1.General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 9.6). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 10.2.1.2.Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 10.2.1.3.Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

#### 10.2.2. External RAM

There are 256 bytes of on-chip RAM mapped into the external data memory space. All of these address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using MOVX indirect addressing mode (such as @R1).

#### Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register | Address | SFR Page | Description                       | Page |

|----------|---------|----------|-----------------------------------|------|

| P1SKIP   | 0xD5    | 0x0      | Port 1 Skip                       | 231  |

| P2       | 0xA0    | All      | Port 2 Latch                      | 233  |

| P2DRV    | 0x9D    | 0xF      | Port 2 Drive Strength             | 234  |

| P2MDOUT  | 0xA6    | 0x0      | Port 2 Output Mode Configuration  | 234  |

| PCA0CN   | 0xD8    | 0x0      | PCA0 Control                      | 313  |

| PCA0CPH0 | 0xFC    | 0x0      | PCA0 Capture 0 High               | 318  |

| PCA0CPH1 | 0xEA    | 0x0      | PCA0 Capture 1 High               | 318  |

| PCA0CPH2 | 0xEC    | 0x0      | PCA0 Capture 2 High               | 318  |

| PCA0CPL0 | 0xFB    | 0x0      | PCA0 Capture 0 Low                | 318  |

| PCA0CPL1 | 0xE9    | 0x0      | PCA0 Capture 1 Low                | 318  |

| PCA0CPL2 | 0xEB    | 0x0      | PCA0 Capture 2 Low                | 318  |

| PCA0CPM0 | 0xDA    | 0x0      | PCA0 Module 0 Mode Register       | 316  |

| PCA0CPM1 | 0xDB    | 0x0      | PCA0 Module 1 Mode Register       | 316  |

| PCA0CPM2 | 0xDC    | 0x0      | PCA0 Module 2 Mode Register       | 316  |

| PCA0H    | 0xFA    | 0x0      | PCA0 Counter High                 | 317  |

| PCA0L    | 0xF9    | 0x0      | PCA0 Counter Low                  | 317  |

| PCA0MD   | 0xD9    | 0x0      | PCA0 Mode                         | 314  |

| PCA0PWM  | 0xDF    | 0x0      | PCA0 PWM Configuration            | 315  |

| PCON     | 0x87    | All      | Power Control                     | 171  |

| PMU0CF   | 0xB5    | 0x0      | PMU0 Configuration                | 168  |

| PMU0FL   | 0xCE    | 0x0      | PMU0 Flag Register                | 169  |

| PMU0MD   | 0xB5    | 0xF      | PMU0 Mode                         | 170  |

| PSCTL    | 0x8F    | All      | Program Store R/W Control         | 159  |

| PSW      | 0xD0    | All      | Program Status Word               | 127  |

| REF0CN   | 0xD1    | 0x0      | Voltage Reference Control         | 90   |

| REG0CN   | 0xC9    | 0x0      | Voltage Regulator (REG0) Control  | 180  |

| REVID    | 0xE2    | 0xF      | Revision ID                       | 155  |

| RSTSRC   | 0xEF    | 0x0      | Reset Source Configuration/Status | 187  |

| RTC0ADR  | 0xAC    | 0x0      | RTC0 Address                      | 202  |

| RTC0DAT  | 0xAD    | 0x0      | RTC0 Data                         | 202  |

| RTC0KEY  | 0xAE    | 0x0      | RTC0 Key                          | 201  |

| SBUF0    | 0x99    | 0x0      | UART0 Data Buffer                 | 263  |

| SCON0    | 0x98    | 0x0      | UART0 Control                     | 262  |

| SFRPAGE  | 0xA7    | All      | SFR Page                          | 134  |

| SMB0ADM  | 0xF5    | 0x0      | SMBus Slave Address Mask          | 247  |

| SMB0ADR  | 0xF4    | 0x0      | SMBus Slave Address               | 247  |

| SMB0CF   | 0xC1    | 0x0      | SMBus0 Configuration              | 242  |

| SMB0CN   | 0xC0    | 0x0      | SMBus0 Control                    | 244  |

| SMB0DAT  | 0xC2    | 0x0      | SMBus0 Data                       | 248  |

| SP       | 0x81    | All      | Stack Pointer                     | 126  |

| SPI0CFG  | 0xA1    | 0x0      | SPI0 Configuration                | 272  |

| SPI0CKR  | 0xA2    | 0x0      | SPI0 Clock Rate Control           | 274  |

| SPI0CN   | 0xF8    | 0x0      | SPI0 Control                      | 273  |

| SPI0DAT  | 0xA3    | 0x0      | SPI0 Data                         | 274  |

| Register | Address | SFR Page | Description                 | Page |

|----------|---------|----------|-----------------------------|------|

| TCON     | 0x88    | 0x0      | Timer/Counter Control       | 284  |

| TH0      | 0x8C    | 0x0      | Timer/Counter 0 High        | 287  |

| TH1      | 0x8D    | 0x0      | Timer/Counter 1 High        | 287  |

| TL0      | 0x8A    | 0x0      | Timer/Counter 0 Low         | 286  |

| TL1      | 0x8B    | 0x0      | Timer/Counter 1 Low         | 286  |

| TMOD     | 0x89    | 0x0      | Timer/Counter Mode          | 285  |

| TMR2CN   | 0xC8    | 0x0      | Timer/Counter 2 Control     | 291  |

| TMR2H    | 0xCD    | 0x0      | Timer/Counter 2 High        | 293  |

| TMR2L    | 0xCC    | 0x0      | Timer/Counter 2 Low         | 293  |

| TMR2RLH  | 0xCB    | 0x0      | Timer/Counter 2 Reload High | 292  |

| TMR2RLL  | 0xCA    | 0x0      | Timer/Counter 2 Reload Low  | 292  |

| TMR3CN   | 0x91    | 0x0      | Timer/Counter 3 Control     | 297  |

| TMR3H    | 0x95    | 0x0      | Timer/Counter 3 High        | 299  |

| TMR3L    | 0x94    | 0x0      | Timer/Counter 3 Low         | 299  |

| TMR3RLH  | 0x93    | 0x0      | Timer/Counter 3 Reload High | 298  |

| TMR3RLL  | 0x92    | 0x0      | Timer/Counter 3 Reload Low  | 298  |

| TOFFH    | 0x8E    | 0xF      | Temperature Offset High     | 87   |

| TOFFL    | 0x8D    | 0xF      | Temperature Offset Low      | 87   |

| VDM0CN   | 0xFF    | 0x0      | VDD Monitor Control         | 184  |

| XBR0     | 0xE1    | 0x0      | Port I/O Crossbar Control 0 | 222  |

| XBR1     | 0xE2    | 0x0      | Port I/O Crossbar Control 1 | 223  |

| XBR2     | 0xE3    | 0x0      | Port I/O Crossbar Control 2 | 224  |

#### Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

## SFR Definition 14.5. FLSCL: Flash Scale

| Bit   | 7 | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|--------|---|---|---|---|---|---|

| Name  |   | BYPASS |   |   |   |   |   |   |

| Туре  | R | R/W    | R | R | R | R | R | R |

| Reset | 0 | 0      | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xB6

| Bit   | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Function                                                                                                                                                                                                                                                                  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Always Write to 0.                                                                                                                                                                                                                                                        |  |  |  |  |

| 6     | BYPASS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Flash Read Timing One-Shot Bypass.                                                                                                                                                                                                                                        |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>0: The one-shot determines the Flash read time. This setting should be used for operating frequencies less than 14 MHz.</li> <li>1: The system clock determines the Flash read time. This setting should be used for frequencies greater than 14 MHz.</li> </ul> |  |  |  |  |

| 5:0   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reserved. Always Write to 000000b.                                                                                                                                                                                                                                        |  |  |  |  |

| Note: | <ul> <li>Preserved Preserved Pre</li></ul> |                                                                                                                                                                                                                                                                           |  |  |  |  |

## SFR Definition 14.6. FLWR: Flash Write Only

| Bit                  | 7              | 6                | 5                                                               | 4 | 3 | 2 | 1 | 0 |  |

|----------------------|----------------|------------------|-----------------------------------------------------------------|---|---|---|---|---|--|

| Nam                  | е              | FLWR[7:0]        |                                                                 |   |   |   |   |   |  |

| Туре                 | 9              | W                |                                                                 |   |   |   |   |   |  |

| <b>Reset</b> 0 0 0 0 |                | 0                | 0                                                               | 0 | 0 |   |   |   |  |

| SFR F                | Page = All; SF | R Address = 0    | )xE5                                                            |   |   |   |   |   |  |

| Bit                  | Name           |                  | Function                                                        |   |   |   |   |   |  |

| 7:0                  | FLWR[7:0]      | Flash Write (    | Flash Write Only.                                               |   |   |   |   |   |  |

|                      |                | All writes to th | All writes to this register have no effect on system operation. |   |   |   |   |   |  |

## SFR Definition 15.4. PCON: Power Management Control Register

| Bit   | 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |

|-------|---|---|---|------|------|---|---|---|

| Name  |   |   |   | STOP | IDLE |   |   |   |

| Туре  |   |   |   | W    | W    |   |   |   |

| Reset | 0 | 0 | 0 | 0    | 0    | 0 | 0 | 0 |

SFR Page = All; SFR Address = 0x87

| Bit | Name    | Description           | Write                                     | Read                     |

|-----|---------|-----------------------|-------------------------------------------|--------------------------|

| 7:2 | GF[5:0] | General Purpose Flags | Sets the logic value.                     | Returns the logic value. |

| 1   | STOP    | Stop Mode Select      | Writing 1 places the device in Stop Mode. | N/A                      |

| 0   | IDLE    | Idle Mode Select      | Writing 1 places the device in Idle Mode. | N/A                      |

## 15.8. Power Management Specifications

See Table 4.5 on page 58 for detailed Power Management Specifications.

## SFR Definition 16.1. CRC0CN: CRC0 Control

| Bit   | 7 | 6 | 5 | 4 | 3        | 2       | 1 | 0       |

|-------|---|---|---|---|----------|---------|---|---------|

| Name  |   |   |   |   | CRC0INIT | CRC0VAL |   | CRC0PNT |

| Туре  | R | R | R | R | R/W      | R/W     | R | R/W     |

| Reset | 0 | 0 | 0 | 1 | 0        | 0       | 0 | 0       |

#### SFR Page = All; SFR Address = 0x84

| Bit   | Name                                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4   | Unused                                                    | Read = 0001b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                              |

| 3     | CRC0INIT                                                  | CRC0 Result Initialization Bit.                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                           | Writing a 1 to this bit initializes the entire CRC result based on CRC0VAL.                                                                                                                                                                                                                                                                                                                                    |

| 2     | CRC0VAL                                                   | CRC0 Set Value Initialization Bit.                                                                                                                                                                                                                                                                                                                                                                             |

|       |                                                           | This bit selects the set value of the CRC result.                                                                                                                                                                                                                                                                                                                                                              |

|       |                                                           | 0: CRC result is set to 0x00000000 on write of 1 to CRC0INIT.                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                           | 1: CRC result is set to 0xFFFFFFF on write of 1 to CRC0INIT.                                                                                                                                                                                                                                                                                                                                                   |

| 1     | Unused                                                    | Read = 0b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                 |

| 0     | CRC0PNT                                                   | CRC0 Result Pointer.                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                           | Specifies the byte of the CRC result to be read/written on the next access to                                                                                                                                                                                                                                                                                                                                  |

|       |                                                           | CRC0DAT. The value of these bits will auto-increment upon each read or write.                                                                                                                                                                                                                                                                                                                                  |

|       |                                                           | 0: CRC0DAT accesses bits 7–0 of the 16-bit CRC result.                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                           | 1: CRC0DAT accesses bits 15–8 of the 16-bit CRC result.                                                                                                                                                                                                                                                                                                                                                        |

| Note: | CRC operation n<br>bytes in the instr<br>register. When p | f an automatic CRC calculation, the three cycles following a write to CRC0CN that initiate a nust only contain instructions which execute in the same number of cycles as the number of uction. An example of such an instruction is a 3-byte MOV that targets the CRC0FLIP rogramming in C, the dummy value written to CRC0FLIP should be a non-zero value to piler from generating a 2-byte MOV instruction. |

## SFR Definition 19.3. OSCICL: Internal Oscillator Calibration

| Bit   | 7   | 6      | 5           | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|-----|--------|-------------|--------|--------|--------|--------|--------|--|--|

| Name  | SSE |        | OSCICL[6:0] |        |        |        |        |        |  |  |

| Туре  | R/W | R/W    | R/W         | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Reset | 0   | Varies | Varies      | Varies | Varies | Varies | Varies | Varies |  |  |

SFR Page = 0x0; SFR Address = 0xB3

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | SSE    | Spread Spectrum Enable.                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|     |        | 0: Spread Spectrum clock dithering disabled.                                                                                                                                                                                                                                                                                  |  |  |  |  |

|     |        | 1: Spread Spectrum clock dithering enabled.                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 6:0 | OSCICL | Internal Oscillator Calibration.                                                                                                                                                                                                                                                                                              |  |  |  |  |

|     |        | Factory calibrated to obtain a frequency of 24.5 MHz. Incrementing this register decreases the oscillator frequency and decrementing this register increases the oscillator frequency. The step size is approximately 1% of the calibrated frequency. The recommended calibration frequency range is between 16 and 24.5 MHz. |  |  |  |  |

|     |        |                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

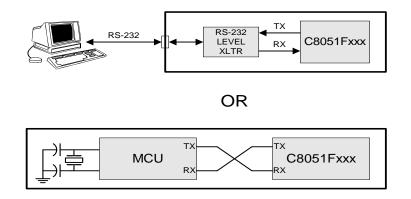

## 23.2. Operational Modes

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown below.

Figure 23.3. UART Interconnect Diagram

#### 23.2.1. 8-Bit UART

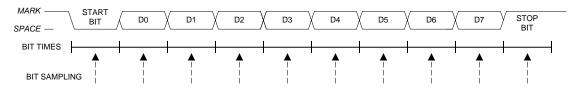

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 23.4. 8-Bit UART Timing Diagram

|                                                                            | Frequency: 24.5 MHz          |                      |                                  |                       |                                                 |                  |                                  |  |

|----------------------------------------------------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|

|                                                                            | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |

|                                                                            | 230400                       | -0.32%               | 106                              | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |  |

|                                                                            | 115200                       | -0.32%               | 212                              | SYSCLK                | XX                                              | 1                | 0x96                             |  |

|                                                                            | 57600                        | 0.15%                | 426                              | SYSCLK                | XX                                              | 1                | 0x2B                             |  |

| E                                                                          | 28800                        | -0.32%               | 848                              | SYSCLK/4              | 01                                              | 0                | 0x96                             |  |

| C fr                                                                       | 14400                        | 0.15%                | 1704                             | SYSCLK/12             | 00                                              | 0                | 0xB9                             |  |

| 2Lk<br>al                                                                  | 9600                         | -0.32%               | 2544                             | SYSCLK/12             | 00                                              | 0                | 0x96                             |  |

| SC<br>ern                                                                  | 2400                         | -0.32%               | 10176                            | SYSCLK/48             | 10                                              | 0                | 0x96                             |  |

| SYSCLK from<br>Internal Osc.                                               | 1200                         | 0.15%                | 20448                            | SYSCLK/48             | 10                                              | 0                | 0x2B                             |  |

| Notes:<br>1 SCA1–SCA0 and T1M bit definitions can be found in Section 25.1 |                              |                      |                                  |                       |                                                 |                  |                                  |  |

#### Table 23.1. Timer Settings for Standard Baud Rates Using The Internal 24.5 MHz Oscillator

SCA1–SCA0 and T1M bit definitions can be found in Section 25.1.

2. X = Don't care.

#### Table 23.2. Timer Settings for Standard Baud Rates Using an External 22.1184 MHz Oscillator

|                        | Frequency: 22.1184 MHz       |                      |                                  |                       |                                                 |                  |                                  |

|------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                        | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                        | 230400                       | 0.00%                | 96                               | SYSCLK                | XX <b>2</b>                                     | 1                | 0xD0                             |

|                        | 115200                       | 0.00%                | 192                              | SYSCLK                | XX                                              | 1                | 0xA0                             |

|                        | 57600                        | 0.00%                | 384                              | SYSCLK                | XX                                              | 1                | 0x40                             |

| from<br>Osc.           | 28800                        | 0.00%                | 768                              | SYSCLK / 12           | 00                                              | 0                | 0xE0                             |

| ( fro<br>Os            | 14400                        | 0.00%                | 1536                             | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |

| CLk<br>nal             | 9600                         | 0.00%                | 2304                             | SYSCLK / 12           | 00                                              | 0                | 0xA0                             |

| SYSCLK  <br>External 0 | 2400                         | 0.00%                | 9216                             | SYSCLK / 48           | 10                                              | 0                | 0xA0                             |

|                        | 1200                         | 0.00%                | 18432                            | SYSCLK / 48           | 10                                              | 0                | 0x40                             |

|                        | 230400                       | 0.00%                | 96                               | EXTCLK / 8            | 11                                              | 0                | 0xFA                             |

| from<br>Jsc.           | 115200                       | 0.00%                | 192                              | EXTCLK / 8            | 11                                              | 0                | 0xF4                             |

| < fror<br>Osc.         | 57600                        | 0.00%                | 384                              | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |

|                        | 28800                        | 0.00%                | 768                              | EXTCLK / 8            | 11                                              | 0                | 0xD0                             |

| SYSCL<br>Internal      | 14400                        | 0.00%                | 1536                             | EXTCLK / 8            | 11                                              | 0                | 0xA0                             |

| SY<br>Inte             | 9600                         | 0.00%                | 2304                             | EXTCLK / 8            | 11                                              | 0                | 0x70                             |

| Notes:                 |                              |                      |                                  |                       |                                                 |                  |                                  |

1. SCA1–SCA0 and T1M bit definitions can be found in Section 25.1.

**2.** X = Don't care.

## 26. Programmable Counter Array

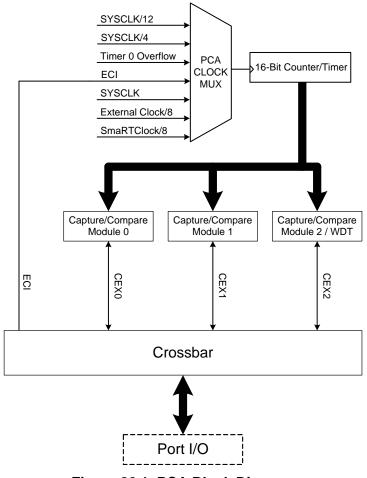

The programmable counter array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled. The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, SmaRTClock divided by 8, Timer 0 overflows, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8 to 11-Bit PWM, or 16-Bit PWM (each mode is described in Section "26.3. Capture/Compare Modules" on page 303). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 26.1

**Important Note:** The PCA Module 2 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section 26.4 for details.

Figure 26.1. PCA Block Diagram

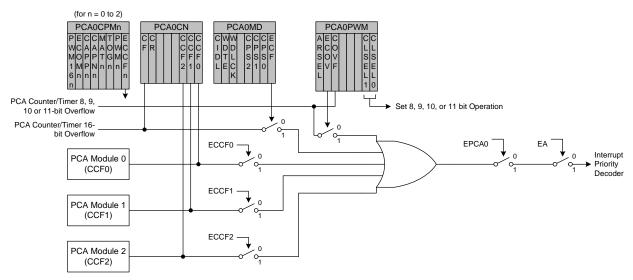

### 26.2. PCA0 Interrupt Sources

Figure 26.3 shows a diagram of the PCA interrupt tree. There are five independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter, an intermediate overflow flag (COVF), which can be set on an overflow from the 8th, 9th, 10th, or 11th bit of the PCA0 counter, and the individual flags for each PCA channel (CCF0, CCF1, and CCF2), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, ECOV for COVF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1.

Figure 26.3. PCA Interrupt Block Diagram

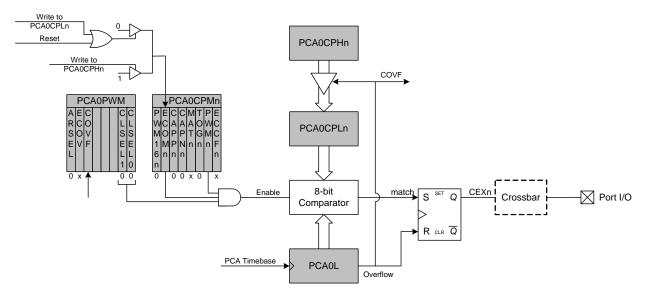

#### 26.3.5.1. 8-Bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 8-bit PWM mode is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 26.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to 00b enables 8-Bit Pulse Width Modulator mode. If the MATn bit is set to 1, the CCFn flag for the module will be set each time an 8-bit comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 256 PCA clock cycles. The duty cycle for 8-Bit PWM Mode is given in Equation 26.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(256 - PCA0CPHn)}{256}$$

#### Equation 26.2. 8-Bit PWM Duty Cycle

Using Equation 26.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 26.8. PCA 8-Bit PWM Mode Diagram

## C8051F99x-C8051F98x

## SFR Definition 26.7. PCA0CPLn: PCA Capture Module Low Byte

| Bit   | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|--------------|-----|-----|-----|-----|-----|-----|

| Name  |     | PCA0CPn[7:0] |     |     |     |     |     |     |

| Туре  | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Addresses: PCA0CPL0 = 0xFB, PCA0CPL1 = 0xE9, PCA0CPL2 = 0xEB

#### SFR Pages: PCA0CPL0 = 0x0, PCA0CPL1 = 0x0, PCA0CPL2 = 0x0,

| Bit   | Name                                                                     | Function                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0   | PCA0CPn[7:0]                                                             | PCA Capture Module Low Byte.                                                                                                                                                                                                                                                                                |  |  |  |  |

|       |                                                                          | The PCA0CPLn register holds the low byte (LSB) of the 16-bit capture module n.<br>This register address also allows access to the low byte of the corresponding<br>PCA channel's auto-reload value for 9, 10, or 11-bit PWM mode. The ARSEL bit<br>in register PCA0PWM controls which register is accessed. |  |  |  |  |

| Note: | Note: A write to this register will clear the module's ECOMn bit to a 0. |                                                                                                                                                                                                                                                                                                             |  |  |  |  |

## SFR Definition 26.8. PCA0CPHn: PCA Capture Module High Byte

| Bit   | 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |