Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                      |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, POR, PWM, WDT                 |

| Number of I/O              | 17                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 512 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                      |

| Data Converters            | -                                                                |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 24-WFQFN Exposed Pad                                             |

| Supplier Device Package    | 24-QFN (4x4)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f997-c-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

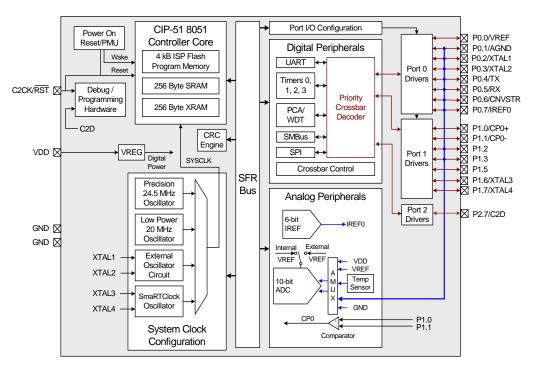

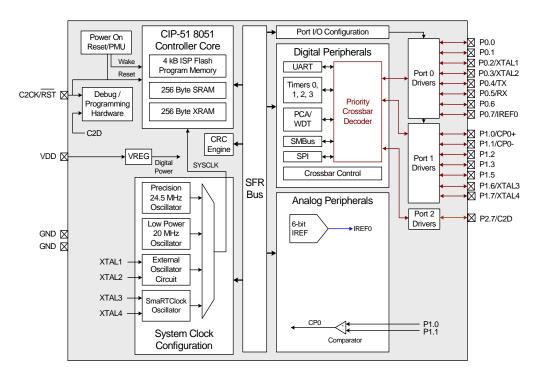

## C8051F99x-C8051F98x

#### Table 4.9. SmaRTClock Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                  | Conditions | Min  | Тур  | Max  | Units |

|----------------------------|------------|------|------|------|-------|

| Oscillator Frequency (LFO) |            | 13.1 | 16.4 | 19.7 | kHz   |

#### Table 4.10. ADC0 Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, VREF = 1.65 V (REFSL[1:0] = 11), -40 to +85 °C unless otherwise specified.

| Parameter                                           | Conditions                                                               | Min        | Тур          | Мах         | Units  |

|-----------------------------------------------------|--------------------------------------------------------------------------|------------|--------------|-------------|--------|

|                                                     | DC Accuracy                                                              |            | 1            |             |        |

| Resolution                                          | 12-bit mode<br>10-bit mode                                               |            | 12<br>10     |             | bits   |

| Integral Nonlinearity                               | 12-bit mode <sup>1</sup><br>10-bit mode                                  |            | ±1<br>±0.5   | ±1.5<br>±1  | LSB    |

| Differential Nonlinearity<br>(Guaranteed Monotonic) | 12-bit mode <sup>1</sup><br>10-bit mode                                  | _          | ±0.8<br>±0.5 | ±1<br>±1    | LSB    |

| Offset Error                                        | 12-bit mode<br>10-bit mode                                               |            | ±<1<br>±<1   | ±2<br>±2    | LSB    |

| Full Scale Error                                    | 12-bit mode <sup>2</sup><br>10-bit mode                                  | —          | ±1<br>±1     | ±4<br>±2.5  | LSB    |

| Dynamic performance (10 kHz s<br>sampling rate)     | ine-wave single-ended input,                                             | 1 dB belo  | ow Full So   | ale, ma     | kimum  |

| Signal-to-Noise Plus Distortion <sup>3</sup>        | 12-bit mode<br>10-bit mode                                               | 62<br>54   | 65<br>58     | _           | dB     |

| Signal-to-Distortion <sup>3</sup>                   | 12-bit mode<br>10-bit mode                                               | _          | 76<br>73     | _           | dB     |

| Spurious-Free Dynamic Range <sup>3</sup>            | 12-bit mode<br>10-bit mode                                               | —          | 82<br>75     | _           | dB     |

| Conversion Rate                                     |                                                                          |            | I            |             |        |

| SAR Conversion Clock                                | Normal Power Mode<br>Low Power Mode                                      | _          | _            | 8.33<br>4.4 | MHz    |

| Conversion Time in SAR Clocks                       | 10-bit Mode<br>8-bit Mode                                                | 13<br>11   | _            |             | clocks |

| Track/Hold Acquisition Time                         | Initial Acquisition<br>Subsequent Acquisitions (DC<br>input, burst mode) | 1.5<br>1.1 | —            | —           | us     |

| Throughput Rate                                     | 12-bit mode<br>10-bit mode                                               | —<br>—     | —            | 75<br>300   | ksps   |

2. The maximum code in 12-bit mode is 0xFFFC. The Full Scale Error is referenced from the maximum code.

**3.** Performance in 8-bit mode is similar to 10-bit mode.

## Table 4.13. IREF0 Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C, unless otherwise specified.

| Static PerformanceResolution6bitsOutput Compliance RangeLow Power Mode, Source<br>High Current Mode, Source<br>Low Power Mode, Sink0 $V_{DD} - 0.4$<br>$V_{DD} - 0.8$<br>$V_{DD} - 0.8$ Integral Nonlinearity<±0.2±1.0LSBDifferential Nonlinearity<±0.2±1.0LSBOffset Error±5%High Current Mode, Source±6%Integral Nonlinearity<±0.1±0.5LSBDifferential Nonlinearity<±0.1±0.5LSBFull Scale ErrorLow Power Mode, Source±6High Current Mode, Source±8%How Power Mode, Sink±8%Absolute Current ErrorLow Power Mode, Sink±8Output Settling Time to 1/2 LSB300nsStartup Time1 $\mu A$ Net Power Supply Current<br>(Vop Supplied to IREFO minus<br>any output source current)IREFODAT = 00000110IREFODAT = 100100110 $\mu A$ IREFODAT = 111111 $\mu A$ IREFODAT = 00000111 $\mu A$ IREFODAT = 00000110IREFODAT = 00000110 $\mu A$ IREFODAT = 00000110 $\mu A$ IREFODAT = 00000111 $\mu A$ <th>Parameter</th> <th>Conditions</th> <th>Min</th> <th>Тур</th> <th>Max</th> <th>Units</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Parameter                                | Conditions                                        | Min      | Тур   | Max                                      | Units |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------|----------|-------|------------------------------------------|-------|--|--|

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Static Performance                       |                                                   |          |       |                                          |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Resolution                               |                                                   | 6        |       | bits                                     |       |  |  |

| $\begin{array}{ c c c c c } \hline Differential Nonlinearity & < < \pm 0.2 & \pm 1.0 & LSB \\ \hline Offset Error & - & < \pm 0.1 & \pm 0.5 & LSB \\ \hline Low Power Mode, Source & & & \pm 5 & \% \\ \hline High Current Mode, Source & & & \pm 6 & \% \\ \hline Low Power Mode, Sink & & & \pm 8 & \% \\ \hline Low Power Mode, Sink & & & \pm 8 & \% \\ \hline Low Power Mode, Sink & & & \pm 8 & \% \\ \hline High Current Mode, Sink & & & \pm 8 & \% \\ \hline Absolute Current Error & Low Power Mode & & < \pm 1 & \pm 3 & \% \\ \hline Dynamic Performance & & & & & & & \\ \hline Output Settling Time to 1/2 LSB & & 300 & & ns \\ \hline Startup Time & & 1 & & \mus \\ \hline Power Consumption & & & & & \\ Net Power Supply Current & & & & & \\ (Vop Supplied to IREF0 minus any output source current) & Low Power Mode, Source & & & & \\ IREF0DAT = 000001 & & 10 & & \muA \\ IREF0DAT = 000001 & & 10 & & \muA \\ IREF0DAT = 111111 & & 10 & & \muA \\ IREF0DAT = 111111 & & 10 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 1000001 & & 1 & & \muA \\ IREF0DAT = 1000001 & & 1 & & \muA \\ IREF0DAT = 000001 & & 1 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 000001 & & 1 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 11 & & \muA \\ IREF0DAT = 111111 & & 12 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & \muA \\ IREF0DAT = 111111 & & 81 & & & & & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Output Compliance Range                  | High Current Mode, Source<br>Low Power Mode, Sink | 0<br>0.3 |       | V <sub>DD</sub> – 0.8<br>V <sub>DD</sub> | V     |  |  |

| $\begin{array}{ c c c c c } \hline \label{eq:constraint} Offset Error & & - & - & \pm 0.1 & \pm 0.5 & LSB \\ \hline \mbox{Low Power Mode, Source} & & - & \pm 5 & \% \\ \hline \mbox{High Current Mode, Source} & & - & \pm 6 & \% \\ \hline \mbox{Low Power Mode, Sink} & & - & \pm 8 & \% \\ \hline \mbox{High Current Mode, Sink} & & - & \pm 8 & \% \\ \hline \mbox{High Current Mode, Sink} & & - & \pm 8 & \% \\ \hline \mbox{Absolute Current Error} & Low Power Mode & & <\pm 1 & \pm 3 & \% \\ \hline \mbox{Dynamic Performance} & & 1 & & \pm 8 & \% \\ \hline \mbox{Dynamic Performance} & & - & \pm 8 & \% \\ \hline \mbox{Dynamic Performance} & & - & \pm 8 & \% \\ \hline \mbox{Dynamic Performance} & & & \pm 8 & \% \\ \hline \mbox{Output Settling Time to 1/2 LSB} & & 300 & & ns \\ \hline \mbox{Startup Time} & & 1 & & \mu s \\ \hline \mbox{Power Consumption} \\ \hline \mbox{Net Power Supply Current} & Low Power Mode, Source \\ \mbox{IREF0DAT = 000001} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 10 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 11 & & \mu A \\ \hline \mbox{IREF0DAT = 1000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 1 & & \mu A \\ \hline \mbox{IREF0DAT = 000001} & & 12 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline \mbox{IREF0DAT = 111111} & & 81 & & \mu A \\ \hline IREF0DAT =$                                                                     | Integral Nonlinearity                    |                                                   | _        | <±0.2 | ±1.0                                     | LSB   |  |  |

| $\begin{tabular}{ c c c c c c c } \hline Low Power Mode, Source & - & - & \pm 5 & \% \\ \hline High Current Mode, Source & - & - & \pm 6 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline High Current Mode, Sink & - & - & \pm 8 & \% \\ \hline Absolute Current Error & Low Power Mode & - & <\pm 1 & \pm 3 & \% \\ \hline Dynamic Performance & & & & & & & \\ \hline Output Settling Time to 1/2 LSB & - & 300 & - & ns \\ \hline Startup Time & - & 1 & - & \mus \\ \hline Power Consumption & & & & & & & \\ Net Power Supply Current (V_{DD} supplied to IREF0 minus any output source current) & Low Power Mode, Source IREF0DAT = 000001 & - & 10 & - & \muA \\ IREF0DAT = 111111 & - & 10 & - & \muA \\ IREF0DAT = 111111 & - & 10 & - & \muA \\ IREF0DAT = 111111 & - & 10 & - & \muA \\ IREF0DAT = 1000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 111111 & - & 11 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 000001 & - & 1 & - & \muA \\ IREF0DAT = 111111 & - & 11 & - & \muA \\ IREF0DAT = 000001 & - & 12 & - & \muA \\ IREF0DAT = 000001 & - & 12 & - & \muA \\ IREF0DAT = 000001 & - & 12 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & \muA \\ IREF0DAT = 111111 & - & 81 & - & & \muA \\ IREF0DAT = 1111111 & - & 81 & - $ | Differential Nonlinearity                |                                                   | —        | <±0.2 | ±1.0                                     | LSB   |  |  |

| Full Scale Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Offset Error                             |                                                   | _        | <±0.1 | ±0.5                                     | LSB   |  |  |

| Full Scale ErrorImage: Sink intermediate intermedint intermediate intermediate interm                                                                                                                                                                                                                                                          |                                          | Low Power Mode, Source                            |          | —     | ±5                                       | %     |  |  |

| $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Full Scole Error                         | High Current Mode, Source                         |          | —     | ±6                                       | %     |  |  |

| Absolute Current ErrorLow Power Mode<br>Sourcing 20 $\mu$ A-<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          | Low Power Mode, Sink                              | —        | —     | ±8                                       | %     |  |  |

| Absolute Current ErrorSourcing 20 $\mu$ AImage: Constraint of the second se                                                                                                                                                                                                                                        |                                          | High Current Mode, Sink                           |          | —     | ±8                                       | %     |  |  |

| Output Settling Time to 1/2 LSB         —         300         —         ns           Startup Time         —         1         —         µs           Power Consumption         —         1         —         µs           Net Power Supply Current<br>(V <sub>DD</sub> supplied to IREF0 minus<br>any output source current)         Low Power Mode, Source<br>IREF0DAT = 000001         —         10         —         µA           High Current Mode, Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Absolute Current Error                   |                                                   |          | <±1   | ±3                                       | %     |  |  |

| Startup Time         —         1         —         μs           Power Consumption         Net Power Supply Current (V <sub>DD</sub> supplied to IREF0 minus any output source current)         Low Power Mode, Source         10         —         μA           IREF0DAT = 000001         —         10         —         μA           IREF0DAT = 111111         —         10         —         μA           IREF0DAT = 000001         —         10         —         μA           IREF0DAT = 000001         —         10         —         μA           IREF0DAT = 111111         —         10         —         μA           IREF0DAT = 000001         —         1         —         μA           IREF0DAT = 111111         —         11         —         μA           IREF0DAT = 000001         —         12         —         μA           IREF0DAT = 111111         —         81         —         μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Dynamic Performance                      |                                                   |          |       |                                          |       |  |  |

| Power ConsumptionNet Power Supply Current<br>(V <sub>DD</sub> supplied to IREF0 minus<br>any output source current)Low Power Mode, Source<br>IREF0DAT = 00000110µAIREF0DAT = 11111110µAHigh Current Mode, Source<br>IREF0DAT = 00000110µAIREF0DAT = 00000110µAIREF0DAT = 00000110µAIREF0DAT = 00000110µAIREF0DAT = 11111110µAIREF0DAT = 0000011µAIREF0DAT = 11111111µAIREF0DAT = 00000112µAIREF0DAT = 00000112µAIREF0DAT = 11111181µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output Settling Time to 1/2 LSB          |                                                   | —        | 300   | —                                        | ns    |  |  |

| Net Power Supply Current<br>(V <sub>DD</sub> supplied to IREF0 minus<br>any output source current)Low Power Mode, Source<br>IREF0DAT = 00000110 $ \mu A$ IREF0DAT = 111111-10- $\mu A$ High Current Mode, Source<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Startup Time                             |                                                   | —        | 1     | —                                        | μs    |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Power Consumption                        |                                                   |          |       |                                          |       |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (V <sub>DD</sub> supplied to IREF0 minus | IREF0DAT = 000001<br>IREF0DAT = 111111            | —        |       |                                          | •     |  |  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                          | IREF0DAT = 000001<br>IREF0DAT = 111111            | —        |       | _                                        |       |  |  |

| IREF0DAT = 111111 — 81 — µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          | IREF0DAT = 111111<br>High Current Mode, Sink      | _        | 11    | _                                        | μA    |  |  |

| INOTE: Refer to "PWM Enhanced Mode" on page 91 for information on how to improve IREEO resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                          |                                                   |          |       |                                          |       |  |  |

# 5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

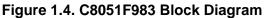

The ADC0 on C8051F980/6 and C8051F990/6 devices is a 300 ksps, 10-bit or 75 ksps, 12-bit successiveapproximation-register (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically oversample and average the ADC results. See Section 5.4 for more details on using the ADC in 12-bit mode. C8051F982 and C8051F988 devices only support the 10-bit mode.

The ADC is fully configurable under software control via Special Function Registers. The ADC0 operates in Single-ended mode and may be configured to measure various different signals using the analog multiplexer described in "5.7. ADC0 Analog Multiplexer" on page 83. The voltage reference for the ADC is selected as described in "5.9. Voltage and Ground Reference Options" on page 88.

Figure 5.1. ADC0 Functional Block Diagram

## C8051F99x-C8051F98x

## SFR Definition 12.1. SFR Page: SFR Page

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-----------------|---|---|---|---|---|---|

| Name  |   | SFRPAGE[7:0]    |   |   |   |   |   |   |

| Туре  |   | R/W             |   |   |   |   |   |   |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

SFR Page = All; SFR Address = 0xA7

| Bit | Name         | Function                                                                                    |

|-----|--------------|---------------------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page.                                                                                   |

|     |              | Specifies the SFR Page used when reading, writing, or modifying special function registers. |

### Table 12.3. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register | Address | SFR Page | Description                       | Page |

|----------|---------|----------|-----------------------------------|------|

| ACC      | 0xE0    | All      | Accumulator                       | 126  |

| ADC0AC   | 0xBA    | 0x0      | ADC0 Accumulator Configuration    | 76   |

| ADC0CF   | 0x97    | 0x0      | ADC0 Configuration                | 75   |

| ADC0CN   | 0xE8    | 0x0      | ADC0 Control                      | 74   |

| ADC0GTH  | 0xC4    | 0x0      | ADC0 Greater-Than Compare High    | 80   |

| ADC0GTL  | 0xC3    | 0x0      | ADC0 Greater-Than Compare Low     | 80   |

| ADC0H    | 0xBE    | 0x0      | ADC0 High                         | 79   |

| ADC0L    | 0xBD    | 0x0      | ADC0 Low                          | 79   |

| ADC0LTH  | 0xC6    | 0x0      | ADC0 Less-Than Compare Word High  | 81   |

| ADC0LTL  | 0xC5    | 0x0      | ADC0 Less-Than Compare Word Low   | 81   |

| ADC0MX   | 0x96    | 0x0      | AMUX0 Channel Select              | 84   |

| ADC0PWR  | 0xBB    | All      | ADC0 Burst Mode Power-Up Time     | 77   |

| ADC0TK   | 0xBC    | All      | ADC0 Tracking Control             | 78   |

| В        | 0xF0    | All      | B Register                        | 126  |

| CKCON    | 0x8E    | 0x0      | Clock Control                     | 279  |

| CLKSEL   | 0xA9    | All      | Clock Select                      | 193  |

| CPT0CN   | 0x9B    | 0x0      | Comparator0 Control               | 96   |

| CPT0MD   | 0x9D    | 0x0      | Comparator0 Mode Selection        | 97   |

| CPT0MX   | 0x9F    | 0x0      | Comparator0 Mux Selection         | 99   |

| CRC0AUTO | 0x9E    | All      | CRC0 Automatic Control            | 177  |

| CRC0CN   | 0x84    | All      | CRC0 Control                      | 175  |

| CRC0CNT  | 0x9A    | All      | CRC0 Automatic Flash Sector Count | 178  |

| CRC0DAT  | 0x86    | All      | CRC0 Data                         | 176  |

| CRC0FLIP | 0x9C    | All      | CRC0 Flip                         | 179  |

| CRC0IN   | 0x85    | All      | CRC0 Input                        | 176  |

| CS0CF    | 0xAA    | 0x0      | CS0 Configuration                 | 108  |

| CS0CN    | 0xB0    | 0x0      | CS0 Control                       | 107  |

## 13.6. External Interrupts INT0 and INT1

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INT0 Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "25.1. Timer 0 and Timer 1" on page 280) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 13.7). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register PnSKIP (see Section "21.3. Priority Crossbar Decoder" on page 219 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

## 14.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

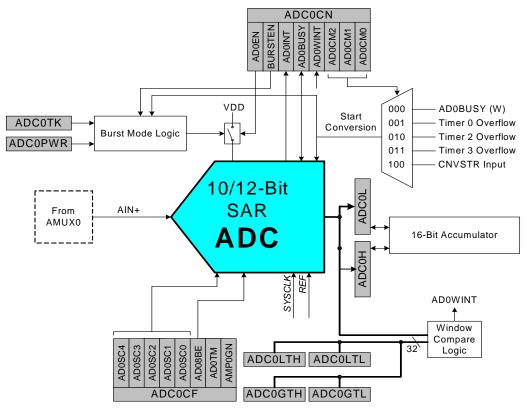

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. See **Section "10. Memory Organization" on page 128** for the location of the security byte. The Flash security mechanism allows the user to lock *n* 512-byte Flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where *n* is the 1s complement number represented by the Security Lock Byte. **The page containing the Flash Security Lock Byte is unlocked when no other Flash pages are locked (all bits of the Lock Byte are 1) and locked when any other Flash pages are locked (any bit of the Lock Byte is 0).**

| Security Lock Byte: | 1111 1011b                                  |

|---------------------|---------------------------------------------|

| ones Complement:    | 0000 0100b                                  |

| Flash pages locked: | 5 (First four Flash pages + Lock Byte Page) |

Figure 14.1. Flash Program Memory Map (8 kB and smaller devices)

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 14.1 summarizes the Flash security features of the C8051F99x-C8051F98x devices.

## C8051F99x-C8051F98x

## SFR Definition 15.3. PMU0MD: Power Management Unit Mode

| Bit   | 7     | 6      | 5      | 4   | 3   | 2   | 1   | 0   |

|-------|-------|--------|--------|-----|-----|-----|-----|-----|

| Name  | RTCOE | WAKEOE | MONDIS |     |     |     |     |     |

| Туре  | R/W   | R/W    | R/W    | R/W | R/W | R/W | R/W | R/W |

| Reset | 0     | 0      | 0      | 0   | 0   | 0   | 0   | 0   |

### SFR Page = 0xF; SFR Address = 0xB5

| Bit   | Name          | Function                                                                                                                                                                                                                                                                               |

|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | RTCOE         | Buffered SmaRTClock Output Enable.                                                                                                                                                                                                                                                     |

|       |               | Enables the buffered SmaRTClock oscillator output on P0.2.<br>0: Buffered SmaRTClock output not enabled.                                                                                                                                                                               |

|       |               | 1: Buffered SmaRTClock output is enabled.                                                                                                                                                                                                                                              |

| 6     | WAKEOE        | Wakeup Request Output Enable.                                                                                                                                                                                                                                                          |

|       |               | Enables the Sleep Mode wake-up request signal on P0.3.                                                                                                                                                                                                                                 |

|       |               | 0: Wake-up request signal is not enabled.                                                                                                                                                                                                                                              |

|       |               | 1: Wake-up request signal is enabled.                                                                                                                                                                                                                                                  |

| 5     | MONDIS*       | POR Supply Monitor Disable.                                                                                                                                                                                                                                                            |

|       |               | Writing a 1 to this bit disables the POR supply monitor.                                                                                                                                                                                                                               |

| 4:0   | Unused        | Read = 00000b. Write = Don't Care.                                                                                                                                                                                                                                                     |

| Notes | sleep mode cu | ply Monitor should not be disabled if the supply voltage is greater than 2.4 V. The lowest power urrent, 10 nA typical, can only be achieved when the supply voltage is less than 2.4 V. The sleep mode for voltages above 2.4 V is 50 nA typical with the POR Supply Monitor enabled. |

Rev. 1.2

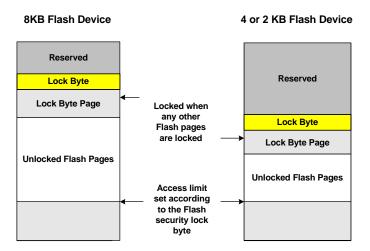

## 16. Cyclic Redundancy Check Unit (CRC0)

C8051F99x-C8051F98x devices include a cyclic redundancy check unit (CRC0) that can perform a CRC using a 16-bit polynomial. CRC0 accepts a stream of 8-bit data written to the CRC0IN register. CRC0 posts the 16-bit result to an internal register. The internal result register may be accessed indirectly using the CRC0PNT bits and CRC0DAT register, as shown in Figure 16.1. CRC0 also has a bit reverse register for quick data manipulation.

Figure 16.1. CRC0 Block Diagram

## 16.1. CRC Algorithm

The C8051F99x-C8051F98x CRC unit generates a CRC result equivalent to the following algorithm:

- XOR the input with the most-significant bits of the current CRC result. If this is the first iteration of the CRC unit, the current CRC result will be the set initial value (0x0000 or 0xFFFF).

- 2a. If the MSB of the CRC result is set, shift the CRC result and XOR the result with the selected polynomial.

- 2b. If the MSB of the CRC result is not set, shift the CRC result.

Repeat Steps 2a/2b for the number of input bits (8). The algorithm is also described in the following example.

## SFR Definition 16.4. CRC0AUTO: CRC0 Automatic Control

| Bit   | 7 6 5 4 3 2 |         | 2 | 1 0 |   |            |   |   |

|-------|-------------|---------|---|-----|---|------------|---|---|

| Name  | AUTOEN      | CRCDONE |   |     | ( | CRC0ST[4:0 | ] |   |

| Туре  | R/W         | R       | R | R/W |   |            |   |   |

| Reset | 0           | 1       | 0 | 0   | 0 | 0          | 0 | 0 |

#### SFR Page = All; SFR Address = 0x9E

| Bit | Name        | Function                                                                                                                                                                                                                                |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AUTOEN      | Automatic CRC Calculation Enable.                                                                                                                                                                                                       |

|     |             | When AUTOEN is set to 1, any write to CRC0CN will initiate an automatic CRC starting at Flash sector CRC0ST and continuing for CRC0CNT sectors.                                                                                         |

| 6   | CRCDONE     | CRCDONE Automatic CRC Calculation Complete.                                                                                                                                                                                             |

|     |             | Set to 0 when a CRC calculation is in progress. Code execution is stopped during a CRC calculation; therefore, reads from firmware will always return 1.                                                                                |

| 5   | Unused      | Read = 0b; Write = Don't Care.                                                                                                                                                                                                          |

| 4:0 | CRC0ST[4:0] | Automatic CRC Calculation Starting Block.                                                                                                                                                                                               |

|     |             | These bits specify the Flash block to start the automatic CRC calculation. The starting address of the first Flash block included in the automatic CRC calculation is CRC0ST x Block Size.<br><b>Note:</b> The block size is 256 bytes. |

## 20. SmaRTClock (Real Time Clock)

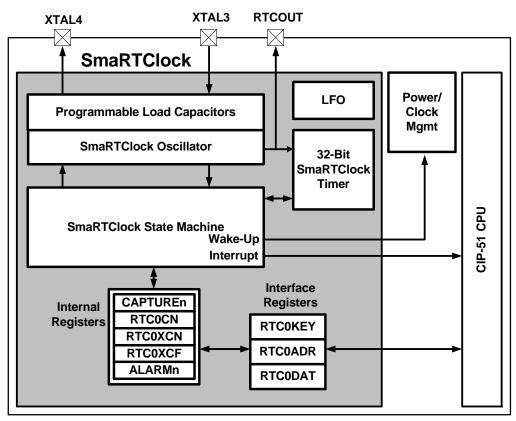

C8051F99x-C8051F98x devices include an ultra low power 32-bit SmaRTClock Peripheral (Real Time Clock) with alarm. The SmaRTClock has a dedicated 32 kHz oscillator that can be configured for use with or without a crystal. No external resistor or loading capacitors are required. The on-chip loading capacitors are programmable to 16 discrete levels allowing compatibility with a wide range of crystals. The SmaRT-Clock can operate directly from a 1.8–3.6 V battery voltage and remains operational even when the device goes into its lowest power down mode. The SmaRTClock output can be buffered and routed to a GPIO pin to provide an accurate, low frequency clock to other devices while the MCU is in its lowest power down mode (see "PMU0MD: Power Management Unit Mode" on page 170 for more details). C8051F99x-C8051F98x devices also support an ultra low power internal LFO that reduces sleep mode current.

The SmaRTClock allows a maximum of 36 hour 32-bit independent time-keeping when used with a 32.768 kHz Watch Crystal. The SmaRTClock provides an Alarm and Missing SmaRTClock events, which could be used as reset or wakeup sources. See Section "18. Reset Sources" on page 181 and Section "15. Power Management" on page 162 for details on reset sources and low power mode wake-up sources, respectively.

Figure 20.1. SmaRTClock Block Diagram

## 21.5. Special Function Registers for Accessing and Configuring Port I/O

All Port I/O are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

Each Port has a corresponding PnSKIP register which allows its individual Port pins to be assigned to digital functions or skipped by the Crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions such as the EMIF should have their PnSKIP bit set to 1.

The Port input mode of the I/O pins is defined using the Port Input Mode registers (PnMDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is P2.7, which can only be used for digital I/O.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings.

The drive strength of the output drivers are controlled by the Port Drive Strength (PnDRV) registers. The default is low drive strength. See Section "4. Electrical Characteristics" on page 48 for the difference in output drive strength between the two modes.

## SFR Definition 21.15. P1MDIN: Port1 Input Mode

| Bit   | 7                    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------------------|---|---|---|---|---|---|---|

| Name  | P1MDIN[7:0]          |   |   |   |   |   |   |   |

| Туре  | R/W                  |   |   |   |   |   |   |   |

| Reset | et 1 1 1 1 1 1 1 1 1 |   |   |   |   |   |   | 1 |

SFR Page = 0x0; SFR Address = 0xF2

| Bit | Name        | Function                                                                                                                                                                                                                                                                 |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDIN[7:0] | Analog Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                                                                  |

|     |             | Port pins configured for analog mode have their weak pullup and digital receiver<br>disabled. The digital driver is not explicitly disabled.<br>0: Corresponding P1.n pin is configured for analog mode.<br>1: Corresponding P1.n pin is not configured for analog mode. |

## SFR Definition 21.16. P1MDOUT: Port1 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P1MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xA5

| Bit | Name         | Function                                                                                             |

|-----|--------------|------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDOUT[7:0] | Output Configuration Bits for P1.7–P1.0 (respectively).                                              |

|     |              | These bits control the digital driver even when the corresponding bit in register P1MDIN is logic 0. |

|     |              | 0: Corresponding P1.n Output is open-drain.                                                          |

|     |              | 1: Corresponding P1.n Output is push-pull.                                                           |

### 22.5.2. Read Sequence (Master)

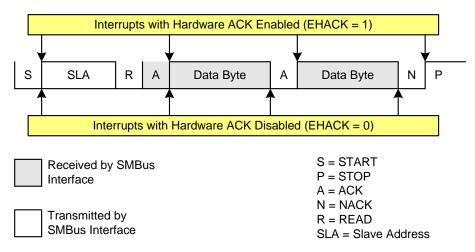

During a read sequence, an SMBus master reads data from a slave device. The master in this transfer will be a transmitter during the address byte, and a receiver during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.