Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Active                                                            |

| Core Processor             | CIP-51 8051                                                       |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, POR, PWM, WDT                  |

| Number of I/O              | 17                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-WFQFN Exposed Pad                                              |

| Supplier Device Package    | 24-QFN (4x4)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f997-c-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Figures

| Figure 1.1. C8051F980 Block Diagram                                                          | 18 |

|----------------------------------------------------------------------------------------------|----|

| Figure 1.2. C8051F981 Block Diagram                                                          | 18 |

| Figure 1.3. C8051F982 Block Diagram                                                          | 19 |

| Figure 1.4. C8051F983 Block Diagram                                                          | 19 |

| Figure 1.5. C8051F985 Block Diagram                                                          | 20 |

| Figure 1.6. C8051F986 Block Diagram                                                          | 20 |

| Figure 1.7. C8051F987 Block Diagram                                                          | 21 |

| Figure 1.8. C8051F988 Block Diagram                                                          | 21 |

| Figure 1.9. C8051F989 Block Diagram                                                          | 22 |

| Figure 1.10. C8051F990 Block Diagram                                                         | 22 |

| Figure 1.11. C8051F991 Block Diagram                                                         | 23 |

| Figure 1.12. C8051F996 Block Diagram                                                         | 23 |

| Figure 1.13. C8051F997 Block Diagram                                                         |    |

| Figure 1.14. Port I/O Functional Block Diagram                                               | 26 |

| Figure 1.15. PCA Block Diagram                                                               | 27 |

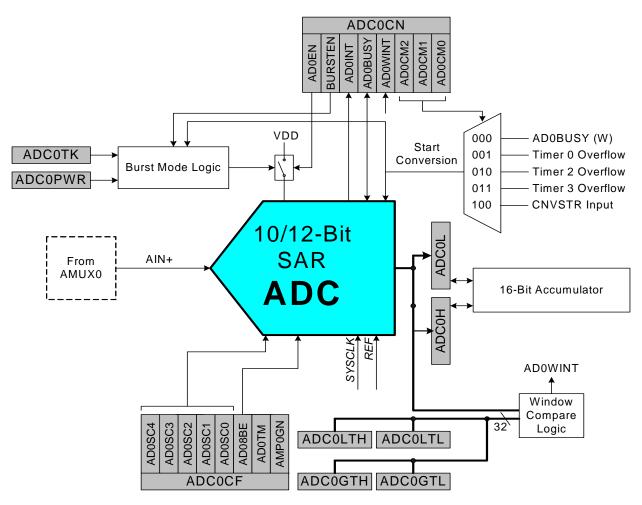

| Figure 1.16. ADC0 Functional Block Diagram                                                   |    |

| Figure 1.17. ADC0 Multiplexer Block Diagram                                                  | 29 |

| Figure 1.18. Comparator 0 Functional Block Diagram                                           | 30 |

| Figure 3.1. QFN-20 Pinout Diagram (Top View)                                                 |    |

| Figure 3.2. QFN-24 Pinout Diagram (Top View)                                                 |    |

| Figure 3.3. QSOP-24 Pinout Diagram (Top View)                                                |    |

| Figure 3.4. QFN-20 Package Marking Diagram                                                   |    |

| Figure 3.5. QFN-24 Package Marking Diagram                                                   |    |

| Figure 3.6. QSOP-24 Package Marking Diagram                                                  |    |

| Figure 3.7. QFN-20 Package Drawing                                                           |    |

| Figure 3.8. Typical QFN-20 Landing Diagram                                                   |    |

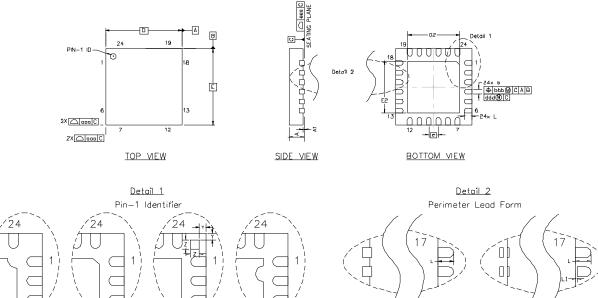

| Figure 3.9. QFN-24 Package Drawing                                                           |    |

| Figure 3.10. Typical QFN-24 Landing Diagram                                                  |    |

| Figure 3.11. QSOP-24 Package Diagram                                                         |    |

| Figure 3.12. QSOP-24 Landing Diagram                                                         |    |

| Figure 4.1. Active Mode Current (External CMOS Clock)                                        |    |

| Figure 4.2. Idle Mode Current (External CMOS Clock)                                          |    |

| Figure 4.3. Typical VOH Curves, 1.8–3.6 V                                                    |    |

| Figure 4.4. Typical VOL Curves, 1.8–3.6 V                                                    |    |

| Figure 5.1. ADC0 Functional Block Diagram                                                    |    |

| Figure 5.2. 10-Bit ADC Track and Conversion Example Timing (BURSTEN = 0)                     |    |

| Figure 5.3. Burst Mode Tracking Example with Repeat Count Set to 4                           |    |

| Figure 5.4. ADC0 Equivalent Input Circuits                                                   |    |

| Figure 5.5. ADC Window Compare Example: Right-Justified Single-Ended Data                    |    |

| Figure 5.6. ADC Window Compare Example: Left-Justified Single-Ended Data                     |    |

| Figure 5.7. ADC0 Multiplexer Block Diagram                                                   |    |

| Figure 5.8. Temperature Sensor Transfer Function                                             | 85 |

| Figure 5.9. Temperature Sensor Error with 1-Point Calibration ( $V_{REF} = 1.65 \text{ V}$ ) | 86 |

| SFR Definition 13.2. IP: Interrupt Priority                                       |     |

|-----------------------------------------------------------------------------------|-----|

| SFR Definition 13.3. EIE1: Extended Interrupt Enable 1                            | 144 |

| SFR Definition 13.4. EIP1: Extended Interrupt Priority 1                          |     |

| SFR Definition 13.5. EIE2: Extended Interrupt Enable 2                            | 146 |

| SFR Definition 13.6. EIP2: Extended Interrupt Priority 2                          | 147 |

| SFR Definition 13.7. IT01CF: INT0/INT1 Configuration                              | 149 |

| SFR Definition 14.1. DEVICEID: Device Identification                              | 154 |

| SFR Definition 14.2. REVID: Revision Identification                               |     |

| SFR Definition 14.3. PSCTL: Program Store R/W Control                             | 159 |

| SFR Definition 14.4. FLKEY: Flash Lock and Key                                    |     |

| SFR Definition 14.5. FLSCL: Flash Scale                                           | 161 |

| SFR Definition 14.6. FLWR: Flash Write Only                                       | 161 |

| SFR Definition 15.1. PMU0CF: Power Management Unit Configuration <sup>1,2,3</sup> | 168 |

| SFR Definition 15.2. PMU0FL: Power Management Unit Flag <sup>1,2</sup>            | 169 |

| SFR Definition 15.3. PMU0MD: Power Management Unit Mode                           |     |

| SFR Definition 15.4. PCON: Power Management Control Register                      |     |

| SFR Definition 16.1. CRC0CN: CRC0 Control                                         |     |

| SFR Definition 16.2. CRC0IN: CRC0 Data Input                                      |     |

| SFR Definition 16.3. CRC0DAT: CRC0 Data Output                                    |     |

| SFR Definition 16.4. CRC0AUTO: CRC0 Automatic Control                             |     |

| SFR Definition 16.5. CRC0CNT: CRC0 Automatic Flash Sector Count                   |     |

| SFR Definition 16.6. CRC0FLIP: CRC0 Bit Flip                                      |     |

| SFR Definition 17.1. REGOCN: Voltage Regulator Control                            |     |

| SFR Definition 18.1. VDM0CN: VDD Supply Monitor Control                           |     |

| SFR Definition 18.2. RSTSRC: Reset Source                                         | 187 |

| SFR Definition 19.1. CLKSEL: Clock Select                                         |     |

| SFR Definition 19.2. OSCICN: Internal Oscillator Control                          |     |

| SFR Definition 19.3. OSCICL: Internal Oscillator Calibration                      |     |

| SFR Definition 19.4. OSCXCN: External Oscillator Control                          |     |

| SFR Definition 20.1. RTC0KEY: SmaRTClock Lock and Key                             |     |

| SFR Definition 20.2. RTC0ADR: SmaRTClock Address                                  |     |

| SFR Definition 20.3. RTC0DAT: SmaRTClock Data                                     |     |

| Internal Register Definition 20.4. RTC0CN: SmaRTClock Control                     |     |

| Internal Register Definition 20.5. RTC0XCN: SmaRTClock Oscillator Control         |     |

| Internal Register Definition 20.6. RTC0XCF: SmaRTClock Oscillator Configuration . |     |

| Internal Register Definition 20.7. CAPTUREn: SmaRTClock Timer Capture             |     |

| Internal Register Definition 20.8. ALARMn: SmaRTClock Alarm Programmed Value      |     |

| SFR Definition 21.1. XBR0: Port I/O Crossbar Register 0                           |     |

| SFR Definition 21.2. XBR1: Port I/O Crossbar Register 1                           |     |

| SFR Definition 21.3. XBR2: Port I/O Crossbar Register 2                           |     |

| SFR Definition 21.4. P0MASK: Port0 Mask Register                                  |     |

| SFR Definition 21.5. P0MAT: Port0 Match Register                                  |     |

| SFR Definition 21.6. P1MASK: Port1 Mask Register                                  |     |

| SFR Definition 21.7. P1MAT: Port1 Match Register                                  |     |

| SFR Definition 21.8. P0: Port0                                                    |     |

|                                                                                   |     |

# 1.5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

C8051F99x-C8051F98x devices have a 300 ksps, 10-bit or 75 ksps 12-bit successive-approximationregister (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically average the ADC results, providing an effective 11, 12, or 13 bit ADC result without any additional CPU intervention.

The ADC can sample the voltage at select GPIO pins (see Figure 1.17) and has an on-chip attenuator that allows it to measure voltages up to twice the voltage reference. Additional ADC inputs include an on-chip temperature sensor, the VDD supply voltage, and the internal digital supply voltage.

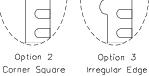

Option 1 Irregular Corner

Option 1 Edge Exposed

Option 2 Edge Pull-Back

## Figure 3.9. QFN-24 Package Drawing

| Dimension | Min      | Тур  | Max  | Dimension | Min  | Тур  | Max  |

|-----------|----------|------|------|-----------|------|------|------|

| А         | 0.70     | 0.75 | 0.80 | L         | 0.30 | 0.40 | 0.50 |

| A1        | 0.00     | 0.02 | 0.05 | L1        | 0.00 | —    | 0.15 |

| b         | 0.18     | 0.25 | 0.30 | aaa       | _    | —    | 0.15 |

| D         | 4.00 BSC |      |      | bbb       | _    | —    | 0.10 |

| D2        | 2.55     | 2.70 | 2.80 | ddd       | _    | —    | 0.05 |

| е         | 0.50 BSC |      |      | eee       | —    | —    | 0.08 |

| E         | 4.00 BSC |      |      | Z         | _    | 0.24 |      |

| E2        | 2.55     | 2.70 | 2.80 | Y         | _    | 0.18 | —    |

#### Table 3.4. QFN-24 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation WGGD except for custom features D2, E2, Z, Y, and L which are toleranced per supplier designation.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

| Dimension | MIN      | MAX  |  |  |  |

|-----------|----------|------|--|--|--|

| C1        | 3.90     | 4.00 |  |  |  |

| C2        | 3.90     | 4.00 |  |  |  |

| E         | 0.50 BSC |      |  |  |  |

| X1        | 0.20     | 0.30 |  |  |  |

| X2        | 2.70     | 2.80 |  |  |  |

| Y1        | 0.65     | 0.75 |  |  |  |

| Y2        | 2.70     | 2.80 |  |  |  |

#### Table 3.5. PCB Land Pattern

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### **Stencil Design**

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- **4.** A 2x2 array of 1.10 mm x 1.10 mm openings on 1.30 mm pitch should be used for the center ground pad.

#### **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### Table 4.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameters               | Conditions                                        | Min                   | Тур       | Max          | Units |

|--------------------------|---------------------------------------------------|-----------------------|-----------|--------------|-------|

| Output High Voltage      | High Drive Strength, PnDRV.n = 1                  |                       |           |              | V     |

|                          | IOH = –3 mA, Port I/O push-pull                   | V <sub>DD</sub> – 0.7 | _         |              |       |

|                          | IOH = −10 µA, Port I/O push-pull                  | V <sub>DD</sub> – 0.1 | —         | _            |       |

|                          | IOH = –10 mA, Port I/O push-pull                  |                       | See Chart |              |       |

|                          | Low Drive Strength, PnDRV.n = 0                   |                       |           |              |       |

|                          | IOH = −1 mA, Port I/O push-pull                   | V <sub>DD</sub> – 0.7 | —         | —            |       |

|                          | IOH = −10 μA, Port I/O push-pull                  | V <sub>DD</sub> – 0.1 | —         | —            |       |

|                          | IOH = -3 mA, Port I/O push-pull                   | _                     | See Chart | _            |       |

| Output Low Voltage       | High Drive Strength, PnDRV.n = 1                  |                       |           |              | V     |

|                          | I <sub>OL</sub> = 8.5 mA                          | _                     | _         | 0.6          |       |

|                          | I <sub>OL</sub> = 10 μA                           | —                     | —         | 0.1          |       |

|                          | I <sub>OL</sub> = 25 mA                           | —                     | See Chart | _            |       |

|                          | Low Drive Strength, PnDRV.n = 0                   |                       |           |              |       |

|                          | I <sub>OL</sub> = 1.4 mA                          | —                     | —         | 0.6          |       |

|                          | I <sub>OL</sub> = 10 μA                           | —                     | —         | 0.1          |       |

|                          | I <sub>OL</sub> = 4 mA                            | _                     | See Chart | —            |       |

| Input High Voltage       | V <sub>DD</sub> = 2.0 to 3.6 V                    | V <sub>DD</sub> - 0.6 | _         | _            | V     |

|                          | V <sub>DD</sub> = 0.9 to 2.0 V                    | 0.7 x VDD             | —         | —            | V     |

| Input Low Voltage        | V <sub>DD</sub> = 2.0 to 3.6 V                    | —                     | —         | 0.6          | V     |

|                          | V <sub>DD</sub> = 0.9 to 2.0 V                    | —                     | —         | 0.3 x<br>VDD | V     |

|                          | Weak Pullup Off                                   | —                     | —         | ±1           | μA    |

| Input Leakage<br>Current | Weak Pullup On, $V_{IN} = 0 V$ , $V_{DD} = 1.8 V$ | —                     | 4         | —            |       |

|                          | Weak Pullup On, Vin = 0 V, $V_{DD}$ = 3.6 V       | —                     | 20        | 35           |       |

#### Table 4.16. Capacitive Sense Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_{A}$  = –40 to +85 °C unless otherwise specified.

| Parameter                            | Conditions                                                                       | Min | Тур | Max  | Units    |

|--------------------------------------|----------------------------------------------------------------------------------|-----|-----|------|----------|

| Single Conversion Time <sup>1</sup>  | 12-bit Mode                                                                      | 20  | 25  | 40   | μs       |

|                                      | 13-bit Mode (default)                                                            | 21  | 27  | 42.5 |          |

|                                      | 14-bit Mode                                                                      | 23  | 29  | 45   |          |

|                                      | 16-bit Mode                                                                      | 26  | 33  | 50   |          |

| Number of Channels                   | 24-pin Packages                                                                  |     | 17  |      | Channels |

|                                      | 20-pin Packages                                                                  |     | 16  |      |          |

| Capacitance per Code                 | Default Configuration                                                            | —   | 1   | —    | fF       |

| Maximum External                     | CS0CG = 111b (Default)                                                           | —   | 45  | —    | pF       |

| Capacitive Load                      | CS0CG = 000b                                                                     | —   | 500 | —    | pF       |

| Maximum External<br>Series Impedance | CS0CG = 111b (Default)                                                           | —   | 50  | —    | kΩ       |

| Power Supply Current                 | CS module bias current, 25 °C                                                    | —   | 50  | 60   | μA       |

|                                      | CS module alone, maximum code<br>output, 25 °C                                   | —   | 90  | 125  | μA       |

|                                      | Wake-on-CS threshold (suspend mode with regulator and CS module on) <sup>3</sup> | —   | 130 | 180  | μA       |

| Notes:                               | •                                                                                | •   | •   | •    | •        |

1. Conversion time is specified with the default configuration.

2. RMS Noise is equivalent to one standard deviation. Peak-to-peak noise encompasses ±3.3 standard deviations. The RMS noise value is specified with the default configuration.

3. Includes only current from regulator, CS module, and MCU in suspend mode.

#### 5.2. Modes of Operation

ADC0 has a maximum conversion speed of 300 ksps in 10-bit mode. The ADC0 conversion clock (SARCLK) is a divided version of the system clock when burst mode is disabled (BURSTEN = 0), or a divided version of the low power oscillator when burst mode is enabled (BURSEN = 1). The clock divide value is determined by the AD0SC bits in the ADC0CF register.

#### 5.2.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2–0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a 1 to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 3 overflow

- 5. A rising edge on the CNVSTR input signal (pin P0.6)

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. When Timer 2 or Timer 3 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2/3 is in 16-bit mode. See "25. Timers" on page 278 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.6. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.6 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.6, set to 1 Bit 6 in register P0SKIP. See "21. Port Input/Output" on page 215 for details on Port I/O configuration.

### 8.12. CS0 Pin Monitor

The CS0 module provides accurate conversions in all operating modes of the CPU, peripherals and I/O ports. Pin monitoring circuits are provided to improve interference immunity from high-current output pin switching. The CS0 Pin Monitor register (CS0PM, SFR Definition 8.14) controls the operation of these pin monitors.

Conversions in the CS0 module are immune to any change on digital inputs and immune to most output switching. Even high-speed serial data transmission will not affect CS0 operation as long as the output load is limited. Output changes that switch large loads such as LEDs and heavily-loaded communications lines can affect conversion accuracy. For this reason, the CS0 module includes pin monitoring circuits that will, if enabled, automatically adjust conversion timing if necessary to eliminate any effect from high-current output pin switching.

The pin monitor enable bit should be set for any output signal that is expected to drive a large load.

Example: The SMBus in a system is heavily loaded with multiple slaves and a long PCB route. Set the SMBus pin monitor enable, SMBPM = 1.

Example: Timer2 controls an LED on Port 1, pin 3 to provide variable dimming. Set the Port SFR write monitor enable, PIOPM = 1.

Example: The SPI bus is used to communicate to a nearby host. The pin monitor is not needed because the output is not heavily loaded, SPIPM remains = 0, the default reset state.

Pin monitors should not be enabled unless they are required. The pin monitor works by repeating any portion of a conversion that may have been corrupted by a change on an output pin. Setting pin monitor enables bits will slow CS0 conversions.

The frequency of CS0 retry operations can be limited by setting the CSPMMD bits. In the default (reset) state, all converter retry requests will be performed. This is the recommended setting for all applications. The number of retries per conversion can be limited to either two or four retries by changing CSPMMD. Limiting the number of retries per conversion ensures that even in circumstances where extremely frequent high-power output switching occurs, conversions will be completed, though there may be some loss of accuracy due to switching noise.

Activity of the pin monitor circuit can be detected by reading the Pin Monitor Event bit, CS0PME, in register CS0CN. This bit will be set if any CS0 converter retries have occurred. It remains set until cleared by software or a device reset.

### 8.13. Adjusting CS0 For Special Situations

There are several configuration options in the CS0 module designed to modify the operation of the circuit and address special situations. In particular, any circuit with more than 500 ohms of series impedance between the sensor and the device pin may require adjustments for optimal performance. Typical applications which may require adjustments include:

- Touch panel sensors fabricated using a resistive conductor such as indium-tin-oxide (ITO).

- Circuits using a high-value series resistor to isolate the sensor element for high ESD protection.

Most systems will require no fine tuning, and the default settings for CS0DT, CS0DR, CS0IA, CS0RP and CS0LP should be used.

## SFR Definition 9.6. PSW: Program Status Word

| Bit                                                                                         | 7       | 6                                                                    | 5                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4             | 3             | 2          | 1              | 0            |  |  |

|---------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|------------|----------------|--------------|--|--|

| Nam                                                                                         | e CY    | AC                                                                   | F0                                                                                                                                                                                                                                                                                                                                                                                                                                   | RS            | [1:0]         | OV         | F1             | PARITY       |  |  |

| Туре                                                                                        | R/W     | R/W                                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/            | /W            | R/W        | R/W            | R            |  |  |

| Rese                                                                                        | et O    | 0                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0             | 0             | 0          | 0              | 0            |  |  |

| SFR F                                                                                       |         |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |               |            |                |              |  |  |

| SFR Page = All; SFR Address = 0xD0; Bit-Addressable         Bit       Name         Function |         |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |               |            |                |              |  |  |

| 7                                                                                           | CY      | <b>Carry Flag.</b><br>This bit is set<br>row (subtraction            |                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |               |            |                | n) or a bor- |  |  |

| 6                                                                                           | AC      | This bit is set<br>borrow from (s                                    | Auxiliary Carry Flag.<br>This bit is set when the last arithmetic operation resulted in a carry into (addition) or a<br>porrow from (subtraction) the high order nibble. It is cleared to logic 0 by all other arith-<br>netic operations.                                                                                                                                                                                           |               |               |            |                |              |  |  |

| 5                                                                                           | F0      | <b>User Flag 0.</b><br>This is a bit-ad                              | <b>User Flag 0.</b><br>This is a bit-addressable, general purpose flag for use under software control.                                                                                                                                                                                                                                                                                                                               |               |               |            |                |              |  |  |

| 4:3                                                                                         | RS[1:0] | These bits sel<br>00: Bank 0, Ao<br>01: Bank 1, Ao<br>10: Bank 2, Ao | Register Bank Select.These bits select which register bank is used during register accesses.D0: Bank 0, Addresses 0x00-0x07D1: Bank 1, Addresses 0x08-0x0F10: Bank 2, Addresses 0x10-0x1711: Bank 3, Addresses 0x18-0x1F                                                                                                                                                                                                             |               |               |            |                |              |  |  |

| 2                                                                                           | OV      | This bit is set<br>• An ADD,<br>• A MUL in<br>• A DIV ins            | <ul> <li>Dverflow Flag.</li> <li>This bit is set to 1 under the following circumstances: <ul> <li>An ADD, ADDC, or SUBB instruction causes a sign-change overflow.</li> <li>A MUL instruction results in an overflow (result is greater than 255).</li> <li>A DIV instruction causes a divide-by-zero condition.</li> </ul> </li> <li>The OV bit is cleared to 0 by the ADD, ADDC, SUBB, MUL, and DIV instructions in all</li> </ul> |               |               |            |                |              |  |  |

| 1                                                                                           | F1      | <b>User Flag 1.</b><br>This is a bit-ad                              |                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |               |            |                |              |  |  |

| 0                                                                                           | PARITY  | <b>Parity Flag.</b><br>This bit is set t<br>if the sum is e          | •                                                                                                                                                                                                                                                                                                                                                                                                                                    | ne sum of the | eight bits in | the accumu | lator is odd a | and cleared  |  |  |

## SFR Definition 13.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7                  | 6                                                                     | 5                                                                                                                                                                                                                                                                                                                                            | 4                           | 3                          | 2 | 1        | 0 |  |  |

|-------|--------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|---|----------|---|--|--|

| Nam   | e ET3              | ECP0 EPCA0 EADC0 EWADC0 ERTC0A ES                                     |                                                                                                                                                                                                                                                                                                                                              |                             |                            |   |          |   |  |  |

| Туре  | e R/W              | R                                                                     | R R/W R/W R/W R/W R/W                                                                                                                                                                                                                                                                                                                        |                             |                            |   |          |   |  |  |

| Rese  | et 0 0 0 0 0 0 0 0 |                                                                       |                                                                                                                                                                                                                                                                                                                                              |                             |                            |   |          | 0 |  |  |

| SFR F | age = All; S       | SFR Address =                                                         | 0xE6                                                                                                                                                                                                                                                                                                                                         |                             |                            |   |          |   |  |  |

| Bit   | Name               |                                                                       |                                                                                                                                                                                                                                                                                                                                              |                             | Function                   |   |          |   |  |  |

| 7     | ET3                | This bit sets th<br>0: Disable Tim                                    | nable Timer 3 Interrupt.<br>his bit sets the masking of the Timer 3 interrupt.<br>Disable Timer 3 interrupts.<br>Enable interrupt requests generated by the TF3L or TF3H flags.                                                                                                                                                              |                             |                            |   |          |   |  |  |

| 6     | Unused             | Read = 0b. W                                                          | rite = Don't d                                                                                                                                                                                                                                                                                                                               | care.                       |                            |   |          |   |  |  |

| 5     | ECP0               | This bit sets th<br>0: Disable CP                                     | Enable Comparator0 (CP0) Interrupt.<br>This bit sets the masking of the CP0 interrupt.<br>0: Disable CP0 interrupts.<br>1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.                                                                                                                                                |                             |                            |   |          |   |  |  |

| 4     | EPCA0              | This bit sets th<br>0: Disable all I                                  | Enable Programmable Counter Array (PCA0) Interrupt.<br>This bit sets the masking of the PCA0 interrupts.<br>0: Disable all PCA0 interrupts.<br>1: Enable interrupt requests generated by PCA0.                                                                                                                                               |                             |                            |   |          |   |  |  |

| 3     | EADC0              | Enable ADC0<br>This bit sets th<br>0: Disable AD<br>1: Enable inte    | ne masking o<br>C0 Conversi                                                                                                                                                                                                                                                                                                                  | of the ADC0<br>ion Complete | Conversion<br>e interrupt. | · | terrupt. |   |  |  |

| 2     | EWADC0             | This bit sets th<br>0: Disable AD                                     | <ol> <li>Enable interrupt requests generated by the AD0INT flag.</li> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>Disable ADC0 Window Comparison interrupt.</li> <li>Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ol> |                             |                            |   |          |   |  |  |

| 1     | ERTC0A             | This bit sets th<br>0: Disable Sm                                     | Enable SmaRTClock Alarm Interrupts.<br>This bit sets the masking of the SmaRTClock Alarm interrupt.<br>D: Disable SmaRTClock Alarm interrupts.<br>1: Enable interrupt requests generated by a SmaRTClock Alarm.                                                                                                                              |                             |                            |   |          |   |  |  |

| 0     | ESMB0              | Enable SMBL<br>This bit sets th<br>0: Disable all s<br>1: Enable inte | ne masking o<br>SMB0 interru                                                                                                                                                                                                                                                                                                                 | of the SMB0<br>upts.        | ·                          |   |          |   |  |  |

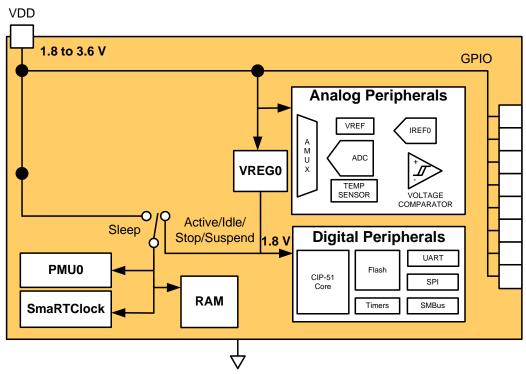

### 15.1. Normal Mode

The MCU is fully functional in normal mode. Figure 15.1 shows the on-chip power distribution to various peripherals. There are two supply voltages powering various sections of the chip:  $V_{DD}$  and the 1.8 V internal core supply. All analog peripherals are directly powered from the  $V_{DD}$  pin. All digital peripherals and the CIP-51 core are powered from the 1.8 V internal core supply. RAM, PMU0 and the SmaRTClock are always powered directly from the  $V_{DD}$  pin in sleep mode and powered from the core supply in all other power modes.

Figure 15.1. C8051F99x-C8051F98x Power Distribution

#### 18.2. Power-Fail Reset

C8051F99x-C8051F98x devices have a V<sub>DD</sub> Supply Monitor that is enabled and selected as a reset source after each power-on or power-fail reset. When enabled and selected as a reset source, any power down transition or power irregularity that causes V<sub>DD</sub> to drop below V<sub>RST</sub> will cause the RST pin to be driven low and the CIP-51 will be held in a reset state (see Figure 18.2). When V<sub>DD</sub> returns to a level above V<sub>RST</sub>, the CIP-51 will be released from the reset state.

After a power-fail reset, the PORSF flag reads 1, the contents of RAM invalid, and the  $V_{DD}$  supply monitor is enabled and selected as a reset source. The enable state of the  $V_{DD}$  supply monitor and its selection as a reset source is only altered by power-on and power-fail resets. For example, if the  $V_{DD}$  supply monitor is de-selected as a reset source and disabled by software, then a software reset is performed, the  $V_{DD}$  supply monitor will remain disabled and de-selected after the reset.

In battery-operated systems, the contents of RAM can be preserved near the end of the battery's usable life if the device is placed in Sleep Mode prior to a power-fail reset occurring. When the device is in Sleep Mode, the power-fail reset is automatically disabled and the contents of RAM are preserved as long as  $V_{DD}$  does not fall below  $V_{POR}$ . A large capacitor can be used to hold the power supply voltage above  $V_{POR}$  while the user is replacing the battery. Upon waking from Sleep mode, the enable and reset source select state of the  $V_{DD}$  supply monitor are restored to the value last set by the user.

To allow software early notification that a power failure is about to occur, the VDDOK bit is cleared when the  $V_{DD}$  supply falls below the  $V_{WARN}$  threshold. The VDDOK bit can be configured to generate an interrupt. See Section "13. Interrupt Handler" on page 138 for more details.

Important Note: To protect the integrity of Flash contents, the V<sub>DD</sub> supply monitor must be enabled and selected as a reset source if software contains routines which erase or write Flash memory. If the V<sub>DD</sub> supply monitor is not enabled, any erase or write performed on Flash memory will cause a Flash Error device reset.

#### Important Notes:

- The Power-on Reset (POR) delay is not incurred after a V<sub>DD</sub> supply monitor reset. See Section

"4. Electrical Characteristics" on page 48 for complete electrical characteristics of the V<sub>DD</sub> monitor.

- Software should take care not to inadvertently disable the V<sub>DD</sub> Monitor as a reset source when writing to RSTSRC to enable other reset sources or to trigger a software reset. All writes to RSTSRC should explicitly set PORSF to 1 to keep the V<sub>DD</sub> Monitor enabled as a reset source.

- The V<sub>DD</sub> supply monitor must be enabled before selecting it as a reset source. Selecting the V<sub>DD</sub> supply monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V<sub>DD</sub> supply monitor and selecting it as a reset source. See Section "4. Electrical Characteristics" on page 48 for minimum V<sub>DD</sub> Supply Monitor turn-on time. No delay should be introduced in systems where software contains routines that erase or write Flash memory. The procedure for enabling the V<sub>DD</sub> supply monitor and selecting it as a reset source is shown below:

- 1. Enable the  $V_{DD}$  Supply Monitor (VDMEN bit in VDM0CN = 1).

- 2. Wait for the V<sub>DD</sub> Supply Monitor to stabilize (optional).

- 3. Select the  $V_{DD}$  Supply Monitor as a reset source (PORSF bit in RSTSRC = 1).

### 18.4. Missing Clock Detector Reset

The missing clock detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The missing clock detector reset is automatically disabled when the device is in the low power suspend or sleep mode. Upon exit from either low power state, the enabled/disabled state of this reset source is restored to its previous value. The state of the RST pin is unaffected by this reset.

### 18.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The Comparator0 reset source remains functional even when the device is in the low power <u>susp</u>end and sleep states as long as Comparator0 is also enabled as a wake-up source. The state of the RST pin is unaffected by this reset.

### 18.6. PCA Watchdog Timer Reset

The programmable watchdog timer (WDT) function of the programmable counter array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "26.4. Watchdog Timer Mode" on page 311; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The PCA Watchdog Timer reset source is automatically disabled when the device is in the low power suspend or sleep mode. Upon exit from either low power state, the enabled/disabled state of this reset source is restored to its previous value. The state of the RST pin is unaffected by this reset.

### 18.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above the Lock Byte address.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above the Lock Byte address.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above the Lock Byte address.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "14.3. Security Options" on page 152).

- A Flash write or erase is attempted while the V<sub>DD</sub> Monitor is disabled.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

### 19.1. Programmable Precision Internal Oscillator

All C8051F99x-C8051F98x devices include a programmable precision internal oscillator that may be selected as the system clock. OSCICL is factory calibrated to obtain a 24.5 MHz frequency. See Section "4. Electrical Characteristics" on page 48 for complete oscillator specifications.

The precision oscillator supports a spread spectrum mode which modulates the output frequency in order to reduce the EMI generated by the system. When enabled (SSE = 1), the oscillator output frequency is modulated by a stepped triangle wave whose frequency is equal to the oscillator frequency divided by 384 (63.8 kHz using the factory calibration). The deviation from the nominal oscillator frequency is +0%, -1.6%, and the step size is typically 0.26% of the nominal frequency. When using this mode, the typical average oscillator frequency is lowered from 24.5 MHz to 24.3 MHz.

**Important Note**: The precision internal oscillator may potentially lock up after exiting Sleep mode. Systems using Sleep Mode should switch to the low power oscillator prior to entering Sleep Mode:

- 1. Switch the system clock to the low power oscillator (CLKSEL = 0x04).

- 2. Turn off the Precision Oscillator (OSCICN &= ~0x80).

- 3. Enter Sleep.

- 4. Exit Sleep.

- 5. Turn on the Precision Oscillator (OSCICN |= 0x80).

- 6. Switch the system clock to the Precision Oscillator (CLKSEL = 0x00).

#### 19.2. Low Power Internal Oscillator

All C8051F99x-C8051F98x devices include a low power internal oscillator that defaults as the system clock after a system reset. The low power internal oscillator frequency is 20 MHz  $\pm$  10% and is automatically enabled when selected as the system clock and disabled when not in use. See Section "4. Electrical Characteristics" on page 48 for complete oscillator specifications.

### **19.3. External Oscillator Drive Circuit**

All C8051F99x-C8051F98x devices include an external oscillator circuit that may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. Figure 19.1 shows a block diagram of the four external oscillator options. The external oscillator is enabled and configured using the OSCXCN register.

The external oscillator output may be selected as the system clock or used to clock some of the digital peripherals (e.g., Timers, PCA, etc.). See the data sheet chapters for each digital peripheral for details. See Section "4. Electrical Characteristics" on page 48 for complete oscillator specifications.

#### 19.3.1. External Crystal Mode

If a crystal or ceramic resonator is used as the external oscillator, the crystal/resonator and a 10 M $\Omega$  resistor must be wired across the XTAL1 and XTAL2 pins as shown in Figure 19.1, Option 1. Appropriate loading capacitors should be added to XTAL1 and XTAL2, and both pins should be configured for analog I/O with the digital output drivers disabled.

Figure 19.2 shows the external oscillator circuit for a 20 MHz quartz crystal with a manufacturer recommended load capacitance of 12.5 pF. Loading capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins. The total value of the each loading capacitor and the stray capacitance of each XTAL pin should equal 12.5 pF x 2 = 25 pF. With a stray capacitance of 10 pF per pin, the 15 pF capacitors yield an equivalent series capacitance of 12.5 pF across the crystal.

**Note:** The recommended load capacitance depends upon the crystal and the manufacturer. Please refer to the crystal data sheet when completing these calculations.

#### 20.3.3. Software Considerations for using the SmaRTClock Timer and Alarm

The SmaRTClock timer and alarm have two operating modes to suit varying applications. The two modes are described below:

#### Mode 1:

The first mode uses the SmaRTClock timer as a perpetual timebase which is never reset to zero. Every 36 hours, the timer is allowed to overflow without being stopped or disrupted. The alarm interval is software managed and is added to the ALRMn registers by software after each alarm. This allows the alarm match value to always stay ahead of the timer by one software managed interval. If software uses 32-bit unsigned addition to increment the alarm match value, then it does not need to handle overflows since both the timer and the alarm match value will overflow in the same manner.

This mode is ideal for applications which have a long alarm interval (e.g., 24 or 36 hours) and/or have a need for a perpetual timebase. An example of an application that needs a perpetual timebase is one whose wake-up interval is constantly changing. For these applications, software can keep track of the number of timer overflows in a 16-bit variable, extending the 32-bit (36 hour) timer to a 48-bit (272 year) perpetual timebase.

#### Mode 2:

The second mode uses the SmaRTClock timer as a general purpose up counter which is auto reset to zero by hardware after each alarm. The alarm interval is managed by hardware and stored in the ALRMn registers. Software only needs to set the alarm interval once during device initialization. After each alarm, software should keep a count of the number of alarms that have occurred in order to keep track of time.

This mode is ideal for applications that require minimal software intervention and/or have a fixed alarm interval. This mode is the most power efficient since it requires less CPU time per alarm.

## 21.5. Special Function Registers for Accessing and Configuring Port I/O

All Port I/O are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

Each Port has a corresponding PnSKIP register which allows its individual Port pins to be assigned to digital functions or skipped by the Crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions such as the EMIF should have their PnSKIP bit set to 1.

The Port input mode of the I/O pins is defined using the Port Input Mode registers (PnMDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is P2.7, which can only be used for digital I/O.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings.

The drive strength of the output drivers are controlled by the Port Drive Strength (PnDRV) registers. The default is low drive strength. See Section "4. Electrical Characteristics" on page 48 for the difference in output drive strength between the two modes.

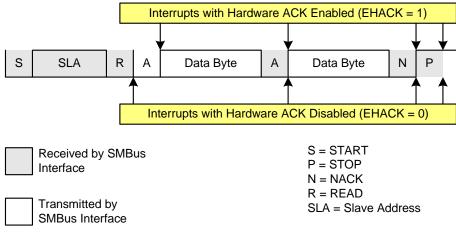

#### 22.5.4. Read Sequence (Slave)

During a read sequence, an SMBus master reads data from a slave device. The slave in this transfer will be a receiver during the address byte, and a transmitter during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are transmitted. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters Slave Transmitter Mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (Note: an error condition may be generated if SMB0DAT is written following a received NACK while in Slave Transmitter Mode). The interface exits Slave Transmitter Mode after receiving a STOP. Note that the interface will switch to Slave Receiver Mode if SMB0DAT is not written following a received are shown, though any number of bytes may be transmitted. Notice that all of the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode, regardless of whether hardware ACK generation is enabled.

Figure 22.8. Typical Slave Read Sequence

## 22.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMBOCN register. The appropriate actions to take in response to an SMBus event depend on whether hardware slave address recognition and ACK generation is enabled or disabled. Table 22.5 describes the typical actions when hardware slave address recognition and ACK generation is disabled. Table 22.6 describes the typical actions when hardware slave address recognition and ACK generation is enabled. In the tables, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. The shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed by hardware but do not conform to the SMBus specification.

## C2 Register Definition 27.4. FPCTL: C2 Flash Programming Control

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|-----|---|---|---|---|---|---|--|

| Name  | FPCTL[7:0] |     |   |   |   |   |   |   |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |

C2 Address: 0x02

| Bit | Name       | Function                                                                                                                                                                                                                                                                    |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FPCTL[7:0] | Flash Programming Control Register.                                                                                                                                                                                                                                         |

|     |            | This register is used to enable Flash programming via the C2 interface. To enable C2 Flash programming, the following codes must be written in order: 0x02, 0x01. Note that once C2 Flash programming is enabled, a system reset must be issued to resume normal operation. |

## C2 Register Definition 27.5. FPDAT: C2 Flash Programming Data

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | FPDAT[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

C2 Address: 0xB4

| Bit | Name       | Function                                                                                                                     |                   |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 7:0 | FPDAT[7:0] | C2 Flash Programming Data Register.                                                                                          |                   |

|     |            | This register is used to pass Flash commands, addresses, and data during C2 Flash accesses. Valid commands are listed below. |                   |

|     |            | Code                                                                                                                         | Command           |

|     |            | 0x06                                                                                                                         | Flash Block Read  |

|     |            | 0x07                                                                                                                         | Flash Block Write |

|     |            | 0x08                                                                                                                         | Flash Page Erase  |

|     |            | 0x03                                                                                                                         | Device Erase      |

oscillator while in Sleep mode.

- Added a note to "15.5. Sleep Mode" and SFR Definition "15.3. Stop Mode" regarding not disabling the POR Supply Monitor while operating above 2.4 V.

- Adjusted QFN20 c, D2, and E2 package specifications in Table 3.2.