# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

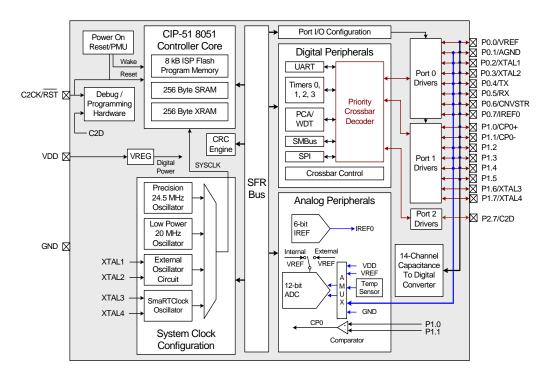

| Core Processor             | CIP-51 8051                                                       |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, POR, PWM, WDT                  |

| Number of I/O              | 17                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 512 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                    |

| Supplier Device Package    | 24-QSOP                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f997-c-gur |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

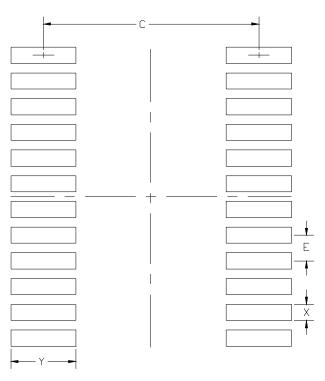

#### Table 3.7. PCB Land Pattern

| Dimension | MIN       | MAX  |  |  |  |

|-----------|-----------|------|--|--|--|

| С         | 5.20 5.30 |      |  |  |  |

| E         | 0.635 BSC |      |  |  |  |

| X         | 0.30      | 0.40 |  |  |  |

| Y         | 1.50      | 1.60 |  |  |  |

#### Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

3. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

#### Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

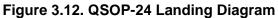

#### Table 4.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameters               | Conditions                                        | Min                   | Тур       | Max          | Units |

|--------------------------|---------------------------------------------------|-----------------------|-----------|--------------|-------|

| Output High Voltage      | High Drive Strength, PnDRV.n = 1                  |                       |           |              | V     |

|                          | IOH = –3 mA, Port I/O push-pull                   | V <sub>DD</sub> – 0.7 | _         |              |       |

|                          | IOH = −10 µA, Port I/O push-pull                  | V <sub>DD</sub> – 0.1 | —         | _            |       |

|                          | IOH = –10 mA, Port I/O push-pull                  |                       | See Chart |              |       |

|                          | Low Drive Strength, PnDRV.n = 0                   |                       |           |              |       |

|                          | IOH = −1 mA, Port I/O push-pull                   | V <sub>DD</sub> – 0.7 | —         | —            |       |

|                          | IOH = −10 μA, Port I/O push-pull                  | V <sub>DD</sub> – 0.1 | —         | —            |       |

|                          | IOH = -3 mA, Port I/O push-pull                   | _                     | See Chart | _            |       |

| Output Low Voltage       | High Drive Strength, PnDRV.n = 1                  |                       |           |              | V     |

|                          | I <sub>OL</sub> = 8.5 mA                          | _                     | _         | 0.6          |       |

|                          | I <sub>OL</sub> = 10 μA                           | —                     | —         | 0.1          |       |

|                          | I <sub>OL</sub> = 25 mA                           | —                     | See Chart | _            |       |

|                          | Low Drive Strength, PnDRV.n = 0                   |                       |           |              |       |

|                          | I <sub>OL</sub> = 1.4 mA                          | —                     | —         | 0.6          |       |

|                          | I <sub>OL</sub> = 10 μA                           | —                     | —         | 0.1          |       |

|                          | I <sub>OL</sub> = 4 mA                            | _                     | See Chart | —            |       |

| Input High Voltage       | V <sub>DD</sub> = 2.0 to 3.6 V                    | V <sub>DD</sub> - 0.6 | _         | _            | V     |

|                          | V <sub>DD</sub> = 0.9 to 2.0 V                    | 0.7 x VDD             | —         | —            | V     |

| Input Low Voltage        | V <sub>DD</sub> = 2.0 to 3.6 V                    | —                     | —         | 0.6          | V     |

|                          | V <sub>DD</sub> = 0.9 to 2.0 V                    | —                     | —         | 0.3 x<br>VDD | V     |

|                          | Weak Pullup Off                                   | —                     | —         | ±1           | μA    |

| Input Leakage<br>Current | Weak Pullup On, $V_{IN} = 0 V$ , $V_{DD} = 1.8 V$ | —                     | 4         | —            |       |

|                          | Weak Pullup On, Vin = 0 V, $V_{DD}$ = 3.6 V       | —                     | 20        | 35           |       |

### SFR Definition 5.13. TOFFH: ADC0 Data Word High Byte

| Bit   | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |

|-------|-----------|--------|--------|--------|--------|--------|--------|--------|--|

| Name  | TOFF[9:2] |        |        |        |        |        |        |        |  |

| Туре  | R         | R      | R      | R      | R      | R      | R      | R      |  |

| Reset | Varies    | Varies | Varies | Varies | Varies | Varies | Varies | Varies |  |

SFR Page = 0xF; SFR Address = 0x8E

| Bit | Name      | Function                                                                   |

|-----|-----------|----------------------------------------------------------------------------|

| 7:0 | TOFF[9:2] | Temperature Sensor Offset High Bits.                                       |

|     |           | Most Significant Bits of the 10-bit temperature sensor offset measurement. |

### SFR Definition 5.14. TOFFL: ADC0 Data Word Low Byte

| Bit   | 7         | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|--------|---|---|---|---|---|---|

| Name  | TOFF[1:0] |        |   |   |   |   |   |   |

| Туре  | R         | R      | R | R | R | R | R | R |

| Reset | Varies    | Varies | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0x8D

| Bit | Name      | Function                                                                    |

|-----|-----------|-----------------------------------------------------------------------------|

| 7:6 | TOFF[1:0] | Temperature Sensor Offset Low Bits.                                         |

|     |           | Least Significant Bits of the 10-bit temperature sensor offset measurement. |

| 5:0 | Unused    | Read = 0; Write = Don't Care.                                               |

### SFR Definition 5.15. REF0CN: Voltage Reference Control

| Bit   | 7 | 6 | 5      | 4     | 3   | 2     | 1 | 0 |

|-------|---|---|--------|-------|-----|-------|---|---|

| Name  |   |   | REFGND | REFSL |     | TEMPE |   |   |

| Туре  | R | R | R/W    | R/W   | R/W | R/W   | R | R |

| Reset | 0 | 0 | 0      | 1     | 1   | 0     | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xD1

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                     |

| 5   | REFGND | <ul> <li>Analog Ground Reference.</li> <li>Selects the ADC0 ground reference.</li> <li>0: The ADC0 ground reference is the GND pin.</li> <li>1: The ADC0 ground reference is the P0.1/AGND pin.</li> </ul>                                                                                                                                                                                          |

| 4:3 | REFSL  | <ul> <li>Voltage Reference Select.</li> <li>Selects the ADC0 voltage reference.</li> <li>00: The ADC0 voltage reference is the P0.0/VREF pin.</li> <li>01: The ADC0 voltage reference is the VDD pin.</li> <li>10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage.</li> <li>11: The ADC0 voltage reference is the internal 1.65 V high speed voltage reference.</li> </ul> |

| 2   | TEMPE  | Temperature Sensor Enable.Enables/Disables the internal temperature sensor.0: Temperature Sensor Disabled.1: Temperature Sensor Enabled.                                                                                                                                                                                                                                                            |

| 1:0 | Unused | Read = 00b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                     |

### 5.14. Voltage Reference Electrical Specifications

See Table 4.12 on page 61 for detailed Voltage Reference Electrical Specifications.

## SFR Definition 7.1. CPT0CN: Comparator 0 Control

| Bit   | 7     | 6      | 5             | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|---------------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | <b>CP0RIF</b> | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W           | R/W    | R/W         |   | R/W         |   |

| Reset | 0     | 0      | 0             | 0      | 0           | 0 | 0           | 0 |

#### SFR Page= 0x0; SFR Address = 0x9B

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0                                                      |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3-2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = Hysteresis 1.                                       |

|     |             | 10: Positive Hysteresis = Hysteresis 2.                                       |

|     |             | 11: Positive Hysteresis = Hysteresis 3 (Maximum).                             |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = Hysteresis 1.                                       |

|     |             | 10: Negative Hysteresis = Hysteresis 2.                                       |

|     |             | 11: Negative Hysteresis = Hysteresis 3 (Maximum).                             |

## SFR Definition 7.2. CPT0MD: Comparator 0 Mode Selection

| Bit   | 7   | 6 | 5      | 4      | 3 | 2 | 1          | 0 |

|-------|-----|---|--------|--------|---|---|------------|---|

| Name  |     |   | CP0RIE | CP0FIE |   |   | CP0MD[1:0] |   |

| Туре  | R/W | R | R/W    | R/W    | R | R | R/W        |   |

| Reset | 1   | 0 | 0      | 0      | 0 | 0 | 1          | 0 |

## SFR Page = 0x0; SFR Address = 0x9D

| Bit | Name       | Function                                                                                                                                                                                                                                                           |  |  |  |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | Reserved   | Read = 1b, Must Write 1b.                                                                                                                                                                                                                                          |  |  |  |  |

| 6   | Unused     | Read = 0b, Write = don't care.                                                                                                                                                                                                                                     |  |  |  |  |

| 5   | CPORIE     | Comparator0 Rising-Edge Interrupt Enable.<br>0: Comparator0 Rising-edge interrupt disabled.<br>1: Comparator0 Rising-edge interrupt enabled.                                                                                                                       |  |  |  |  |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.<br>0: Comparator0 Falling-edge interrupt disabled.<br>1: Comparator0 Falling-edge interrupt enabled.                                                                                                                    |  |  |  |  |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                    |  |  |  |  |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |  |  |  |  |

## SFR Definition 9.3. SP: Stack Pointer

| Bit                                | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------|-----------------|---|---|---|---|---|---|---|

| Name                               | SP[7:0]         |   |   |   |   |   |   |   |

| Туре                               | R/W             |   |   |   |   |   |   |   |

| Reset                              | 0 0 0 0 0 1 1 1 |   |   |   |   |   |   |   |

| SFR Page = All; SFR Address = 0x81 |                 |   |   |   |   |   |   |   |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

### SFR Definition 9.4. ACC: Accumulator

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------|---|---|---|---|---|---|---|

| Name  | ACC[7:0]        |   |   |   |   |   |   |   |

| Туре  | R/W             |   |   |   |   |   |   |   |

| Reset | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

|       |                 |   |   |   |   |   |   |   |

SFR Page = All; SFR Address = 0xE0; Bit-Addressable

| Bit | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

#### SFR Definition 9.5. B: B Register

| Bit   | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---|---|---|---|---|---|---|

| Name  | B[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W    |   |   |   |   |   |   |   |

| Reset | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = All; SFR Address = 0xF0; Bit-Addressable

| Bit | Name   | Function                                                                        |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

### SFR Definition 13.5. EIE2: Extended Interrupt Enable 2

| Bit   | 7   | 6      | 5     | 4      | 3 | 2      | 1    | 0     |

|-------|-----|--------|-------|--------|---|--------|------|-------|

| Name  |     | ECSEOS | ECSDC | ECSCPT |   | ERTC0F | EMAT | EWARN |

| Туре  | R/W | R/W    | R/W   | R/W    | R | R/W    | R/W  | R/W   |

| Reset | 0   | 0      | 0     | 0      | 0 | 0      | 0    | 0     |

#### SFR Page = All;SFR Address = 0xE7

| Bit | Name   | Function                                                                                                                                                                                                                                                                                    |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused | Read = 0b. Write = Don't care.                                                                                                                                                                                                                                                              |

| 6   | ECSEOS | Enable Capacitive Sense End of Scan Interrupt.<br>0: Disable Capacitive Sense End of Scan interrupt.<br>1: Enable interrupt requests generated by CS0EOS.                                                                                                                                   |

| 5   | ECSDC  | Enable Capacitive Sense Digital Comparator Interrupt.<br>0: Disable Capacitive Sense Digital Comparator interrupt.<br>1: Enable interrupt requests generated by CS0CMPF.                                                                                                                    |

| 4   | ECSCPT | <ul> <li>Enable Capacitive Sense Conversion Complete Interrupt.</li> <li>0: Disable Capacitive Sense Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by CS0INT.</li> </ul>                                                                                   |

| 3   | Unused | Read = 0b. Write = Don't care.                                                                                                                                                                                                                                                              |

| 2   | ERTC0F | <ul> <li>Enable SmaRTClock Oscillator Fail Interrupt.</li> <li>This bit sets the masking of the SmaRTClock Alarm interrupt.</li> <li>0: Disable SmaRTClock Alarm interrupts.</li> <li>1: Enable interrupt requests generated by SmaRTClock Alarm.</li> </ul>                                |

| 1   | EMAT   | <ul> <li>Enable Port Match Interrupts.</li> <li>This bit sets the masking of the Port Match Event interrupt.</li> <li>0: Disable all Port Match interrupts.</li> <li>1: Enable interrupt requests generated by a Port Match.</li> </ul>                                                     |

| 0   | EWARN  | <ul> <li>Enable Supply Monitor Early Warning Interrupt.</li> <li>This bit sets the masking of the Supply Monitor Early Warning interrupt.</li> <li>0: Disable the Supply Monitor Early Warning interrupt.</li> <li>1: Enable interrupt requests generated by the Supply Monitor.</li> </ul> |

### 13.6. External Interrupts INT0 and INT1

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INT0 Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "25.1. Timer 0 and Timer 1" on page 280) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 13.7). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register PnSKIP (see Section "21.3. Priority Crossbar Decoder" on page 219 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

#### 14.1.2. Flash Erase Procedure

The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire Flash page, perform the following steps:

- 1. Save current interrupt state and disable interrupts.

- 2. Set the PSEE bit (register PSCTL).

- 3. Set the PSWE bit (register PSCTL).

- 4. Write the first key code to FLKEY: 0xA5.

- 5. Write the second key code to FLKEY: 0xF1.

- 6. Using the MOVX instruction, write a data byte to any location within the page to be erased.

- 7. Clear the PSWE and PSEE bits.

- 8. Restore previous interrupt state.

Steps 4–6 must be repeated for each 512-byte page to be erased.

#### Notes:

- 1. Flash security settings may prevent erasure of some Flash pages, such as the reserved area and the page containing the lock bytes. For a summary of Flash security settings and restrictions affecting Flash erase operations, please see Section "14.3. Security Options" on page 152.

- 2. 8-bit MOVX instructions cannot be used to erase or write to Flash memory at addresses higher than 0x00FF.

#### 14.1.3. Flash Write Procedure

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. A byte location to be programmed should be erased before a new value is written.

The recommended procedure for writing a single byte in Flash is as follows:

- 1. Save current interrupt state and disable interrupts.

- 2. Ensure that the Flash byte has been erased (has a value of 0xFF).

- 3. Set the PSWE bit (register PSCTL).

- 4. Clear the PSEE bit (register PSCTL).

- 5. Write the first key code to FLKEY: 0xA5.

- 6. Write the second key code to FLKEY: 0xF1.

- 7. Using the MOVX instruction, write a single data byte to the desired location within the 1024-byte sector.

- 8. Clear the PSWE bit.

- 9. Restore previous interrupt state.

Steps 5–7 must be repeated for each byte to be written.

#### Notes:

- 1. Flash security settings may prevent writes to some areas of Flash, such as the reserved area. For a summary of Flash security settings and restrictions affecting Flash write operations, please see Section "14.3. Security Options" on page 152.

- 2. 8-bit MOVX instructions cannot be used to erase or write to Flash memory at addresses higher than 0x00FF.

#### 14.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. MOVX read instructions always target XRAM.

#### 19.3.2. External RC Mode

If an RC network is used as the external oscillator, the circuit should be configured as shown in Figure 19.1, Option 2. The RC network should be added to XTAL2, and XTAL2 should be configured for analog I/O with the digital output drivers disabled. XTAL1 is not affected in RC mode.

The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. The resistor should be no smaller than 10 k $\Omega$ . The oscillation frequency can be determined by the following equation:

$$f = \frac{1.23 \times 10^3}{\text{R} \times \text{C}}$$

where

f = frequency of clock in MHzR = pull-up resistor value in k $\Omega$ V<sub>DD</sub> = power supply voltage in VoltsC = capacitor value on the XTAL2 pin in pF

To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation. For example, if the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

$$f = \frac{1.23 \times 10^3}{\text{R} \times \text{C}} = \frac{1.23 \times 10^3}{246 \times 50} = 100 \text{ kHz}$$

where

$\begin{array}{ll} f = \mbox{frequency of clock in MHz} & R = \mbox{pull-up resistor value in } k\Omega \\ V_{DD} = \mbox{power supply voltage in Volts} & C = \mbox{capacitor value on the XTAL2 pin in pF} \end{array}$

Referencing Table 19.2, the recommended XFCN setting is 010.

| XFCN | Approximate<br>Frequency Range (RC<br>and C Mode) | K Factor (C Mode) | Typical Supply Current/ Actual<br>Measured Frequency<br>(C Mode, VDD = 2.4 V) |

|------|---------------------------------------------------|-------------------|-------------------------------------------------------------------------------|

| 000  | f ≤ 25 kHz                                        | K Factor = 0.87   | 3.0 µA, f = 11 kHz, C = 33 pF                                                 |

| 001  | 25 kHz < f ≤ 50 kHz                               | K Factor = 2.6    | 5.5 μA, f = 33 kHz, C = 33 pF                                                 |

| 010  | 50 kHz < f ≤ 100 kHz                              | K Factor = 7.7    | 13 μA, f = 98 kHz, C = 33 pF                                                  |

| 011  | 100 kHz < f ≤ 200 kHz                             | K Factor = 22     | 32 µA, f = 270 kHz, C = 33 pF                                                 |

| 100  | 200 kHz < f ≤ 400 kHz                             | K Factor = 65     | 82 μA, f = 310 kHz, C = 46 pF                                                 |

| 101  | 400 kHz < f ≤ 800 kHz                             | K Factor = 180    | 242 µA, f = 890 kHz, C = 46 pF                                                |

| 110  | 800 kHz < f ≤ 1.6 MHz                             | K Factor = 664    | 1.0 mA, f = 2.0 MHz, C = 46 pF                                                |

| 111  | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$         | K Factor = 1590   | 4.6 mA, f = 6.8 MHz, C = 46 pF                                                |

When the RC oscillator is first enabled, the external oscillator valid detector allows software to determine when oscillation has stabilized. The recommended procedure for starting the RC oscillator is as follows:

- 1. Configure XTAL2 for analog I/O and disable the digital output drivers.

- 2. Configure and enable the external oscillator.

- 3. Poll for XTLVLD  $\geq$  1.

- 4. Switch the system clock to the external oscillator.

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 22.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                                                          | Minimum SDA Setup Time             | Minimum SDA Hold Time |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                  | T <sub>low</sub> – 4 system clocks |                       |  |  |  |  |

| 0                                                                                                                                                                                                                                                                                                                | or                                 | 3 system clocks       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                  | 1 system clock + s/w delay*        |                       |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                | 11 system clocks                   | 12 system clocks      |  |  |  |  |

| *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                                    |                       |  |  |  |  |

Table 22.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "22.3.4. SCL Low Timeout" on page 238). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 22.4).

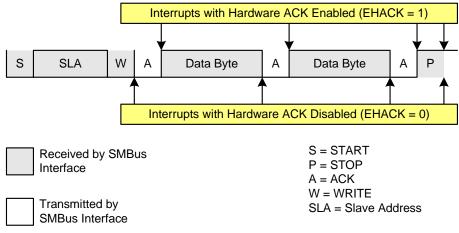

#### 22.5.3. Write Sequence (Slave)

During a write sequence, an SMBus master writes data to a slave device. The slave in this transfer will be a receiver during the address byte, and a receiver during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

The interface exits Slave Receiver Mode after receiving a STOP. Note that the interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 22.7 shows a typical slave write sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 22.7. Typical Slave Write Sequence

### SFR Definition 24.3. SPI0CKR: SPI0 Clock Rate

| Bit           | 7             | 6             | 5      | 4 | 3        | 2 | 1 | 0 |  |  |  |

|---------------|---------------|---------------|--------|---|----------|---|---|---|--|--|--|

| Name SCR[7:0] |               |               |        |   |          |   | I | I |  |  |  |

| Type R/W      |               |               |        |   |          |   |   |   |  |  |  |

| Reset         | 0             | 0 0 0 0 0 0 0 |        |   |          |   |   |   |  |  |  |

| SFR Pa        | ige = 0x0; SF | R Address =   | = 0xA2 |   | 1        |   |   |   |  |  |  |

| Bit           | Name          |               |        |   | Functior | า |   |   |  |  |  |

| 7:0           | SCR[7:0]      |               |        |   |          |   |   |   |  |  |  |

### SFR Definition 24.4. SPI0DAT: SPI0 Data

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | SPI0DAT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xA3

| Bit | Name         | Function                                                                                                                                                                                                                                     |  |  |  |  |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0 | SPI0DAT[7:0] | SPI0 Transmit and Receive Data.                                                                                                                                                                                                              |  |  |  |  |

|     |              | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer. |  |  |  |  |

### SFR Definition 25.2. TCON: Timer Control

| Bit   | 7                                                   | 6                                                                                                                                                                                                                                                                | 5                                                                                                                                                                             | 4               | 3        | 2   | 1   | 0   |  |  |

|-------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-----|-----|-----|--|--|

|       |                                                     | TR1                                                                                                                                                                                                                                                              | TF0                                                                                                                                                                           | TR0             | IE1      | IT1 | IE0 | ITO |  |  |

| Name  | ·                                                   |                                                                                                                                                                                                                                                                  |                                                                                                                                                                               |                 |          |     |     |     |  |  |

| Туре  | R/W                                                 | R/W                                                                                                                                                                                                                                                              | R/W                                                                                                                                                                           | R/W             | R/W      | R/W | R/W | R/W |  |  |

| Rese  | t 0                                                 | 0                                                                                                                                                                                                                                                                | 0                                                                                                                                                                             | 0               | 0        | 0   | 0   | 0   |  |  |

| SFR P | SFR Page = 0x0; SFR Address = 0x88; Bit-Addressable |                                                                                                                                                                                                                                                                  |                                                                                                                                                                               |                 |          |     |     |     |  |  |

| Bit   | Name                                                |                                                                                                                                                                                                                                                                  |                                                                                                                                                                               |                 | Function |     |     |     |  |  |

| 7     | TF1                                                 | Timer 1 Ov                                                                                                                                                                                                                                                       | erflow Flag                                                                                                                                                                   | •               |          |     |     |     |  |  |

|       |                                                     |                                                                                                                                                                                                                                                                  | Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine. |                 |          |     |     |     |  |  |

| 6     | TR1                                                 | Timer 1 Ru                                                                                                                                                                                                                                                       | n Control.                                                                                                                                                                    |                 |          |     |     |     |  |  |

|       |                                                     | Timer 1 is e                                                                                                                                                                                                                                                     | nabled by se                                                                                                                                                                  | etting this bit | to 1.    |     |     |     |  |  |

| 5     | TF0                                                 | Timer 0 Ov                                                                                                                                                                                                                                                       | erflow Flag                                                                                                                                                                   |                 |          |     |     |     |  |  |

|       |                                                     | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                    |                                                                                                                                                                               |                 |          |     |     |     |  |  |

| 4     | TR0                                                 | Timer 0 Ru                                                                                                                                                                                                                                                       | n Control.                                                                                                                                                                    |                 |          |     |     |     |  |  |

|       |                                                     | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                     |                                                                                                                                                                               |                 |          |     |     |     |  |  |

| 3     | IE1                                                 | External In                                                                                                                                                                                                                                                      | terrupt 1.                                                                                                                                                                    |                 |          |     |     |     |  |  |

|       |                                                     | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                          |                                                                                                                                                                               |                 |          |     |     |     |  |  |

| 2     | IT1                                                 | Interrupt 1                                                                                                                                                                                                                                                      | Interrupt 1 Type Select.                                                                                                                                                      |                 |          |     |     |     |  |  |

|       |                                                     | This bit selects whether the configured INT1 interrupt will be edge or level sensitive.<br>INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see SFR Definition 13.7).<br>0: INT1 is level triggered.<br>1: INT1 is edge triggered. |                                                                                                                                                                               |                 |          |     |     |     |  |  |

| 1     | IE0                                                 | External In                                                                                                                                                                                                                                                      | •                                                                                                                                                                             |                 |          |     |     |     |  |  |

|       |                                                     | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                          |                                                                                                                                                                               |                 |          |     |     |     |  |  |

| 0     | IT0                                                 | Interrupt 0 Type Select.                                                                                                                                                                                                                                         |                                                                                                                                                                               |                 |          |     |     |     |  |  |

|       |                                                     | This bit selects whether the configured INT0 interrupt will be edge or level sensitive.INT0 is configured active low or high by the IN0PL bit in register IT01CF (see SFRDefinition 13.7).0: INT0 is level triggered.1: INT0 is edge triggered.                  |                                                                                                                                                                               |                 |          |     |     |     |  |  |

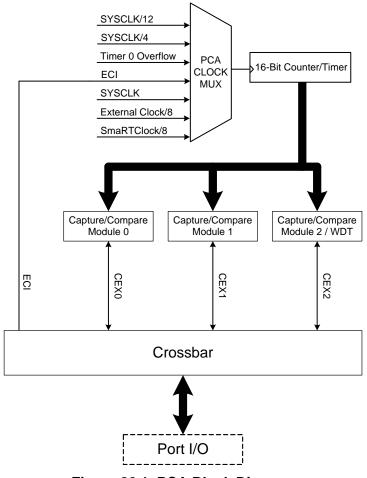

## 26. Programmable Counter Array

The programmable counter array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled. The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, SmaRTClock divided by 8, Timer 0 overflows, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8 to 11-Bit PWM, or 16-Bit PWM (each mode is described in Section "26.3. Capture/Compare Modules" on page 303). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 26.1

**Important Note:** The PCA Module 2 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section 26.4 for details.

Figure 26.1. PCA Block Diagram

## DOCUMENT CHANGE LIST

### Revision 0.3 to Revision 0.4

• QFN-20 package and landing diagram updated.

#### **Revision 0.4 to Revision 1.0**

- IREF0CF register description updated.

- Updated ADC0 Chapter Text.

- Corrected an error in the Product Selector Guide.

- Updated SmaRTClock chapter to indicate how the Alarm value should be set when using Auto Reset and the LFO.

- Updated electrical specifications to fill TBDs and updated power specifications based on Rev B characterization data.

- Added a note to the OSCICL register description.

- Added a note to the CRC0CN register description.

- Updated equation in the CRC0CNT register description.

- Updated Power On Reset description.

### Revision 1.0 to Revision 1.1

Removed references to AN338.

#### **Revision 1.1 to Revision 1.2**

- Removed QuickSense references.

- Updated part numbers to Revision C in "Ordering Information" on page 31 and added Figure 3.4, Figure 3.5, and Figure 3.6 to identify the silicon revision.

- Updated REVID register (SFR Definition 14.2) and REVID C2 register (C2 Register Definition 27.3) with the 0x02 value for Revision C.

- Updated Figure "7.3 CP0 Multiplexer Block Diagram" on page 98 to remove the bar over the CPnOUT signals.

- Updated the "Reset Sources" on page 181 chapter to reflect the correct state of the RST pin during power-on reset.

- Updated Figure "1.14 Port I/O Functional Block Diagram" on page 26 and Figure "21.1 Port I/O Functional Block Diagram" on page 215 to mention P1.4 is not available on 20-pin devices.

- Removed references to the EMI0CN register, which does not exist.

- Updated Figure "8.2 Auto-Scan Example" on page 103 to refer to the correct pins.

- Updated POR Monitor Threshold (V<sub>POR</sub>) Brownout Condition (VDD Falling) specification minimum, typical, and maximum values.

- Updated the reset value of the CLKSEL register (SFR Definition 19.1).

- Updated description of WEAKPUD in SFR Definition 21.3.

- Corrected SFR addresses for P0DRV (SFR Definition 21.12), P1DRV (SFR Definition 21.17), P2DRV (SFR Definition 21.20), PMU0MD (SFR Definition 15.3), FLSCL (SFR Definition 14.5), REF0CN (SFR Definition 5.15), CS0SCAN0 (SFR Definition 8.5), and CS0SCAN1 (SFR Definition 8.6).

- Replaced all instances of V<sub>BAT</sub> with V<sub>DD</sub>.

- Added a note to "11.1. Accessing XRAM", "15.5. Sleep Mode", and "18. Reset Sources" regarding an issue with the first address of XRAM.

- Added a note to "15.5. Sleep Mode" and "19. Clocking Sources" regarding using the internal low power