Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                     |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, POR, PWM, WDT                |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                            |

| Supplier Device Package    | 24-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f997-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 22.1. SMBus Clock Source Selection     24       Table 22.4. SMBus Clock Source Selection     24 |    |

|-------------------------------------------------------------------------------------------------------|----|

| Table 22.2. Minimum SDA Setup and Hold Times     24                                                   |    |

| Table 22.3. Sources for Hardware Changes to SMB0CN                                                    | 45 |

| Table 22.4. Hardware Address Recognition Examples (EHACK = 1)                                         | 46 |

| Table 22.5. SMBus Status Decoding With Hardware ACK Generation Disabled                               |    |

| (EHACK = 0)                                                                                           | 53 |

| Table 22.6. SMBus Status Decoding With Hardware ACK Generation Enabled                                |    |

| (EHACK = 1)                                                                                           | 55 |

| Table 23.1. Timer Settings for Standard Baud Rates                                                    |    |

| Using The Internal 24.5 MHz Oscillator                                                                | 64 |

| Table 23.2. Timer Settings for Standard Baud Rates                                                    |    |

| Using an External 22.1184 MHz Oscillator                                                              | 64 |

| Table 24.1. SPI Slave Timing Parameters                                                               | 77 |

| Table 25.1. Timer 0 Running Modes     28                                                              | 80 |

| Table 26.1. PCA Timebase Input Options                                                                | 01 |

| Table 26.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare                                  |    |

| Modules                                                                                               | 03 |

| Table 26.3. Watchdog Timer Timeout Intervals1                                                         | 12 |

### 5.2.4. Settling Time Requirements

A minimum amount of tracking time is required before each conversion can be performed, to allow the sampling capacitor voltage to settle. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For many applications, these three SAR clocks will meet the minimum tracking time requirements, and higher values for the external source impedance will increase the required tracking time.

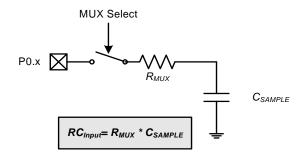

Figure 5.4 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 5.1. When measuring the Temperature Sensor output or  $V_{DD}$  with respect to GND,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 4.10 for ADC0 minimum settling time requirements as well as the mux impedance and sampling capacitor values.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL}C_{SAMPLE}$$

### Equation 5.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

*n* is the ADC resolution in bits (10).

Note: The value of CSAMPLE depends on the PGA Gain. See Table 4.10 for details.

# Figure 5.4. ADC0 Equivalent Input Circuits

# SFR Definition 5.10. ADC0LTH: ADC0 Less-Than High Byte

| Bit    | 7                                 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|--------|-----------------------------------|-------------|---|---|---|---|---|---|--|--|--|

| Name   |                                   | ADOLT[15:8] |   |   |   |   |   |   |  |  |  |

| Туре   |                                   | R/W         |   |   |   |   |   |   |  |  |  |

| Reset  | 0                                 | 0           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR Pa | FR Page = 0x0; SFR Address = 0xC6 |             |   |   |   |   |   |   |  |  |  |

| Bit    | Name Function                     |             |   |   |   |   |   |   |  |  |  |

| Bit | Name        | Function                                                               |

|-----|-------------|------------------------------------------------------------------------|

| 7:0 | AD0LT[15:8] | ADC0 Less-Than High Byte.                                              |

|     |             | Most Significant Byte of the 16-bit Less-Than window compare register. |

# SFR Definition 5.11. ADC0LTL: ADC0 Less-Than Low Byte

| Bit     | 7                                                                       | 6             | 5              | 4       | 3        | 2 | 1 | 0 |  |  |  |  |

|---------|-------------------------------------------------------------------------|---------------|----------------|---------|----------|---|---|---|--|--|--|--|

| Name    | ADOLT[7:0]                                                              |               |                |         |          |   |   |   |  |  |  |  |

| Туре    |                                                                         | R/W           |                |         |          |   |   |   |  |  |  |  |

| Reset   | 0 0 0 0 0 0 0 0                                                         |               |                |         |          |   |   |   |  |  |  |  |

| SFR Pa  | ge = 0x0; SFF                                                           | R Address =   | = 0xC5         |         |          |   |   |   |  |  |  |  |

| Bit     | Name                                                                    |               |                |         | Function | l |   |   |  |  |  |  |

| 7:0     | AD0LT[7:0]                                                              | ADC0 Le       | ss-Than Lo     | w Byte. |          |   |   |   |  |  |  |  |

|         | Least Significant Byte of the 16-bit Less-Than window compare register. |               |                |         |          |   |   |   |  |  |  |  |

| Note: I | n 8-bit mode, th                                                        | is register s | hould be set t | o 0x00. |          |   |   |   |  |  |  |  |

# SFR Definition 5.12. ADC0MX: ADC0 Input Channel Select

| Bit   | 7 | 6 | 5 | 4     | 3   | 2   | 1   | 0   |  |

|-------|---|---|---|-------|-----|-----|-----|-----|--|

| Name  |   |   |   | ADOMX |     |     |     |     |  |

| Туре  | R | R | R | R/W   | R/W | R/W | R/W | R/W |  |

| Reset | 0 | 0 | 0 | 1     | 1   | 1   | 1   | 1   |  |

#### SFR Page = 0x0; SFR Address = 0x96

| Bit | Name   |             | Fu                                      | nction        |                                |  |  |  |  |  |  |  |

|-----|--------|-------------|-----------------------------------------|---------------|--------------------------------|--|--|--|--|--|--|--|

| 7:5 | Unused | Read = 000  | Read = 000b; Write = Don't Care.        |               |                                |  |  |  |  |  |  |  |

| 4:0 | AD0MX  | AMUX0 Pos   | AMUX0 Positive Input Selection.         |               |                                |  |  |  |  |  |  |  |

|     |        | Selects the | positive input channel for AD           | CO.           |                                |  |  |  |  |  |  |  |

|     |        | 00000:      | Reserved.                               | 10000:        | Reserved.                      |  |  |  |  |  |  |  |

|     |        | 00001:      | P0.1                                    | 10001:        | Reserved.                      |  |  |  |  |  |  |  |

|     |        | 00010:      | P0.2                                    | 10010:        | Reserved.                      |  |  |  |  |  |  |  |

|     |        | 00011:      | P0.3                                    | 10011:        | Reserved.                      |  |  |  |  |  |  |  |

|     |        | 00100:      | P0.4                                    | 10100:        | Reserved.                      |  |  |  |  |  |  |  |

|     |        | 00101:      | P0.5                                    | P0.5 10101: F |                                |  |  |  |  |  |  |  |

|     |        | 00110:      | P0.6                                    | 10110:        | Reserved.                      |  |  |  |  |  |  |  |

|     |        | 00111:      | P0.7                                    | 10111:        | Reserved.                      |  |  |  |  |  |  |  |

|     |        | 01000:      | Reserved.                               | 11000:        | Reserved.                      |  |  |  |  |  |  |  |

|     |        | 01001:      | Reserved.                               | 11001:        | Reserved.                      |  |  |  |  |  |  |  |

|     |        | 01010:      | P1.2                                    | 11010:        | Reserved.                      |  |  |  |  |  |  |  |

|     |        | 01011:      | P1.3                                    | 11011:        | Temperature Sensor             |  |  |  |  |  |  |  |

|     |        | 01100:      | P1.4 (only available on 24-pin devices) | 11100:        | V <sub>DD</sub> Supply Voltage |  |  |  |  |  |  |  |

|     |        | 01101:      | Reserved.                               | 11101:        | Digital Supply Voltage         |  |  |  |  |  |  |  |

|     |        | 01110:      | Reserved.                               |               | (VREG0 Output, 1.7 V Typical)  |  |  |  |  |  |  |  |

|     |        | 01111:      | Reserved.                               | 11110:        | V <sub>DD</sub> Supply Voltage |  |  |  |  |  |  |  |

|     |        |             |                                         | 11111:        | Ground                         |  |  |  |  |  |  |  |

# SFR Definition 6.2. IREF0CF: Current Reference Configuration

| Bit   | 7     | 6   | 5   | 4   | 3   | 2          | 1 | 0 |

|-------|-------|-----|-----|-----|-----|------------|---|---|

| Name  | PWMEN |     |     |     |     | PWMSS[2:0] |   |   |

| Туре  | R/W   | R/W | R/W | R/W | R/W | R/W        |   |   |

| Reset | 0     | 0   | 0   | 0   | 0   | 0          | 0 | 0 |

#### SFR Page = All; SFR Address = 0xB9

| Bit | Name       | Function                                                                                                                |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------|

| 7   | PWMEN      | PWM Enhanced Mode Enable.                                                                                               |

|     |            | Enables the PWM Enhanced Mode.                                                                                          |

|     |            | 0: PWM Enhanced Mode disabled.                                                                                          |

|     |            | 1: PWM Enhanced Mode enabled.                                                                                           |

| 6:3 | Unused     | Read = 0000b, Write = don't care.                                                                                       |

| 2:0 | PWMSS[2:0] | PWM Source Select.                                                                                                      |

|     |            | Selects the PCA channel to use for the fine-tuning control signal.<br>000: CEX0 selected as fine-tuning control signal. |

|     |            | 001: CEX1 selected as fine-tuning control signal.                                                                       |

|     |            | 010: CEX2 selected as fine-tuning control signal.                                                                       |

|     |            | All Other Values: Reserved.                                                                                             |

# 6.2. IREF0 Specifications

See Table 4.13 on page 62 for a detailed listing of IREF0 specifications.

# 7. Comparator

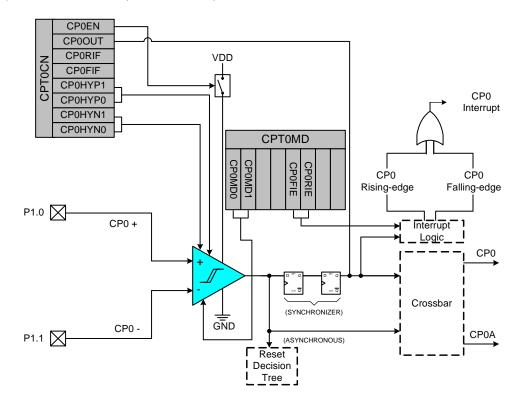

C8051F99x-C8051F98x devices include an on-chip programmable voltage comparator: Comparator 0 (CPT0) shown in Figure 7.1.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a digital synchronous "latched" output (CP0), or a digital asynchronous "raw" output (CP0A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output when the device is in some low power modes.

# 7.1. Comparator Inputs

Each Comparator performs an analog comparison of the voltage levels at its positive (CP0+) and negative (CP0-) input. The analog input multiplexers are completely under software control and configured using SFR registers. See Section "7.6. Comparator0 Analog Multiplexer" on page 98 for details on how to select and configure Comparator inputs.

**Important Note About Comparator Inputs:** The Port pins selected as Comparator inputs should be configured as analog inputs and skipped by the Crossbar. See the Port I/O chapter for more details on how to configure Port I/O pins as Analog Inputs. The Comparator may also be used to compare the logic level of digital signals, however, Port I/O pins configured as digital inputs must be driven to a valid logic state (HIGH or LOW) to avoid increased power consumption.

Figure 7.1. Comparator 0 Functional Block Diagram

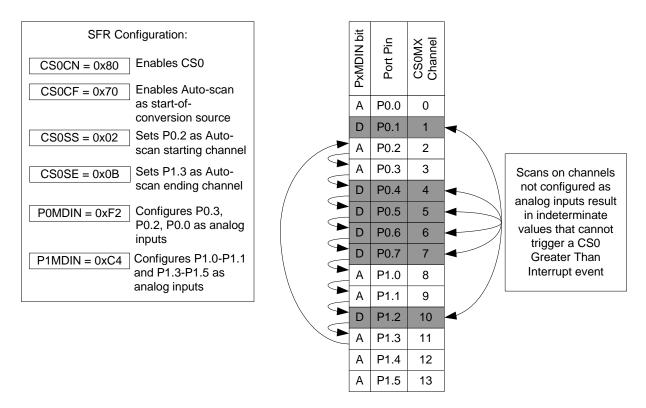

# 8.8. Automatic Scanning (Method 1—CS0SMEN = 0)

CS0 can be configured to automatically scan a sequence of contiguous CS0 input channels by configuring and enabling auto-scan. Using auto-scan with the CS0 comparator interrupt enabled allows a system to detect a change in measured capacitance without requiring any additional dedicated MCU resources.

Auto-scan is enabled by setting the CS0 start-of-conversion bits (CS0CF6:4) to 111b. After enabling autoscan, the starting and ending channels should be set to appropriate values in CS0SS and CS0SE, respectively. Writing to CS0SS when auto-scan is enabled will cause the value written to CS0SS to be copied into CS0MX. After being enabled, writing a 1 to CS0BUSY will start auto-scan conversions. When auto-scan completes the number of conversions defined in the CS0 accumulator bits (CS0CF1:0), autoscan configures CS0MX to the next sequential port pin configured as an analog input and begins a conversion on that channel. All other pins between CS0SS and CS0SE which are set as analog inputs are grounded during the conversion. This scan sequence continues until CS0MX reaches the ending input channel value defined in CS0SE. After one or more conversions have been taken at this channel, autoscan configures CS0MX back to the starting input channel. For an example system configured to use autoscan, please see Figure "8.2 Auto-Scan Example" on page 103.

**Note:** Auto-scan attempts one conversion on a CS0MX channel regardless of whether that channel's port pin has been configured as an analog input. Auto-scan will also complete the current rotation when the device is halted for debugging.

If auto-scan is enabled when the device enters suspend mode, auto-scan will remain enabled and running. This feature allows the device to wake from suspend through CS0 greater-than comparator event on any configured capacitive sense input included in the auto-scan sequence of inputs.

Figure 8.2. Auto-Scan Example

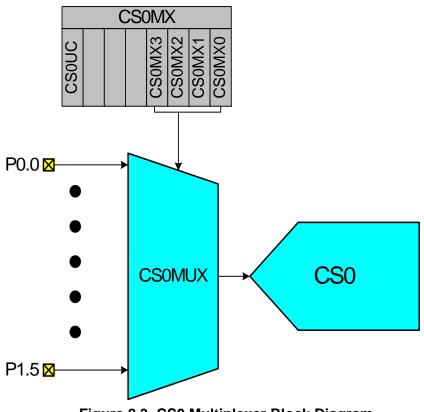

# 8.14. Capacitive Sense Multiplexer

The input multiplexer can be controlled through two methods. The CS0MX register can be written to through firmware, or the register can be configured automatically using the modules auto-scan functionality (see "8.8. Automatic Scanning (Method 1—CS0SMEN = 0)").

Figure 8.3. CS0 Multiplexer Block Diagram

| Mnemonic           | Description                                | Bytes | Clock<br>Cycles |

|--------------------|--------------------------------------------|-------|-----------------|

| CLR A              | Clear A                                    | 1     | 1               |

| CPL A              | Complement A                               | 1     | 1               |

| RL A               | Rotate A left                              | 1     | 1               |

| RLC A              | Rotate A left through Carry                | 1     | 1               |

| RR A               | Rotate A right                             | 1     | 1               |

| RRC A              | Rotate A right through Carry               | 1     | 1               |

| SWAP A             | Swap nibbles of A                          | 1     | 1               |

|                    | Data Transfer                              |       |                 |

| MOV A, Rn          | Move Register to A                         | 1     | 1               |

| MOV A, direct      | Move direct byte to A                      | 2     | 2               |

| MOV A, @Ri         | Move indirect RAM to A                     | 1     | 2               |

| MOV A, #data       | Move immediate to A                        | 2     | 2               |

| MOV Rn, A          | Move A to Register                         | 1     | 1               |

| MOV Rn, direct     | Move direct byte to Register               | 2     | 2               |

| MOV Rn, #data      | Move immediate to Register                 | 2     | 2               |

| MOV direct, A      | Move A to direct byte                      | 2     | 2               |

| MOV direct, Rn     | Move Register to direct byte               | 2     | 2               |

| MOV direct, direct | Move direct byte to direct byte            | 3     | 3               |

| MOV direct, @Ri    | Move indirect RAM to direct byte           | 2     | 2               |

| MOV direct, #data  | Move immediate to direct byte              | 3     | 3               |

| MOV @Ri, A         | Move A to indirect RAM                     | 1     | 2               |

| MOV @Ri, direct    | Move direct byte to indirect RAM           | 2     | 2               |

| MOV @Ri, #data     | Move immediate to indirect RAM             | 2     | 2               |

| MOV DPTR, #data16  | Load DPTR with 16-bit constant             | 3     | 3               |

| MOVC A, @A+DPTR    | Move code byte relative DPTR to A          | 1     | 3               |

| MOVC A, @A+PC      | Move code byte relative PC to A            | 1     | 3               |

| MOVX A, @Ri        | Move external data (8-bit address) to A    | 1     | 3               |

| MOVX @Ri, A        | Move A to external data (8-bit address)    | 1     | 3               |

| MOVX A, @DPTR      | Move external data (16-bit address) to A   | 1     | 3               |

| MOVX @DPTR, A      | Move A to external data (16-bit address)   | 1     | 3               |

| PUSH direct        | Push direct byte onto stack                | 2     | 2               |

| POP direct         | Pop direct byte from stack                 | 2     | 2               |

| XCH A, Rn          | Exchange Register with A                   | 1     | 1               |

| XCH A, direct      | Exchange direct byte with A                | 2     | 2               |

| XCH A, @Ri         | Exchange indirect RAM with A               | 1     | 2               |

| XCHD A, @Ri        | Exchange low nibble of indirect RAM with A | 1     | 2               |

|                    | Boolean Manipulation                       | I     | 1               |

| CLR C              | Clear Carry                                | 1     | 1               |

| CLR bit            | Clear direct bit                           | 2     | 2               |

| SETB C             | Set Carry                                  | 1     | 1               |

| SETB bit           | Set direct bit                             | 2     | 2               |

| CPL C              | Complement Carry                           | 1     | 1               |

| CPL bit            | Complement direct bit                      | 2     | 2               |

| ANL C, bit         | AND direct bit to Carry                    | 2     | 2               |

# Table 9.1. CIP-51 Instruction Set Summary (Continued)

#### Notes on Registers, Operands and Addressing Modes:

**Rn**—Register R0–R7 of the currently selected register bank.

@Ri—Data RAM location addressed indirectly through R0 or R1.

**rel**—8-bit, signed (twos complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct**—8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data—8-bit constant

#data16—16-bit constant

**bit**—Direct-accessed bit in Data RAM or SFR

**addr11**—11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16**—16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

# SFR Definition 13.2. IP: Interrupt Priority

| Bit    | 7             | 6                                                                          | 5                                                                                                                                                                                                  | 4                               | 3                           | 2             | 1   | 0   |  |  |  |  |  |

|--------|---------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------|---------------|-----|-----|--|--|--|--|--|

| Name   |               | PSPI0                                                                      | PT2                                                                                                                                                                                                | PS0                             | PT1                         | PX1           | PT0 | PX0 |  |  |  |  |  |

| Туре   | R             | R/W                                                                        | R/W                                                                                                                                                                                                | R/W                             | R/W                         | R/W           | R/W | R/W |  |  |  |  |  |

| Reset  | 1             | 0                                                                          | 0                                                                                                                                                                                                  | 0                               | 0                           | 0             | 0   | 0   |  |  |  |  |  |

| SFR Pa | age = All; \$ | SFR Address =                                                              | 0xB8; Bit-A                                                                                                                                                                                        | ddressable                      |                             |               |     |     |  |  |  |  |  |

| Bit    | Name          | Function                                                                   |                                                                                                                                                                                                    |                                 |                             |               |     |     |  |  |  |  |  |

| 7      | Unused        | Read = 1b, W                                                               | rite = don't c                                                                                                                                                                                     | care.                           |                             |               |     |     |  |  |  |  |  |

| 6      | PSPI0         | Serial Periph<br>This bit sets th<br>0: SPI0 interru<br>1: SPI0 interru    | ne priority of<br>opt set to lov                                                                                                                                                                   | the SPI0 int<br>v priority leve | errupt.<br>el.              | rity Control. |     |     |  |  |  |  |  |

| 5      | PT2           | Timer 2 Intern<br>This bit sets th<br>0: Timer 2 inter<br>1: Timer 2 inter | ne priority of<br>errupt set to                                                                                                                                                                    | the Timer 2<br>low priority le  | evel.                       |               |     |     |  |  |  |  |  |

| 4      | PS0           | UART0 Interr<br>This bit sets th<br>0: UART0 inte<br>1: UART0 inte         | ne priority of<br>rrupt set to                                                                                                                                                                     | the UART0<br>low priority le    | evel.                       |               |     |     |  |  |  |  |  |

| 3      | PT1           | Timer 1 Intern<br>This bit sets th<br>0: Timer 1 inte<br>1: Timer 1 inte   | ne priority of<br>errupt set to                                                                                                                                                                    | the Timer 1<br>low priority le  | evel.                       |               |     |     |  |  |  |  |  |

| 2      | PX1           | External Inter<br>This bit sets th<br>0: External Int<br>1: External Int   | ne priority of<br>errupt 1 set                                                                                                                                                                     | the Externa to low priorit      | l Interrupt 1 i<br>y level. | interrupt.    |     |     |  |  |  |  |  |

| 1      | PT0           | This bit sets th<br>0: Timer 0 inte                                        | Timer 0 Interrupt Priority Control.<br>This bit sets the priority of the Timer 0 interrupt.<br>0: Timer 0 interrupt set to low priority level.<br>1: Timer 0 interrupt set to high priority level. |                                 |                             |               |     |     |  |  |  |  |  |

| 0      | PX0           | External Inter<br>This bit sets th<br>0: External Int<br>1: External Int   | ne priority of<br>errupt 0 set                                                                                                                                                                     | the Externa to low priorit      | l Interrupt 0 i<br>y level. | interrupt.    |     |     |  |  |  |  |  |

# 14.5. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

To help prevent the accidental modification of Flash by firmware, the  $V_{DD}$  Monitor must be enabled and enabled as a reset source on C8051F99x-C8051F98x devices for the Flash to be successfully modified. If either the  $V_{DD}$  Monitor or the  $V_{DD}$  Monitor reset source is not enabled, a Flash Error Device Reset will be generated when the firmware attempts to modify the Flash.

The following guidelines are recommended for any system that contains routines which write or erase Flash from code.

#### 14.5.1. $V_{DD}$ Maintenance and the $V_{DD}$ Monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. Make certain that the minimum  $V_{DD}$  rise time specification of 1 ms is met. If the system cannot meet this rise time specification, then add an external  $V_{DD}$  brownout circuit to the RST pin of the device that holds the device in reset until  $V_{DD}$  reaches the minimum device operating voltage and re-asserts RST if  $V_{DD}$  drops below the minimum device operating voltage.

- 3. Keep the on-chip V<sub>DD</sub> Monitor enabled and enable the V<sub>DD</sub> Monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> Monitor and enabling the V<sub>DD</sub> Monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories website.

#### Notes:

- On C8051F99x-C8051F98x devices, both the V<sub>DD</sub> Monitor and the V<sub>DD</sub> Monitor reset source must be enabled to write or erase Flash without generating a Flash Error Device Reset.

- 2. On C8051F99x-C8051F98x devices, both the  $V_{DD}$  Monitor and the  $V_{DD}$  Monitor reset source are enabled by hardware after a power-on reset.

- 4. As an added precaution, explicitly enable the V<sub>DD</sub> Monitor and enable the V<sub>DD</sub> Monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> Monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct, but "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

# SFR Definition 15.4. PCON: Power Management Control Register

| Bit   | 7 | 6 | 5    | 4    | 3 | 2 | 1 | 0 |

|-------|---|---|------|------|---|---|---|---|

| Name  |   |   | STOP | IDLE |   |   |   |   |

| Туре  |   |   |      | W    | W |   |   |   |

| Reset | 0 | 0 | 0    | 0    | 0 | 0 | 0 | 0 |

SFR Page = All; SFR Address = 0x87

| Bit | Name    | Description           | Write                                     | Read                     |

|-----|---------|-----------------------|-------------------------------------------|--------------------------|

| 7:2 | GF[5:0] | General Purpose Flags | Sets the logic value.                     | Returns the logic value. |

| 1   | STOP    | Stop Mode Select      | Writing 1 places the device in Stop Mode. | N/A                      |

| 0   | IDLE    | Idle Mode Select      | Writing 1 places the device in Idle Mode. | N/A                      |

# 15.8. Power Management Specifications

See Table 4.5 on page 58 for detailed Power Management Specifications.

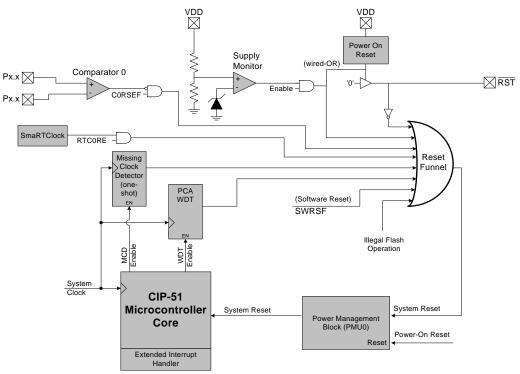

# 18. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled

All SFRs are reset to the predefined values noted in the SFR descriptions. The contents of RAM are unaffected during a reset; any previously stored data is preserved as long as power is not lost. Since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For power-on resets, the RST pin is high-impedance with the weak pull-up off until the device exits the reset state. For  $V_{DD}$  Monitor resets, the RST pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to an internal oscillator. Refer to Section "19. Clocking Sources" on page 188 for information on selecting and configuring the system clock source. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source (Section "26.4. Watchdog Timer Mode" on page 311 details the use of the Watchdog Timer). Program execution begins at location 0x0000.

**Important Note**: On device reset or upon waking up from Sleep mode, address 0x0000 of external memory may be overwritten by an indeterminate value. The indeterminate value is 0x00 in most situations. A dummy variable should be placed at address 0x0000 in external memory to ensure that the application firmware does not store any data that needs to be retained during sleep or reset at this memory location.

181

# 21.1.3. Interfacing Port I/O to 5 V Logic

All Port I/O have internal ESD protection diodes to prevent the pin voltage from exceeding the V<sub>DD</sub> supply. The Port I/O pins are not 5V tolerant and require level translators to interface to 5V logic.

#### 21.1.4. Increasing Port I/O Drive Strength

Port I/O output drivers support a high and low drive strength; the default is low drive strength. The drive strength of a Port I/O can be configured using the PnDRV registers. See Section "4. Electrical Characteristics" on page 48 for the difference in output drive strength between the two modes.

### 21.2. Assigning Port I/O Pins to Analog and Digital Functions

Port I/O pins P0.0–P1.7 can be assigned to various analog, digital, and external interrupt functions. The Port pins assuaged to analog functions should be configured for analog I/O and Port pins assuaged to digital or external interrupt functions should be configured for digital I/O.

#### 21.2.1. Assigning Port I/O Pins to Analog Functions

Table 21.1 shows all available analog functions that need Port I/O assignments. **Port pins selected for these analog functions should have their digital drivers disabled (PnMDOUT.n = 0 and Port Latch = 1) and their corresponding bit in PnSKIP set to 1.** This reserves the pin for use by the analog function and does not allow it to be claimed by the Crossbar. Table 21.1 shows the potential mapping of Port I/O to each analog function.

| Analog Function                      | Potentially<br>Assignable Port Pins | Registers used for<br>Assignment |

|--------------------------------------|-------------------------------------|----------------------------------|

| ADC Input                            | P0.1–P0.7, P1.2–P1.4                | ADC0MX, PnSKIP                   |

| Comparator0 Input                    | P1.0, P1.1                          | CPT0MX, PnSKIP                   |

| Voltage Reference (VREF0)            | P0.0                                | REF0CN, PnSKIP                   |

| Analog Ground Reference (AGND)       | P0.1                                | REF0CN, PnSKIP                   |

| Current Reference (IREF0)            | P0.7                                | IREF0CN, PnSKIP                  |

| External Oscillator Input (XTAL1)    | P0.2                                | OSCXCN, PnSKIP                   |

| External Oscillator Output (XTAL2)   | P0.3                                | OSCXCN, PnSKIP                   |

| SmaRTClock Oscillator Input (XTAL3)  | P1.6                                | RTC0CN, PnSKIP                   |

| SmaRTClock Oscillator Output (XTAL4) | P1.7                                | RTC0CN, PnSKIP                   |

#### Table 21.1. Port I/O Assignment for Analog Functions

# SFR Definition 21.12. P0DRV: Port0 Drive Strength

| Bit                                | 7    | 6           | 5 | 4    | 3      | 2 | 1 | 0 |

|------------------------------------|------|-------------|---|------|--------|---|---|---|

| Nam                                | 9    |             |   | P0DR | V[7:0] |   |   |   |

| Туре                               | •    | R/W         |   |      |        |   |   |   |

| Rese                               | t 0  | 0           | 0 | 0    | 0      | 0 | 0 | 0 |

| SFR Page = 0xF; SFR Address = 0x99 |      |             |   |      |        |   |   |   |

| Bit                                | Name | me Function |   |      |        |   |   |   |

| 2.0 | Hamo       | i unotioni                                                                                                                                                                                             |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0DRV[7:0] | Drive Strength Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P0.n Output has low output drive strength.<br>1: Corresponding P0.n Output has high output drive strength. |

#### 22.4.3. Hardware Slave Address Recognition

The SMBus hardware has the capability to automatically recognize incoming slave addresses and send an ACK without software intervention. Automatic slave address recognition is enabled by setting the EHACK bit in register SMB0ADM to 1. This will enable both automatic slave address recognition and automatic hardware ACK generation for received bytes (as a master or slave). More detail on automatic hardware ACK generation can be found in Section 22.4.2.2.

The registers used to define which address(es) are recognized by the hardware are the SMBus Slave Address register (SFR Definition 22.3) and the SMBus Slave Address Mask register (SFR Definition 22.4). A single address or range of addresses (including the General Call Address 0x00) can be specified using these two registers. The most-significant seven bits of the two registers are used to define which addresses will be ACKed. A 1 in bit positions of the slave address mask SLVM[6:0] enable a comparison between the received slave address and the hardware's slave address SLV[6:0] for those bits. A 0 in a bit of the slave address mask means that bit will be treated as a "don't care" for comparison purposes. In this case, either a 1 or a 0 value are acceptable on the incoming slave address (0x00). Table 22.4 shows some example parameter settings and the slave addresses that will be recognized by hardware under those conditions.

| Hardware Slave Address<br>SLV[6:0] | Slave Address Mask<br>SLVM[6:0] | GC bit | Slave Addresses Recognized by<br>Hardware |

|------------------------------------|---------------------------------|--------|-------------------------------------------|

| 0x34                               | 0x7F                            | 0      | 0x34                                      |

| 0x34                               | 0x7F                            | 1      | 0x34, 0x00 (General Call)                 |

| 0x34                               | 0x7E                            | 0      | 0x34, 0x35                                |

| 0x34                               | 0x7E                            | 1      | 0x34, 0x35, 0x00 (General Call)           |

| 0x70                               | 0x73                            | 0      | 0x70, 0x74, 0x78, 0x7C                    |

Table 22.4. Hardware Address Recognition Examples (EHACK = 1)

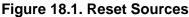

# 22.5.4. Read Sequence (Slave)

During a read sequence, an SMBus master reads data from a slave device. The slave in this transfer will be a receiver during the address byte, and a transmitter during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are transmitted. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters Slave Transmitter Mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (Note: an error condition may be generated if SMB0DAT is written following a received NACK while in Slave Transmitter Mode). The interface exits Slave Transmitter Mode after receiving a STOP. Note that the interface will switch to Slave Receiver Mode if SMB0DAT is not written following a received are shown, though any number of bytes may be transmitted. Notice that all of the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode, regardless of whether hardware ACK generation is enabled.

Figure 22.8. Typical Slave Read Sequence

# 22.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMBOCN register. The appropriate actions to take in response to an SMBus event depend on whether hardware slave address recognition and ACK generation is enabled or disabled. Table 22.5 describes the typical actions when hardware slave address recognition and ACK generation is disabled. Table 22.6 describes the typical actions when hardware slave address recognition and ACK generation is enabled. In the tables, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. The shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed by hardware but do not conform to the SMBus specification.

# C8051F99x-C8051F98x

# SFR Definition 23.2. SBUF0: Serial (UART0) Port Data Buffer

| Bit   | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | SBUF0[7:0] |     |     |     |     |     |     |     |

| Туре  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Page = 0x0; SFR Address = 0x99

| Bit | Name  | Function                                                                                                                                                                                                                                                                                                                    |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SBUF0 | Serial Data Buffer Bits 7:0 (MSB–LSB).                                                                                                                                                                                                                                                                                      |

|     |       | This SFR accesses two registers; a transmit shift register and a receive latch register.<br>When data is written to SBUF0, it goes to the transmit shift register and is held for<br>serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of<br>SBUF0 returns the contents of the receive latch. |

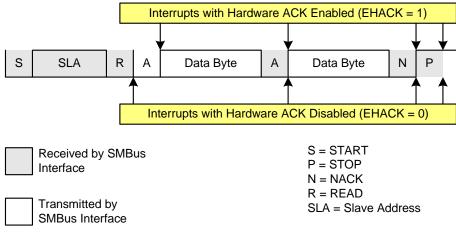

#### 26.3.5.1. 8-Bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 8-bit PWM mode is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 26.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to 00b enables 8-Bit Pulse Width Modulator mode. If the MATn bit is set to 1, the CCFn flag for the module will be set each time an 8-bit comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 256 PCA clock cycles. The duty cycle for 8-Bit PWM Mode is given in Equation 26.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(256 - PCA0CPHn)}{256}$$

#### Equation 26.2. 8-Bit PWM Duty Cycle

Using Equation 26.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 26.8. PCA 8-Bit PWM Mode Diagram