# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                    |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, POR, PWM, WDT               |

| Number of I/O              | 17                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 24-QSOP                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f997-gu |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Figures

| Figure 1.1. C8051F980 Block Diagram                                                          | 18 |

|----------------------------------------------------------------------------------------------|----|

| Figure 1.2. C8051F981 Block Diagram                                                          | 18 |

| Figure 1.3. C8051F982 Block Diagram                                                          | 19 |

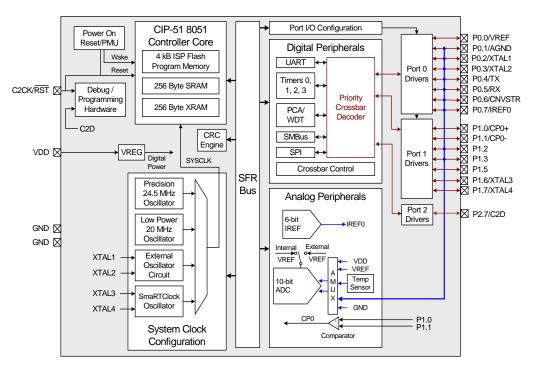

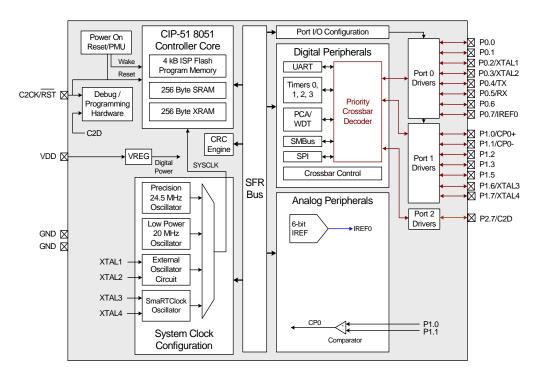

| Figure 1.4. C8051F983 Block Diagram                                                          | 19 |

| Figure 1.5. C8051F985 Block Diagram                                                          | 20 |

| Figure 1.6. C8051F986 Block Diagram                                                          | 20 |

| Figure 1.7. C8051F987 Block Diagram                                                          | 21 |

| Figure 1.8. C8051F988 Block Diagram                                                          | 21 |

| Figure 1.9. C8051F989 Block Diagram                                                          | 22 |

| Figure 1.10. C8051F990 Block Diagram                                                         | 22 |

| Figure 1.11. C8051F991 Block Diagram                                                         | 23 |

| Figure 1.12. C8051F996 Block Diagram                                                         | 23 |

| Figure 1.13. C8051F997 Block Diagram                                                         |    |

| Figure 1.14. Port I/O Functional Block Diagram                                               | 26 |

| Figure 1.15. PCA Block Diagram                                                               | 27 |

| Figure 1.16. ADC0 Functional Block Diagram                                                   |    |

| Figure 1.17. ADC0 Multiplexer Block Diagram                                                  | 29 |

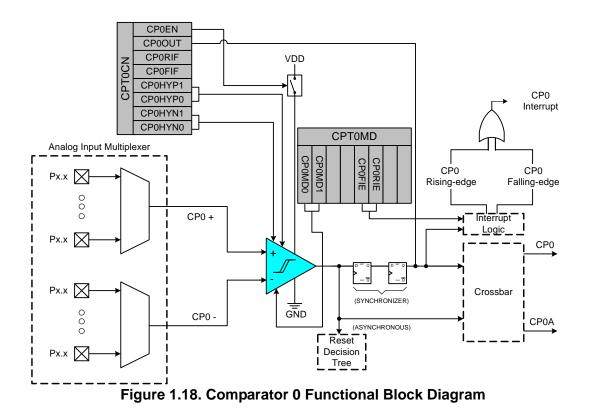

| Figure 1.18. Comparator 0 Functional Block Diagram                                           | 30 |

| Figure 3.1. QFN-20 Pinout Diagram (Top View)                                                 |    |

| Figure 3.2. QFN-24 Pinout Diagram (Top View)                                                 |    |

| Figure 3.3. QSOP-24 Pinout Diagram (Top View)                                                |    |

| Figure 3.4. QFN-20 Package Marking Diagram                                                   |    |

| Figure 3.5. QFN-24 Package Marking Diagram                                                   |    |

| Figure 3.6. QSOP-24 Package Marking Diagram                                                  |    |

| Figure 3.7. QFN-20 Package Drawing                                                           |    |

| Figure 3.8. Typical QFN-20 Landing Diagram                                                   |    |

| Figure 3.9. QFN-24 Package Drawing                                                           |    |

| Figure 3.10. Typical QFN-24 Landing Diagram                                                  |    |

| Figure 3.11. QSOP-24 Package Diagram                                                         |    |

| Figure 3.12. QSOP-24 Landing Diagram                                                         |    |

| Figure 4.1. Active Mode Current (External CMOS Clock)                                        |    |

| Figure 4.2. Idle Mode Current (External CMOS Clock)                                          |    |

| Figure 4.3. Typical VOH Curves, 1.8–3.6 V                                                    |    |

| Figure 4.4. Typical VOL Curves, 1.8–3.6 V                                                    |    |

| Figure 5.1. ADC0 Functional Block Diagram                                                    |    |

| Figure 5.2. 10-Bit ADC Track and Conversion Example Timing (BURSTEN = 0)                     |    |

| Figure 5.3. Burst Mode Tracking Example with Repeat Count Set to 4                           |    |

| Figure 5.4. ADC0 Equivalent Input Circuits                                                   |    |

| Figure 5.5. ADC Window Compare Example: Right-Justified Single-Ended Data                    |    |

| Figure 5.6. ADC Window Compare Example: Left-Justified Single-Ended Data                     |    |

| Figure 5.7. ADC0 Multiplexer Block Diagram                                                   |    |

| Figure 5.8. Temperature Sensor Transfer Function                                             | 85 |

| Figure 5.9. Temperature Sensor Error with 1-Point Calibration ( $V_{REF} = 1.65 \text{ V}$ ) | 86 |

## SFR Definition 7.2. CPT0MD: Comparator 0 Mode Selection

| Bit   | 7   | 6 | 5      | 4      | 3 | 2 | 1          | 0 |

|-------|-----|---|--------|--------|---|---|------------|---|

| Name  |     |   | CP0RIE | CP0FIE |   |   | CP0MD[1:0] |   |

| Туре  | R/W | R | R/W    | R/W    | R | R | R/W        |   |

| Reset | 1   | 0 | 0      | 0      | 0 | 0 | 1          | 0 |

## SFR Page = 0x0; SFR Address = 0x9D

| Bit | Name       | Function                                                                                                                                                                                                                                                           |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved   | Read = 1b, Must Write 1b.                                                                                                                                                                                                                                          |

| 6   | Unused     | Read = 0b, Write = don't care.                                                                                                                                                                                                                                     |

| 5   | CPORIE     | Comparator0 Rising-Edge Interrupt Enable.<br>0: Comparator0 Rising-edge interrupt disabled.<br>1: Comparator0 Rising-edge interrupt enabled.                                                                                                                       |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.<br>0: Comparator0 Falling-edge interrupt disabled.<br>1: Comparator0 Falling-edge interrupt enabled.                                                                                                                    |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                    |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

## SFR Definition 8.3. CS0DH: Capacitive Sense Data High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | CS0DH[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R          | R | R | R | R | R | R | R |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Page = 0x0; SFR Address = 0xEE

| Bit | Name  | Description                                                                    |

|-----|-------|--------------------------------------------------------------------------------|

| 7:0 | CS0DH | CS0 Data High Byte.                                                            |

|     |       | Stores the high byte of the last completed 16-bit Capacitive Sense conversion. |

### SFR Definition 8.4. CS0DL: Capacitive Sense Data Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | CS0DL[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R          | R | R | R | R | R | R | R |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Page = 0x0; SFR Address = 0xED

| Bit | Name  | Description                                                                   |

|-----|-------|-------------------------------------------------------------------------------|

| 7:0 | CS0DL | CS0 Data Low Byte.                                                            |

|     |       | Stores the low byte of the last completed 16-bit Capacitive Sense conversion. |

## 11. On-Chip XRAM

The C8051F99x-C8051F98x MCUs include on-chip RAM mapped into the external data memory space (XRAM). The external memory space may be accessed using the external move instruction (MOVX) with the target address specified in either the data pointer (DPTR), or with the target address low byte in R0 or R1. On C8051F99x-C8051F98x devices, the target address high byte is a don't care.

When using the MOVX instruction to access on-chip RAM, no additional initialization is required and the MOVX instruction execution time is as specified in the CIP-51 chapter.

**Important Note**: MOVX write operations can be configured to target Flash memory, instead of XRAM. See Section "14. Flash Memory" on page 150 for more details. The MOVX instruction accesses XRAM by default.

**Important Note**: On device reset or upon waking up from Sleep mode, address 0x0000 of external memory may be overwritten by an indeterminate value. The indeterminate value is 0x00 in most situations. A dummy variable should be placed at address 0x0000 in external memory to ensure that the application firmware does not store any data that needs to be retained during sleep or reset at this memory location.

### 11.1. Accessing XRAM

The XRAM memory space is accessed using the MOVX instruction. The MOVX instruction has two forms, both of which use an indirect addressing method. The first method uses the Data Pointer, DPTR, a 16-bit register which contains the effective address of the XRAM location to be read from or written to. The second method uses R0 or R1 to generate the effective XRAM address. Examples of both of these methods are given below.

#### 11.1.1. 16-Bit MOVX Example

The 16-bit form of the MOVX instruction accesses the memory location pointed to by the contents of the DPTR register. The following series of instructions reads the value of the byte at address 0x1234 into the accumulator A:

| MOV  | DPTR, #0034h | ; load DPTR with 16-bit address to read (0x0034 | .) |

|------|--------------|-------------------------------------------------|----|

| MOVX | A, @DPTR     | ; load contents of 0x0034 into accumulator A    |    |

The above example uses the 16-bit immediate MOV instruction to set the contents of DPTR. Alternately, the DPTR can be accessed through the SFR registers DPH, which contains the upper 8-bits of DPTR, and DPL, which contains the lower 8-bits of DPTR.

#### 11.1.2. 8-Bit MOVX Example

The 8-bit form of the MOVX instruction uses the contents of R0 or R1 to determine the 8-bits of the effective address to be accessed. The following series of instructions read the contents of the byte at address 0x0034 into the accumulator A.

| MOV  | R0, #34h | ; | load | low byte | of | address into R0 (or R1)   |

|------|----------|---|------|----------|----|---------------------------|

| MOVX | a, @R0   | ; | load | contents | of | 0x0034 into accumulator A |

| Register | Address | SFR Page | Description                 | Page |

|----------|---------|----------|-----------------------------|------|

| TCON     | 0x88    | 0x0      | Timer/Counter Control       | 284  |

| TH0      | 0x8C    | 0x0      | Timer/Counter 0 High        | 287  |

| TH1      | 0x8D    | 0x0      | Timer/Counter 1 High        | 287  |

| TL0      | 0x8A    | 0x0      | Timer/Counter 0 Low         | 286  |

| TL1      | 0x8B    | 0x0      | Timer/Counter 1 Low         | 286  |

| TMOD     | 0x89    | 0x0      | Timer/Counter Mode          | 285  |

| TMR2CN   | 0xC8    | 0x0      | Timer/Counter 2 Control     | 291  |

| TMR2H    | 0xCD    | 0x0      | Timer/Counter 2 High        | 293  |

| TMR2L    | 0xCC    | 0x0      | Timer/Counter 2 Low         | 293  |

| TMR2RLH  | 0xCB    | 0x0      | Timer/Counter 2 Reload High | 292  |

| TMR2RLL  | 0xCA    | 0x0      | Timer/Counter 2 Reload Low  | 292  |

| TMR3CN   | 0x91    | 0x0      | Timer/Counter 3 Control     | 297  |

| TMR3H    | 0x95    | 0x0      | Timer/Counter 3 High        | 299  |

| TMR3L    | 0x94    | 0x0      | Timer/Counter 3 Low         | 299  |

| TMR3RLH  | 0x93    | 0x0      | Timer/Counter 3 Reload High | 298  |

| TMR3RLL  | 0x92    | 0x0      | Timer/Counter 3 Reload Low  | 298  |

| TOFFH    | 0x8E    | 0xF      | Temperature Offset High     | 87   |

| TOFFL    | 0x8D    | 0xF      | Temperature Offset Low      | 87   |

| VDM0CN   | 0xFF    | 0x0      | VDD Monitor Control         | 184  |

| XBR0     | 0xE1    | 0x0      | Port I/O Crossbar Control 0 | 222  |

| XBR1     | 0xE2    | 0x0      | Port I/O Crossbar Control 1 | 223  |

| XBR2     | 0xE3    | 0x0      | Port I/O Crossbar Control 2 | 224  |

### Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

## SFR Definition 14.3. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

| Name  |   |   |   |   |   |   | PSEE | PSWE |

| Туре  | R | R | R | R | R | R | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

#### SFR Page =All; SFR Address = 0x8F

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1   | PSEE   | Program Store Erase Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit (in combination with PSWE) allows an entire page of Flash program memory to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> <li>1: Flash program memory erasure enabled.</li> </ul> |

| 0   | PSWE   | Program Store Write Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul>                                                                                                                                                     |

## 15.7. Determining the Event that Caused the Last Wakeup

When waking from idle mode, the CPU will vector to the interrupt which caused it to wake up. When waking from stop mode, the RSTSRC register may be read to determine the cause of the last reset.

Upon exit from suspend or sleep mode, the wake-up flags in the PMU0CF and PMU0FL registers can be read to determine the event which caused the device to wake up. After waking up, the wake-up flags will continue to be updated if any of the wake-up events occur. Wake-up flags are always updated, even if they are not enabled as wake-up sources.

All wake-up flags enabled as wake-up sources in PMU0CF and PMU0FL must be cleared before the device can enter suspend or sleep mode. After clearing the wake-up flags, each of the enabled wake-up events should be checked in the individual peripherals to ensure that a wake-up event did not occur while the wake-up flags were being cleared.

```

The 16-bit C8051F99x-C8051F98x CRC algorithm can be described by the following code:

```

```

unsigned short UpdateCRC (unsigned short CRC_acc, unsigned char CRC_input)

ł

unsigned char i;

// loop counter

#define POLY 0x1021

// Create the CRC "dividend" for polynomial arithmetic (binary arithmetic

// with no carries)

CRC_acc = CRC_acc ^ (CRC_input << 8);</pre>

// "Divide" the poly into the dividend using CRC XOR subtraction

// CRC_acc holds the "remainder" of each divide

11

// Only complete this division for 8 bits since input is 1 byte

for (i = 0; i < 8; i++)

{

// Check if the MSB is set (if MSB is 1, then the POLY can "divide"

// into the "dividend")

if ((CRC_acc & 0x8000) == 0x8000)

{

// if so, shift the CRC value, and XOR "subtract" the poly

CRC_acc = CRC_acc << 1;</pre>

CRC_acc ^= POLY;

}

else

{

// if not, just shift the CRC value

CRC_acc = CRC_acc << 1;

}

}

// Return the final remainder (CRC value)

return CRC_acc;

}

```

Table 16.1 lists several input values and the associated outputs using the 16-bit C8051F99x-C8051F98x CRC algorithm:

| Input                        | Output |

|------------------------------|--------|

| 0x63                         | 0xBD35 |

| 0x8C                         | 0xB1F4 |

| 0x7D                         | 0x4ECA |

| 0xAA, 0xBB, 0xCC             | 0x6CF6 |

| 0x00, 0x00, 0xAA, 0xBB, 0xCC | 0xB166 |

| Table 16.1. | . Example | e 16-bit | CRC | Outputs |

|-------------|-----------|----------|-----|---------|

|-------------|-----------|----------|-----|---------|

### 16.5. CRC0 Bit Reverse Feature

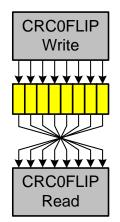

CRC0 includes hardware to reverse the bit order of each bit in a byte as shown in Figure 16.2. Each byte of data written to CRC0FLIP is read back bit reversed. For example, if 0xC0 is written to CRC0FLIP, the data read back is 0x03. Bit reversal is a useful mathematical function used in algorithms such as the FFT.

Figure 16.2. Bit Reverse Register

## SFR Definition 16.6. CRC0FLIP: CRC0 Bit Flip

| Bit   | 7             | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|---------------|-----|---|---|---|---|---|---|--|--|--|--|

| Name  | CRC0FLIP[7:0] |     |   |   |   |   |   |   |  |  |  |  |

| Туре  |               | R/W |   |   |   |   |   |   |  |  |  |  |

| Reset | 0             | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

#### SFR Page = All; SFR Address = 0x9C

| Bit | Name          | Function                                                                                                                                                                                  |

|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC0FLIP[7:0] | CRC0 Bit Flip.                                                                                                                                                                            |

|     |               | Any byte written to CRC0FLIP is read back in a bit-reversed order, i.e. the written LSB becomes the MSB. For example:<br>If 0xC0 is written to CRC0FLIP, the data read back will be 0x03. |

|     |               | If 0x05 is written to CRC0FLIP, the data read back will be 0xA0.                                                                                                                          |

### 20.2.2. Using the SmaRTClock Oscillator in Self-Oscillate Mode

When using Self-Oscillate Mode, the XTAL3 and XTAL4 pins are internally shorted together. The following steps show how to configure SmaRTClock for use in Self-Oscillate Mode:

- 1. Set SmaRTClock to Self-Oscillate Mode (XMODE = 0).

- Set the desired oscillation frequency: For oscillation at about 20 kHz, set BIASX2 = 0. For oscillation at about 40 kHz, set BIASX2 = 1.

- 3. The oscillator starts oscillating instantaneously.

- 4. Fine tune the oscillation frequency by adjusting the load capacitance (RTC0XCF).

#### 20.2.3. Using the Low Frequency Oscillator (LFO)

The low frequency oscillator provides an ultra low power, on-chip clock source to the SmaRTClock. The typical frequency of oscillation is 16.4 kHz  $\pm 20\%$ . No external components are required to use the LFO and the XTAL3 and XTAL4 pins do not need to be shorted together.

The following steps show how to configure SmaRTClock for use with the LFO:

- 1. Enable and select the Low Frequency Oscillator (LFOEN = 1).

- 2. The LFO starts oscillating instantaneously.

When the LFO is enabled, the SmaRTClock oscillator increments bit 1 of the 32-bit timer (instead of bit 0). This effectively multiplies the LFO frequency by 2, making the RTC timebase behave as if a 32.768 kHz crystal is connected at the output.

### 20.3.3. Software Considerations for using the SmaRTClock Timer and Alarm

The SmaRTClock timer and alarm have two operating modes to suit varying applications. The two modes are described below:

#### Mode 1:

The first mode uses the SmaRTClock timer as a perpetual timebase which is never reset to zero. Every 36 hours, the timer is allowed to overflow without being stopped or disrupted. The alarm interval is software managed and is added to the ALRMn registers by software after each alarm. This allows the alarm match value to always stay ahead of the timer by one software managed interval. If software uses 32-bit unsigned addition to increment the alarm match value, then it does not need to handle overflows since both the timer and the alarm match value will overflow in the same manner.

This mode is ideal for applications which have a long alarm interval (e.g., 24 or 36 hours) and/or have a need for a perpetual timebase. An example of an application that needs a perpetual timebase is one whose wake-up interval is constantly changing. For these applications, software can keep track of the number of timer overflows in a 16-bit variable, extending the 32-bit (36 hour) timer to a 48-bit (272 year) perpetual timebase.

#### Mode 2:

The second mode uses the SmaRTClock timer as a general purpose up counter which is auto reset to zero by hardware after each alarm. The alarm interval is managed by hardware and stored in the ALRMn registers. Software only needs to set the alarm interval once during device initialization. After each alarm, software should keep a count of the number of alarms that have occurred in order to keep track of time.

This mode is ideal for applications that require minimal software intervention and/or have a fixed alarm interval. This mode is the most power efficient since it requires less CPU time per alarm.

## Internal Register Definition 20.4. RTC0CN: SmaRTClock Control

| Bit   | 7          | 6                                                                                        | 5                                    | 4                    | 3                                                          | 2                | 1                               | 0             |  |  |

|-------|------------|------------------------------------------------------------------------------------------|--------------------------------------|----------------------|------------------------------------------------------------|------------------|---------------------------------|---------------|--|--|

| Name  | RTCOEN     | MCLKEN                                                                                   | OSCFAIL                              | RTC0TR               | RTC0AEN                                                    | ALRM             | <b>RTC0SET</b>                  | RTC0CAP       |  |  |

| Туре  | R/W        | R/W                                                                                      | R/W                                  | R/W                  | R/W                                                        | R/W              | R/W                             | R/W           |  |  |

| Rese  | t 0        | 0                                                                                        | Varies                               | 0                    | 0                                                          | 0                | 0                               | 0             |  |  |

| SmaR  | TClock Add | ress = 0x04                                                                              |                                      |                      |                                                            |                  |                                 |               |  |  |

| Bit   |            |                                                                                          |                                      |                      |                                                            |                  |                                 |               |  |  |

| 7     | RTC0EN     | SmaRTClock                                                                               | Enable.                              |                      |                                                            |                  |                                 |               |  |  |

|       |            | Enables/disabl<br>0: SmaRTClock<br>1: SmaRTClock                                         | < oscillator dis                     | abled.               | tor and associ                                             | ated bias cu     | rents.                          |               |  |  |

| 6     | MCLKEN     | Missing SmaR                                                                             | TClock Dete                          | ctor Enable.         |                                                            |                  |                                 |               |  |  |

|       |            | Enables/disable<br>0: Missing Sma<br>1: Missing Sma                                      | RTClock dete                         | ector disabled       | l.                                                         |                  |                                 |               |  |  |

| 5     | OSCFAIL    | SmaRTClock                                                                               | Oscillator Fai                       | il Event Flag        | •                                                          |                  |                                 |               |  |  |

|       |            | Set by hardwar<br>software. The v<br>oscillator is dis                                   | alue of this bi                      |                      |                                                            |                  | ırs. Must be cle                | eared by      |  |  |

| 4     | RTC0TR     | SmaRTClock                                                                               | Timer Run Co                         | ontrol.              |                                                            |                  |                                 |               |  |  |

|       |            | Controls if the S<br>0: SmaRTClock<br>1: SmaRTClock                                      | k timer is stop                      | ped.                 | ng or stopped                                              | (holds currer    | nt value).                      |               |  |  |

| 3     | RTC0AEN    | SmaRTClock                                                                               |                                      |                      |                                                            |                  |                                 |               |  |  |

|       |            | Enables/disabl<br>0: SmaRTCloc<br>1: SmaRTCloc                                           | k alarm disabl                       | ed.                  | function. Also                                             | clears the Al    | ₋RM flag.                       |               |  |  |

| 2     | ALRM       | SmaRTClock                                                                               |                                      | Read:                |                                                            | Wr               |                                 |               |  |  |

|       |            | Flag and Auto<br>Reads return th<br>alarm event fla<br>Writes enable/o<br>Auto Reset fun | ne state of the<br>g.<br>disable the | flag is d<br>1: Smal | RTClock alarm<br>le-asserted.<br>RTClock alarm<br>sserted. | 1: E             | Disable Auto R<br>Enable Auto R |               |  |  |

| 1     | RTC0SET    | SmaRTClock                                                                               | Timer Set.                           |                      |                                                            |                  |                                 |               |  |  |

|       |            | Writing 1 initiate cate that the tir                                                     | ner set operat                       | ion is comple        |                                                            | is bit is clear  | ed to 0 by hard                 | ware to indi- |  |  |

| 0     | RTC0CAP    | SmaRTClock                                                                               | -                                    |                      |                                                            |                  |                                 |               |  |  |

|       |            | Writing 1 initiate indicate that the                                                     |                                      |                      |                                                            | n. This bit is c | leared to 0 by                  | hardware to   |  |  |

| Note: |            | ag will remain a                                                                         |                                      |                      |                                                            | •                |                                 |               |  |  |

|       |            | it" on page 162 f<br>atically cleared                                                    |                                      | on how to ca         | apture a SmaR                                              | TClock Aları     | n event using                   | a flag which  |  |  |

## Internal Register Definition 20.6. RTC0XCF: SmaRTClock Oscillator Configuration

| Bit   | 7       | 6       | 5 | 4 | 3       | 2      | 1      | 0      |

|-------|---------|---------|---|---|---------|--------|--------|--------|

| Name  | AUTOSTP | LOADRDY |   |   | LOADCAP |        |        |        |

| Туре  | R/W     | R       | R | R | R/W     |        |        |        |

| Reset | 0       | 0       | 0 | 0 | Varies  | Varies | Varies | Varies |

SmaRTClock Address = 0x06

| Bit | Name    | Function                                                                            |

|-----|---------|-------------------------------------------------------------------------------------|

| 7   | AUTOSTP | Automatic Load Capacitance Stepping Enable.                                         |

|     |         | Enables/disables automatic load capacitance stepping.                               |

|     |         | 0: Load capacitance stepping disabled.                                              |

|     |         | 1: Load capacitance stepping enabled.                                               |

| 6   | LOADRDY | Load Capacitance Ready Indicator.                                                   |

|     |         | Set by hardware when the load capacitance matches the programmed value.             |

|     |         | 0: Load capacitance is currently stepping.                                          |

|     |         | 1: Load capacitance has reached it programmed value.                                |

| 5:4 | Unused  | Read = 00b; Write = Don't Care.                                                     |

| 3:0 | LOADCAP | Load Capacitance Programmed Value.                                                  |

|     |         | Holds the user's desired value of the load capacitance. See Table 20.2 on page 205. |

### 22.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

- Optional hardware recognition of slave address and automatic acknowledgement of address/data

SMBus interrupts are generated for each data byte or slave address that is transferred. When hardware acknowledgement is disabled, the point at which the interrupt is generated depends on whether the hardware is acting as a data transmitter or receiver. When a transmitter (i.e. sending address/data, receiving an ACK), this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data (i.e., receiving address/data, sending an ACK), this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. If hardware acknowledgement is enabled, these interrupts are always generated after the ACK cycle. See Section 22.5 for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in Section 22.4.2; Table 22.5 provides a quick SMB0CN decoding reference.

## SFR Definition 25.1. CKCON: Clock Control

| Bit   | 7           | 6                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                         | 4                                                 | 3                           | 2      | 1   | 0             |  |  |  |

|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------|--------|-----|---------------|--|--|--|

| Nam   | e T3MH      | I T3ML                                                                                                                                                                                                                                                     | T2MH                                                                                                                                                                                                                                                                                      | T2ML                                              | T1M                         | TOM    | SCA | <b>[</b> 1:0] |  |  |  |

| Туре  | e R/W       | R/W                                                                                                                                                                                                                                                        | R/W                                                                                                                                                                                                                                                                                       | R/W                                               | R/W                         | R/W    | R   | /W            |  |  |  |

| Rese  | et 0        | 0                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                         | 0                                                 | 0                           | 0      | 0   | 0             |  |  |  |

| SFR F | Page = 0x0; | SFR Address :                                                                                                                                                                                                                                              | = 0x8E                                                                                                                                                                                                                                                                                    |                                                   |                             |        |     |               |  |  |  |

| Bit   | Name        |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                           |                                                   | Function                    |        |     |               |  |  |  |

| 7     | ТЗМН        | Selects the clo<br>0: Timer 3 high                                                                                                                                                                                                                         | <b>Fimer 3 High Byte Clock Select.</b><br>Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).<br>It Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.<br>It Timer 3 high byte uses the system clock.                                   |                                                   |                             |        |     |               |  |  |  |

| 6     | T3ML        | Selects the clo<br>in split 8-bit tim<br>0: Timer 3 low                                                                                                                                                                                                    | <b>Timer 3 Low Byte Clock Select.</b><br>Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.<br>It: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.<br>It: Timer 3 low byte uses the system clock. |                                                   |                             |        |     |               |  |  |  |

| 5     | T2MH        | Selects the clo<br>0: Timer 2 high                                                                                                                                                                                                                         | Timer 2 High Byte Clock Select.         Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).         0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.         1: Timer 2 high byte uses the system clock.                           |                                                   |                             |        |     |               |  |  |  |

| 4     | T2ML        | Timer 2 Low E<br>Selects the clo<br>this bit selects<br>0: Timer 2 low<br>1: Timer 2 low                                                                                                                                                                   | ck supplied<br>the clock su<br>byte uses th                                                                                                                                                                                                                                               | to Timer 2. If<br>pplied to the<br>le clock defir | lower 8-bit<br>ned by the T | timer. |     | ner mode,     |  |  |  |

| 3     | T1M         | Timer 1 Clock<br>Selects the clo<br>0: Timer 1 use<br>1: Timer 1 use                                                                                                                                                                                       | ck source su<br>s the clock d                                                                                                                                                                                                                                                             | lefined by the                                    | -                           |        |     |               |  |  |  |

| 2     | ТОМ         | Selects the clo<br>0: Counter/Tim                                                                                                                                                                                                                          | <b>Timer 0 Clock Select.</b><br>Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.<br>0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].<br>1: Counter/Timer 0 uses the system clock.                                                     |                                                   |                             |        |     |               |  |  |  |

| 1:0   | SCA[1:0]    | Timer 0/1 Prescale Bits.<br>These bits control the Timer 0/1 Clock Prescaler:<br>00: System clock divided by 12<br>01: System clock divided by 4<br>10: System clock divided by 48<br>11: External clock divided by 8 (synchronized with the system clock) |                                                                                                                                                                                                                                                                                           |                                                   |                             |        |     |               |  |  |  |

## SFR Definition 25.16. TMR3L: Timer 3 Low Byte

| Bit   | 7 | 6          | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|---|------------|---|----|---|---|---|---|--|--|--|--|

| Name  |   | TMR3L[7:0] |   |    |   |   |   |   |  |  |  |  |

| Туре  |   |            |   | R/ | W |   |   |   |  |  |  |  |

| Reset | 0 | 0          | 0 | 0  | 0 | 0 | 0 | 0 |  |  |  |  |

SFR Page = 0x0; SFR Address = 0x94

| Bit | Name       | Function                                                                                                       |

|-----|------------|----------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3L[7:0] | <b>Timer 3 Low Byte.</b><br>In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In |

|     |            | 8-bit mode, TMR3L contains the 8-bit low byte timer value.                                                     |

## SFR Definition 25.17. TMR3H Timer 3 High Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|---|------------|---|---|---|---|---|---|--|--|--|--|

| Name  |   | TMR3H[7:0] |   |   |   |   |   |   |  |  |  |  |

| Туре  |   | R/W        |   |   |   |   |   |   |  |  |  |  |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

SFR Page = 0x0; SFR Address = 0x95

| Bit | Name       | Function                                                                                                                                        |  |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:0 | TMR3H[7:0] | Timer 3 High Byte.                                                                                                                              |  |

|     |            | In 16-bit mode, the TMR3H register contains the high byte of the 16-bit Timer 3. In 8-bit mode, TMR3H contains the 8-bit high byte timer value. |  |

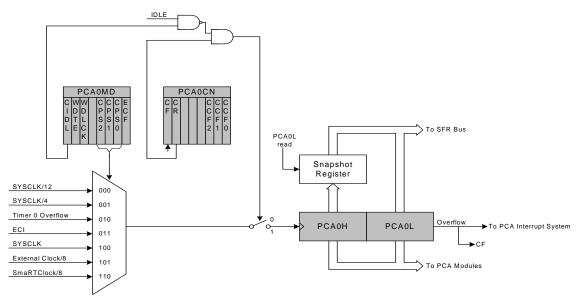

## 26.1. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter.** Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2–CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 26.1.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2 | CPS1 | CPS0 | Timebase                                                              |  |  |  |

|------|------|------|-----------------------------------------------------------------------|--|--|--|

| 0    | 0    | 0    | System clock divided by 12                                            |  |  |  |

| 0    | 0    | 1    | System clock divided by 4                                             |  |  |  |

| 0    | 1    | 0    | Timer 0 overflow                                                      |  |  |  |

| 0    | 1    | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |  |  |  |

| 1    | 0    | 0    | System clock                                                          |  |  |  |

| 1    | 0    | 1    | External oscillator source divided by 8 <sup>1</sup>                  |  |  |  |

| 1    | 1    | 0    | SmaRTClock oscillator source divided by 8 <sup>2</sup>                |  |  |  |

| 1    | 1    | 1    | Reserved                                                              |  |  |  |

|      |      |      |                                                                       |  |  |  |

Table 26.1. PCA Timebase Input Options

Notes:

1. External oscillator source divided by 8 is synchronized with the system clock.

2. SmaRTClock oscillator source divided by 8 is synchronized with the system clock.

## DOCUMENT CHANGE LIST

## Revision 0.3 to Revision 0.4

• QFN-20 package and landing diagram updated.

## **Revision 0.4 to Revision 1.0**

- IREF0CF register description updated.

- Updated ADC0 Chapter Text.

- Corrected an error in the Product Selector Guide.

- Updated SmaRTClock chapter to indicate how the Alarm value should be set when using Auto Reset and the LFO.

- Updated electrical specifications to fill TBDs and updated power specifications based on Rev B characterization data.

- Added a note to the OSCICL register description.

- Added a note to the CRC0CN register description.

- Updated equation in the CRC0CNT register description.

- Updated Power On Reset description.

## Revision 1.0 to Revision 1.1

Removed references to AN338.

## **Revision 1.1 to Revision 1.2**

- Removed QuickSense references.

- Updated part numbers to Revision C in "Ordering Information" on page 31 and added Figure 3.4, Figure 3.5, and Figure 3.6 to identify the silicon revision.

- Updated REVID register (SFR Definition 14.2) and REVID C2 register (C2 Register Definition 27.3) with the 0x02 value for Revision C.

- Updated Figure "7.3 CP0 Multiplexer Block Diagram" on page 98 to remove the bar over the CPnOUT signals.

- Updated the "Reset Sources" on page 181 chapter to reflect the correct state of the RST pin during power-on reset.

- Updated Figure "1.14 Port I/O Functional Block Diagram" on page 26 and Figure "21.1 Port I/O Functional Block Diagram" on page 215 to mention P1.4 is not available on 20-pin devices.

- Removed references to the EMI0CN register, which does not exist.

- Updated Figure "8.2 Auto-Scan Example" on page 103 to refer to the correct pins.

- Updated POR Monitor Threshold (V<sub>POR</sub>) Brownout Condition (VDD Falling) specification minimum, typical, and maximum values.

- Updated the reset value of the CLKSEL register (SFR Definition 19.1).

- Updated description of WEAKPUD in SFR Definition 21.3.

- Corrected SFR addresses for P0DRV (SFR Definition 21.12), P1DRV (SFR Definition 21.17), P2DRV (SFR Definition 21.20), PMU0MD (SFR Definition 15.3), FLSCL (SFR Definition 14.5), REF0CN (SFR Definition 5.15), CS0SCAN0 (SFR Definition 8.5), and CS0SCAN1 (SFR Definition 8.6).

- Replaced all instances of V<sub>BAT</sub> with V<sub>DD</sub>.

- Added a note to "11.1. Accessing XRAM", "15.5. Sleep Mode", and "18. Reset Sources" regarding an issue with the first address of XRAM.

- Added a note to "15.5. Sleep Mode" and "19. Clocking Sources" regarding using the internal low power