Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                 |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                               |

| Number of I/O              | 62                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3445axa-181 |

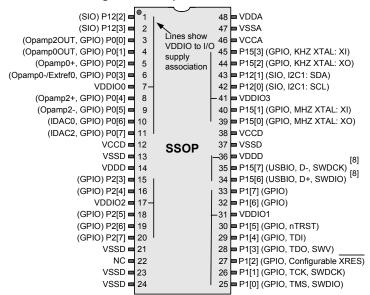

Figure 2-3. 48-pin SSOP Part Pinout

8. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

# ■ Program branching instructions

# 4.3.1 Instruction Set Summary

# 4.3.1.1 Arithmetic Instructions

Arithmetic instructions support the direct, indirect, register, immediate constant, and register-specific instructions. Arithmetic modes are used for addition, subtraction, multiplication, division, increment, and decrement operations. Table 4-1 lists the different arithmetic instructions.

**Table 4-1. Arithmetic Instructions**

| Mnemonic      | Description                                          | Bytes | Cycles |

|---------------|------------------------------------------------------|-------|--------|

| ADD A,Rn      | Add register to accumulator                          | 1     | 1      |

| ADD A,Direct  | Add direct byte to accumulator                       | 2     | 2      |

| ADD A,@Ri     | Add indirect RAM to accumulator                      | 1     | 2      |

| ADD A,#data   | Add immediate data to accumulator                    | 2     | 2      |

| ADDC A,Rn     | Add register to accumulator with carry               | 1     | 1      |

| ADDC A,Direct | Add direct byte to accumulator with carry            | 2     | 2      |

| ADDC A,@Ri    | Add indirect RAM to accumulator with carry           | 1     | 2      |

| ADDC A,#data  | Add immediate data to accumulator with carry         | 2     | 2      |

| SUBB A,Rn     | Subtract register from accumulator with borrow       | 1     | 1      |

| SUBB A,Direct | Subtract direct byte from accumulator with borrow    | 2     | 2      |

| SUBB A,@Ri    | Subtract indirect RAM from accumulator with borrow   | 1     | 2      |

| SUBB A,#data  | Subtract immediate data from accumulator with borrow | 2     | 2      |

| INC A         | Increment accumulator                                | 1     | 1      |

| INC Rn        | Increment register                                   | 1     | 2      |

| INC Direct    | Increment direct byte                                | 2     | 3      |

| INC @Ri       | Increment indirect RAM                               | 1     | 3      |

| DEC A         | Decrement accumulator                                | 1     | 1      |

| DEC Rn        | Decrement register                                   | 1     | 2      |

| DEC Direct    | Decrement direct byte                                | 2     | 3      |

| DEC @Ri       | Decrement indirect RAM                               | 1     | 3      |

| INC DPTR      | Increment data pointer                               | 1     | 1      |

| MUL           | Multiply accumulator and B                           | 1     | 2      |

| DIV           | Divide accumulator by B                              | 1     | 6      |

| DAA           | Decimal adjust accumulator                           | 1     | 3      |

Document Number: 001-57331 Rev. \*G Page 11 of 143

# 5. Memory

### 5.1 Static RAM

CY8C34 SRAM is used for temporary data storage. Up to 8 KB of SRAM is provided and can be accessed by the 8051 or the DMA controller. See Memory Map on page 24. Simultaneous access of SRAM by the 8051 and the DMA controller is possible if different 4-KB blocks are accessed.

### 5.2 Flash Program Memory

Flash memory in PSoC devices provides nonvolatile storage for user firmware, user configuration data, bulk data storage, and optional ECC data. The main flash memory area contains up to 64 KB of user program space.

Up to an additional 8 KB of flash space is available for ECC. If ECC is not used this space can store device configuration data and bulk user data. User code may not be run out of the ECC flash memory section. ECC can correct one bit error and detect two bit errors per 8 bytes of firmware memory; an interrupt can be generated when an error is detected.

The CPU reads instructions located in flash through a cache controller. This improves instruction execution rate and reduces system power consumption by requiring less frequent flash access. The cache has 8 lines at 64 bytes per line for a total of 512 bytes. It is fully associative, automatically controls flash power, and can be enabled or disabled. If ECC is enabled, the cache controller also performs error checking and correction, and interrupt generation.

Flash programming is performed through a special interface and preempts code execution out of flash. The flash programming interface performs flash erasing, programming and setting code protection levels. Flash in-system serial programming (ISSP), typically used for production programming, is possible through both the SWD and JTAG interfaces. In-system programming, typically used for bootloaders, is also possible using serial interfaces such as I<sup>2</sup>C, USB, UART, and SPI, or any communications protocol.

#### 5.3 Flash Security

All PSoC devices include a flexible flash-protection model that prevents access and visibility to on-chip flash memory. This prevents duplication or reverse engineering of proprietary code. Flash memory is organized in blocks, where each block contains 256 bytes of program or data and 32 bytes of ECC or configuration data. A total of up to 256 blocks is provided on 64-KB flash devices.

The device offers the ability to assign one of four protection levels to each row of flash. Table 5-1 lists the protection modes available. Flash protection levels can only be changed by performing a complete flash erase. The Full Protection and Field Upgrade settings disable external access (through a debugging tool such as PSoC Creator, for example). If your application requires code update through a bootloader, then use the Field Upgrade setting. Use the Unprotected setting only when no security is needed in your application. The PSoC device also offers an advanced security feature called Device Security which permanently disables all test, programming, and debug ports,

protecting your application from external access (see the "Device Security" section on page 63). For more information about how to take full advantage of the security features in PSoC, see the PSoC 3 TRM.

Table 5-1. Flash Protection

| Protection<br>Setting | Allowed                                              | Not Allowed                              |

|-----------------------|------------------------------------------------------|------------------------------------------|

| Unprotected           | External read and write<br>+ internal read and write | _                                        |

| Factory<br>Upgrade    | External write + internal read and write             | External read                            |

| Field Upgrade         | Internal read and write                              | External read and write                  |

| Full Protection       | Internal read                                        | External read and write + internal write |

#### **Disclaimer**

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as 'unbreakable'. Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# 5.4 EEPROM

PSoC EEPROM memory is a byte-addressable nonvolatile memory. The CY8C34 has up to 2 KB of EEPROM memory to store user data. Reads from EEPROM are random access at the byte level. Reads are done directly; writes are done by sending write commands to an EEPROM programming interface. CPU code execution can continue from flash during EEPROM writes. EEPROM is erasable and writeable at the row level. The EEPROM is divided into 128 rows of 16 bytes each. The CPU can not execute out of EEPROM. There is no ECC hardware associated with EEPROM. If ECC is required it must be handled in firmware.

It can take as much as 20 milliseconds to write to EEPROM or flash. During this time the device should not be reset, or unexpected changes may be made to portions of EEPROM or flash. Reset sources (see Section 6.3.1) include XRES pin, software reset, and watchdog; care should be taken to make sure that these are not inadvertently activated. Also, the low voltage detect circuits should be configured to generate an interrupt instead of a reset.

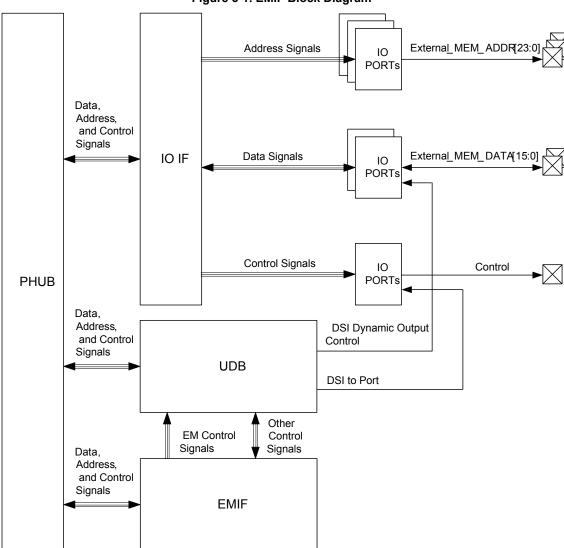

# 5.6 External Memory Interface

CY8C34 provides an EMIF for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles. Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C34 supports only one type of external memory device at a time. External memory can be accessed through the 8051 xdata space; up to 24 address bits can be used. See "xdata Space" section on page 25. The memory can be 8 or 16 bits wide.

Figure 5-1. EMIF Block Diagram

Document Number: 001-57331 Rev. \*G

# PSoC® 3: CY8C34 Automotive Family Datasheet

### 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own Port Interrupt Control Unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to '1' and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt vector in the interrupt controller and the pin status register providing easy determination of the interrupt source down to the pin level.

Port pin interrupts remain active in all sleep modes allowing the PSoC device to wake from an externally generated interrupt. While level sensitive interrupts are not directly supported; UDB provide this functionality to the system when needed.

#### 6.4.6 Input Buffer Mode

GPIO and SIO input buffers can be configured at the port level for the default CMOS input thresholds or the optional LVTTL input thresholds. All input buffers incorporate Schmitt triggers for input hysteresis. Additionally, individual pin input buffers can be disabled in any drive mode.

#### 6.4.7 I/O Power Supplies

Up to four I/O pin power supplies are provided depending on the device and package. Each I/O supply must be less than or equal to the voltage on the chip's analog (VDDA) pin. This feature allows users to provide different I/O voltage levels for different pins on the device. Refer to the specific device package pinout to determine VDDIO capability for a given port and pin. The SIO port pins support an additional regulated high output capability, as described in Adjustable Output Level.

# 6.4.8 Analog Connections

These connections apply only to GPIO pins. All GPIO pins may be used as analog inputs or outputs. The analog voltage present on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs. Each GPIO may connect to one of the analog global busses or to one of the analog mux buses to connect any pin to any internal analog resource such as ADC or comparators. In addition, select pins provide direct connections to specific analog features such as the high current DACs or uncommitted opamps.

### 6.4.9 CapSense

This section applies only to GPIO pins. All GPIO pins may be used to create CapSense buttons and sliders<sup>[14]</sup>. See the "CapSense" section on page 58 for more information.

#### 6.4.10 LCD Segment Drive

This section applies only to GPIO pins. All GPIO pins may be used to generate Segment and Common drive signals for direct glass drive of LCD glass. See the "LCD Direct Drive" section on page 57 for details.

### 6.4.11 Adjustable Output Level

This section applies only to SIO pins. SIO port pins support the ability to provide a regulated high output level for interface to external signals that are lower in voltage than the SIO's respective VDDIO. SIO pins are individually configurable to output either the standard VDDIO level or the regulated output, which is based on an internally generated reference. Typically a voltage DAC (VDAC) is used to generate the reference (see Figure 6-11). The "DAC" section on page 59 has more details on VDAC use and reference routing to the SIO pins. Resistive pullup and pull-down drive modes are not available with SIO in regulated output mode.

### 6.4.12 Adjustable Input Level

This section applies only to SIO pins. SIO pins by default support the standard CMOS and LVTTL input levels but also support a differential mode with programmable levels. SIO pins are grouped into pairs. Each pair shares a reference generator block which, is used to set the digital input buffer reference level for interface to external signals that differ in voltage from VDDIO. The reference sets the pins voltage threshold for a high logic level (see Figure 6-11). Available input thresholds are:

- 0.5 × VDDIO

- 0.4 × VDDIO

- $\blacksquare 0.5 \times V_{REF}$

- V<sub>REF</sub>

Typically a voltage DAC (VDAC) generates the  $V_{REF}$  reference. "DAC" section on page 59 has more details on VDAC use and reference routing to the SIO pins.

#### Note

14. GPIOs with opamp outputs are not recommended for use with CapSense.

#### 8.3.2 LUT

The CY8C34 family of devices contains four LUTs. The LUT is a two input, one output lookup table that is driven by any one or two of the comparators in the chip. The output of any LUT is routed to the digital system interface of the UDB array. From the digital system interface of the UDB array, these signals can be connected to UDBs, DMA controller, I/O, or the interrupt controller.

The LUT control word written to a register sets the logic function on the output. The available LUT functions and the associated control word is shown in Table 8-2.

Table 8-2. LUT Function vs. Program Word and Inputs

| Control Word | Output (A and B are LUT inputs) |

|--------------|---------------------------------|

| 0000b        | FALSE ('0')                     |

| 0001b        | A AND B                         |

| 0010b        | A AND (NOT B)                   |

| 0011b        | A                               |

| 0100b        | (NOT <b>A</b> ) AND <b>B</b>    |

| 0101b        | В                               |

| 0110b        | A XOR B                         |

| 0111b        | A OR B                          |

| 1000b        | A NOR B                         |

| 1001b        | A XNOR B                        |

| 1010b        | NOT <b>B</b>                    |

| 1011b        | A OR (NOT B)                    |

| 1100b        | NOT A                           |

| 1101b        | (NOT A) OR B                    |

| 1110b        | A NAND B                        |

| 1111b        | TRUE ('1')                      |

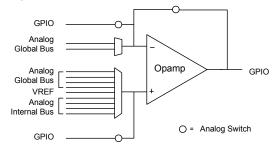

#### 8.4 Opamps

The CY8C34 family of devices contain up to two general purpose opamps in a device.

Figure 8-6. Opamp

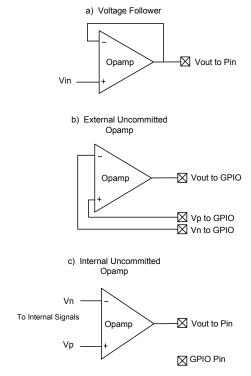

The opamp is uncommitted and can be configured as a gain stage or voltage follower, or output buffer on external or internal signals.

See Figure 8-7. In any configuration, the input and output signals can all be connected to the internal global signals and monitored with an ADC, or comparator. The configurations are implemented with switches between the signals and GPIO pins.

Figure 8-7. Opamp Configurations

The opamp has three speed modes, slow, medium, and fast. The slow mode consumes the least amount of quiescent power and the fast mode consumes the most power. The inputs are able to swing rail-to-rail. The output swing is capable of rail-to-rail operation at low current output, within 50 mV of the rails. When driving high current loads (about 25 mA) the output voltage may only get within 500 mV of the rails.

### 8.5 Programmable SC/CT Blocks

The CY8C34 family of devices contains up to two switched capacitor/continuous time (SC/CT) blocks in a device. Each switched capacitor/continuous time block is built around a single rail-to-rail high bandwidth opamp.

Switched capacitor is a circuit design technique that uses capacitors plus switches instead of resistors to create analog functions. These circuits work by moving charge between capacitors by opening and closing different switches. Nonoverlapping in phase clock signals control the switches, so that not all switches are ON simultaneously.

The PSoC Creator tool offers a user friendly interface, which allows you to easily program the SC/CT blocks. Switch control and clock phase control configuration is done by PSoC Creator so users only need to determine the application use parameters such as gain, amplifier polarity,  $V_{\rm RFF}$  connection, and so on.

The same opamps and block interfaces are also connectable to an array of resistors which allows the construction of a variety of continuous time functions.

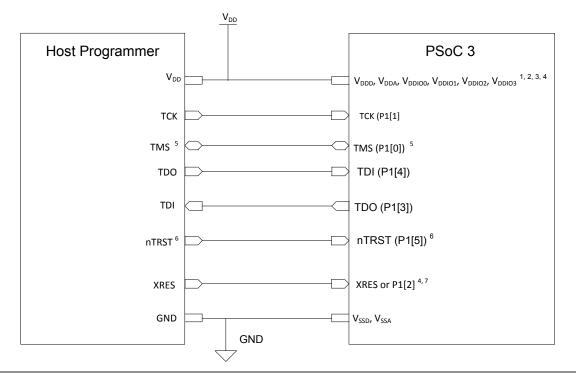

Figure 9-1. JTAG Interface Connections between PSoC 3 and Programmer

- <sup>1</sup> The voltage levels of Host Programmer and the PSoC 3 voltage domains involved in Programming should be same. The Port 1 JTAG pins, XRES pin (XRES\_N or P1[2]) are powered by V<sub>DDIO1</sub>. So, V<sub>DDIO1</sub> of PSoC 3 should be at same voltage level as host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDD</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer.

- <sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

- <sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- <sup>4</sup> For JTAG Programming, Device reset can also be done without connecting to the XRES pin or Power cycle mode by using the TMS,TCK,TDI, TDO pins of PSoC 3, and writing to a specific register. But this requires that the DPS setting in NVL is not equal to "Debug Ports Disabled".

- <sup>5</sup> By default, PSoC 3 is configured for 4-wire JTAG mode unless user changes the DPS setting. So the TMS pin is unidirectional. But if the DPS setting is changed to non-JTAG mode, the TMS pin in JTAG is bi-directional as the SWD Protocol has to be used for acquiring the PSoC 3 device initially. After switching from SWD to JTAG mode, the TMS pin will be uni-directional. In such a case, unidirectional buffer should not be used on TMS line.

- <sup>6</sup> nTRST JTAG pin (P1[5]) cannot be used to reset the JTAG TAP controlller during first time programming of PSoC 3 as the default setting is 4-wire JTAG (nTRST disabled). Use the TMS, TCK pins to do a reset of JTAG TAP controller.

- If XRES pin is used by host, P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48-pin devices, but use dedicated XRES pin for rest of devices.

Document Number: 001-57331 Rev. \*G Page 61 of 143

Table 11-11. USBIO AC Specifications

| Parameter | Description                                                 | Conditions                                        | Min        | Тур | Max           | Units |

|-----------|-------------------------------------------------------------|---------------------------------------------------|------------|-----|---------------|-------|

| Tdrate    | Full-speed data rate average bit rate                       |                                                   | 12 - 0.25% | 12  | 12 +<br>0.25% | MHz   |

| Tdjr1     | Receiver data jitter tolerance to next transition           |                                                   | -8         | -   | 8             | ns    |

| Tdjr2     | Receiver data jitter tolerance to pair transition           |                                                   | -5         | -   | 5             | ns    |

| Tudj1     | Driver differential jitter to next transition               |                                                   | -3.5       | -   | 3.5           | ns    |

| Tudj2     | Driver differential jitter to pair transition               |                                                   | -4         | -   | 4             | ns    |

| Tfdeop    | Source jitter for differential transition to SE0 transition |                                                   | -2         | -   | 5             | ns    |

| Tfeopt    | Source SE0 interval of EOP                                  |                                                   | 160        | -   | 175           | ns    |

| Tfeopr    | Receiver SE0 interval of EOP                                |                                                   | 82         | -   | -             | ns    |

| Tfst      | Width of SE0 interval during differential transition        |                                                   | -          | -   | 14            | ns    |

| Fgpio_out | GPIO mode output operating                                  | $3 \text{ V} \leq \text{Vddd} \leq 5.5 \text{ V}$ | -          | -   | 20            | MHz   |

|           | frequency                                                   | Vddd = 1.71 V                                     | -          | -   | 6             | MHz   |

| Tr_gpio   | Rise time, GPIO mode, 10%/90%                               | Vddd > 3 V, 25 pF load                            | _          | _   | 12            | ns    |

|           | Vddd                                                        | Vddd = 1.71 V, 25 pF load                         | _          | _   | 40            | ns    |

| Tf_gpio   | Fall time, GPIO mode, 90%/10% Vddd                          | Vddd > 3 V, 25 pF load                            | _          | _   | 12            | ns    |

|           |                                                             | Vddd = 1.71 V, 25 pF load                         | _          | _   | 40            | ns    |

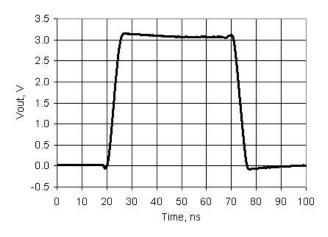

Figure 11-15. USBIO Output Rise and Fall Times, GPIO Mode,  $V_{DDD}$  = 3.3 V, 25 pF Load

Table 11-12. USB Driver AC Specifications

| Parameter | Description                     | Conditions            | Min | Тур | Max  | Units |

|-----------|---------------------------------|-----------------------|-----|-----|------|-------|

| Tr        | Transition rise time            |                       | _   | _   | 20   | ns    |

| Tf        | Transition fall time            |                       | -   | _   | 20   | ns    |

| TR        | Rise/fall time matching         | VUSB_5, VUSB_3.3, see | 90% | -   | 111% |       |

| Vcrs      | Output signal crossover voltage |                       | 1.3 | -   | 2    | V     |

Document Number: 001-57331 Rev. \*G Page 83 of 143

# 11.5 Analog Peripherals

Specifications are valid for -40  $^{\circ}$  C  $\leq$  Ta  $\leq$  125  $^{\circ}$  C and Tj  $\leq$  150  $^{\circ}$  C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

# 11.5.1 Opamp

Table 11-15. Opamp DC Specifications

| Parameter       | Description                                 | Conditions                                                                                                                                                  | Min       | Тур  | Max          | Units   |

|-----------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|--------------|---------|

| Vioff           | Input offset voltage                        | $-40^{\circ}\text{C} \le \text{Ta} \le 85^{\circ}\text{C} \text{ and Tj} \le 100^{\circ}\text{C}$                                                           | -         | -    | ±2.5         | mV      |

|                 |                                             | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C                                                                                                                           | -         | -    | ±5.0         | mV      |

| TCVos           | Input offset voltage drift with temperature | Power mode = high                                                                                                                                           | -         | _    | ±30          | μV / °C |

| Ge1             | Gain error, unity gain buffer mode          | Rload = 1 kΩ                                                                                                                                                | -         | -    | <u>+</u> 0.1 | %       |

| Vi              | Input voltage range                         |                                                                                                                                                             | Vssa      | -    | Vdda         | mV      |

| Vo              | Output voltage range                        | Output load = 1 mA                                                                                                                                          | Vssa + 50 | -    | Vdda - 50    | mV      |

| lout            | Output current                              | Output voltage is between Vssa +500 mV and Vdda -500 mV, and Vdda > 2.7 V, -40 $^{\circ}$ C $\leq$ Ta $\leq$ 85 $^{\circ}$ C and Tj $\leq$ 100 $^{\circ}$ C | 25        | -    | -            | mA      |

|                 |                                             | Output voltage is between Vssa +500 mV and Vdda -500 mV, and Vdda > 2.7 V, -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C                                 | 20        | -    | -            | mA      |

| lout            | Output current                              | Output voltage is between Vssa<br>+500 mV and Vdda -500 mV, and<br>Vdda > 1.7 V and Vdda < 2.7 V                                                            | 16        | -    | -            | mA      |

| I <sub>DD</sub> | Quiescent current                           | Power mode = min                                                                                                                                            | _         | 250  | 400          | μA      |

|                 |                                             | Power mode = low                                                                                                                                            | -         | 250  | 400          | μA      |

|                 |                                             | Power mode = med                                                                                                                                            | _         | 330  | 950          | μA      |

|                 |                                             | Power mode = high                                                                                                                                           | _         | 1000 | 2500         | μA      |

| CMRR            | Common mode rejection ratio <sup>[29]</sup> |                                                                                                                                                             | 80        | -    | _            | dB      |

| PSRR            | Power supply rejection ratio                | Vdda ≥ 2.7 V                                                                                                                                                | 85        | -    | _            | dB      |

|                 |                                             | Vdda < 2.7 V                                                                                                                                                | 70        | _    | _            | dB      |

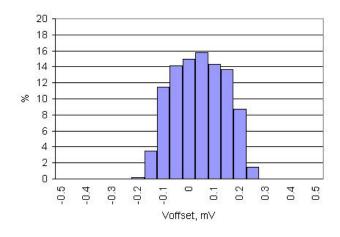

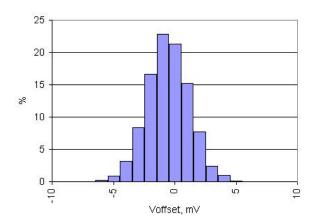

Figure 11-16. Opamp Voffset Histogram, 3388 samples/847 parts, 25 °C, Vdda = 5 V

Document Number: 001-57331 Rev. \*G Page 85 of 143

# Table 11-17. 12-bit Delta-sigma ADC DC Specifications (continued)

| Parameter          | Description                                                                     | Conditions                                         | Min | Тур                 | Max  | Units |

|--------------------|---------------------------------------------------------------------------------|----------------------------------------------------|-----|---------------------|------|-------|

| Rin_Buff           | ADC input resistance                                                            | Input buffer used                                  | 10  | _                   | _    | МΩ    |

| Rin_ADC12          | ADC input resistance                                                            | Input buffer bypassed, 12 bit,<br>Range = ±1.024 V | _   | 148 <sup>[36]</sup> | _    | kΩ    |

| Vextref            | ADC external reference input voltage                                            | Pins P0[3], P3[2]                                  | 0.9 | _                   | 1.3  | V     |

| Current Co         | •                                                                               |                                                    |     |                     |      |       |

| I <sub>DD_12</sub> | I <sub>DDD</sub> + I <sub>DDA</sub> Current consumption, 12 bit <sup>[37]</sup> | 192 ksps, unbuffered                               | -   | _                   | 1.95 | mA    |

| I <sub>BUFF</sub>  | Buffer current consumption <sup>[37]</sup>                                      |                                                    | _   | _                   | 2.5  | mA    |

#### Notes

37. Based on device characterization (Not production tested).

Document Number: 001-57331 Rev. \*G Page 90 of 143

<sup>36.</sup> By using switched capacitors at the ADC input an effective input resistance is created. Holding the gain and number of bits constant, the resistance is proportional to the inverse of the clock frequency. This value is calculated, not measured. For more information see the Technical Reference Manual.

# 11.5.6 IDAC

All specifications are based on use of the low-resistance IDAC output pins (see Pin Descriptions on page 9 for details). See the IDAC component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

Table 11-24. IDAC (Current Digital-to-Analog Converter) DC Specifications

| Parameter        | Description                           | Conditions                                                                                   | Min | Тур    | Max  | Units  |

|------------------|---------------------------------------|----------------------------------------------------------------------------------------------|-----|--------|------|--------|

| Resolution       |                                       |                                                                                              | -   | 8      | -    |        |

| I <sub>OUT</sub> | Output current at code = 255          | Range = 2.04 mA, code = 255,<br>$V_{DDA} \ge 2.7$ V, Rload = 600 $\Omega$                    | -   | 2.04   | _    | mA     |

|                  |                                       | Range = 2.04 mA, high speed mode, code = 255, $V_{DDA} \le 2.7$ V, Rload = 300 $\Omega$      | _   | 2.04   | -    | mA     |

|                  |                                       | Range = 255 $\mu$ A, code = 255, Rload<br>= 600 $\Omega$                                     | _   | 255    | _    | μΑ     |

|                  |                                       | Range = 31.875 $\mu$ A, code = 255,<br>Rload = 600 $\Omega$                                  | _   | 31.875 | _    | μΑ     |

|                  | Monotonicity                          |                                                                                              | -   | -      | Yes  |        |

| INL              | Integral nonlinearity                 | Sink mode, range = 255 $\mu$ A, Codes 8 – 255, Rload = 2.4 $k\Omega$ , Cload = 15 pF         | _   | ±0.9   | ±1   | LSB    |

|                  |                                       | Source mode, range = 255 $\mu$ A,<br>Codes 8 – 255, Rload = 2.4 $k\Omega$ ,<br>Cload = 15 pF | _   | ±1.2   | ±1.5 | LSB    |

| DNL              | Differential nonlinearity             | Sink mode, range = 255 $\mu$ A, Rload = 2.4 $k\Omega$ , Cload = 15 pF                        | _   | ±0.3   | ±1   | LSB    |

|                  |                                       | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 k $\Omega$ , Cload = 15 pF                  | _   | ±0.3   | ±1   | LSB    |

| Ezs              | Zero scale error                      | -40°C ≤ Ta ≤ 85°C and Tj ≤ 100°C                                                             | -   | 0      | ±1   | LSB    |

|                  |                                       | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C                                                            | -   | -      | ±2   | LSB    |

| Eg               | Gain error                            | Range = 2.04 mA, 25 °C                                                                       | -   | _      | ±2.5 | %      |

|                  |                                       | Range = 255 μA, 25 ° C                                                                       | -   | _      | ±2.5 | %      |

|                  |                                       | Range = 31.875 μA, 25 ° C                                                                    | -   | _      | ±3.5 | %      |

| TC_Eg            | Temperature coefficient of gain error | Range = 2.04 mA                                                                              | _   | _      | 0.04 | % / °C |

|                  |                                       | Range = 255 µA                                                                               | -   | _      | 0.04 | % / °C |

|                  |                                       | Range = 31.875 μA                                                                            | -   | _      | 0.05 | % / °C |

| Vcompliance      | Dropout voltage, source or sink mode  | Voltage headroom at max current,<br>Rload to Vdda or Rload to Vssa,<br>Vdiff from Vdda       | 1   | _      | -    | V      |

Document Number: 001-57331 Rev. \*G Page 95 of 143

Table 11-24. IDAC (Current Digital-to-Analog Converter) DC Specifications (continued)

| Parameter       | Description                 | Conditions                                      | Min | Тур | Max | Units |

|-----------------|-----------------------------|-------------------------------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | Operating current, code = 0 | Low speed mode, source mode, range = 31.875 µA  | -   | 44  | 100 | μΑ    |

|                 |                             | Low speed mode, source mode, range = 255 µA,    | -   | 33  | 100 | μΑ    |

|                 |                             | Low speed mode, source mode, range = 2.04 mA    | -   | 33  | 100 | μΑ    |

|                 |                             | Low speed mode, sink mode, range = 31.875 µA    | -   | 36  | 100 | μΑ    |

|                 |                             | Low speed mode, sink mode, range = 255 µA       | -   | 33  | 100 | μΑ    |

|                 |                             | Low speed mode, sink mode, range = 2.04 mA      | -   | 33  | 100 | μΑ    |

|                 |                             | High speed mode, source mode, range = 31.875 μA | -   | 310 | 500 | μΑ    |

|                 |                             | High speed mode, source mode, range = 255 μA    | -   | 305 | 500 | μΑ    |

|                 |                             | High speed mode, source mode, range = 2.04 mA   | -   | 305 | 500 | μΑ    |

|                 |                             | High speed mode, sink mode, range = 31.875 μA   | -   | 310 | 500 | μΑ    |

|                 |                             | High speed mode, sink mode, range = 255 μA      | -   | 300 | 500 | μΑ    |

|                 |                             | High speed mode, sink mode, range = 2.04 mA     | -   | 300 | 500 | μΑ    |

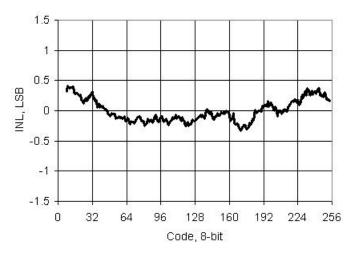

Figure 11-27. IDAC INL vs Input Code, Range = 255  $\mu$ A, Source Mode

Document Number: 001-57331 Rev. \*G Page 96 of 143

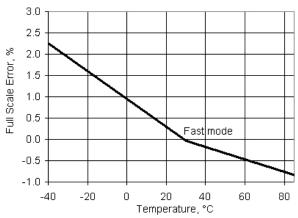

Figure 11-34. IDAC Full Scale Error vs Temperature, Range = 255  $\mu$ A, Sink Mode

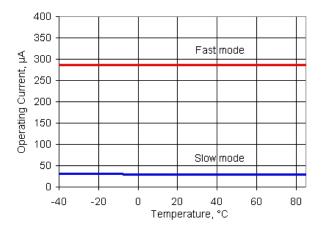

Figure 11-35. IDAC Operating Current vs Temperature, Range = 255 µA, Code = 0, Source Mode

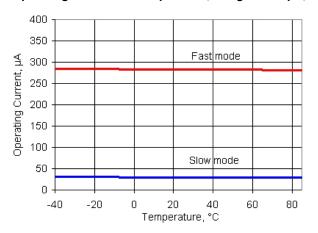

Figure 11-36. IDAC Operating Current vs Temperature, Range = 255  $\mu$ A, Code = 0, Sink Mode

Table 11-25. IDAC (Current Digital-to-Analog Converter) AC Specifications

| Parameter           | Description              | Conditions                                                                                             | Min | Тур | Max | Units     |

|---------------------|--------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|-----------|

| Fdac                | Update rate              |                                                                                                        | _   | _   | 8   | Msps      |

| T <sub>SETTLE</sub> | Settling time to 0.5 LSB | Range = 31.875 $\mu$ A or 255 $\mu$ A, full scale transition, High speed mode, 600 $\Omega$ 15-pF load | -   | _   | 125 | ns        |

|                     | Current noise            | Range = 255 µA, source mode,<br>High speed mode, Vdda = 5 V,<br>10 kHz                                 | ı   | 340 | ı   | pA/sqrtHz |

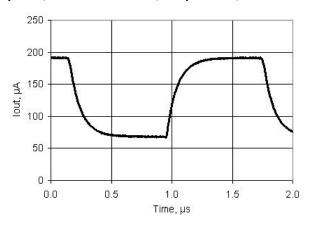

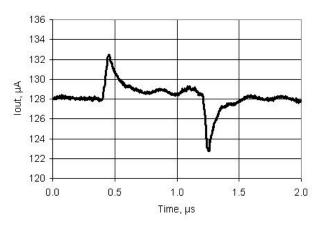

Figure 11-37. IDAC Step Response, Codes 0x40 - 0xC0, 255 µA Mode, Source Mode, High speed mode, Vdda = 5 V

Figure 11-38. IDAC Glitch Response, Codes 0x7F - 0x80, 255 μA Mode, Source Mode, High speed mode, Vdda = 5 V

Document Number: 001-57331 Rev. \*G Page 100 of 143

# 11.5.10 Programmable Gain Amplifier

The PGA is created using a SC/CT Analog Block, see the PGA component data sheet in PSoC Creator for full AC/DC specifications, and APIs and example code.

Unless otherwise specified, operating conditions are:

- Operating temperature = 25 °C for typical values

- Unless otherwise specified, all charts and graphs show typical values

Table 11-32. PGA DC Specifications

| Parameter | Description                                 | Conditions                                                                   | Min                        | Тур | Max                     | Units    |

|-----------|---------------------------------------------|------------------------------------------------------------------------------|----------------------------|-----|-------------------------|----------|

| Vin       | Input voltage range                         | Power mode = minimum                                                         | Vssa                       | -   | Vdda                    | V        |

| Vos       | Input offset voltage                        | Power mode = high,<br>gain = 1                                               | _                          | _   | 10                      | mV       |

|           | Gain Error <sup>[29]</sup>                  | Non inverting mode, reference = Vs                                           | ssa                        |     |                         |          |

| Ge1       | Gain = 1                                    | Rin of 40K, -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                  | _                          | _   | ±0.15                   | %        |

|           |                                             | Rin of 40K, -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C                 | _                          | _   | ±0.15                   | %        |

| Ge16      | Gain = 16                                   | Rin of 40K, -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                  | _                          | _   | ±2.5                    | %        |

|           |                                             | Rin of 40K, -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C                 | _                          | _   | ±4                      | %        |

| Ge50      | Gain = 50                                   | Rin of 40K, -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                  | _                          | _   | ±5                      | %        |

|           |                                             | Rin of 40K, -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C                 | _                          | _   | ±6                      | %        |

| TCVos     | Input offset voltage drift with temperature | Power mode = high,<br>gain = 1                                               | _                          | _   | ±30                     | μV/°C    |

| Vonl      | DC output nonlinearity                      | Gain = 1                                                                     | _                          | _   | ±0.01                   | % of FSR |

| Cin       | Input capacitance                           |                                                                              | _                          | _   | 7                       | pF       |

| Voh       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = $100 \text{ k}\Omega$ to $V_{DDA}/2$ | V <sub>DDA</sub> –<br>0.15 | _   | -                       | V        |

| Vol       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = $100 \text{ k}\Omega$ to $V_{DDA}/2$ | _                          | _   | V <sub>SSA</sub> + 0.15 | V        |

| Vsrc      | Output voltage under load                   | lload = 250 μA, Vdda ≥ 2.7V, power mode = high                               | _                          | _   | 300                     | mV       |

| ldd       | Operating current                           | Power mode = high                                                            | _                          | 1.5 | 1.65                    | mA       |

| PSRR      | Power supply rejection ratio                |                                                                              | 48                         | _   | -                       | dB       |

Document Number: 001-57331 Rev. \*G Page 110 of 143

Figure 11-53. PGA Voffset Histogram, 4096 samples / 1024 parts

Table 11-33. PGA AC Specifications

| Parameter      | Description         | Conditions                                                                 | Min | Тур | Max | Units     |

|----------------|---------------------|----------------------------------------------------------------------------|-----|-----|-----|-----------|

| BW1            | -3 dB bandwidth     | Power mode = high,<br>gain = 1, input = 100 mV<br>peak-to-peak, CI = 40 pF | 5.5 | 8   | _   | MHz       |

| SR1            | Slew rate           | Power mode = high,<br>gain = 1, 20% to 80%                                 | 3   | _   | _   | V/µs      |

| e <sub>n</sub> | Input noise density | Power mode = high,<br>Vdda = 5 V, at 100 kHz                               | _   | 43  | -   | nV/sqrtHz |

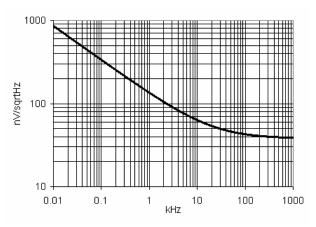

Figure 11-54. Noise vs. Frequency, Vdda = 5 V, Power Mode = High

# 11.5.11 Temperature Sensor

Table 11-34. Temperature Sensor Specifications

| Parameter            | Description | Conditions               | Min | Тур | Max | Units |

|----------------------|-------------|--------------------------|-----|-----|-----|-------|

| Temp sensor accuracy |             | Range: –40 °C to +150 °C |     | ±5  |     | °C    |

Document Number: 001-57331 Rev. \*G Page 111 of 143

# 11.8.3 Interrupt Controller

# Table 11-65. Interrupt Controller AC Specifications

| Parameter | Description                                                           | Conditions                                                              | Min | Тур | Max | Units   |

|-----------|-----------------------------------------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|---------|

|           | Delay from Interrupt signal input to ISR code execution from ISR code | Includes worse case completion of longest instruction DIV with 6 cycles | -   | 1   | 25  | Tcy CPU |

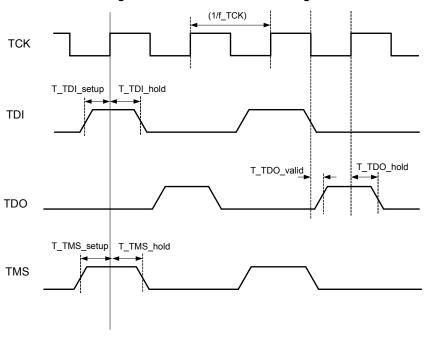

# 11.8.4 JTAG Interface

# Table 11-66. JTAG Interface AC Specifications<sup>[29]</sup>

| Parameter   | Description                  | Conditions                                           | Min           | Тур | Max                | Units |

|-------------|------------------------------|------------------------------------------------------|---------------|-----|--------------------|-------|

| f_TCK       | TCK frequency                | $3.3 \text{ V} \leq \text{V}_{DDD} \leq 5 \text{ V}$ | _             | _   | 14 <sup>[58]</sup> | MHz   |

|             |                              | 1.71 V ≤ V <sub>DDD</sub> < 3.3 V                    | _             | _   | 7 <sup>[58]</sup>  | MHz   |

| T_TDI_setup | TDI setup before TCK high    |                                                      | (T/10) –<br>5 | _   | _                  | ns    |

| T_TMS_setup | TMS setup before TCK high    |                                                      | T/4           | _   | _                  |       |

| T_TDI_hold  | TDI, TMS hold after TCK high | T = 1/f_TCK max                                      | T/4           | _   | _                  |       |

| T_TDO_valid | TCK low to TDO valid         | T = 1/f_TCK max                                      | _             | _   | 2T/5               |       |

| T_TDO_hold  | TDO hold after TCK high      | T = 1/f_TCK max                                      | T/4           | _   | _                  |       |

Figure 11-60. JTAG Interface Timing

# 13. Packaging

Table 13-1. Package Characteristics

| Parameter      | Description                            | Conditions | Min | Тур   | Max | Units |

|----------------|----------------------------------------|------------|-----|-------|-----|-------|

| T <sub>A</sub> | Operating ambient temperature          |            | -40 | 25.00 | 125 | °C    |

| T <sub>J</sub> | Operating junction temperature         |            | -40 | _     | 150 | °C    |

| $T_{JA}$       | Package $\theta_{JA}$ (48-pin SSOP)    |            | _   | 49    | -   | °C/W  |

| $T_{JA}$       | Package $\theta_{JA}$ (100-pin TQFP)   |            | -   | 34    | _   | °C/W  |

| $T_JC$         | Package θ <sub>JC</sub> (48-pin SSOP)  |            | _   | 24    | -   | °C/W  |

| $T_JC$         | Package θ <sub>JC</sub> (100-pin TQFP) |            | _   | 10    | _   | °C/W  |

Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 100-pin TQFP | MSL 3 |

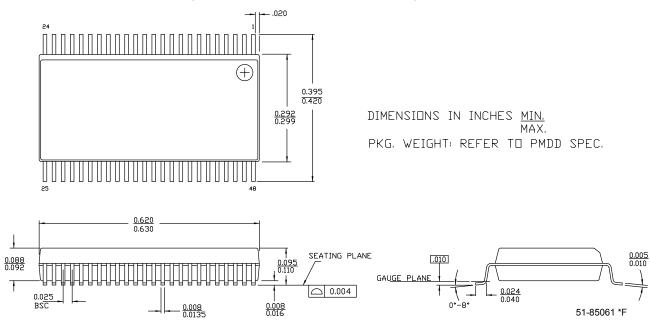

Figure 13-1. 48-pin (300 mil) SSOP Package Outline

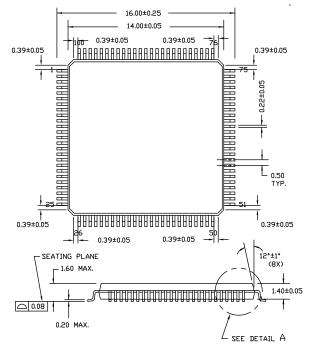

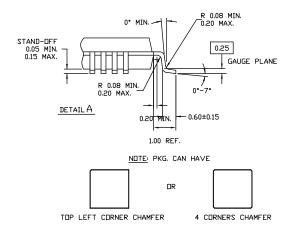

Figure 13-2. 100-pin TQFP (14 × 14 × 1.4 mm) Package Outline

- JEDEC STD REF MS-026

BDDY LENGTH DIMENSION DOES NOT INCLUDE MOLD PROTRUSION/END FLASH

MOLD PROTRUSION/END FLASH SHALL NOT EXCEED 0.0098 in (0.25 mm) PER SIDE

BDDY LENGTH DIMENSIONS ARE MAX PLASTIC BODY SIZE INCLUDING MOLD MISMATCH

- 3. DIMENSIONS IN MILLIMETERS

51-85048 \*I

Document Number: 001-57331 Rev. \*G

Table 14-1. Acronyms Used in this Document (continued)

| Acronym           | Description                                                  |

|-------------------|--------------------------------------------------------------|

| PHUB              | peripheral hub                                               |

| PHY               | physical layer                                               |

| PICU              | port interrupt control unit                                  |

| PLA               | programmable logic array                                     |

| PLD               | programmable logic device, see also PAL                      |

| PLL               | phase-locked loop                                            |

| PMDD              | package material declaration data sheet                      |

| POR               | power-on reset                                               |

| PRES              | precise low-voltage reset                                    |

| PRS               | pseudo random sequence                                       |

| PS                | port read data register                                      |

| PSoC <sup>®</sup> | Programmable System-on-Chip™                                 |

| PSRR              | power supply rejection ratio                                 |

| PWM               | pulse-width modulator                                        |

| RAM               | random-access memory                                         |

| RISC              | reduced-instruction-set computing                            |

| RMS               | root-mean-square                                             |

| RTC               | real-time clock                                              |

| RTL               | register transfer language                                   |

| RTR               | remote transmission request                                  |

| RX                | receive                                                      |

| SAR               | successive approximation register                            |

| SC/CT             | switched capacitor/continuous time                           |

| SCL               | I <sup>2</sup> C serial clock                                |

| SDA               | I <sup>2</sup> C serial data                                 |

| S/H               | sample and hold                                              |

| SINAD             | signal to noise and distortion ratio                         |

| SIO               | special input/output, GPIO with advanced features. See GPIO. |

| SOC               | start of conversion                                          |

Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                            |

|---------|------------------------------------------------------------------------|

| SOF     | start of frame                                                         |

| SPI     | Serial Peripheral Interface, a communications protocol                 |

| SR      | slew rate                                                              |

| SRAM    | static random access memory                                            |

| SRES    | software reset                                                         |

| SWD     | serial wire debug, a test protocol                                     |

| SWV     | single-wire viewer                                                     |

| TD      | transaction descriptor, see also DMA                                   |

| THD     | total harmonic distortion                                              |

| TIA     | transimpedance amplifier                                               |

| TRM     | technical reference manual                                             |

| TTL     | transistor-transistor logic                                            |

| TX      | transmit                                                               |

| UART    | Universal Asynchronous Transmitter Receiver, a communications protocol |

| UDB     | universal digital block                                                |

| USB     | Universal Serial Bus                                                   |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port              |

| VDAC    | voltage DAC, see also DAC, IDAC                                        |

| WDT     | watchdog timer                                                         |

| WOL     | write once latch, see also NVL                                         |

| WRES    | watchdog timer reset                                                   |

| XRES    | external reset I/O pin                                                 |

| XTAL    | crystal                                                                |

# 15. Reference Documents

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 3 Registers TRM

Document Number: 001-57331 Rev. \*G Page 138 of 143