Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Details                    |                                                                                |

| Product Status             | Obsolete                                                                       |

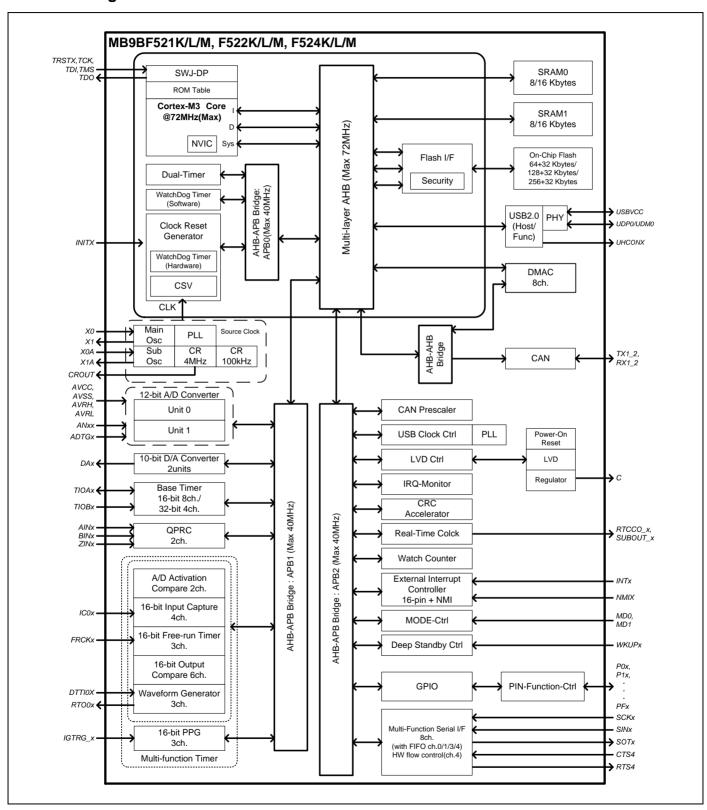

| Core Processor             | ARM® Cortex®-M3                                                                |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | CANbus, CSIO, I <sup>2</sup> C, LINbus, UART/USART, USB                        |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                        |

| Number of I/O              | 65                                                                             |

| Program Memory Size        | 288KB (288K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                    |

| Data Converters            | A/D 26x12b; D/A 2x10b                                                          |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-LQFP                                                                        |

| Supplier Device Package    | 80-LQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb9bf524mpmc-g-jne2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3. Pin Assignment

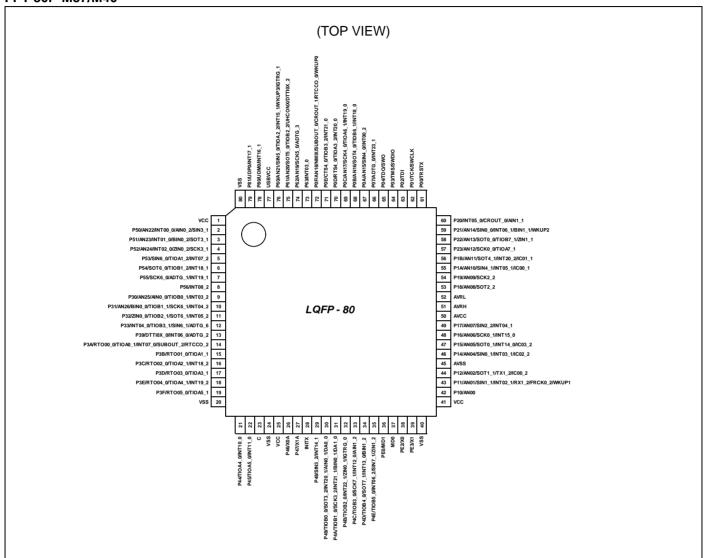

## FPT-80P-M37/M40

#### Note:

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

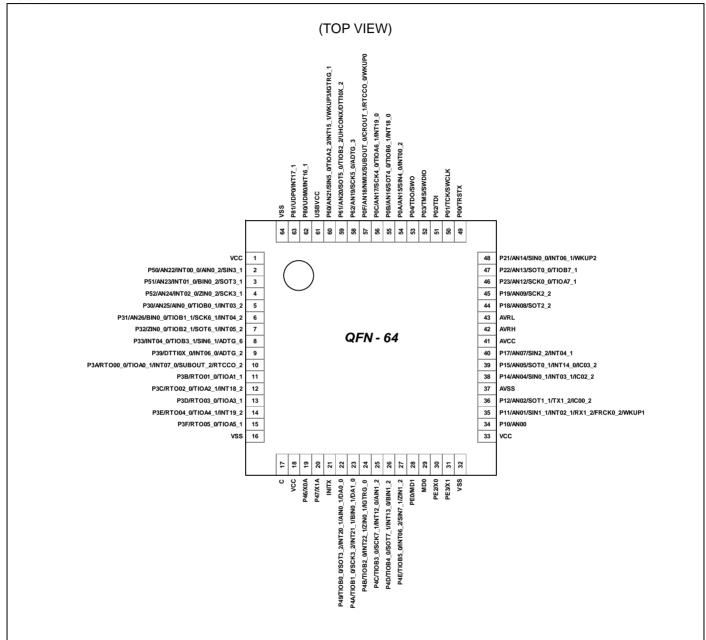

## LCC-64P-M24

### Note:

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

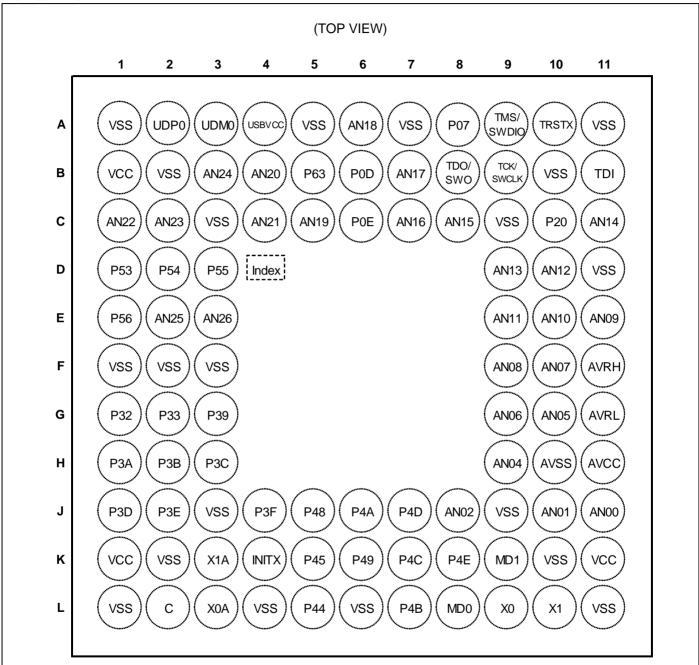

#### **BGA-96P-M07**

#### Note:

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

|         | Pin No |                   |                   |                |                     | Din state      |

|---------|--------|-------------------|-------------------|----------------|---------------------|----------------|

| LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | Pin Name       | I/O circuit<br>type | Pin state type |

|         |        |                   |                   | P3E            |                     |                |

|         |        |                   |                   | RTO04_0        |                     |                |

| 18      | J2     | 14                | 10                | (PPG04_0)      | G                   | L              |

|         |        |                   |                   | TIOA4_1        |                     |                |

|         |        |                   |                   | INT19_2        |                     |                |

|         |        |                   |                   | P3F            |                     |                |

| 19      | J4     | 15                | 11                | RTO05_0        | G                   | К              |

| 19      | 34     | 13                | ''                | (PPG04_0)      |                     |                |

|         |        |                   |                   | TIOA5_1        |                     |                |

| 20      | L1     | 16                | 12                | VSS            | -                   |                |

|         |        |                   |                   | P44            |                     |                |

| 21      | L5     | -                 | -                 | TIOA4_0        | G                   | L              |

|         |        |                   |                   | INT10_0        |                     | -              |

| 22      | K5     | _                 | _                 | P45<br>TIOA5_0 | G                   | L              |

| 22      | NO     |                   |                   | INT11_0        | $\dashv$            |                |

| 23      | L2     | 17                | 13                | C              | -                   |                |

| 24      | L4     | -                 | -                 | VSS            | -                   |                |

| 25      | K1     | 18                | 14                | VCC            | -                   |                |

|         |        |                   |                   | P46            |                     |                |

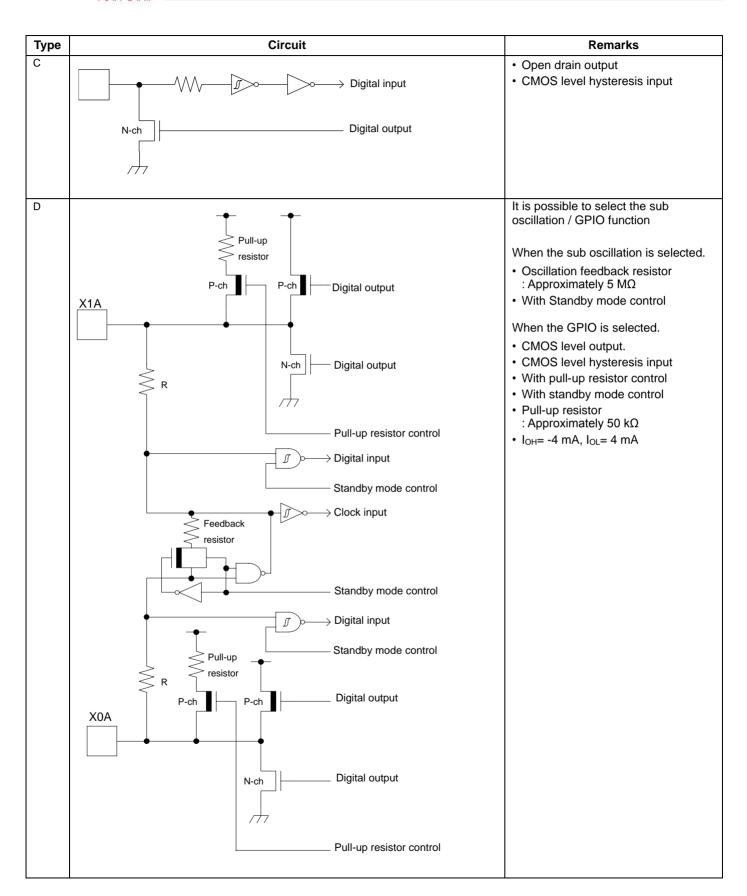

| 26      | L3     | 19                | 15                | X0A            | D                   | F              |

|         |        |                   |                   | P47            |                     |                |

| 27      | K3     | 20                | 16                | X1A            | D                   | G              |

| 28      | K4     | 21                | 17                | INITX          | В                   | С              |

|         |        |                   | 1.                | P48            |                     |                |

| 29      | J5     | _                 | _                 | INT14_1        | E                   | L              |

|         |        |                   |                   | SIN3_2         |                     | -              |

|         |        |                   |                   | P49            |                     |                |

|         |        |                   |                   | TIOB0_0        |                     |                |

|         |        |                   | 18                | INT20_1        |                     |                |

| 30      | K6     | 22                |                   | DA0_0          | L                   | L              |

|         |        |                   |                   | SOT3_2         | _                   | -              |

|         |        |                   | _                 | (SDA3_2)       |                     |                |

|         |        |                   |                   | AIN0_1         |                     |                |

|         |        |                   |                   | P4A            |                     |                |

|         |        |                   |                   | TIOB1_0        |                     |                |

|         |        |                   | 19                | INT21_1        |                     |                |

| 31      | J6     | 23                |                   | DA1_0          | L                   | L              |

|         |        |                   |                   | SCK3_2         |                     |                |

|         |        |                   | _                 | (SCL3_2)       |                     |                |

|         |        |                   |                   | BIN0_1         |                     |                |

|         | i      |                   | 1                 |                |                     | 1              |

|              |             |                                               |         | Pin No |                   |                   |  |  |  |

|--------------|-------------|-----------------------------------------------|---------|--------|-------------------|-------------------|--|--|--|

| Pin function | Pin name    | Function description                          | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 |  |  |  |

| External     | INT00_0     | Fortessellisterment on several CO insertation | 2       | C1     | 2                 | 2                 |  |  |  |

| Interrupt    | INT00_2     | External interrupt request 00 input pin       | 67      | C8     | 54                | -                 |  |  |  |

|              | INT01 0     | External interrupt request 01 input pin       | 3       | C2     | 3                 | 3                 |  |  |  |

|              | INT02 0     |                                               | 4       | B3     | 4                 | 4                 |  |  |  |

|              | INT02_1     | External interrupt request 02 input pin       | 43      | J10    | 35                | 26                |  |  |  |

|              | INT03 0     |                                               | 73      | B5     | -                 | -                 |  |  |  |

|              | INT03 1     | External interrupt request 03 input pin       | 46      | H9     | 38                | 29                |  |  |  |

|              | INT03 2     |                                               | 9       | E2     | 5                 | -                 |  |  |  |

|              | INT04_0     |                                               | 12      | G2     | 8                 | -                 |  |  |  |

|              | INT04 1     | External interrupt request 04 input pin       | 49      | F10    | 40                | -                 |  |  |  |

|              | INT04 2     |                                               | 10      | E3     | 6                 | -                 |  |  |  |

|              | INT05 0     |                                               | 60      | P20    | -                 | -                 |  |  |  |

|              | INT05 1     | External interrupt request 05 input pin       | 55      | E10    | -                 | -                 |  |  |  |

|              | INT05 2     |                                               | 11      | G1     | 7                 | -                 |  |  |  |

|              | INT06 0     |                                               | 13      | G3     | 9                 | 5                 |  |  |  |

|              | INT06 1     | External interrupt request 06 input pin       | 59      | C11    | 48                | 36                |  |  |  |

|              | INT06 2     |                                               | 35      | K8     | 27                | -                 |  |  |  |

|              | INT07 0     |                                               | 14      | H1     | 10                | 6                 |  |  |  |

|              | INT07_2     | External interrupt request 07 input pin       | 5       | D1     | -                 | -                 |  |  |  |

|              | INT08 2     | External interrupt request 08 input pin       | 8       | E1     | -                 | -                 |  |  |  |

|              | INT10_0     | External interrupt request 10 input pin       | 21      | L5     | -                 | -                 |  |  |  |

|              | INT11_0     | External interrupt request 11 input pin       | 22      | K5     | -                 | -                 |  |  |  |

|              | INT12_0     | External interrupt request 12 input pin       | 33      | K7     | 25                | -                 |  |  |  |

|              | INT13 0     | External interrupt request 13 input pin       | 34      | J7     | 26                | -                 |  |  |  |

|              | INT14_0     |                                               | 47      | G10    | 39                | 30                |  |  |  |

|              | INT14_1     | External interrupt request 14 input pin       | 29      | J5     | -                 | -                 |  |  |  |

|              | <br>INT15_0 | F. 11                                         | 48      | G9     | -                 | -                 |  |  |  |

|              | INT15_1     | External interrupt request 15 input pin       | 76      | C4     | 60                | 44                |  |  |  |

|              | INT16_1     | External interrupt request 16 input pin       | 78      | A3     | 62                | 46                |  |  |  |

|              | INT17_1     | External interrupt request 17 input pin       | 79      | A2     | 63                | 47                |  |  |  |

|              | INT18_0     |                                               | 68      | C7     | 55                | -                 |  |  |  |

|              | INT18_1     | External interrupt request 18 input pin       | 6       | D2     | -                 | -                 |  |  |  |

|              | INT18_2     | 7 ' ' ' '                                     | 16      | H3     | 12                | 8                 |  |  |  |

|              | INT19_0     |                                               | 59      | C11    | 56                | -                 |  |  |  |

|              | INT19_1     | External interrupt request 19 input pin       | 7       | D3     | -                 | -                 |  |  |  |

|              | INT19_2     | 7                                             | 18      | J2     | 14                | 10                |  |  |  |

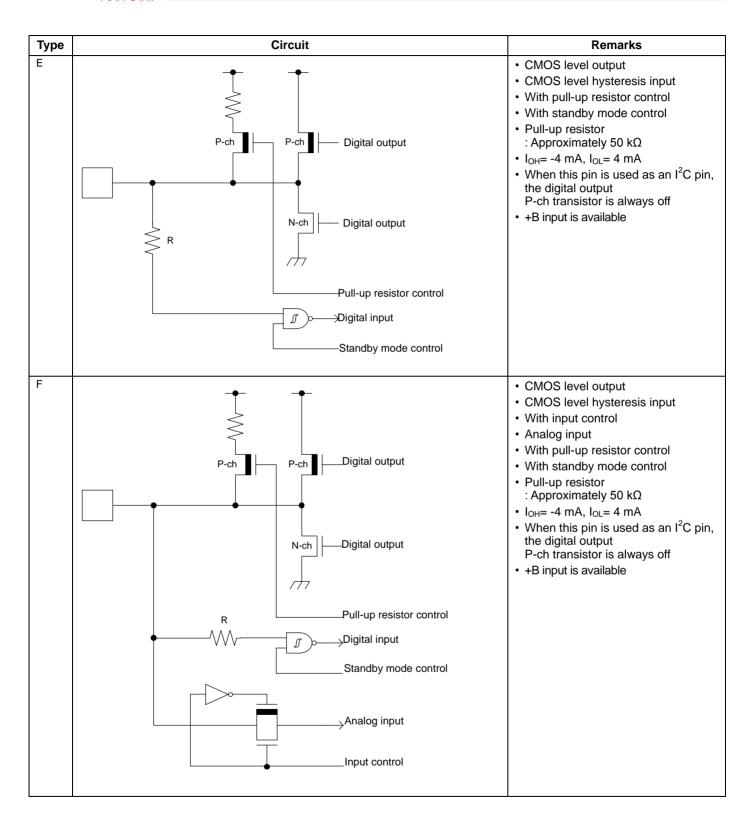

| Type | Circuit                                                                                                                | Remarks                                                                                                                                                                                                                                                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L    | P-ch Digital output  N-ch Digital output  Pull-up resistor control  Digital input  Standby mode Control  Analog output | <ul> <li>CMOS level output</li> <li>CMOS level hysteresis input</li> <li>With input control</li> <li>Analog output</li> <li>With pull-up resistor control</li> <li>With standby mode control</li> <li>Pull-up resistor <ul> <li>Approximately 50 kΩ</li> </ul> </li> <li>I<sub>OH</sub> = -4 mA, I<sub>OL</sub> = 4 mA</li> </ul> |

# 6. Handling Precautions

Any semiconductor devices have inherently a certain rate of failure. The possibility of failure is greatly affected by the conditions in which they are used (circuit conditions, environmental conditions, etc.). This page describes precautions that must be observed to minimize the chance of failure and to obtain higher reliability from your Cypress semiconductor devices.

#### 6.1 Precautions for Product Design

This section describes precautions when designing electronic equipment using semiconductor devices.

#### **Absolute Maximum Ratings**

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of certain established limits, called absolute maximum ratings. Do not exceed these ratings.

#### **Recommended Operating Conditions**

Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their sales representative beforehand.

#### **Processing and Protection of Pins**

These precautions must be followed when handling the pins which connect semiconductor devices to power supply and input/output functions.

- 1. Preventing Over-Voltage and Over-Current Conditions

- Exposure to voltage or current levels in excess of maximum ratings at any pin is likely to cause deterioration within the device, and in extreme cases leads to permanent damage of the device. Try to prevent such overvoltage or over-current conditions at the design stage.

- 2. Protection of Output Pins

- Shorting of output pins to supply pins or other output pins, or connection to large capacitance can cause large current flows. Such conditions if present for extended periods of time can damage the device. Therefore, avoid this type of connection.

- 3. Handling of Unused Input Pins

- Unconnected input pins with very high impedance levels can adversely affect stability of operation. Such pins should be connected through an appropriate resistance to a power supply pin or ground pin.

#### Latch-up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

- 1. Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

- 2. Be sure that abnormal current flows do not occur during the power-on sequence.

#### **Observance of Safety Regulations and Standards**

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

#### **Static Electricity**

Because semiconductor devices are particularly susceptible to damage by static electricity, you must take the following precautions:

- 1. Maintain relative humidity in the working environment between 40% and 70%. Use of an apparatus for ion generation may be needed to remove electricity.

- 2. Electrically ground all conveyors, solder vessels, soldering irons and peripheral equipment.

- 3. Eliminate static body electricity by the use of rings or bracelets connected to ground through high resistance (on the level of 1 MΩ).

- Wearing of conductive clothing and shoes, use of conductive floor mats and other measures to minimize shock loads is recommended.

- 4. Ground all fixtures and instruments, or protect with anti-static measures.

- 5. Avoid the use of styrofoam or other highly static-prone materials for storage of completed board assemblies.

#### 6.3 Precautions for Use Environment

Reliability of semiconductor devices depends on ambient temperature and other conditions as described above.

For reliable performance, do the following:

- 1. Humidity

- Prolonged use in high humidity can lead to leakage in devices as well as printed circuit boards. If high humidity levels are anticipated, consider anti-humidity processing.

- 2. Discharge of Static Electricity

- When high-voltage charges exist close to semiconductor devices, discharges can cause abnormal operation. In such cases, use anti-static measures or processing to prevent discharges.

- 3. Corrosive Gases, Dust, or Oil

- Exposure to corrosive gases or contact with dust or oil may lead to chemical reactions that will adversely affect the device. If you use devices in such conditions, consider ways to prevent such exposure or to protect the devices.

- 4. Radiation, Including Cosmic Radiation

- Most devices are not designed for environments involving exposure to radiation or cosmic radiation. Users should provide shielding as appropriate.

- 5. Smoke, Flame

- CAUTION: Plastic molded devices are flammable, and therefore should not be used near combustible substances. If devices begin to smoke or burn, there is danger of the release of toxic gases.

Customers considering the use of Cypress products in other special environmental conditions should consult with sales representatives.

# 7. Handling Devices

#### Power supply pins

In products with multiple VCC and VSS pins, respective pins at the same potential are interconnected within the device in order to prevent malfunctions such as latch-up. However, all of these pins should be connected externally to the power supply or ground lines in order to reduce electromagnetic emission levels, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with each Power supply pin and GND pin of this device at low impedance. It is also advisable that a ceramic capacitor of approximately 0.1 µF be connected as a bypass capacitor between each Power supply pin and GND pin, between AVCC pin and AVSS pin, between AVRH pin and AVRL pin near this device.

## Stabilizing power supply voltage

A malfunction may occur when the power supply voltage fluctuates rapidly even though the fluctuation is within the recommended operating conditions of the VCC power supply voltage. As a rule, with voltage stabilization, suppress the voltage fluctuation so that the fluctuation in VCC ripple (peak-to-peak value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the VCC value in the recommended operating conditions, and the transient fluctuation rate does not exceed 0.1 V/µs when there is a momentary fluctuation on switching the power supply.

#### Crystal oscillator circuit

Noise near the X0/X1 and X0A/X1A pins may cause the device to malfunction. Design the printed circuit board so that X0/X1, X0A/X1A pins, the crystal oscillator, and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended that the PC board artwork be designed such that the X0/X1 and X0A/X1A pins are surrounded by ground plane as this is expected to produce stable operation.

Evaluate oscillation of your using crystal oscillator by your mount board.

#### Sub crystal oscillator

This series sub oscillator circuit is low gain to keep the low current consumption. The crystal oscillator to fill the following conditions is recommended for sub crystal oscillator to stabilize the oscillation.

· Surface mount type

Size: More than 3.2 mm x 1.5 mm

Load capacitance: Approximately 6 pF to 7 pF

Lead type

Load capacitance: Approximately 6 pF to 7 pF

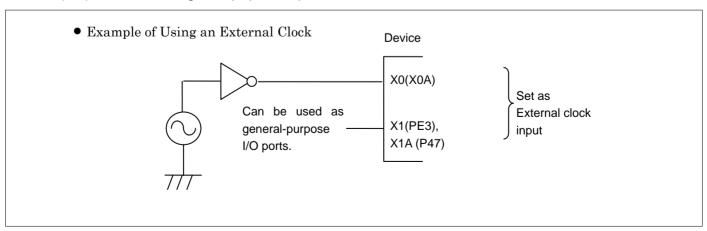

#### Using an external clock

When using an external clock as an input of the main clock, set X0/X1 to the external clock input, and input the clock to X0. X1(PE3) can be used as a general-purpose I/O port.

Similarly, when using an external clock as an input of the sub clock, set X0A/X1A to the external clock input, and input the clock to X0A. X1A (P47) can be used as a general-purpose I/O port.

# 8. Block Diagram

## 12. Electrical Characteristics

## 12.1 Absolute Maximum Ratings

| B                                      | 0 11                   |                       | Rating                                | 11.24 | Domonico                   |  |

|----------------------------------------|------------------------|-----------------------|---------------------------------------|-------|----------------------------|--|

| Parameter                              | Symbol                 | Min                   | Max                                   | Unit  | Remarks                    |  |

| Power supply voltage*1, *2             | V <sub>cc</sub>        | V <sub>SS</sub> - 0.5 | V <sub>SS</sub> + 6.5                 | V     |                            |  |

| Power supply voltage (for USB)*1, *3   | USBV <sub>cc</sub>     | V <sub>SS</sub> - 0.5 | V <sub>ss</sub> + 6.5                 | V     |                            |  |

| Analog power supply voltage*1, *4      | AV <sub>CC</sub>       | V <sub>SS</sub> - 0.5 | V <sub>SS</sub> + 6.5                 | V     |                            |  |

| Analog reference voltage*1, *4         | AVRH                   | V <sub>SS</sub> - 0.5 | V <sub>SS</sub> + 6.5                 | V     |                            |  |

|                                        |                        | V <sub>SS</sub> - 0.5 | V <sub>CC</sub> + 0.5<br>(≤ 6.5V)     | V     | Except for USB pin         |  |

| Input voltage*1                        | Vı                     | V <sub>SS</sub> - 0.5 | USBV <sub>CC</sub> + 0.5<br>(≤ 6.5 V) | V     | USB pin                    |  |

|                                        |                        | V <sub>SS</sub> - 0.5 | V <sub>SS</sub> + 6.5                 | V     | 5 V tolerant               |  |

| Analog pin input voltage*1             | V <sub>IA</sub>        | V <sub>SS</sub> - 0.5 | AV <sub>CC</sub> + 0.5<br>(≤ 6.5 V)   | V     |                            |  |

| Output voltage*1                       | Vo                     | V <sub>SS</sub> - 0.5 | V <sub>CC</sub> + 0.5<br>(≤ 6.5 V)    | V     |                            |  |

| Clamp maximum current                  | I <sub>CLAMP</sub>     | -2                    | +2                                    | mA    | *8                         |  |

| Clamp total maximum current            | Σ[I <sub>CLAMP</sub> ] |                       | +20                                   | mA    | *8                         |  |

|                                        |                        | -                     | 10                                    | mA    | 4 mA type                  |  |

| L level maximum output current*5       | I <sub>OL</sub>        |                       | 20                                    | mA    | 12 mA type                 |  |

|                                        |                        |                       | 39                                    | mA    | The pin doubled as USB I/O |  |

|                                        |                        |                       | 4                                     | mA    | 4 mA type                  |  |

| L level average output current*6       | I <sub>OLAV</sub>      | -                     | 12                                    | mA    | 12 mA type                 |  |

|                                        |                        |                       | 16.5                                  | mA    | The pin doubled as USB I/O |  |

| L level total maximum output current   | ∑I <sub>OL</sub>       | -                     | 100                                   | mA    |                            |  |

| L level total average output current*7 | $\sum I_{OLAV}$        | -                     | 50                                    | mA    |                            |  |

|                                        |                        |                       | - 10                                  | mA    | 4 mA type                  |  |

| H level maximum output current*⁵       | I <sub>OH</sub>        | -                     | - 20                                  | mA    | 12 mA type                 |  |

|                                        |                        |                       | - 39                                  | mA    | The pin doubled as USB I/O |  |

|                                        |                        |                       | - 4                                   | mA    | 4 mA type                  |  |

| H level average output current*6       | I <sub>OHAV</sub>      | -                     | - 12                                  | mA    | 12 mA type                 |  |

|                                        |                        |                       | - 18                                  | mA    | The pin doubled as USB I/O |  |

| H level total maximum output current   | ∑I <sub>OH</sub>       | -                     | - 100                                 | mA    |                            |  |

| H level total average output current*7 | ∑I <sub>OHAV</sub>     | -                     | - 50                                  | mA    |                            |  |

| Power consumption                      | P <sub>D</sub>         | -                     | 300                                   | mW    |                            |  |

| Storage temperature                    | T <sub>STG</sub>       | - 55                  | + 150                                 | °C    |                            |  |

<sup>\*1:</sup> These parameters are based on the condition that  $V_{SS}$  =  $AV_{SS}$  = 0 V.

<sup>\*2:</sup>  $V_{\text{CC}}$  must not drop below  $V_{\text{SS}}$  - 0.5 V.

<sup>\*3:</sup> USBV $_{\text{CC}}$  must not drop below V $_{\text{SS}}$  - 0.5 V.

$<sup>^*4</sup>$ : Ensure that the voltage does not exceed  $V_{CC}$  + 0.5 V, for example, when the power is turned on.

<sup>\*5:</sup> The maximum output current is defined as the value of the peak current flowing through any one of the corresponding pins.

<sup>\*6:</sup> The average output current is defined as the average current value flowing through any one of the corresponding pins for a 100 ms period.

<sup>\*7:</sup> The total average output current is defined as the average current value flowing through all of corresponding pins for a 100 ms.

## **Low-Voltage Detection Current**

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V, T_A = -40^{\circ}C \text{ to } + 105^{\circ}C)$

| Parameter                             | Symbol | Pin  | Pin Conditions                           |         | lue | Unit  | Remarks       |  |

|---------------------------------------|--------|------|------------------------------------------|---------|-----|-------|---------------|--|

| i didilictei                          | Symbol | name | Conditions                               | Typ Max |     | Oilit | Nemarks       |  |

| Low-voltage detection                 |        | WO O | At operation<br>for reset<br>Vcc = 5.5 V | 0.13    | 0.3 | μА    | At not detect |  |

| circuit (LVD) power<br>supply current | ICCLVD | VCC  | At operation for interrupt Vcc = 5.5 V   | 0.13    | 0.3 | μΑ    | At not detect |  |

## **Flash Memory Current**

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V, T_A = -40^{\circ}C \text{ to } + 105^{\circ}C)$

| Parameter                              | Symbol Pin | Symbol Pin Conditions |                | Va  | lue  | Unit  | Remarks     |

|----------------------------------------|------------|-----------------------|----------------|-----|------|-------|-------------|

| rarameter                              | Symbol     | name                  | Conditions     | Тур | Max  | Oilit | iveillai ks |

| Flash memory<br>write/erase<br>current | Iccflash   | vcc                   | At Write/Erase | 9.5 | 11.2 | mA    | *           |

<sup>\*:</sup> The current at which to write or erase Flash memory, "Iccflash" is added to "Icc".

### A/D Converter Current

$(V_{CC} = AV_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = AV_{SS} = AVRL = 0V, T_A = -40^{\circ}C \text{ to } + 105^{\circ}C)$

| Parameter                      | Symbol              | Pin  | Conditions                       | Va   | lue   | Unit  | Remarks |

|--------------------------------|---------------------|------|----------------------------------|------|-------|-------|---------|

| Parameter                      | Symbol              | name | Conditions                       | Тур  | Max   | Offic | Remarks |

| Power supply current           | 1                   | AVCC | At 1unit operation               | 0.69 | 0.90  | mA    |         |

| Power supply current           | ICCAD               | AVCC | At stop                          | 0.25 | 25.84 | μΑ    |         |

| Reference power supply current | I <sub>CCAVRH</sub> | AVRH | At 1unit operation<br>AVRH=5.5 V | 1.1  | 1.97  | mA    |         |

| очрру очноп                    |                     |      | At stop                          | 0.2  | 3.4   | μΑ    |         |

#### **D/A Converter Current**

(V<sub>CC</sub> = AV<sub>CC</sub> = 2.7V to 5.5V, V<sub>SS</sub> = AV<sub>SS</sub> = 0V,  $T_A$  = -40°C to + 105°C)

| Parameter              | Symbol | Pin  | Conditions                                                                            |            | Value      |            | Unit  | Remarks |

|------------------------|--------|------|---------------------------------------------------------------------------------------|------------|------------|------------|-------|---------|

| Parameter Symbol       |        | name | Conditions                                                                            | Min        | Тур        | Max        | Offic | Remarks |

| Power supply current*1 | IDDA*2 | AVCC | At 1unit operation AV <sub>cc</sub> =3.3 V At 1unit operation AV <sub>cc</sub> =5.0 V | 250<br>380 | 315<br>475 | 380<br>580 | μΑ    |         |

|                        | IDSA   |      | At stop                                                                               | -          | -          | 16         | μA    |         |

<sup>\*1:</sup> No-load

Document Number: 002-05649 Rev.\*A

<sup>\*2:</sup> Generates the max current by the CODE about 0x200

## 12.4 AC Characteristics

## 12.4.1 Main Clock Input Characteristics

$$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V, T_A = -40^{\circ}C \text{ to } + 105^{\circ}C)$$

| Parameter                                | Symbol                              | Pin  | Conditions               | Va    | lue | Unit    | Remarks                    |

|------------------------------------------|-------------------------------------|------|--------------------------|-------|-----|---------|----------------------------|

| Faranielei                               | Syllibol                            | name | Conditions               | Min   | Max | Oilit   | Remarks                    |

|                                          |                                     |      | V <sub>CC</sub> ≥ 4.5 V  | 4     | 48  | MHz     | When crystal oscillator is |

| Input frequency                          | f <sub>CH</sub>                     |      | $V_{CC} < 4.5 \text{ V}$ | 4     | 20  | IVII IZ | connected                  |

| input frequency                          | *CH                                 |      | V <sub>CC</sub> ≥ 4.5 V  | 4     | 48  | MHz     | When using external        |

|                                          |                                     |      | $V_{CC} < 4.5 \text{ V}$ | 4     | 20  | IVII IZ | Clock                      |

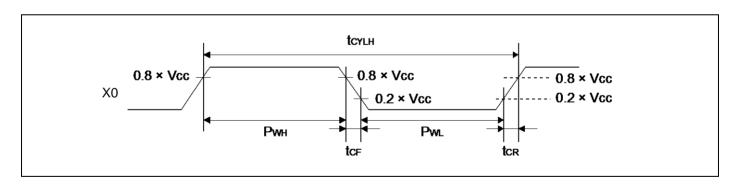

| Input clock cycle                        | t <sub>CYLH</sub>                   | X0,  | V <sub>CC</sub> ≥ 4.5 V  | 20.83 | 250 | ns      | When using external        |

| input clock cycle                        | CYLH                                | X1   | $V_{cc} < 4.5 \text{ V}$ | 50    | 250 | 113     | Clock                      |

| Input clock pulse width                  | _                                   |      | Pwh/tcylh,               | 45    | 55  | %       | When using external        |

|                                          | _                                   |      | PwL/tcYLH                |       |     | , ,     | Clock                      |

| Input clock rising time and falling time | t <sub>CF,</sub><br>t <sub>CR</sub> |      | -                        | -     | 5   | ns      | When using external Clock  |

|                                          | f <sub>CM</sub>                     | -    | -                        | -     | 72  | MHz     | Master clock               |

| latamas la manetica                      | f <sub>CC</sub>                     | -    | -                        | -     | 72  | MHz     | Base clock (HCLK/FCLK)     |

| Internal operating clock frequency*1     | f <sub>CP0</sub>                    | -    | -                        | -     | 40  | MHz     | APB0 bus clock*2           |

| olook frequency                          | f <sub>CP1</sub>                    | -    | -                        | -     | 40  | MHz     | APB1 bus clock*2           |

|                                          | f <sub>CP2</sub>                    | -    | -                        | -     | 40  | MHz     | APB2 bus clock*2           |

|                                          | t <sub>cycc</sub>                   | -    | -                        | 13.8  | -   | ns      | Base clock (HCLK/FCLK)     |

| Internal operating                       | t <sub>CYCP0</sub>                  | -    | -                        | 25    | -   | ns      | APB0 bus clock*2           |

| clock cycle time*1                       | t <sub>CYCP1</sub>                  | -    | -                        | 25    | -   | ns      | APB1 bus clock*2           |

|                                          | t <sub>CYCP2</sub>                  | -    | -                        | 25    | -   | ns      | APB2 bus clock*2           |

<sup>\*1:</sup> For more information about each internal operating clock, see "Chapter: Clock" in "FM3 Family Peripheral Manual".

<sup>\*2:</sup> For about each APB bus which each peripheral is connected to, see "Block Diagram" in this datasheet.

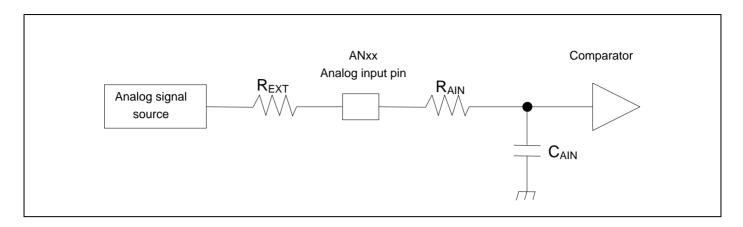

(Equation 1)  $t_S \ge (R_{AIN} + R_{EXT}) \times C_{AIN} \times 9$

t<sub>S</sub>: Sampling time

$R_{AIN}$ : input resistor of A/D = 1.5 kΩ at 4.5 V  $\leq$  AV<sub>CC</sub>  $\leq$  5.5 V ch.0 to ch.7

input resistor of A/D = 1.6 k $\Omega$  at 4.5 V  $\leq$  AV $_{CC} \leq$  5.5 V ch.8 to ch.15 input resistor of A/D = 1.7 k $\Omega$  at 4.5 V  $\leq$  AV $_{CC} \leq$  5.5 V ch.16 to ch.26 input resistor of A/D = 2.2 k $\Omega$  at 2.7 V  $\leq$  AV $_{CC} <$  4.5 V ch.0 to ch.7 input resistor of A/D = 2.3 k $\Omega$  at 2.7 V  $\leq$  AV $_{CC} <$  4.5 V ch.8 to ch.15 input resistor of A/D = 2.4 k $\Omega$  at 2.7 V  $\leq$  AV $_{CC} <$  4.5 V ch.16 to ch.26

C<sub>AIN</sub>: input capacity of A/D = 9.7 pF at 2.7 V  $\leq$  AV<sub>CC</sub>  $\leq$  5.5 V

R<sub>EXT</sub>: Output impedance of external circuit

(Equation 2)  $t_C = t_{CCK} \times 14$

t<sub>C</sub>: Compare time

t<sub>CCK</sub>: Compare clock cycle

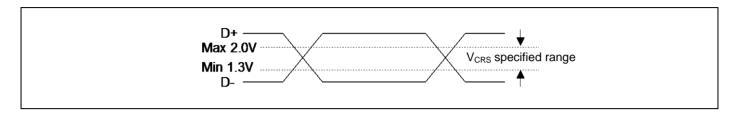

- \*3: The output drive capability of the driver is below 0.3 V at Low-State ( $V_{OL}$ ) (to 3.6 V and 1.5 k $\Omega$  load), and 2.8 V or above (to ground and 15 k $\Omega$  load) at High-State ( $V_{OH}$ ).

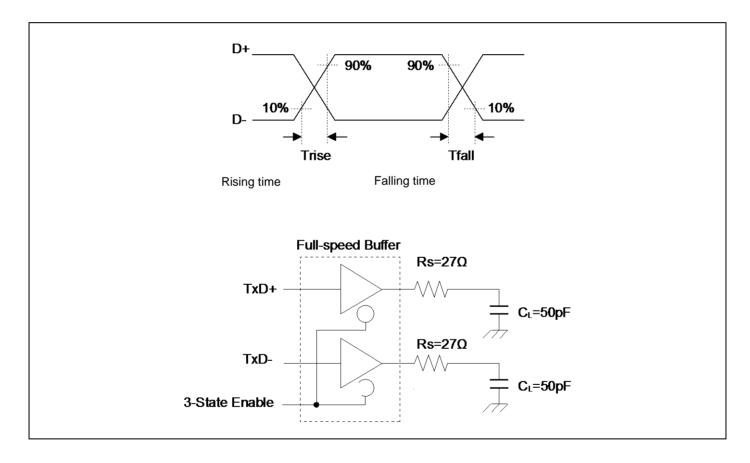

- \*4: The cross voltage of the external differential output signal (D + /D ) of USB I/O buffer is within 1.3 V to 2.0 V.

\*5: They indicate rising time (Trise) and falling time (Tfall) of the full-speed differential data signal. They are defined by the time between 10% and 90% of the output signal voltage. For full-speed buffer, Tr/Tf ratio is regulated as within ± 10% to minimize RFI emission.

# 12.9 Flash Memory Write/Erase Characteristics

#### 12.9.1 Write / Erase time

$(V_{CC} = 2.7V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } + 105^{\circ}C)$

| Dore                          | ımeter       | Va  | lue | Unit | Remarks                                     |  |  |

|-------------------------------|--------------|-----|-----|------|---------------------------------------------|--|--|

| Para                          | imeter       | Тур | Max | Unit | Remarks                                     |  |  |

| Sector erase time             | Large Sector | 1.1 | 2.7 | s    | Includes write time prior to internal erase |  |  |

| Sector erase time             | Small Sector | 0.3 | 0.9 | 5    | includes write time prior to internal erase |  |  |

| Half word (16-bit) write time |              | 16  | 310 | μs   | Not including system-level overhead time    |  |  |

| Chip erase time               |              | 6.8 | 18  | s    | Includes write time prior to internal erase |  |  |

<sup>\*:</sup> The typical value is immediately after shipment, the maximam value is guarantee value under 10,000 cycle of erase/write.

12.9.2 Write cycles and data hold time

| Erase/write cycles (cycle) | Data hold time (year) | Remarks |

|----------------------------|-----------------------|---------|

| 1,000                      | 20*                   |         |

| 10,000                     | 10*                   |         |

<sup>\*:</sup> At average + 85°C

# Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

cypress.com/wireless

#### **Products**

Wireless/RF

ARM® Cortex® Microcontrollers cvpress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Lighting & Power Control cypress.com/powerpsoc Memory cypress.com/memory **PSoC** cypress.com/psoc **Touch Sensing** cypress.com/touch **USB Controllers** cypress.com/usb

#### PSoC® Solutions

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

## **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

# Technical Support

cypress.com/go/support

ARM and Cortex are the registered trademarks of ARM Limited in the EU and other countries.

© Cypress Semiconductor Corporation 2012-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you under its copyright rights in the Software, a personal, non-exclusive, nontransferable license (without the right to sublicense) (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware product units. Cypress also grants you a personal, non-exclusive, nontransferable, license (without the right to sublicense) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely to the minimum extent that is necessary for you to exercise your rights under the copyright license granted in the previous sentence. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and Company shall and hereby does release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. Company shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-05649 Rev.\*A March 7, 2016 Page 108 of 108