Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, LVD, POR, PWM, WDT            |

| Number of I/O              | 52                                                                             |

| Program Memory Size        | 144KB (48K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 4K x 8                                                                         |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6012a-20i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name              | Pin<br>Type | Buffer<br>Type                      | Description                                                                                                                                                                    |

|-----------------------|-------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1                  | I           | ST/CMOS                             | Oscillator crystal input. ST buffer when configured in RC mode;<br>CMOS otherwise.                                                                                             |

| OSC2                  | I/O         | _                                   | Oscillator crystal output. Connects to crystal or resonator in<br>Crystal Oscillator mode. Optionally functions as CLKO in RC<br>and EC modes.                                 |

| PGD                   | I/O         | ST                                  | In-Circuit Serial Programming™ data input/output pin.                                                                                                                          |

| PGC                   | I           | ST                                  | In-Circuit Serial Programming clock input pin.                                                                                                                                 |

| RA6-RA7               | I/O         | ST                                  | PORTA is a bidirectional I/O port.                                                                                                                                             |

| RA9-RA10<br>RA12-RA15 | I/O<br>I/O  | ST<br>ST                            |                                                                                                                                                                                |

| RB0-RB15              | I/O         | ST                                  | POPTR is a hidiractional I/O part                                                                                                                                              |

|                       |             |                                     | PORTB is a bidirectional I/O port.                                                                                                                                             |

| RC1-RC4<br>RC13-RC15  | I/O<br>I/O  | ST<br>ST                            | PORTC is a bidirectional I/O port.                                                                                                                                             |

| RD0-RD15              | I/O         | ST                                  | PORTD is a bidirectional I/O port.                                                                                                                                             |

| RF0-RF8               | I/O         | ST                                  | PORTF is a bidirectional I/O port.                                                                                                                                             |

| RG0-RG3               | 1/O         | ST                                  | PORTG is a bidirectional I/O port.                                                                                                                                             |

| RG6-RG9               | 1/O         | ST                                  |                                                                                                                                                                                |

| RG12-RG15             | I/O         | ST                                  |                                                                                                                                                                                |

| SCK1                  | I/O         | ST                                  | Synchronous serial clock input/output for SPI1.                                                                                                                                |

| SDI1                  | I           | ST                                  | SPI1 Data In.                                                                                                                                                                  |

| SDO1                  | 0           | ST                                  | SPI1 Data Out.                                                                                                                                                                 |

| SS1<br>SCK2           | I<br>I/O    | ST                                  | SPI1 Slave Synchronization.<br>Synchronous serial clock input/output for SPI2.                                                                                                 |

| SDI2                  | ., C        | ST                                  | SPI2 Data In.                                                                                                                                                                  |

| SDO2                  | 0           | —                                   | SPI2 Data Out.                                                                                                                                                                 |

| SS2                   | I           | ST                                  | SPI2 Slave Synchronization.                                                                                                                                                    |

| SCL                   | I/O         | ST                                  | Synchronous serial clock input/output for $I^2C^{TM}$ .                                                                                                                        |

| SDA                   | I/O         | ST                                  | Synchronous serial data input/output for I <sup>2</sup> C.                                                                                                                     |

| SOSCO<br>SOSCI        | 0<br>1      | ST/CMOS                             | <ul> <li>32 kHz low-power oscillator crystal output.</li> <li>32 kHz low-power oscillator crystal input. ST buffer when config<br/>ured in RC mode; CMOS otherwise.</li> </ul> |

| T1CK                  | I           | ST                                  | Timer1 external clock input.                                                                                                                                                   |

| T2CK                  |             | ST                                  | Timer2 external clock input.                                                                                                                                                   |

| T3CK<br>T4CK          |             | ST<br>ST                            | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                   |

| T5CK                  |             | ST                                  | Timer5 external clock input.                                                                                                                                                   |

| U1RX                  | 1           | ST                                  | UART1 Receive.                                                                                                                                                                 |

| U1TX                  | 0           | —                                   | UART1 Transmit.                                                                                                                                                                |

| U1ARX                 |             | ST                                  | UART1 Alternate Receive.                                                                                                                                                       |

| U1ATX                 | 0           |                                     | UART1 Alternate Transmit.                                                                                                                                                      |

| U2RX<br>U2TX          | 0           | ST                                  | UART2 Receive.<br>UART2 Transmit.                                                                                                                                              |

| VDD                   | P           |                                     | Positive supply for logic and I/O pins.                                                                                                                                        |

| Vss                   | P           |                                     | Ground reference for logic and I/O pins.                                                                                                                                       |

| vss<br>Vref+          |             | Analog                              | Analog Voltage Reference (High) input.                                                                                                                                         |

|                       |             | Analog                              |                                                                                                                                                                                |

| VREF-                 |             | Analog                              | Analog Voltage Reference (Low) input.                                                                                                                                          |

|                       |             | ible input or ou<br>r input with CM |                                                                                                                                                                                |

|                       | nput        |                                     | P = Power                                                                                                                                                                      |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

NOTES:

| <b>TABLE 3-3:</b> | CORE REGISTER MAP (CONTINUED) |

|-------------------|-------------------------------|

|-------------------|-------------------------------|

| IADLE 3  | J. U              |        |          |        |        |        | 7      |        |         |        |         |        |        |                |       |       |       |                     |

|----------|-------------------|--------|----------|--------|--------|--------|--------|--------|---------|--------|---------|--------|--------|----------------|-------|-------|-------|---------------------|

| SFR Name | Address<br>(Home) | Bit 15 | Bit 14   | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8   | Bit 7  | Bit 6   | Bit 5  | Bit 4  | Bit 3          | Bit 2 | Bit 1 | Bit 0 | Reset State         |

| SR       | 0042              | OA     | OB       | SA     | SB     | OAB    | SAB    | DA     | DC      | IPL2   | IPL1    | IPL0   | RA     | Ν              | OV    | Z     | С     | 0000 0000 0000 0000 |

| CORCON   | 0044              | _      |          | _      | US     | EDT    | DL2    | DL1    | DL0     | SATA   | SATB    | SATDW  | ACCSAT | IPL3           | PSV   | RND   | IF    | 0000 0000 0010 0000 |

| MODCON   | 0046              | XMODEN | YMODEN   | _      | —      |        | BWN    | 1<3:0> |         |        | YW      | M<3:0> |        |                | XWM<  | :3:0> |       | 0000 0000 0000 0000 |

| XMODSRT  | 0048              |        |          |        |        |        |        | X      | S<15:1> |        |         |        |        |                |       |       | 0     | uuuu uuuu uuuu uuu0 |

| XMODEND  | 004A              |        |          |        |        |        |        | XI     | =<15:1> |        |         |        |        |                |       |       | 1     | uuuu uuuu uuul      |

| YMODSRT  | 004C              |        |          |        |        |        |        | Y      | S<15:1> |        |         |        |        |                |       |       | 0     | uuuu uuuu uuuu uuu0 |

| YMODEND  | 004E              |        |          |        |        |        |        | YI     | =<15:1> |        |         |        |        |                |       |       | 1     | uuuu uuuu uuu1      |

| XBREV    | 0050              | BREN   | XB<14:0> |        |        |        |        |        |         |        |         |        |        | uuuu uuuu uuuu |       |       |       |                     |

| DISICNT  | 0052              | _      | _        |        |        |        |        |        |         | DISICN | T<13:0> |        |        |                |       |       |       | 0000 0000 0000 0000 |

**Legend:** u = uninitialized bit

Note: Refer to dsPIC30F Family Reference Manua (DS70046) for descriptions of register bit fields.

#### 6.6.3 LOADING WRITE LATCHES

Example 6-2 shows a sequence of instructions that can be used to load the 96 bytes of write latches. 32 TBLWTL and 32 TBLWTH instructions are needed to load the write latches selected by the table pointer.

#### EXAMPLE 6-2: LOADING WRITE LATCHES

```

; Set up a pointer to the first program memory location to be written

; program memory selected, and writes enabled

#0x0000,W0

MOV

MOV

W0 TBLPAG

; Initialize PM Page Boundary SFR

#0x6000,W0

MOV

; An example program memory address

; Perform the TBLWT instructions to write the latches

; 0th_program_word

#LOW WORD 0,W2

MOV

;

MOV

#HIGH_BYTE_0,W3

;

TBLWTL W2 [W0]

; Write PM low word into program latch

TBLWTH W3 [W0++]

; Write PM high byte into program latch

; 1st program word

MOV

#LOW_WORD_1,W2

;

#HIGH_BYTE_1,W3

MOV

;

TBLWTL W2 [W0]

; Write PM low word into program latch

TBLWTH W3 [W0++]

; Write PM high byte into program latch

2nd program word

;

MOV #LOW_WORD_2,W2

;

#HIGH_BYTE_2,W3

MOV

;

TBLWTL W2<sub>,</sub> [W0]

; Write PM low word into program latch

TBLWTH W3 [W0++]

; Write PM high byte into program latch

; 31st program word

MOV

#LOW WORD 31,W2

;

#HIGH_BYTE_31,W3

MOV

;

TBLWTL W2 [W0]

; Write PM low word into program latch

; Write PM high byte into program latch

TBLWTH W3 [W0++]

```

Note: In Example 6-2, the contents of the upper byte of W3 has no effect.

# 6.6.4 INITIATING THE PROGRAMMING SEQUENCE

For protection, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

#### EXAMPLE 6-3: INITIATING A PROGRAMMING SEQUENCE

| DISI       | #5                    | ; Block all interrupts with priority <7 for<br>; next 5 instructions |

|------------|-----------------------|----------------------------------------------------------------------|

| MOV<br>MOV | #0x55,W0<br>W0 NVMKEY | ;<br>; Write the 0x55 key                                            |

| MOV        | ,<br>#0xAA,W1         | ;                                                                    |

| MOV        | W1,NVMKEY             | ; Write the OxAA key                                                 |

| BSET       | NVMCON, #WR           | ; Start the erase sequence                                           |

| NOP        |                       | ; Insert two NOPs after the erase                                    |

| NOP        |                       | ; command is asserted                                                |

|            |                       |                                                                      |

NOTES:

# 10.1 Timer Gate Operation

The 32-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal TCY to increment the respective timer when the gate input signal (T2CK pin) is asserted high. Control bit TGATE (T2CON<6>) must be set to enable this mode. When in this mode, Timer2 is the originating clock source. The TGATE setting is ignored for Timer3. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

The falling edge of the external signal terminates the count operation but does not reset the timer. The user must reset the timer in order to start counting from zero.

# 10.2 ADC Event Trigger

When a match occurs between the 32-bit timer (TMR3/ TMR2) and the 32-bit combined period register (PR3/ PR2), or between the 16-bit timer TMR3 and the 16-bit period register PR3, a special ADC trigger event signal is generated by Timer3.

# 10.3 Timer Prescaler

The input clock (FOSC/4 or external clock) to the timer has a prescale option of 1:1, 1:8, 1:64, and 1:256, selected by control bits TCKPS<1:0> (T2CON<5:4> and T3CON<5:4>). For the 32-bit timer operation, the originating clock source is Timer2. The prescaler operation for Timer3 is not applicable in this mode. The prescaler counter is cleared when any of the following occurs:

- a write to the TMR2/TMR3 register

- a write to the T2CON/T3CON register

- device Reset, such as POR and BOR

However, if the timer is disabled (TON = 0), then the Timer 2 prescaler cannot be reset since the prescaler clock is halted.

TMR2/TMR3 is not cleared when T2CON/T3CON is written.

# 10.4 Timer Operation During Sleep Mode

During CPU Sleep mode, the timer will not operate because the internal clocks are disabled.

# 10.5 Timer Interrupt

The 32-bit timer module can generate an interrupt on period match or on the falling edge of the external gate signal. When the 32-bit timer count matches the respective 32-bit period register, or the falling edge of the external "gate" signal is detected, the T3IF bit (IFS0<7>) is asserted and an interrupt will be generated if enabled. In this mode, the T3IF interrupt flag is used as the source of the interrupt. The T3IF bit must be cleared in software.

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T3IE (IEC0<7>).

# TABLE 13-1: OUTPUT COMPARE REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7     | Bit 6     | Bit 5    | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0  | Reset State         |

|----------|-------|--------|--------|--------|--------|--------|--------|-------|-----------|-----------|-----------|----------|-------|--------|-------|-------|--------|---------------------|

| OC1RS    | 0180  |        |        |        |        |        |        | Ou    | Itput Com | pare 1 Se | condary I | Register |       |        |       |       |        | 0000 0000 0000 0000 |

| OC1R     | 0182  |        |        |        |        |        |        |       | Output C  | ompare 1  | Main Reg  | jister   |       |        |       |       |        | 0000 0000 0000 0000 |

| OC1CON   | 0184  | —      | —      | OCSIDI |        | —      | —      | —     | _         | _         |           |          | - OCF | LT OCT | SEL   | OCI   | M<2:0> | 0000 0000 0000 0000 |

| OC2RS    | 0186  |        |        |        |        |        |        | Ou    | tput Com  | pare 2 Se | condary F | Register |       |        |       |       |        | 0000 0000 0000 0000 |

| OC2R     | 0188  |        |        |        |        |        |        |       | Output C  | ompare 2  | Main Reg  | jister   |       |        |       |       |        | 0000 0000 0000 0000 |

| OC2CON   | 018A  | —      | —      | OCSIDI |        | —      | —      | —     | _         | _         |           |          | - OCF | LT OC  | TSE   | OCI   | M<2:0> | 0000 0000 0000 0000 |

| OC3RS    | 018C  |        |        |        |        |        |        | 00    | tiput Com | pare 3 Se | condary i | kegister |       |        |       |       |        | 0000 0000 0000 0000 |

| OC3R     | 018E  |        |        |        |        |        |        |       | Output C  | ompare 3  | Main Reg  | jister   |       |        |       |       |        | 0000 0000 0000 0000 |

| OC3CON   | 0190  | _      | _      | OCSIDI | _      |        |        |       |           |           |           |          |       |        |       |       |        |                     |

DS70143B-page 90

Note: Refer to dsPIC30F Family Reference Manual (DS70046) for descriptions of register bit fields.

# 14.3 Slave Select Synchronization

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be configured in SPI Slave mode with  $\overline{SSx}$  pin control enabled (SSEN = 1). When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven. When  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven. Also, the SPI module is resynchronized, and all counters/control circuitry are reset. Therefore, when the  $\overline{SSx}$  pin is asserted low again, transmission/reception will begin at the MSb even if  $\overline{SSx}$  had been de-asserted in the middle of a transmit/receive.

## 14.4 SPI Operation During CPU Sleep Mode

During Sleep mode, the SPI module is shutdown. If the CPU enters Sleep mode while an SPI transaction is in progress, then the transmission and reception is aborted.

The transmitter and receiver will stop in Sleep mode. However, register contents are not affected by entering or exiting Sleep mode.

# 14.5 SPI Operation During CPU Idle Mode

When the device enters Idle mode, all clock sources remain functional. The SPISIDL bit (SPIxSTAT<13>) selects if the SPI module will stop or continue on Idle. If SPISIDL = 0, the module will continue to operate when the CPU enters Idle mode. If SPISIDL = 1, the module will stop when the CPU enters Idle mode.

#### 16.3.4 TRANSMIT INTERRUPT

The transmit interrupt flag (U1TXIF or U2TXIF) is located in the corresponding interrupt flag register.

The transmitter generates an edge to set the UxTXIF bit. The condition for generating the interrupt depends on the UTXISEL control bit:

- a) If UTXISEL = 0, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR). This implies that the transmit buffer has at least one empty word.

- b) If UTXISEL = 1, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR) and the transmit buffer is empty.

Switching between the two Interrupt modes during operation is possible and sometimes offers more flexibility.

#### 16.3.5 TRANSMIT BREAK

Setting the UTXBRK bit (UxSTA<11>) will cause the UxTX line to be driven to logic '0'. The UTXBRK bit overrides all transmission activity. Therefore, the user should generally wait for the transmitter to be Idle before setting UTXBRK.

To send a break character, the UTXBRK bit must be set by software and must remain set for a minimum of 13 baud clock cycles. The UTXBRK bit is then cleared by software to generate Stop bits. The user must wait for a duration of at least one or two baud clock cycles in order to ensure a valid Stop bit(s) before reloading the UxTXB, or starting other transmitter activity. Transmission of a break character does not generate a transmit interrupt.

#### 16.4 Receiving Data

#### 16.4.1 RECEIVING IN 8-BIT OR 9-BIT DATA MODE

The following steps must be performed while receiving 8-bit or 9-bit data:

- 1. Set up the UART (see Section 16.3.1 "Transmitting in 8-bit data mode").

- 2. Enable the UART (see Section 16.3.1 "Transmitting in 8-bit data mode").

- A receive interrupt will be generated when one or more data words have been received, depending on the receive interrupt settings specified by the URXISEL bits (UxSTA<7:6>).

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read the received data from UxRXREG. The act of reading UxRXREG will move the next word to the top of the receive FIFO, and the PERR and

FERR values will be updated.

#### 16.4.2 RECEIVE BUFFER (UXRXB)

The receive buffer is 4 words deep. Including the Receive Shift register (UxRSR), the user effectively has a 5-word deep FIFO buffer.

URXDA (UxSTA<0>) = 1 indicates that the receive buffer has data available. URXDA = 0 implies that the buffer is empty. If a user attempts to read an empty buffer, the old values in the buffer will be read and no data shift will occur within the FIFO.

The FIFO is reset during any device Reset. It is not affected when the device enters or wakes up from a Power Saving mode.

#### 16.4.3 RECEIVE INTERRUPT

The receive interrupt flag (U1RXIF or U2RXIF) can be read from the corresponding interrupt flag register. The interrupt flag is set by an edge generated by the receiver. The condition for setting the receive interrupt flag depends on the settings specified by the URXISEL<1:0> (UxSTA<7:6>) control bits.

- a) If URXISEL<1:0> = 00 or 01, an interrupt is generated every time a data word is transferred from the Receive Shift register (UxRSR) to the receive buffer. There may be one or more characters in the receive buffer.

- b) If URXISEL<1:0> = 10, an interrupt is generated when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer, which as a result of the transfer, contains 3 characters.

- c) If URXISEL<1:0> = 11, an interrupt is set when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer, which as a result of the transfer, contains 4 characters (i.e., becomes full).

Switching between the Interrupt modes during operation is possible, though generally not advisable during normal operation.

# 16.5 Reception Error Handling

#### 16.5.1 RECEIVE BUFFER OVERRUN ERROR (OERR BIT)

The OERR bit (UxSTA<1>) is set if all of the following conditions occur:

- a) The receive buffer is full.

- b) The Receive Shift register is full, but unable to transfer the character to the receive buffer.

- c) The Stop bit of the character in the UxRSR is detected, indicating that the UxRSR needs to transfer the character to the buffer.

• Receive Error Interrupts:

A receive error interrupt will be indicated by the ERRIF bit. This bit shows that an error condition occurred. The source of the error can be determined by checking the bits in the CAN Interrupt status register, CiINTF.

- Invalid Message Received:

If any type of error occurred during reception of the last message, an error will be indicated by the IVRIF bit.

- Receiver Overrun:

The RXnOVR bit indicates that an overrun condition occurred.

- Receiver Warning:

The RXWAR bit indicates that the receive error counter (RERRCNT<7:0>) has reached the warning limit of 96.

- Receiver Error Passive:

The RXEP bit indicates that the receive error counter has exceeded the error passive limit of 127 and the module has gone into error passive state.

# 17.5 Message Transmission

#### 17.5.1 TRANSMIT BUFFERS

The CAN module has three transmit buffers. Each of the three buffers occupies 14 bytes of data. Eight of the bytes are the maximum 8 bytes of the transmitted message. Five bytes hold the standard and extended identifiers and other message arbitration information.

#### 17.5.2 TRANSMIT MESSAGE PRIORITY

Transmit priority is a prioritization within each node of the pending transmittable messages. There are 4 levels of transmit priority. If TXPRI<1:0> (CiTXnCON<1:0>, where n = 0, 1 or 2 represents a particular transmit buffer) for a particular message buffer is set to '11', that buffer has the highest priority. If TXPRI<1:0> for a particular message buffer is set to '10' or '01', that buffer has an intermediate priority. If TXPRI<1:0> for a particular message buffer is '00', that buffer has the lowest priority.

#### 17.5.3 TRANSMISSION SEQUENCE

To initiate transmission of the message, the TXREQ bit (CiTXnCON<3>) must be set. The CAN bus module resolves any timing conflicts between setting of the TXREQ bit and the Start of Frame (SOF), ensuring that if the priority was changed, it is resolved correctly before the SOF occurs. When TXREQ is set, the TXABT (CiTXnCON<6>), TXLARB (CiTXnCON<5>) and TXERR (CiTXnCON<4>) flag bits are automatically cleared.

Setting TXREQ bit simply flags a message buffer as enqueued for transmission. When the module detects an available bus, it begins transmitting the message which has been determined to have the highest priority.

If the transmission completes successfully on the first attempt, the TXREQ bit is cleared automatically, and an interrupt is generated if TXIE was set.

If the message transmission fails, one of the error condition flags will be set, and the TXREQ bit will remain set indicating that the message is still pending for transmission. If the message encountered an error condition during the transmission attempt, the TXERR bit will be set, and the error condition may cause an interrupt. If the message loses arbitration during the transmission attempt, the TXLARB bit is set. No interrupt is generated to signal the loss of arbitration.

#### 17.5.4 ABORTING MESSAGE TRANSMISSION

The system can also abort a message by clearing the TXREQ bit associated with each message buffer. Setting the ABAT bit (CiCTRL<12>) will request an abort of all pending messages. If the message has not yet started transmission, or if the message started but is interrupted by loss of arbitration or an error, the abort will be processed. The abort is indicated when the module sets the TXABT bit and the TXnIF flag is not automatically set.

# 17.5.5 TRANSMISSION ERRORS

The CAN module will detect the following transmission errors:

- Acknowledge Error

- Form Error

- Bit Error

These transmission errors will not necessarily generate an interrupt but are indicated by the transmission error counter. However, each of these errors will cause the transmission error counter to be incremented by one. Once the value of the error counter exceeds the value of 96, the ERRIF (CiINTF<5>) and the TXWAR bit (CiINTF<10>) are set. Once the value of the error counter exceeds the value of 96, an interrupt is generated and the TXWAR bit in the Error Flag register is set.

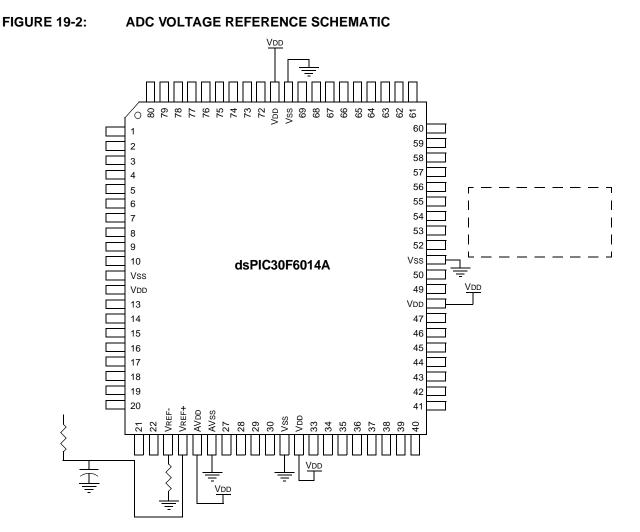

The following figure depicts the recommended circuit for the conversion rates above 100 ksps. The dsPIC30F6014A is shown as an example.

The configuration procedures below give the required setup values for the conversion speeds above 100 ksps.

#### 19.7.1 200 KSPS CONFIGURATION GUIDELINE

The following configuration items are required to achieve a 200 ksps conversion rate.

- Comply with conditions provided in Table 19-2.

- Connect external VREF+ and VREF- pins following the recommended circuit shown in Figure 19-2.

- Set SSRC<2.0> = 111 in the ADCON1 register to enable the auto convert option.

- Enable automatic sampling by setting the ASAM control bit in the ADCON1 register.

- Write the SMPI<3.0> control bits in the ADCON2 register for the desired number of conversions between interrupts.

• Configure the ADC clock period to be:

by writing to the ADCS<5:0> control bits in the ADCON3 register.

• Configure the sampling time to be 1 TAD by writing: SAMC<4:0> = 00001.

The following figure shows the timing diagram of the ADC running at 200 ksps. The TAD selection in conjunction with the guidelines described above allows a conversion speed of 200 ksps. See Example 19-1 for code example.

#### 20.2.6 LOW-POWER RC OSCILLATOR (LPRC)

The LPRC oscillator is a component of the Watchdog Timer (WDT) and oscillates at a nominal frequency of 512 kHz. The LPRC oscillator is the clock source for the Power-up Timer (PWRT) circuit, WDT and clock monitor circuits. It may also be used to provide a low frequency clock source option for applications where power consumption is critical, and timing accuracy is not required.

The LPRC oscillator is always enabled at a Power-on Reset, because it is the clock source for the PWRT. After the PWRT expires, the LPRC oscillator will remain ON if one of the following is TRUE:

- The Fail-Safe Clock Monitor is enabled

- The WDT is enabled

- The LPRC oscillator is selected as the system clock via the COSC<2:0> control bits in the OSCCON register

If one of the above conditions is not true, the LPRC will shut-off after the PWRT expires.

- **Note 1:** OSC2 pin function is determined by the Primary Oscillator mode selection (FPR<4:0>).

- Note that OSC1 pin cannot be used as an I/O pin, even if the secondary oscillator or an internal clock source is selected at all times.

# 20.2.7 FAIL-SAFE CLOCK MONITOR

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by appropriately programming the FCKSM Configuration bits (Clock Switch and Monitor Selection bits) in the Fosc device Configuration register. If the FSCM function is enabled, the LPRC internal oscillator will run at all times (except during Sleep mode) and will not be subject to control by the SWDTEN bit.

In the event of an oscillator failure, the FSCM will generate a clock failure trap event and will switch the system clock over to the FRC oscillator. The user will then have the option to either attempt to restart the oscillator or execute a controlled shutdown. The user may decide to treat the trap as a warm Reset by simply loading the Reset address into the oscillator fail trap vector. In this event, the CF (Clock Fail) status bit (OSCCON<3>) is also set whenever a clock failure is recognized.

In the event of a clock failure, the WDT is unaffected and continues to run on the LPRC clock.

If the oscillator has a very slow start-up time coming out of POR, BOR or Sleep, it is possible that the PWRT timer will expire before the oscillator has started. In such cases, the FSCM will be activated and the FSCM will initiate a clock failure trap, and the COSC<2:0> bits are loaded with FRC oscillator selection. This will effectively shut-off the original oscillator that was trying to start.

The user may detect this situation and restart the oscillator in the clock fail trap ISR.

Upon a clock failure detection, the FSCM module will initiate a clock switch to the FRC oscillator as follows:

- 1. The COSC bits (OSCCON<14:12>) are loaded with the FRC oscillator selection value.

- 2. CF bit is set (OSCCON<3>).

- 3. OSWEN control bit (OSCCON<0>) is cleared.

For the purpose of clock switching, the clock sources are sectioned into four groups:

- 1. Primary

- 2. Secondary

- 3. Internal FRC

- 4. Internal LPRC

The user can switch between these functional groups, but cannot switch between options within a group. If the primary group is selected, then the choice within the group is always determined by the FPR<4:0> Configuration bits.

The OSCCON register holds the control and status bits related to clock switching.

- COSC<2:0>: Read-only status bits always reflect the current oscillator group in effect.

- NOSC<2:0>: Control bits which are written to indicate the new oscillator group of choice.

- On POR and BOR, COSC<2:0> and NOSC<2:0> are both loaded with the Configuration bit values FOS<2:0>.

- LOCK: The LOCK status bit indicates a PLL lock.

- CF: Read-only status bit indicating if a clock fail detect has occurred.

- OSWEN: Control bit changes from a '0' to a '1' when a clock transition sequence is initiated. Clearing the OSWEN control bit will abort a clock transition in progress (used for hang-up situations).

If Configuration bits FCKSM<1:0> = 1x, then the clock switching and Fail-Safe Clock Monitor functions are disabled. This is the default Configuration bit setting.

If clock switching is disabled, then the FOS<2:0> and FPR<4:0> bits directly control the oscillator selection and the COSC<2:0> bits do not control the clock selection. However, these bits will reflect the clock source selection.

Note: The application should not attempt to switch to a clock of frequency lower than 100 kHz when the Fail-Safe Clock Monitor is enabled. If clock switching is performed, the device may generate an oscillator fail trap and switch to the fast RC oscillator.

| REGISTER   | R 20-2: 08 | SCTUN: FRO | C OSCILLA | TOR TUN | ING R | EGIS | TER |       |                |    |       |

|------------|------------|------------|-----------|---------|-------|------|-----|-------|----------------|----|-------|

| Upper Byte | e:         |            |           |         |       |      |     |       |                |    |       |

| U-0        | U-0        | U-0        | U-0       | U-0     | U     | -0   | U-0 | ι     | J-0            |    |       |

|            | —          |            | —         | _       | _     | _    |     | -     |                |    |       |

| bit 15     |            |            |           |         |       |      |     |       | bit 8          |    |       |

|            |            |            |           |         |       |      |     |       |                |    |       |

|            | Lower      | Byte:      |           |         |       |      |     |       |                |    |       |

|            | U-0        | U-0        | U-0       | U       | -0    | R/V  | V-0 | R/W-0 | R/W            | -0 | R/W-0 |

|            |            | _          | —         | -       | _     |      |     | TUN   | <b> </b> <3:0> |    |       |

|            | bit 7      |            |           |         |       |      |     |       |                |    | bit 0 |

#### bit 15-4 Unimplemented: Read as '0'

bit 3-0 **TUN<3:0>:** Lower two bits of TUN field. The four bit field specified by TUN<3:0> specifies the user tuning capability for the internal fast RC oscillator (nominal 7.37 MHz).

0111 = Maximum Frequency 0110 = 0101 = 0100 = 0011 = 0010 = 0001 = 0000 = Center Frequency, Oscillator is running at calibrated frequency 1111 = 1110 = 1101 = 1100 = 1011 = 1010 = 1001 = 1000 = Minimum Frequency

| Legend:                |                        |                      |                    |

|------------------------|------------------------|----------------------|--------------------|

| R = Readable bit       | W = Writable bit       | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR      | '1' = Bit is set       | '0' = Bit is cleared | x = Bit is unknown |

| y = Value set from Cor | figuration bits on POR |                      |                    |

© 2005 Microchip Technology Inc.

# 22.0 DEVELOPMENT SUPPORT

The PICmicro microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

# 22.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PICmicro MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- · Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

#### TABLE 23-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD) (CONTINUED)

| DC CHARACT       | ERISTICS                  |     | (unless oth | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |         |           |  |  |  |  |  |

|------------------|---------------------------|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|--|--|--|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup>    | Max | Units       |                                                                                                                                                                                                      | Co      | onditions |  |  |  |  |  |

| Operating Cur    | rent (IDD) <sup>(2)</sup> |     |             |                                                                                                                                                                                                      |         |           |  |  |  |  |  |

| DC29             | —                         | _   | mA          | -40°C                                                                                                                                                                                                |         |           |  |  |  |  |  |

| DC29a            | 146                       | _   | mA          | 25°C                                                                                                                                                                                                 | 5V      |           |  |  |  |  |  |

| DC29b            | DC29b — —                 |     |             | 85°C                                                                                                                                                                                                 | 30 MIPS |           |  |  |  |  |  |

| DC29c            | —                         | _   | mA          | 125°C                                                                                                                                                                                                | 1       |           |  |  |  |  |  |

**Note 1:** Data in "Typical" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption. The test conditions for all IDD measurements are as follows: OSC1 driven with external square wave from rail to rail. All I/O pins are configured as inputs and pulled to VDD. MCLR = VDD, WDT, FSCM and BOR are disabled. CPU, SRAM, program memory and data memory are operational. No peripheral modules are operating.

### TABLE 23-24: TYPE B TIMER (TIMER2 AND TIMER4) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA       | RACTERIS                                                             | TICS              |                      | (unles | ard Operating<br>s otherwise st<br>ting temperatur | t <b>ated)</b><br>re -40° | °C ≤ Ta ≤ · | +85°C fo | r Industrial<br>or Extended   |

|--------------|----------------------------------------------------------------------|-------------------|----------------------|--------|----------------------------------------------------|---------------------------|-------------|----------|-------------------------------|

| Param<br>No. | Symbol                                                               | Characte          | eristic              |        | Min                                                | Тур                       | Max         | Units    | Conditions                    |

| TB10         | TtxH                                                                 | TxCK High Time    | Synchro<br>no preso  |        | 0.5 Tcy + 20                                       |                           | _           | ns       | Must also meet parameter TB15 |

|              |                                                                      |                   | Synchro<br>with pres |        | 10                                                 |                           | _           | ns       |                               |

| TB11         | TtxL                                                                 | TxCK Low Time     | Synchro<br>no preso  |        | 0.5 TCY + 20                                       |                           | _           | ns       | Must also meet parameter TB15 |

|              |                                                                      |                   | Synchro<br>with pre  |        | 10                                                 | —                         | —           | ns       |                               |

| TB15         | TtxP                                                                 | TxCK Input Period | Synchro<br>no preso  |        | Tcy + 10                                           | _                         | —           | ns       | N = prescale<br>value         |

|              |                                                                      |                   | Synchro<br>with pres |        | Greater of:<br>20 ns or<br>(TCY + 40)/N            |                           |             |          | (1, 8, 64, 256)               |

| TB20         | TB20 TCKEXT- Delay from External TxCK<br>MRL Edge to Timer Increment |                   |                      |        | 0.5 TCY                                            |                           | 1.5 TCY     |          |                               |

**Note:** Timer2 and Timer4 are Type B.

#### TABLE 23-25: TYPE C TIMER (TIMER3 AND TIMER5) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA                                                               | RACTERIST | rics              | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |                                         |     |            |       |                               |  |

|----------------------------------------------------------------------|-----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------|-----|------------|-------|-------------------------------|--|

| Param<br>No. Symbol Characteristic                                   |           |                   |                                                                                                                                                                                                      |      | Min                                     | Тур | Max        | Units | Conditions                    |  |

| TC10                                                                 | TtxH      | TxCK High Time    | Synchro                                                                                                                                                                                              | nous | 0.5 TCY + 20                            |     |            | ns    | Must also meet parameter TC15 |  |

| TC11                                                                 | TtxL      | TxCK Low Time     | Synchro                                                                                                                                                                                              | nous | 0.5 TCY + 20                            |     | _          | ns    | Must also meet parameter TC15 |  |

| TC15                                                                 | TtxP      | TxCK Input Period | Synchro<br>no presc                                                                                                                                                                                  |      | Tcy + 10                                |     | _          | ns    | N = prescale<br>value         |  |

|                                                                      |           |                   | Synchro<br>with pre                                                                                                                                                                                  |      | Greater of:<br>20 ns or<br>(TcY + 40)/N |     |            |       | (1, 8, 64, 256)               |  |

| TC20 TCKEXTMRL Delay from External TxCK C<br>Edge to Timer Increment |           |                   |                                                                                                                                                                                                      | lock | 0.5 TCY                                 | _   | 1.5<br>Тсү |       |                               |  |

**Note:** Timer3 and Timer5 are Type C.

© 2005 Microchip Technology Inc.

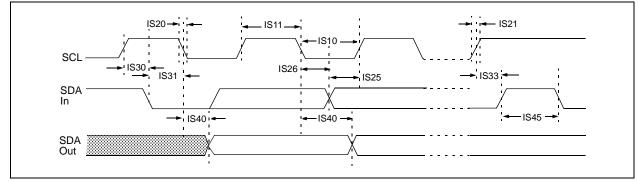

# FIGURE 23-12: DCI MODULE (MULTICHANNEL, I<sup>2</sup>S MODES) TIMING CHARACTERISTICS

| AC CHA       |        | STICS                                                                          | Standard O<br>(unless oth<br>Operating te | erwise st          | <b>ated)</b><br>e -40°C : | ≤ Ta ≤ +85 | 5.5V<br>5°C for Industrial<br>25°C for Extended |

|--------------|--------|--------------------------------------------------------------------------------|-------------------------------------------|--------------------|---------------------------|------------|-------------------------------------------------|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>                                                  | Min                                       | Тур <sup>(2)</sup> | Max                       | Units      | Conditions                                      |

| CS10         | TCSCKL | CSCK Input Low Time<br>(CSCK pin is an input)                                  | Tcy / 2 +<br>20                           | —                  | —                         | ns         | _                                               |

|              |        | CSCK Output Low Time <sup>(3)</sup><br>(CSCK pin is an output)                 | 30                                        | —                  | —                         | ns         | —                                               |

| CS11         | Тсѕскн | CSCK Input High Time<br>(CSCK pin is an input)                                 | Tcy / 2 +<br>20                           | —                  | —                         | ns         | —                                               |

|              |        | CSCK Output High Time <sup>(3)</sup><br>(CSCK pin is an output)                | 30                                        | —                  | —                         | ns         | —                                               |

| CS20         | TCSCKF | CSCK Output Fall Time <sup>(4)</sup><br>(CSCK pin is an output)                | —                                         | 10                 | 25                        | ns         | —                                               |

| CS21         | TCSCKR | CSCK Output Rise Time <sup>(4)</sup><br>(CSCK pin is an output)                | —                                         | 10                 | 25                        | ns         | —                                               |

| CS30         | TCSDOF | CSDO Data Output Fall Time <sup>(4)</sup>                                      | —                                         | 10                 | 25                        | ns         | —                                               |

| CS31         | TCSDOR | CSDO Data Output Rise Time <sup>(4)</sup>                                      | —                                         | 10                 | 25                        | ns         | —                                               |

| CS35         | TDV    | Clock edge to CSDO data valid                                                  | —                                         | —                  | 10                        | ns         | —                                               |

| CS36         | TDIV   | Clock edge to CSDO tri-stated                                                  | 10                                        |                    | 20                        | ns         | —                                               |

| CS40         | TCSDI  | Setup time of CSDI data input to<br>CSCK edge (CSCK pin is input<br>or output) | 20                                        | —                  | —                         | ns         | _                                               |

| CS41         | THCSDI | Hold time of CSDI data input to<br>CSCK edge (CSCK pin is input<br>or output)  | 20                                        | —                  | —                         | ns         | _                                               |

| CS50         | TCOFSF | COFS Fall Time<br>(COFS pin is output)                                         | —                                         | 10                 | 25                        | ns         | Note 1                                          |

| CS51         | TCOFSR | COFS Rise Time<br>(COFS pin is output)                                         | —                                         | 10                 | 25                        | ns         | Note 1                                          |

| CS55         | TSCOFS | Setup time of COFS data input to CSCK edge (COFS pin is input)                 | 20                                        | —                  | _                         | ns         | —                                               |

| CS56         | THCOFS | Hold time of COFS data input to CSCK edge (COFS pin is input)                  | 20                                        | —                  | —                         | ns         | _                                               |

## TABLE 23-29: DCI MODULE (MULTICHANNEL, I<sup>2</sup>S MODES) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for CSCK is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all DCI pins.

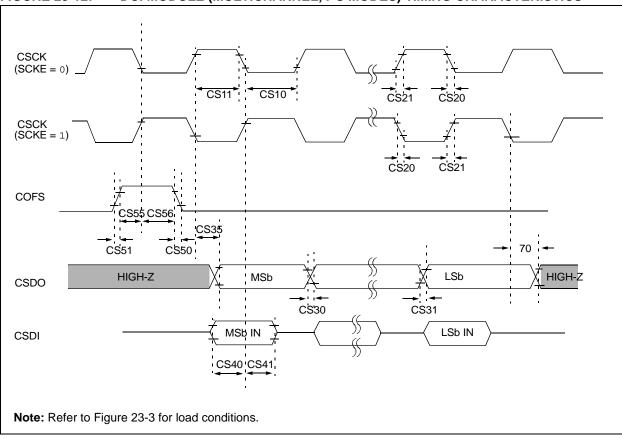

# FIGURE 23-20: I<sup>2</sup>C<sup>TM</sup> BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)