Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20 MIPS                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, LVD, POR, PWM, WDT             |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 144KB (48K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 4K x 8                                                                          |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6012at-20e-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

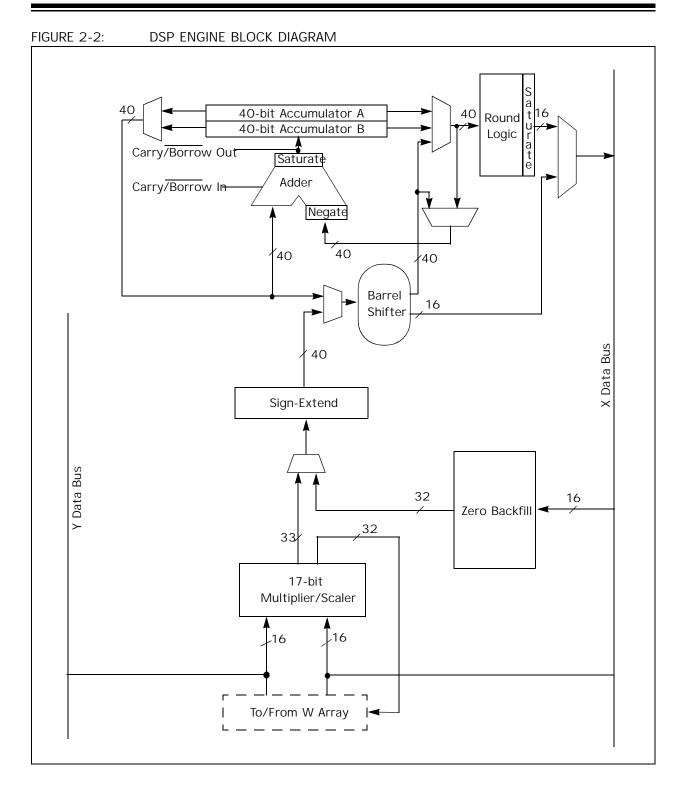

# 2.4 DSP Engine

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The dsPIC3OF is a single-cycle instruction flow architecture, therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations, which require no additional data. These instructions are ADD, SUB and NEG

The DSP engine has various options selected through various bits in the CPU Core Configuration register (CORCON), as listed below:

- 1. Fractional or integer DSP multiply (IF).

- 2. Signed or unsigned DSP multiply (US).

- 3. Conventional or convergent rounding (RND).

- 4. Automatic saturation on/off for AccA (SATA).

- 5. Automatic saturation on/off for AccB (SATB).

- 6. Automatic saturation on/off for writes to data memory (SATDW).

- 7. Accumulator Saturation mode selection (ACCSAT).

|    | Note:   | For CO  | RCO | N lay | out, s | see Table | e 3- | ·3.   |    |

|----|---------|---------|-----|-------|--------|-----------|------|-------|----|

| A  | block   | diagram | of  | the   | DSP    | engine    | is   | shown | in |

| Fi | gure 2- | 2.      |     |       |        |           |      |       |    |

| Instruction | Algebraic Operation | ACC Write Back |

|-------------|---------------------|----------------|

| CLR         | A = O               | Yes            |

| ED          | $A = (x  y)^2$      | No             |

| EDAC        | $A = A + (x y^2)$   | No             |

| MAC         | A = A + (x * y)     | Yes            |

| MAC         | $A = A + \hat{X}$   | No             |

| MOVSAC      | No change in A      | Yes            |

| MPY         | A = x * y           | No             |

| MPY         | $A = x^2$           | No             |

| MPY.N       | A = x * y           | No             |

| MSC         | A = A  x * y        | Yes            |

#### TABLE 2-2: DSP INSTRUCTIONS SUMMARY

# dsPIC30F6011A/6012A/6013A/6014A

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. Should a misaligned read or write be attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed, whereas if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap will then be executed, allowing the system and/or user to examine the machine state prior to execution of the address fault.

FIGURE 3-10: DATA ALIGNMENT

|      | 15 <b>MSB</b> | 8 | 7 LSB  | 0 |      |

|------|---------------|---|--------|---|------|

| 0001 | Byte1         |   | Byte 0 |   | 0000 |

| 0003 | Byte3         |   | Byte 2 |   | 0002 |

| 0005 | Byte5         |   | Byte 4 |   | 0004 |

|      |               |   |        |   |      |

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A sign-extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

## 3.2.5 NEAR DATA SPACE

An 8-Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using MOV instructions, which support memory direct addressing with a 16-bit address field.

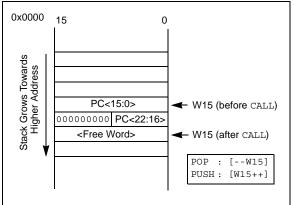

# 3.2.6 SOFTWARE STACK

The dsPIC DSC devices contain a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes as shown in Figure 3-11. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word aligned. Whenever an Effective Address (EA) is generated using W15 as a source or destination pointer, the address thus generated is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a Stack Error Trap will not occur. The Stack Error Trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a Stack Error Trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value, 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### FIGURE 3-11: CALL STACK FRAME

### 16.3.4 TRANSMIT INTERRUPT

The transmit interrupt flag (U1TXIF or U2TXIF) is located in the corresponding interrupt flag register.

The transmitter generates an edge to set the UxTXIF bit. The condition for generating the interrupt depends on the UTXISEL control bit:

- a) If UTXISEL = 0, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR). This implies that the transmit buffer has at least one empty word.

- b) If UTXISEL = 1, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR) and the transmit buffer is empty.

Switching between the two Interrupt modes during operation is possible and sometimes offers more flexibility.

#### 16.3.5 TRANSMIT BREAK

Setting the UTXBRK bit (UxSTA<11>) will cause the UxTX line to be driven to logío. The UTXBRK bit overrides all transmission activity. Therefore, the user should generally wait for the transmitter to be Idle before setting UTXBRK.

To send a break character, the UTXBRK bit must be set by software and must remain set for a minimum of 13 baud clock cycles. The UTXBRK bit is then cleared by software to generate Stop bits. The user must wait for a duration of at least one or two baud clock cycles in order to ensure a valid Stop bit(s) before reloading the UxTXB, or starting other transmitter activity. Transmission of a break character does not generate a transmit interrupt.

### 16.4 Receiving Data

#### 16.4.1 RECEIVING IN 8-BIT OR 9-BIT DATA MODE

The following steps must be performed while receiving 8-bit or 9-bit data:

- 1. Set up the UART (seeSection 16.3.1 Transmitting in 8-bit data mode).

- 2. Enable the UART (seeSection 16.3.1 Transmitting in 8-bit data mode).

- 3. A receive interrupt will be generated when one or more data words have been received, depending on the receive interrupt settings specified by the URXISEL bits (UxSTA<7:6>).

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read the received data from UxRXREG. The act of reading UxRXREG will move the next word to the top of the receive FIFO, and the PERR and

FERR values will be updated.

#### 16.4.2 RECEIVE BUFFER (U xRXB)

The receive buffer is 4 words deep. Including the Receive Shift register (UxRSR), the user effectively has a 5-word deep FIFO buffer.

URXDA (UxSTA<O>) = 1 indicates that the receive buffer has data available. URXDA  $\Theta$  implies that the buffer is empty. If a user attempts to read an empty buffer, the old values in the buffer will be read and no data shift will occur within the FIFO.

The FIFO is reset during any device Reset. It is not affected when the device enters or wakes up from a Power Saving mode.

#### 16.4.3 RECEIVE INTERRUPT

The receive interrupt flag (U1RXIF or U2RXIF) can be read from the corresponding interrupt flag register. The interrupt flag is set by an edge generated by the receiver. The condition for setting the receive interrupt flag depends on the settings specified by the URXISEL<1:0> (UxSTA<7:6>) control bits.

- a) If URXISEL<1:O> =OO orO1, an interrupt is generated every time a data word is transferred from the Receive Shift register (UxRSR) to the receive buffer. There may be one or more characters in the receive buffer.

- b) If URXISEL<1:O> =10, an interrupt is generated when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer, which as a result of the transfer, contains 3 characters.

- c) If URXISEL<1:O> =11, an interrupt is set when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer, which as a result of the transfer, contains 4 characters (i.e., becomes full).

Switching between the Interrupt modes during operation is possible, though generally not advisable during normal operation.

### 16.5 Reception Error Handling

#### 16.5.1 RECEIVE BUFFER OVERRUN ERROR (OERR BIT)

The OERR bit (UxSTA<1>) is set if all of the following conditions occur:

- a) The receive buffer is full.

- b) The Receive Shift register is full, but unable to transfer the character to the receive buffer.

- c) The Stop bit of the character in the UxRSR is detected, indicating that the UxRSR needs to transfer the character to the buffer.

The 20-bit mode treats each 256-bit AC-Link frame as sixteen, 16-bit time slots. In the 20-bit AC-Link mode, the module operates as if COFSG<3:0>1#11 and WS<3:0> =1111. The data alignment for 20-bit data slots is ignored. For example, an entire AC-Link data frame can be transmitted and received in a packed fashion by setting all bits in the TSCON and RSCON SFRs. Since the total available buffer length is 64 bits, it would take 4 consecutive interrupts to transfer the Setting BLEN<1:0> =01 will produce a CPU interrupt, AC-Link frame. The application software must keep track of the current AC-Link frame segment.

#### <sup>2</sup>S Mode Operation 18.7

The DCI module is configured for SImode by writing a value of 01 to the COFSM<1:0> control bits in the DCICON1 SFR. When operating in the<sup>2</sup>\$ mode, the DCI module will generate frame synchronization signals with a 50% duty cycle. Each edge of the frame synchronization signal marks the boundary of a new data word transfer.

The user must also select the frame length and data word size using the COFSG and WS control bits in the DCICON2 SFR.

#### 18.7.1 PS FRAME AND DATA WORD LENGTH SELECTION

The WS and COFSG control bits are set to produce the period for one half of afs Idata frame. That is, the frame length is the total number of CSCK cycles required for a left or a right data word transfer.

The BLEN bits must be set for the desired buffer length. once per <sup>2</sup>S frame.

#### PS DATA JUSTIFICATION 18.7.2

As per the<sup>2</sup>S specification, a data word transfer will, by default, begin one CSCK cycle after a transition of the WS signal. A MSb left justified option can be selected using the DJST control bit in the DCICON2 SFR.

If DJST = 1, the  $\frac{2}{5}$  data transfers will be MSb left justified. The MSb of the data word will be presented on the CSDO pin during the same CSCK cycle as the rising or falling edge of the COFS signal. The CSDO pin is tri-stated after the data word has been sent.

# 20.0 SYSTEM INTEGRATION

Note: This data sheet summarizes features of this group of dsPIC3OF devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to dsFeIC3OF Family Reference Manual (DS70046). For more information on the device instruction set and gramming, refer to thesPIC3OF Programmer's Reference Manual (DS70030).

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection:

**Oscillator Selection**

Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Programmable Brown-out Reset (BOR)

Watchdog Timer (WDT)

Power-Saving modes (Sleep and Idle)

Code Protection

- Unit ID Locations

- In-Circuit Serial Programming (ICSP)

dsPIC3OF devices have a Watchdog Timer, which is permanently enabled via the Configuration bits or can be software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a delay on power-up only, designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry.

Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer Wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit a wide variety of applications. In the Idle mode, the clock sources are still active, but the CPU is shut-off. The RC oscillator option saves system cost, while the LP crystal option saves power.

## 20.1 Oscillator System Overview

The dsPIC3OF oscillator system has the following modules and features:

Various external and internal oscillator options as clock sources

An on-chip PLL to boost internal operating frequency

A clock switching mechanism between various clock sources

Programmable clock postscaler for system power savings

A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures Clock Control register (OSCCON)

Configuration bits for main oscillator selection

Configuration bits determine the clock source upon Power-on Reset (POR) and Brown-out Reset (BOR). Thereafter, the clock source can be changed between permissible clock sources. The OSCCON register controls the clock switching and reflects system clock related status bits.

Table 20-1 provides a summary of the dsPIC3OF oscillator operating modes. A simplified diagram of the oscillator system is shown in Figure 20-1.

| DC CHARACTERISTICS                 |       |                                            |         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |         |       |                                                    |  |  |

|------------------------------------|-------|--------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|----------------------------------------------------|--|--|

| Param<br>No. Symbol Characteristic |       | Characteristic                             | Min     | Typ <sup>(1)</sup>                                                                                                                                                                                                                                                                      | Max     | Units | Conditions                                         |  |  |

|                                    | VIL   | Input Low Voltage <sup>(2)</sup>           |         |                                                                                                                                                                                                                                                                                         |         |       |                                                    |  |  |

| DI10                               |       | I/O pins:<br>with Schmitt Trigger buffer   | Vss     | _                                                                                                                                                                                                                                                                                       | 0.2 Vdd | V     |                                                    |  |  |

| DI15                               |       | MCLR                                       | Vss     | _                                                                                                                                                                                                                                                                                       | 0.2 Vdd | V     |                                                    |  |  |

| DI16                               |       | OSC1 (in XT, HS and LP modes)              | Vss     | —                                                                                                                                                                                                                                                                                       | 0.2 Vdd | V     |                                                    |  |  |

| DI17                               |       | OSC1 (in RC mode) <sup>(3)</sup>           | Vss     | —                                                                                                                                                                                                                                                                                       | 0.3 Vdd | V     |                                                    |  |  |

| DI18                               |       | SDA, SCL                                   | TBD     | —                                                                                                                                                                                                                                                                                       | TBD     | V     | SM bus disabled                                    |  |  |

| DI19                               |       | SDA, SCL                                   | TBD     | —                                                                                                                                                                                                                                                                                       | TBD     | V     | SM bus enabled                                     |  |  |

|                                    | Viн   | Input High Voltage <sup>(2)</sup>          |         |                                                                                                                                                                                                                                                                                         |         |       |                                                    |  |  |

| DI20                               |       | I/O pins:<br>with Schmitt Trigger buffer   | 0.8 Vdd | _                                                                                                                                                                                                                                                                                       | Vdd     | V     |                                                    |  |  |

| DI25                               |       | MCLR                                       | 0.8 Vdd | _                                                                                                                                                                                                                                                                                       | Vdd     | V     |                                                    |  |  |

| DI26                               |       | OSC1 (in XT, HS and LP modes)              | 0.7 Vdd | _                                                                                                                                                                                                                                                                                       | Vdd     | V     |                                                    |  |  |

| DI27                               |       | OSC1 (in RC mode) <sup>(3)</sup>           | 0.9 Vdd | —                                                                                                                                                                                                                                                                                       | Vdd     | V     |                                                    |  |  |

| DI28                               |       | SDA, SCL                                   | TBD     | —                                                                                                                                                                                                                                                                                       | TBD     | V     | SM bus disabled                                    |  |  |

| DI29                               |       | SDA, SCL                                   | TBD     | —                                                                                                                                                                                                                                                                                       | TBD     | V     | SM bus enabled                                     |  |  |

|                                    | ICNPU | CNxx Pull-up Current <sup>(2)</sup>        |         |                                                                                                                                                                                                                                                                                         |         |       |                                                    |  |  |

| DI30                               |       |                                            | 50      | 250                                                                                                                                                                                                                                                                                     | 400     | μΑ    | VDD = 5V, VPIN = VSS                               |  |  |

| DI31                               |       |                                            | TBD     | TBD                                                                                                                                                                                                                                                                                     | TBD     | μΑ    | VDD = 3V, VPIN = VSS                               |  |  |

|                                    | lı∟   | Input Leakage Current <sup>(2)(4)(5)</sup> |         |                                                                                                                                                                                                                                                                                         |         |       |                                                    |  |  |

| DI50                               |       | I/O ports                                  |         | 0.01                                                                                                                                                                                                                                                                                    | ±1      | μA    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance         |  |  |

| DI51                               |       | Analog input pins                          | _       | 0.50                                                                                                                                                                                                                                                                                    | —       | μA    | $VSS \le VPIN \le VDD,$<br>Pin at high-impedance   |  |  |

| DI55                               |       | MCLR                                       | —       | 0.05                                                                                                                                                                                                                                                                                    | ±5      | μΑ    | $VSS \leq VPIN \leq VDD$                           |  |  |

| DI56                               |       | OSC1                                       | —       | 0.05                                                                                                                                                                                                                                                                                    | ±5      | μA    | VSS $\leq$ VPIN $\leq$ VDD, XT, HS and LP Osc mode |  |  |

# TABLE 23-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Legend:** TBD = To Be Determined

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

**3:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the dsPIC30F device be driven with an external clock while in RC mode.

4: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

5: Negative current is defined as current sourced by the pin.

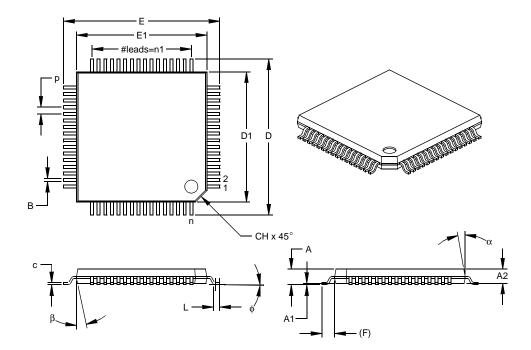

64-Lead Plastic Thin Quad Flatpack 14x14x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

|                          | Units     |      | INCHES |      | MILLIMETERS* |       |      |  |

|--------------------------|-----------|------|--------|------|--------------|-------|------|--|

| Dimensi                  | on Limits | MIN  | NOM    | MAX  | MIN          | NOM   | MAX  |  |

| Number of Pins           | n         |      | 64     |      |              | 64    |      |  |

| Pitch                    | р         |      | .032   |      |              | 0.80  |      |  |

| Pins per Side            | n1        |      | 16     |      |              | 16    |      |  |

| Overall Height           | А         |      |        | .047 |              |       | 1.20 |  |

| Molded Package Thickness | A2        | .037 | .039   | .041 | 0.95         | 1.00  | 1.05 |  |

| Standoff §               | A1        | .002 |        | .006 | 0.05         |       | 0.15 |  |

| Foot Length              | L         | .018 | .024   | .030 | 0.45         | 0.60  | 0.75 |  |

| Footprint (Reference)    | (F)       |      | .039   |      |              | 1.00  |      |  |

| Foot Angle               | φ         | 0    |        | 7    | 0            |       | 7    |  |

| Overall Width            | Е         |      | .630   |      |              | 16.00 |      |  |

| Overall Length           | D         |      | .630   |      |              | 16.00 |      |  |

| Molded Package Width     | E1        |      | .551   |      |              | 14.00 |      |  |

| Molded Package Length    | D1        |      | .551   |      |              | 14.00 |      |  |

| Lead Thickness           | С         | .004 |        | .008 | 0.09         |       | 0.20 |  |

| Lead Width               | В         | .019 | .013   | .018 | 0.30         | 0.32  | 0.45 |  |

| Pin 1 Corner Chamfer     | CH        |      |        |      |              |       |      |  |

| Mold Draft Angle Top     | α         | 11   |        | 13   | 11           |       | 13   |  |

| Mold Draft Angle Bottom  | β         | 11   |        | 13   | 11           |       | 13   |  |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-026

Drawing No. C04-085

# dsPIC30F6011A/6012A/6013A/6014A

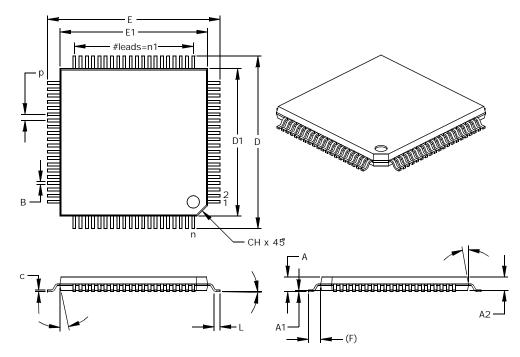

80-Lead Plastic Thin Quad Flatpack 12x12x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

|                          | Units    |      | INCHES |                  | MILLIMETERS* |                   |        |  |

|--------------------------|----------|------|--------|------------------|--------------|-------------------|--------|--|

| Dimensio                 | n Limits | MIN  | NOM    | MAX              | MIN          | NOM               | MAX    |  |

| Number of Pins           | n        |      | 80     |                  |              | 80                |        |  |

| Pitch                    | р        |      | .020   |                  |              | 0.50              | 5      |  |

| Pins per Side            | n1       |      | 20     | )                |              | 2                 | 2D     |  |

| Overall Height           | Α        | .039 | .043   | .04              | 1.00         | 1.10              | 1.2    |  |

| Molded Package Thickness | A2       | .03  | 7.03   | 9.C              | 41 C         | ).95 <sup>-</sup> | 1.00   |  |

| Standoff §               | A1       | .00  | 2.00   | 4.00             | 06 0         | .05 0             | .10 0  |  |

| Foot Length              | L        | .018 | .02    | 4.03             | 30 C         | .45 0             | .60 (  |  |

| Footprint (Reference)    | (F)      |      | .039   |                  |              | 1.00              | 1      |  |

| Foot Angle               |          | 0    | 3.5    | 7                |              | 9 3.              | 5      |  |

| Overall Width            | E        | .54  | 1.55   | 1.56             | 1 13.        | 75 14             | .00 14 |  |

| Overall Length           | D        | .54  | 1.55   | 1.56             | 1 13.        | 75 14             | .00 14 |  |

| Molded Package Width     | E1       | .46  | 3.47   | .4               | 82 11        | .75 12            | 2.00 1 |  |

| Molded Package Length    | D1       | .46  | 3.4    | .4               | 82 11        | 75 12             | 2.00 1 |  |

| Lead Thickness           | С        | .004 | .006   | .00              | 8 0.         | 09 0.             | .15 0  |  |

| Lead Width               | В        | .00  | .00    | 9.0 <sup>°</sup> | 11 0.        | 17 0.             | .22 0  |  |

| Pin 1 Corner Chamfer     | СН       | .025 | .035   | .045             | 0.64         | 0.89              | 1.14   |  |

| Mold Draft Angle Top     |          | 5    | 10     | 15               |              | 5 1(              | Q 1!   |  |

| Mold Draft Angle Bottom  |          | 5    | 10     | 15               |              | 5 1(              | Q 1!   |  |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010 (0.254mm) per side. JEDEC Equivalent: MS-026

Drawing No. CO4-092