# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | e200z7                                                                  |

| Core Size                  | 32-Bit Dual-Core                                                        |

| Speed                      | 264MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, Ethernet, FlexCANbus, LINbus, SCI, SPI                 |

| Peripherals                | DMA, LVD, POR, Zipwire                                                  |

| Number of I/O              | 293                                                                     |

| Program Memory Size        | 4MB (4M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 40x12b eQADCx2                                                      |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 416-BGA                                                                 |

| Supplier Device Package    | 416-MAPBGA (27x27)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5775edk3mme3 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1** Introduction

# **1.1 Features summary**

On-chip modules available within the family include the following features:

- Three dual issue, 32-bit CPU core complexes (e200z7), two of which run in lockstep

- Power Architecture embedded specification compliance

- Instruction set enhancement allowing variable length encoding (VLE), optional encoding of mixed 16-bit and 32-bit instructions, for code size footprint reduction

- On the two computational cores: Signal processing extension (SPE1.1) instruction support for digital signal processing (DSP)

- Single-precision floating point operations

- On the two computational cores: 16 KB I-Cache and 16 KB D-Cache

- Hardware cache coherency between cores

- 16 hardware semaphores

- 3-channel CRC module

- 4 MB on-chip flash memory

- Supports read during program and erase operations, and multiple blocks allowing EEPROM emulation

- 512 KB on-chip general-purpose SRAM including 64 KB standby RAM

- Two multichannel direct memory access controllers (eDMA)

- 64 channels per eDMA

- Dual core Interrupt Controller (INTC)

- Dual phase-locked loops (PLLs) with stable clock domain for peripherals and frequency modulation (FM) domain for computational shell

- Crossbar Switch architecture for concurrent access to peripherals, flash memory, or RAM from multiple bus masters with End-To-End ECC

- System Integration Unit (SIU)

- Error Injection Module (EIM) and Error Reporting Module (ERM)

- Four protected port output (PPO) pins

- Boot Assist Module (BAM) supports serial bootload via CAN or SCI

- Up to three second-generation Enhanced Time Processor Units (eTPUs)

- 32 channels per eTPU

- Total of 36 KB code RAM

- Total of 9 KB parameter RAM

| Symbol                                         | Parameter                                               | Conditions                   |      | Unit                |      |      |  |

|------------------------------------------------|---------------------------------------------------------|------------------------------|------|---------------------|------|------|--|

| Symbol                                         | Parameter                                               | Conditions                   | Min  | Тур                 | Max  | 7    |  |

| V <sub>RL_SD</sub>                             | SDADC ground reference voltage                          | -                            |      | V <sub>SSA_SD</sub> |      | V    |  |

| V <sub>DDA_SD</sub>                            | SDADC supply voltage <sup>15</sup>                      | -                            | 4.5  | —                   | 5.5  | V    |  |

| V <sub>DDA_EQA/B</sub>                         | eQADC supply voltage                                    | -                            | 4.75 | —                   | 5.25 | V    |  |

| V <sub>RH_SD</sub>                             | SDADC reference                                         | -                            | 4.5  | V <sub>DDA_SD</sub> | 5.5  | V    |  |

| V <sub>DDA_SD</sub> – V <sub>RH_SD</sub>       | SDADC reference differential voltage                    | -                            | _    | _                   | 25   | mV   |  |

| V <sub>SSA_SD</sub> – V <sub>RL_SD</sub>       | V <sub>RL_SD</sub> differential voltage                 | -                            | -25  | —                   | 25   | mV   |  |

| V <sub>RH_EQ</sub>                             | eQADC reference                                         | -                            | 4.75 | _                   | 5.25 | V    |  |

| V <sub>DDA_EQA/B</sub> –<br>V <sub>RH_EQ</sub> | eQADC reference differential voltage                    | -                            | _    | _                   | 25   | mV   |  |

| $V_{SSA_{EQ}} - V_{RL_{EQ}}$                   | V <sub>RL_EQ</sub> differential voltage                 | -                            | -25  | _                   | 25   | mV   |  |

| $V_{SSA_{EQ}} - V_{SS}$                        | V <sub>SSA_EQ</sub> differential voltage                | -                            | -25  |                     | 25   | mV   |  |

| $V_{SSA\_SD} - V_{SS}$                         | V <sub>SSA_SD</sub> differential voltage                | -                            | -25  | _                   | 25   | mV   |  |

| V <sub>RAMP</sub>                              | Slew rate on power supply pins                          | -                            | —    | _                   | 100  | V/ms |  |

|                                                |                                                         | Current                      |      |                     |      |      |  |

| l <sub>IC</sub>                                | DC injection current (per pin) <sup>16,</sup><br>17, 18 | Digital pins and analog pins | -3.0 | —                   | 3.0  | mA   |  |

| I <sub>MAXSEG</sub>                            | Maximum current per power segment <sup>19, 20</sup>     | -                            | -80  |                     | 80   | mA   |  |

Table 3. Device operating conditions (continued)

- 1. Maximum operating frequency is applicable to the computational cores and platform for the device. See the Clocking chapter in the MPC5775E Microcontroller Reference Manual for more information on the clock limitations for the various IP blocks on the device.

- 2. If frequency modulation (FM) is enabled, the maximum frequency still cannot exceed this value.

- 3. MPC5775B Max value is 220 MHz.

- 4. MPC5775B Max value is 110 MHz

- 5. The maximum specification for operating junction temperature T<sub>J</sub> must be respected. Thermal characteristics provides details.

- 6. Core voltage as measured on device pin to guarantee published silicon performance

- 7. During power ramp, voltage measured on silicon might be lower. Maximum performance is not guaranteed, but correct silicon operation is guaranteed. See power management and reset management for description.

- 8. Maximum core voltage is not permitted for entire product life. See absolute maximum rating.

- 9. When internal LVD/HVDs are disabled, external monitoring is required to guarantee device operation. Failure to monitor externally supply voltage may result in erroneous operation of the device.

- 10. This LVD/HVD disabled supply voltage condition only applies after LVD/HVD are disabled by the application during the reset sequence, and the LVD/HVD are active until that point.

- 11. This spec does not apply to  $V_{DDEH1}$ .

- 12. When internal flash memory regulator is used:

- Flash memory read operation is supported for a minimum V<sub>DDPMC</sub> value of 3.15 V.

- Flash memory read, program, and erase operations are supported for a minimum V<sub>DDPMC</sub> value of 3.5 V.

When flash memory power is supplied externally (V<sub>DDPMC</sub> shorted to V<sub>DDFLA</sub>): The V<sub>DDPMC</sub> range must be within the limits specified for LVD\_FLASH and HVD\_FLASH monitoring. Table 26 provides the monitored LVD\_FLASH and HVD\_FLASH limits.

- 13. If the standby RAM regulator is not used, the  $V_{STBY}$  supply input pin must be tied to ground.

- 14. V<sub>STBY\_BO</sub> is the maximum voltage that sets the standby RAM brownout flag in the device logic. The minimum voltage for RAM data retention is guaranteed always to be less than the V<sub>STBY\_BO</sub> maximum value.

- 15. For supply voltages between 3.0 V and 4.0 V there will be no guaranteed precision of ADC (accuracy/linearity). ADC will recover to a fully functional state when the voltage rises above 4.0 V.

- 16. Full device lifetime without performance degradation

- 17. I/O and analog input specifications are only valid if the injection current on adjacent pins is within these limits. See the absolute maximum ratings table for maximum input current for reliability requirements.

- 18. The I/O pins on the device are clamped to the I/O supply rails for ESD protection. When the voltage of the input pin is above the supply rail, current will be injected through the clamp diode to the supply rail. For external RC network calculation, assume a typical 0.3 V drop across the active diode. The diode voltage drop varies with temperature.

- 19. The sum of all controller pins (including both digital and analog) must not exceed 200 mA. A V<sub>DDEx</sub>/V<sub>DDEHx</sub> power segment is defined as one or more GPIO pins located between two V<sub>DDEx</sub>/V<sub>DDEHx</sub> supply pins.

- 20. The average current values given in I/O pad current specifications should be used to calculate total I/O segment current.

# 3.5 DC electrical specifications

### NOTE

$I_{DDA\_MISC}$  is the sum of current consumption of IRC,  $I_{TRNG}$ , and  $I_{STBY}$  in the 5 V domain. IRC current is provided in the IRC specifications.

### NOTE

I/O, XOSC, EQADC, SDADC, and Temperature Sensor current specifications are in those components' dedicated sections.

| Symbol              | Parameter                                                                      | Conditions                                   |     | Value | /alue |      |

|---------------------|--------------------------------------------------------------------------------|----------------------------------------------|-----|-------|-------|------|

| Symbol              | Parameter                                                                      | Conditions                                   | Min | Тур   | Max   | Unit |

| I <sub>DD</sub>     | Operating current on the V <sub>DD</sub> core logic supply <sup>1</sup>        | LVD/HVD enabled, $V_{DD}$ = 1.2 V to 1.32 V  |     | 0.65  | 1.35  | A    |

|                     |                                                                                | LVD/HVD disabled, $V_{DD} = 1.2 V$ to 1.38 V | _   | 0.65  | 1.4   |      |

| I <sub>DD_PE</sub>  | Operating current on the V <sub>DD</sub> supply for flash memory program/erase | -                                            |     | _     | 85    | mA   |

| I <sub>DDPMC</sub>  | Operating current on the V <sub>DDPMC</sub> supply <sup>2</sup>                | Flash memory read                            | _   | —     | 40    | mA   |

|                     |                                                                                | Flash memory program/erase                   | —   | —     | 70    |      |

|                     |                                                                                | PMC only                                     | _   | _     | 35    |      |

|                     | Operating current on the V <sub>DDPMC</sub> supply                             | Flash memory read                            | _   | _     | 10    | mA   |

|                     | (internal core regulator bypassed)                                             | Flash memory program/erase                   | _   | —     | 40    |      |

|                     |                                                                                | PMC only                                     | _   | _     | 5     |      |

| IREGCTL             | Core regulator DC current output on V <sub>REGCTL</sub> pin                    | -                                            | _   | _     | 25    | mA   |

| I <sub>STBY</sub>   | Standby RAM supply current (T <sub>J</sub> = 150°C)                            | 1.08 V                                       | _   | _     | 1140  | μA   |

|                     |                                                                                | 1.25 V to 5.5 V                              | _   | —     | 1170  |      |

| I <sub>DD_PWR</sub> | Operating current on the V <sub>DDPWR</sub> supply                             | -                                            | —   | —     | 50    | mA   |

| I <sub>BG_REF</sub> | Bandgap reference current consumption <sup>3</sup>                             |                                              | —   | —     | 600   | μA   |

| I <sub>TRNG</sub>   | True Random Number Generator current                                           | —                                            | —   | —     | 2.1   | mA   |

Table 4. DC electrical specifications

#### **Electrical characteristics**

| Symbol           | Parameter             | Conditions                                 |     | Value |     |      |  |

|------------------|-----------------------|--------------------------------------------|-----|-------|-----|------|--|

| Symbol           | Farameter             | Conditions                                 | Min | Тур   | Max | Unit |  |

| I <sub>WPU</sub> | Weak pullup current   | V <sub>IN</sub> = 0.35 * V <sub>DDEx</sub> | 40  | _     | 120 | μA   |  |

|                  |                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V          |     |       |     |      |  |

|                  |                       | V <sub>IN</sub> = 0.35 * V <sub>DDEx</sub> | 25  | —     | 80  |      |  |

|                  |                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V          |     |       |     |      |  |

| I <sub>WPD</sub> | Weak pulldown current | V <sub>IN</sub> = 0.65 * V <sub>DDEx</sub> | 40  | —     | 120 | μA   |  |

|                  |                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V          |     |       |     |      |  |

|                  |                       | V <sub>IN</sub> = 0.65 * V <sub>DDEx</sub> | 25  | _     | 80  |      |  |

|                  |                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V          |     |       |     |      |  |

### Table 7. I/O pullup/pulldown DC electrical characteristics

The specifications in Table 8 apply to the pins ANA0\_SDA0 to ANA7, ANA16\_SDB0 to ANA23\_SDC3, and ANB0\_SDD0 to ANB7\_SDD7.

Table 8.

I/O pullup/pulldown resistance electrical characteristics

| Symbol            | Parameter                                             | Conditions |     | Unit |     |    |

|-------------------|-------------------------------------------------------|------------|-----|------|-----|----|

| Symbol            |                                                       |            | Min | Тур  | Мах |    |

| R <sub>PUPD</sub> |                                                       | 200 kΩ     | 130 | 200  | 280 | kΩ |

|                   | pulldown resistance                                   | 100 kΩ     | 65  | 100  | 140 |    |

|                   |                                                       | 5 kΩ       | 1.4 | 5    | 7.5 |    |

| $\Delta_{PUPD}$   | R <sub>PUPD</sub> pullup/pulldown resistance mismatch | —          |     |      | 5   | %  |

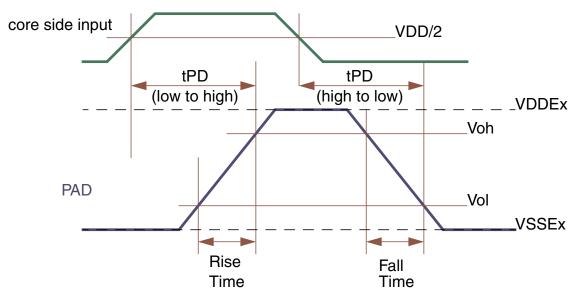

# 3.6.2 Output pad specifications

Figure 4 shows output DC electrical characteristics.

**Electrical characteristics**

Figure 4. I/O output DC electrical characteristics definition

The following tables specify output DC electrical characteristics.

| Table 9. | GPIO data pad | I output buffer electrical | characteristics (SR pads) <sup>1</sup> |

|----------|---------------|----------------------------|----------------------------------------|

|----------|---------------|----------------------------|----------------------------------------|

| Symbol          | Parameter            | Conditions <sup>2</sup>                   |                       | Value <sup>3</sup> |     |     |    |  | Unit |

|-----------------|----------------------|-------------------------------------------|-----------------------|--------------------|-----|-----|----|--|------|

| Symbol          | Farameter            | Conditions                                |                       | Min                | Тур | Max |    |  |      |

| I <sub>OH</sub> | GPIO pad output high | V <sub>OH</sub> = 0.8 * V <sub>DDEx</sub> | PCR[SRC] = 11b or 01b | 25                 | —   | _   | mA |  |      |

|                 | current              | 4.5 V < V <sub>DDEx</sub> < 5.5 V         | PCR[SRC] = 10b or 00b | 15                 | —   | _   |    |  |      |

|                 |                      | V <sub>OH</sub> = 0.8 * V <sub>DDEx</sub> | PCR[SRC] = 11b or 01b | 13                 | —   | —   |    |  |      |

|                 |                      | 3.0 V < V <sub>DDEx</sub> < 3.6 V         | PCR[SRC] = 10b or 00b | 8                  | —   | _   |    |  |      |

| I <sub>OL</sub> | GPIO pad output low  | $V_{OL} = 0.2 * V_{DDEx}$                 | PCR[SRC] = 11b or 01b | 48                 | —   | —   | mA |  |      |

|                 | current              | 4.5 V < V <sub>DDEx</sub> < 5.5 V         | PCR[SRC] = 10b or 00b | 22                 | —   | _   |    |  |      |

|                 |                      | $V_{OL} = 0.2 * V_{DDEx}$                 | PCR[SRC] = 11b or 01b | 17                 | —   | —   |    |  |      |

|                 |                      | 3.0 V < V <sub>DDEx</sub> < 3.6 V         | PCR[SRC] = 10b or 00b | 10.5               | —   | _   |    |  |      |

Table continues on the next page ...

| Table 9. | GPIO data pad output buffer electrical characteristics ( | (SR pads) <sup>1</sup> | (continued) |

|----------|----------------------------------------------------------|------------------------|-------------|

|----------|----------------------------------------------------------|------------------------|-------------|

|                  |                                       | _                                 |                         |     | Value <sup>3</sup> |      | <b>.</b> |

|------------------|---------------------------------------|-----------------------------------|-------------------------|-----|--------------------|------|----------|

| Symbol           | Parameter                             | Conditions <sup>2</sup>           |                         | Min | Тур                | Max  | Uni      |

| t <sub>R_F</sub> | GPIO pad output                       | PCR[SRC] = 11b                    | C <sub>L</sub> = 25 pF  | _   | _                  | 1.2  | ns       |

|                  | transition time (rise/fall)           | 4.5 V < V <sub>DDEx</sub> < 5.5 V | $C_{L} = 50  \text{pF}$ | _   |                    | 2.5  | 1        |

|                  |                                       | DDLX                              | C <sub>L</sub> = 200 pF |     |                    | 8    | -        |

|                  |                                       | PCR[SRC] = 11b                    | C <sub>L</sub> = 25 pF  |     | _                  | 1.7  |          |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 50 pF  |     |                    | 3.25 | -        |

|                  |                                       |                                   | C <sub>L</sub> = 200 pF | _   | _                  | 12   | 1        |

|                  |                                       | PCR[SRC] = 10b                    | C <sub>L</sub> = 50 pF  | _   | _                  | 5    | 1        |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF | _   | _                  | 18   | 1        |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF  |     | _                  | 7    | -        |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF |     | _                  | 25   |          |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF  |     |                    | 13   | -        |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF |     | _                  | 24   | -        |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF  | _   |                    | 25   | 1        |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF |     |                    | 30   | -        |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF  | _   |                    | 24   | 1        |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF |     |                    | 50   | 1        |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF  |     |                    | 40   | -        |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF |     |                    | 51   | 1        |

| t <sub>PD</sub>  | GPIO pad output                       |                                   | C <sub>L</sub> = 50 pF  |     |                    | 6    | ns       |

|                  | propagation delay time                | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF |     |                    | 13   | -        |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF  |     |                    | 8.25 | -        |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF |     |                    | 19.5 | 1        |

|                  |                                       | PCR[SRC] = 10b                    | C <sub>L</sub> = 50 pF  |     |                    | 9    | 1        |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF |     |                    | 22   | 1        |

|                  |                                       |                                   | C <sub>I</sub> = 50 pF  |     |                    | 12.5 |          |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF |     |                    | 35   | 1        |

|                  |                                       | PCR[SRC] = 01b                    | C <sub>L</sub> = 50 pF  |     |                    | 27   | 1        |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF |     |                    | 40   | 1        |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF  |     |                    | 45   | 1        |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V |                         |     |                    | 65   | 1        |

|                  |                                       |                                   | $C_L = 50 \text{ pF}$   |     |                    | 40   | -        |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V |                         |     |                    | 65   | 1        |

|                  |                                       |                                   | $C_{L} = 50  \text{pF}$ |     |                    | 75   | -        |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V |                         |     |                    | 100  | -        |

| skew_wl          | Difference between rise and fall time |                                   | <u>  - ·</u>            | —   |                    | 25   | %        |

1. All GPIO pad output specifications are valid for  $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 5.5 \text{ V}$ , except where explicitly stated. 2. PCR[SRC] values refer to the setting of that register field in the SIU.

- 3. All values to be confirmed during device validation.

| Symphol                 | Parameter                                      | Conditions                                  |       | Unit |                  |     |

|-------------------------|------------------------------------------------|---------------------------------------------|-------|------|------------------|-----|

| Symbol                  |                                                |                                             | Min   | Тур  | Max              |     |

| $\Delta_{PLL1IN}$       | PLL1 input clock duty cycle <sup>1</sup>       | —                                           | 35    | —    | 65               | %   |

| f <sub>PLL1VCO</sub>    | PLL1 VCO frequency                             | —                                           | 600   | —    | 1250             | MHz |

| f <sub>PLL1PHI</sub>    | PLL1 output clock PHI                          | —                                           | 4.762 | —    | 264 <sup>2</sup> | MHz |

| t <sub>PLL1LOCK</sub>   | PLL1 lock time                                 | —                                           | _     | —    | 100              | μs  |

| $ \Delta_{PLL1PHISPJ} $ | PLL1_PHI single period peak-to-<br>peak jitter | f <sub>PLL1PHI</sub> = 200 MHz, 6-<br>sigma | _     |      | 500 <sup>3</sup> | ps  |

| f <sub>PLL1MOD</sub>    | PLL1 modulation frequency                      | —                                           | _     | —    | 250              | kHz |

| δ <sub>PLL1MOD</sub>    | PLL1 modulation depth (when                    | Center spread                               | 0.25  | —    | 2                | %   |

|                         | enabled)                                       | Down spread                                 | 0.5   | —    | 4                | %   |

| I <sub>PLL1</sub>       | PLL1 consumption                               | FINE LOCK state                             | _     | —    | 6                | mA  |

Table 12. PLL1 electrical characteristics (continued)

1. PLL1IN clock retrieved directly from either internal PLL0 or external XOSC clock. Input characteristics are granted when using internal PLL0 or external oscillator in functional mode.

2. MPC5775B Max value is 220MHz.

3. Noise on the V<sub>DD</sub> supply with frequency content below 40 kHz and above 50 MHz is filtered by the PLL. Noise on the V<sub>DD</sub> supply with frequency content in the range of 40 kHz – 50 MHz must be filtered externally to the device.

# 3.7.2 Oscillator electrical specifications

### NOTE

All oscillator specifications in Table 13 are valid for  $V_{DDEH6} = 3.0 \text{ V}$  to 5.5 V.

Table 13. External oscillator (XOSC) electrical specifications

| Sumbol             | Parameter                                                         | Conditions                                   | Va                     | alue                   | Unit |

|--------------------|-------------------------------------------------------------------|----------------------------------------------|------------------------|------------------------|------|

| Symbol             | Parameter                                                         | Conditions                                   | Min                    | Max                    |      |

| f <sub>XTAL</sub>  | Crystal frequency range                                           | —                                            | 8                      | 40                     | MHz  |

| t <sub>cst</sub>   | Crystal start-up time <sup>1, 2</sup>                             | T <sub>J</sub> = 150 °C                      | —                      | 5                      | ms   |

| t <sub>rec</sub>   | Crystal recovery time <sup>3</sup>                                | —                                            | —                      | 0.5                    | ms   |

| V <sub>IHEXT</sub> | EXTAL input high voltage (external reference)                     | V <sub>REF</sub> = 0.28 * V <sub>DDEH6</sub> | V <sub>REF</sub> + 0.6 |                        | V    |

| V <sub>ILEXT</sub> | EXTAL input low voltage (external reference)                      | V <sub>REF</sub> = 0.28 * V <sub>DDEH6</sub> | —                      | V <sub>REF</sub> – 0.6 | V    |

| $C_{S\_EXTAL}$     | Total on-chip stray capacitance on EXTAL pin <sup>4</sup>         | 416-ball MAPBGA                              | 2.3                    | 3.0                    | pF   |

| $C_{S_XTAL}$       | Total on-chip stray capacitance on XTAL pin <sup>4</sup>          | 416-ball MAPBGA                              | 2.3                    | 3.0                    | pF   |

| 9 <sub>m</sub>     | Oscillator transconductance <sup>5</sup>                          | Low                                          | 3                      | 10                     | mA/V |

|                    |                                                                   | Medium                                       | 10                     | 27                     |      |

|                    |                                                                   | High                                         | 12                     | 35                     | 1    |

| V <sub>EXTAL</sub> | Oscillation amplitude on the EXTAL pin after startup <sup>6</sup> | _                                            | 0.5                    | 1.6                    | V    |

| V <sub>HYS</sub>   | Comparator hysteresis                                             | —                                            | 0.1                    | 1.0                    | V    |

| I <sub>XTAL</sub>  | XTAL current <sup>6, 7</sup>                                      | —                                            | —                      | 14                     | mA   |

- 11. All channels have same 10 k $\Omega$  < Rs < 100 k $\Omega$  Channel under test has Rs = 10 k $\Omega$ ,  $I_{INJ}=I_{INJMAX}$ ,  $I_{INJMIN}$ .

- 12. The TUE specification is always less than the sum of the INL, DNL, offset, and gain errors due to cancelling errors.

- 13. TUE does not apply to differential conversions.

- Variable gain is controlled by setting the PRE\_GAIN bits in the ADC\_ACR1-8 registers to select a gain factor of ×1, ×2, or ×4. Settings are for differential input only. Tested at ×1 gain. Values for other settings are guaranteed as indicated.

- 15. Guaranteed 10-bit monotonicity.

- 16. At  $V_{RH_{EQ}} V_{RL_{EQ}} = 5.12$  V, one LSB = 1.25 mV.

# 3.8.2 Sigma-Delta ADC (SDADC)

The SDADC is a 16-bit Sigma-Delta analog-to-digital converter with a 333 Ksps maximum output conversion rate.

### NOTE

The voltage range is 4.5 V to 5.5 V for SDADC specifications, except where noted otherwise.

| Symbol                  | Parameter                                  | Conditions                                                                             |     | Value                  | e                   | Unit |

|-------------------------|--------------------------------------------|----------------------------------------------------------------------------------------|-----|------------------------|---------------------|------|

| Symbol                  | Parameter                                  | Conditions                                                                             | Min | Тур                    | Мах                 |      |

| V <sub>IN</sub>         | ADC input signal                           |                                                                                        | 0   | —                      | V <sub>DDA_SD</sub> | V    |

| V <sub>IN_PK2PK</sub> 1 | Input range peak to<br>peak                | Single ended<br>V <sub>INM</sub> = V <sub>RL SD</sub>                                  |     | AIN                    | V                   |      |

|                         | $V_{IN_{PK2PK}} = V_{INP}^2 - V_{INM}^{3}$ | Single ended                                                                           |     | ±0.5*V <sub>RI</sub>   | H_SD                |      |

|                         |                                            | V <sub>INM</sub> = 0.5*V <sub>RH_SD</sub><br>GAIN = 1                                  |     |                        |                     |      |

|                         |                                            | Single ended                                                                           |     | ±V <sub>RH_SD</sub> /0 | GAIN                |      |

|                         |                                            | $V_{INM} = 0.5^* V_{RH\_SD}$                                                           |     |                        |                     |      |

|                         |                                            | GAIN = 2,4,8,16                                                                        |     |                        |                     |      |

|                         |                                            | Differential                                                                           |     | ±V <sub>RH_SD</sub> /0 | GAIN                |      |

|                         |                                            | 0 < V <sub>IN</sub> < V <sub>DDEx</sub>                                                |     |                        |                     |      |

| f <sub>ADCD_M</sub>     | SD clock frequency <sup>4</sup>            | —                                                                                      | 4   | 14.4                   | 16                  | MHz  |

| f <sub>ADCD_S</sub>     | Conversion rate                            | —                                                                                      | —   |                        | 333                 | Ksps |

|                         | Oversampling ratio                         | Internal modulator                                                                     | 24  |                        | 256                 | —    |

| RESOLUTION              | SD register resolution <sup>5</sup>        | 2's complement notation                                                                | 16  |                        |                     | bit  |

| GAIN                    | ADC gain                                   | Defined through<br>SDADC_MCR[PGAN]. Only integer<br>powers of 2 are valid gain values. | 1   |                        | 16                  | _    |

### Table 17. SDADC electrical specifications

Table continues on the next page ...

#### **Electrical characteristics**

| Gumbal                   | Deveryoter                                    | Conditions                          |      | Value |     | Unit |

|--------------------------|-----------------------------------------------|-------------------------------------|------|-------|-----|------|

| Symbol                   | Parameter                                     | Conditions                          | Min  | Тур   | Max | Unit |

| SINAD <sub>DIFF150</sub> | Signal to noise and                           | Gain = 1                            | 72   | _     | _   | dBFS |

|                          | distortion ratio in<br>differential mode, 150 | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |     |      |

|                          | Ksps output rate                              | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |     |      |

|                          |                                               | Gain = 2                            | 72   | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |     |      |

|                          |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |     |      |

|                          |                                               | Gain = 4                            | 69   | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |     |      |

|                          |                                               | $V_{RH_SD} = V_{DDA_SD}$            |      |       |     |      |

|                          |                                               | Gain = 8                            | 68.8 | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |     |      |

|                          |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |     |      |

|                          |                                               | Gain = 16                           | 64.8 | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |     |      |

|                          |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |     |      |

| SINAD <sub>DIFF333</sub> | Signal to noise and                           | Gain = 1                            | 66   | _     | _   | dBFS |

|                          | distortion ratio in<br>differential mode, 333 | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |     |      |

|                          | Ksps output rate                              | $V_{RH\_SD} = V_{DDA\_SD}$          |      |       |     |      |

|                          |                                               | Gain = 2                            | 66   | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |     |      |

|                          |                                               | $V_{RH\_SD} = V_{DDA\_SD}$          |      |       |     |      |

|                          |                                               | Gain = 4                            | 63   | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |     |      |

|                          |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |     |      |

|                          |                                               | Gain = 8                            | 62   | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |     |      |

|                          |                                               | $V_{RH\_SD} = V_{DDA\_SD}$          |      |       |     |      |

|                          |                                               | Gain = 16                           | 59   | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |     |      |

|                          |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |     |      |

| Table 17 | SDADC electrical | specifications | (continued) |

|----------|------------------|----------------|-------------|

|          |                  | specifications | (continueu) |

Table continues on the next page...

#### **Electrical characteristics**

| Symbol                 | Parameter                                                    | Conditions                          |      | Value |      | Uni |

|------------------------|--------------------------------------------------------------|-------------------------------------|------|-------|------|-----|

| Symbol                 | Farameter                                                    | Conditions                          | Min  | Тур   | Max  |     |

| THD <sub>DIFF333</sub> | Total harmonic                                               | Gain = 1                            | 65   | —     | —    | dBF |

|                        | distortion in differential mode, 333 Ksps                    | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |      |     |

|                        | output rate                                                  | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |      |     |

|                        |                                                              | Gain = 2                            | 68   |       | _    |     |

|                        |                                                              | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |      |     |

|                        |                                                              | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |      |     |

|                        |                                                              | Gain = 4                            | 74   | _     | _    |     |

|                        |                                                              | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |      |     |

|                        |                                                              | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |      |     |

|                        |                                                              | Gain = 8                            | 80   |       | _    |     |

|                        |                                                              | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |      |     |

|                        |                                                              | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |      |     |

|                        |                                                              | Gain = 16                           | 80   | _     | _    |     |

|                        |                                                              | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |      |     |

|                        |                                                              | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |      |     |

| THD <sub>SE150</sub>   | Total harmonic                                               | Gain = 1                            | 68   | _     | _    | dBF |

|                        | distortion in single-<br>ended mode, 150<br>Ksps output rate | 4.5 V < V <sub>DDA SD</sub> < 5.5 V |      |       |      |     |

|                        |                                                              | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |      |     |

|                        |                                                              | Gain = 2                            | 68   |       | _    |     |

|                        |                                                              | 4.5 V < V <sub>DDA SD</sub> < 5.5 V |      |       |      |     |

|                        |                                                              | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |      |     |

|                        |                                                              | Gain = 4                            | 66   |       | _    |     |

|                        |                                                              | 4.5 V < V <sub>DDA SD</sub> < 5.5 V |      |       |      |     |

|                        |                                                              | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |       |      |     |

|                        |                                                              | Gain = 8                            | 68   | _     | _    |     |

|                        |                                                              | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |       |      |     |

|                        |                                                              | $V_{RH\_SD} = V_{DDA\_SD}$          |      |       |      |     |

|                        |                                                              | Gain = 16                           | 68   | _     | _    |     |

|                        |                                                              | 4.5 V < V <sub>DDA SD</sub> < 5.5 V |      |       |      |     |

|                        |                                                              | $V_{RH\_SD} = V_{DDA\_SD}$          |      |       |      |     |

| SFDR                   | Spurious free dynamic                                        | Any GAIN                            | 60   | _     | _    | dB  |

|                        | range                                                        | -                                   |      |       |      |     |

| $Z_{DIFF}$             | Differential input                                           | GAIN = 1                            | 1000 | 1250  | 1500 | kΩ  |

|                        | impedance <sup>10, 11</sup>                                  | GAIN = 2                            | 600  | 800   | 1000 |     |

|                        |                                                              | GAIN = 4                            | 300  | 400   | 500  |     |

|                        |                                                              | GAIN = 8                            | 200  | 250   | 300  |     |

|                        |                                                              | GAIN = 16                           | 200  | 250   | 300  |     |

## Table 17. SDADC electrical specifications (continued)

Table continues on the next page...

| Symbol                | Parameter                                         | Conditions                                     |                     | Value             |                                                 | Unit |  |

|-----------------------|---------------------------------------------------|------------------------------------------------|---------------------|-------------------|-------------------------------------------------|------|--|

| Symbol                | Falameter                                         |                                                | Min                 | Тур               | Max                                             |      |  |

| δ <sub>GROUP</sub>    | Group delay                                       | Within pass band: Tclk is $f_{ADCD_M}$ / 2     | —                   |                   |                                                 | _    |  |

|                       |                                                   | OSR = 24                                       | —                   |                   | 235.5                                           | Tcll |  |

|                       |                                                   | OSR = 28                                       | —                   |                   | 275                                             |      |  |

|                       |                                                   | OSR = 32                                       | _                   |                   | 314.5                                           |      |  |

|                       |                                                   | OSR = 36                                       | —                   |                   | 354                                             |      |  |

|                       |                                                   | OSR = 40                                       | _                   |                   | 393.5                                           |      |  |

|                       |                                                   | OSR = 44                                       | _                   |                   | 433                                             |      |  |

|                       |                                                   | OSR = 48                                       | _                   | _                 | 472.5                                           |      |  |

|                       |                                                   | OSR = 56                                       |                     | _                 | 551.5                                           |      |  |

|                       |                                                   | OSR = 64                                       | _                   |                   | 630.5                                           |      |  |

|                       |                                                   | OSR = 72                                       | _                   |                   | 709.5                                           |      |  |

|                       |                                                   | OSR = 75                                       | _                   |                   | 696                                             |      |  |

|                       |                                                   | OSR = 80                                       | _                   |                   | 788.5                                           |      |  |

|                       |                                                   | OSR = 88                                       | —                   |                   | 867.5                                           |      |  |

|                       |                                                   | OSR = 96                                       | —                   |                   | 946.5                                           | -    |  |

|                       |                                                   | OSR = 112                                      | _                   | _                 | 1104.5                                          |      |  |

|                       |                                                   | OSR = 128                                      |                     |                   | 1262.5                                          | -    |  |

|                       |                                                   | OSR = 144                                      | —                   |                   | 1420.5                                          |      |  |

|                       |                                                   | OSR = 160                                      | _                   | _                 | 1578.5                                          |      |  |

|                       |                                                   | OSR = 176                                      | —                   |                   | 1736.5                                          |      |  |

|                       |                                                   | OSR = 192                                      | —                   |                   | 1894.5                                          | -    |  |

|                       |                                                   | OSR = 224                                      | _                   |                   | 2210.5                                          |      |  |

|                       |                                                   | OSR = 256                                      | _                   |                   | 2526.5                                          | -    |  |

|                       |                                                   | Distortion within pass band                    | -0.5/               | _                 | +0.5/ f <sub>ADCD_S</sub>                       | - 1  |  |

|                       |                                                   | -                                              | f <sub>ADCD_S</sub> |                   |                                                 |      |  |

| f <sub>ніGH</sub>     | High pass filter 3 dB<br>frequency                | Enabled                                        | _                   | 10e–5*<br>fADCD_S | —                                               | -    |  |

| t <sub>STARTUP</sub>  | Startup time from power down state                | _                                              |                     | _                 | 100                                             | μs   |  |

| t <sub>LATENCY</sub>  | Latency between input data and converted          | HPF = ON                                       | -                   | —                 | δ <sub>GROUP</sub> +<br>f <sub>ADCD_S</sub>     | -    |  |

|                       | data when input mux does not change <sup>15</sup> | HPF = OFF                                      |                     | _                 | δ <sub>GROUP</sub>                              |      |  |

| t <sub>SETTLING</sub> | Settling time after mux                           | Analog inputs are muxed                        |                     |                   | 2*δ <sub>GROUP</sub> +                          | -    |  |

|                       | change                                            | HPF = ON                                       |                     |                   | 3*f <sub>ADCD_S</sub>                           |      |  |

|                       |                                                   | HPF = OFF                                      | _                   | _                 | 2∗δ <sub>GROUP</sub> +<br>2*f <sub>ADCD_S</sub> | ]    |  |

| ODRECOVERY            | Overdrive recovery time                           | After input comes within range from saturation | _                   | _                 | 2*δ <sub>GROUP</sub> +<br>f <sub>ADCD_S</sub>   | -    |  |

|                       |                                                   | HPF = ON                                       |                     |                   |                                                 |      |  |

|                       |                                                   | HPF = OFF                                      |                     |                   | 2*δ <sub>GROUP</sub>                            | 1    |  |

Table 17.

SDADC electrical specifications (continued)

Table continues on the next page ...

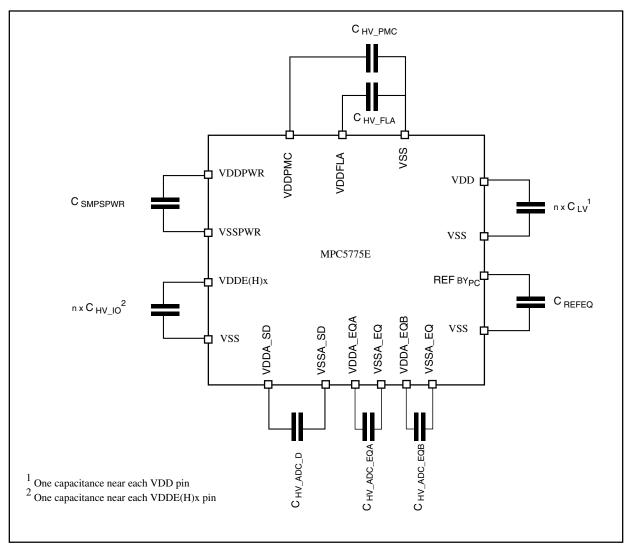

Figure 13. Recommended supply pin circuits

The following table describes the supply stability capacitances required on the device for proper operation.

| Symbol                    | Parameter                                                                       | Conditions | Value <sup>1</sup> |                    |     | Unit |

|---------------------------|---------------------------------------------------------------------------------|------------|--------------------|--------------------|-----|------|

| Symbol                    | Falanielei                                                                      | Conditions | Min                | Тур                | Max | Onit |

| C <sub>LV</sub>           | Minimum V <sub>DD</sub> external bulk capacitance <sup>2, 3</sup>               | LDO mode   |                    | _                  | _   | μF   |

|                           |                                                                                 | SMPS mode  | 22                 |                    | _   | μF   |

| C <sub>SMPSPWR</sub>      | Minimum SMPS driver supply capacitance                                          | —          | 22                 |                    | _   | μF   |

| C <sub>HV_PMC</sub>       | Minimum V <sub>DDPMC</sub> external bulk capacitance <sup>4, 5</sup>            | LDO mode   | 22                 |                    | —   | μF   |

|                           |                                                                                 | SMPS mode  | 22                 |                    | _   | μF   |

| C <sub>HV_IO</sub>        | Minimum V <sub>DDEx</sub> /V <sub>DDEHx</sub> external capacitance <sup>2</sup> | —          | —                  | 4.7 <mark>6</mark> | _   | μF   |

| C <sub>HV_FLA</sub>       | Minimum V <sub>DD_FLA</sub> external capacitance <sup>7</sup>                   | —          | 1.0                | 2.0                |     | μF   |

| C <sub>HV_ADC_EQA/B</sub> | Minimum $V_{DDA_EQA/B}$ external capacitance <sup>8</sup>                       | —          | 0.01               |                    | —   | μF   |

Table 25. Device power supply integration

Table continues on the next page...

# NOTE

In these descriptions, *star route layout* means a track split as close as possible to the power supply source. Each of the split tracks is routed individually to the intended end connection.

- 1. For both LDO mode and SMPS mode, V<sub>DDPMC</sub> and V<sub>DDPWR</sub> must be connected together (shorted) to ensure aligned voltage ramping up/down. In addition:

- For SMPS mode, a star route layout of the power track is required to minimize mutual noise. If SMPS mode is not used, the star route layout is not required. V<sub>DDPWR</sub> is the supply pin for the SMPS circuitry.

- For 3.3 V operation,  $V_{DDFLA}$  must also be star routed and shorted to  $V_{DDPWR}$ and  $V_{DDPMC}$ . This triple connection is required because 3.3 V does not guarantee correct functionality of the internal  $V_{DDFLA}$  regulator. Consequently,  $V_{DDFLA}$  is supplied externally.

- 2. V<sub>DDA\_MISC</sub>: IRC operation is required to provide the clock for chip startup.

- The V<sub>DDPMC</sub>, V<sub>DD</sub>, and V<sub>DDEH1</sub> (reset pin pad segment) supplies are monitored. They hold IRC until all of them reach operational voltage. In other words, V<sub>DDA\_MISC</sub> must reach its specified minimum operating voltage before or at the same time that all of these monitored voltages reach their respective specified minimum voltages.

- An alternative is to connect the same supply voltage to both  $V_{DDEH1}$  and  $V_{DDA\_MISC}$ . This alternative approach requires a star route layout to minimize mutual noise.

- 3. Multiple  $V_{DDEx}$  supplies can be powered up in any order.

During any time when  $V_{DD}$  is powered up but  $V_{DDEx}$  is not yet powered up: pad outputs are unpowered.

During any time when  $V_{DDEx}$  is powered up before all other supplies: all pad output buffers are tristated.

- 4. Ramp up  $V_{DDA\_EQ}$  before  $V_{DD}$ . Otherwise, a reset might occur.

- 5. When the device is powering down while using the internal SMPS regulator,  $V_{DDPMC}$  and  $V_{DDPWR}$  supplies must ramp down through the voltage range from 2.5 V to 1.5 V in less than 1 second. Slower ramp-down times might result in reduced lifetime reliability of the device.

# 3.12 Flash memory specifications

# 3.12.1 Flash memory program and erase specifications

NOTE

All timing, voltage, and current numbers specified in this section are defined for a single embedded flash memory within an SoC, and represent average currents for given supplies and operations.

Table 27 shows the estimated Program/Erase times.

| Symbol               | Characteristic <sup>1</sup>        | Typ <sup>2</sup> |                               | tory<br>nming <sup>3, 4</sup>   | F                                      | Field Update      |                     | Unit |

|----------------------|------------------------------------|------------------|-------------------------------|---------------------------------|----------------------------------------|-------------------|---------------------|------|

|                      |                                    |                  | Initial<br>Max                | Initial<br>Max, Full<br>Temp    | Typical<br>End of<br>Life <sup>5</sup> | Lifeti            | me Max <sup>6</sup> |      |

|                      |                                    |                  | 20°C ≤T <sub>A</sub><br>≤30°C | -40°C ≤T <sub>J</sub><br>≤150°C | -40°C ≤T <sub>J</sub><br>≤150°C        | ≤ 1,000<br>cycles | ≤ 250,000<br>cycles |      |

| t <sub>dwpgm</sub>   | Doubleword (64 bits) program time  | 43               | 100                           | 150                             | 55                                     | 500               | -                   | μs   |

| t <sub>ppgm</sub>    | Page (256 bits) program time       | 73               | 200                           | 300                             | 108                                    | 500               |                     | μs   |

| t <sub>qppgm</sub>   | Quad-page (1024 bits) program time | 268              | 800                           | 1,200                           | 396                                    | 2,000             |                     | μs   |

| t <sub>16kers</sub>  | 16 KB Block erase time             | 168              | 290                           | 320                             | 250                                    | 1,000             |                     | ms   |

| t <sub>16kpgm</sub>  | 16 KB Block program time           | 34               | 45                            | 50                              | 40                                     | 1,000             |                     | ms   |

| t <sub>32kers</sub>  | 32 KB Block erase time             | 217              | 360                           | 390                             | 310                                    | 1,200             |                     | ms   |

| t <sub>32kpgm</sub>  | 32 KB Block program time           | 69               | 100                           | 110                             | 90                                     | 1,200             |                     | ms   |

| t <sub>64kers</sub>  | 64 KB Block erase time             | 315              | 490                           | 590                             | 420                                    | 1,600             |                     | ms   |

| t <sub>64kpgm</sub>  | 64 KB Block program time           | 138              | 180                           | 210                             | 170                                    | 1,600             |                     | ms   |

| t <sub>256kers</sub> | 256 KB Block erase time            | 884              | 1,520                         | 2,030                           | 1,080                                  | 4,000             | —                   | ms   |

| t <sub>256kpgm</sub> | 256 KB Block program time          | 552              | 720                           | 880                             | 650                                    | 4,000             | _                   | ms   |

Table 27. Flash memory program and erase specifications

1. Program times are actual hardware programming times and do not include software overhead. Block program times assume quad-page programming.

2. Typical program and erase times represent the median performance and assume nominal supply values and operation at 25 °C. Typical program and erase times may be used for throughput calculations.

- 3. Conditions:  $\leq$  150 cycles, nominal voltage.

- 4. Plant Programing times provide guidance for timeout limits used in the factory.

- 5. Typical End of Life program and erase times represent the median performance and assume nominal supply values. Typical End of Life program and erase values may be used for throughput calculations.

- 6. Conditions:  $-40^{\circ}C \le T_J \le 150^{\circ}C$ , full spec voltage.

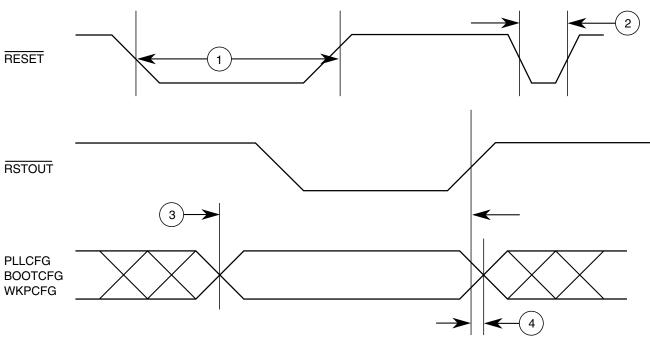

**Electrical characteristics**

Figure 17. Reset and configuration pin timing

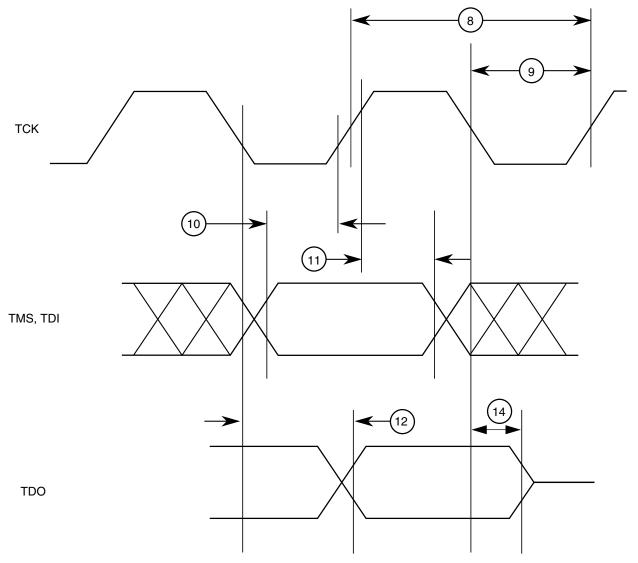

### 3.13.3 IEEE 1149.1 interface timing Table 33. JTAG pin AC electrical characteristics<sup>1</sup>

| #  | Symbol                                | Characteristic                                         | Va  | lue              | Unit |

|----|---------------------------------------|--------------------------------------------------------|-----|------------------|------|

| #  | Symbol                                | Characteristic                                         | Min | Max              | Unit |

| 1  | t <sub>JCYC</sub>                     | TCK cycle time                                         | 100 | —                | ns   |

| 2  | t <sub>JDC</sub>                      | TCK clock pulse width                                  | 40  | 60               | %    |

| 3  | t <sub>TCKRISE</sub>                  | TCK rise and fall times (40%–70%)                      | _   | 3                | ns   |

| 4  | t <sub>TMSS</sub> , t <sub>TDIS</sub> | TMS, TDI data setup time                               | 5   | _                | ns   |

| 5  | t <sub>TMSH</sub> , t <sub>TDIH</sub> | TMS, TDI data hold time                                | 5   | _                | ns   |

| 6  | t <sub>TDOV</sub>                     | TCK low to TDO data valid                              | _   | 16 <sup>2</sup>  | ns   |

| 7  | t <sub>TDOI</sub>                     | TCK low to TDO data invalid                            | 0   | _                | ns   |

| 8  | t <sub>TDOHZ</sub>                    | TCK low to TDO high impedance                          | _   | 15               | ns   |

| 9  | t <sub>JCMPPW</sub>                   | JCOMP assertion time                                   | 100 | _                | ns   |

| 10 | t <sub>JCMPS</sub>                    | JCOMP setup time to TCK low                            | 40  | _                | ns   |

| 11 | t <sub>BSDV</sub>                     | TCK falling edge to output valid                       | _   | 600 <sup>3</sup> | ns   |

| 12 | t <sub>BSDVZ</sub>                    | TCK falling edge to output valid out of high impedance | _   | 600              | ns   |

| 13 | t <sub>BSDHZ</sub>                    | TCK falling edge to output high impedance              | _   | 600              | ns   |

| 14 | t <sub>BSDST</sub>                    | Boundary scan input valid to TCK rising edge           | 15  | —                | ns   |

| 15 | t <sub>BSDHT</sub>                    | TCK rising edge to boundary scan input invalid         | 15  | —                | ns   |

1. These specifications apply to JTAG boundary scan only. See Table 34 for functional specifications.

- 2. Timing includes TCK pad delay, clock tree delay, logic delay and TDO output pad delay.

- 3. Applies to all pins, limited by pad slew rate. Refer to I/O delay and transition specification and add 20 ns for JTAG delay.

| Table 34. | Nexus c | debug | port ti | ming <sup>1</sup> ( | (continued) |

|-----------|---------|-------|---------|---------------------|-------------|

|-----------|---------|-------|---------|---------------------|-------------|

| Spec | Characteristic                                                               | Symbol                                  | Min             | Max | Unit |

|------|------------------------------------------------------------------------------|-----------------------------------------|-----------------|-----|------|

| 8    | Absolute minimum TCK cycle time <sup>4</sup> (TDO sampled on posedge of TCK) | t <sub>TCYC</sub>                       | 40 <sup>5</sup> | _   | ns   |

|      | Absolute minimum TCK cycle time <sup>4</sup> (TDO sampled on negedge of TCK) |                                         | 20 <sup>5</sup> | _   |      |

| 9    | TCK Duty Cycle                                                               | t <sub>TDC</sub>                        | 40              | 60  | %    |

| 10   | TDI, TMS Data Setup Time <sup>6</sup>                                        | t <sub>NTDIS</sub> , t <sub>NTMSS</sub> | 8               | _   | ns   |

| 11   | TDI, TMS Data Hold Time <sup>6</sup>                                         | T <sub>NTDIH</sub> , t <sub>NTMSH</sub> | 5               | _   | ns   |

| 12   | TCK Low to TDO Data Valid <sup>6</sup>                                       | t <sub>NTDOV</sub>                      | 0               | 18  | ns   |

| 13   | RDY Valid to MCKO <sup>7</sup>                                               | _                                       | —               | —   | _    |

| 14   | TDO hold time after TCLK low <sup>6</sup>                                    | t <sub>NTDOH</sub>                      | 1               | —   | ns   |

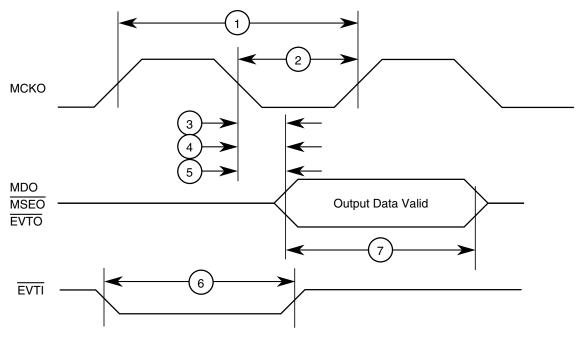

1. All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal. Nexus timing specified at  $V_{DD}$  = 1.08 V to 1.32 V,  $V_{DDE}$  = 3.0 V to 3.6 V,  $V_{DD33}$  and  $V_{DDSYN}$  = 3.0 V to 3.6 V,  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 30 pF with DSC = 0b10.

- 2. MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

- 3. This is a functionally allowable feature. However, it may be limited by the maximum frequency specified by the absolute minimum TCK period specification.

- 4. This value is TDO propagation time plus 2 ns setup time to sampling edge.

- 5. This may require a maximum clock speed that is less than the maximum functional capability of the design depending on the actual system frequency being used.

- 6. Applies to TMS pin timing for the bit frame when using the 1149.7 advanced protocol.

- 7. The RDY pin timing is asynchronous to MCKO. The timing is guaranteed by design to function correctly.

Figure 22. Nexus timings

**Electrical characteristics**

Figure 23. Nexus TCK, TDI, TMS, TDO Timing

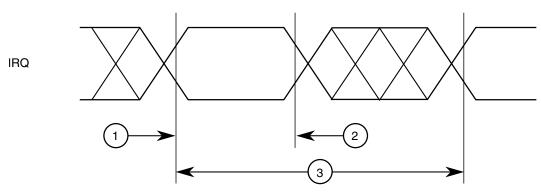

# 3.13.5 External interrupt timing (IRQ/NMI pin) Table 35. External Interrupt timing<sup>1</sup>

| Spec | Characteristic                         | Symbol            | Min | Max | Unit                          |

|------|----------------------------------------|-------------------|-----|-----|-------------------------------|

| 1    | IRQ/NMI Pulse Width Low                | t <sub>IPWL</sub> | 3   | —   | t <sub>cyc</sub> <sup>2</sup> |

| 2    | IRQ/NMI Pulse Width High               | t <sub>IPWH</sub> | 3   | _   | t <sub>cyc</sub> <sup>2</sup> |

| 3    | IRQ/NMI Edge to Edge Time <sup>3</sup> | t <sub>ICYC</sub> | 6   | —   | t <sub>cyc</sub> <sup>2</sup> |

1. IRQ/NMI timing specified at  $V_{DD}$  = 1.08 V to 1.32 V,  $V_{DDEH}$  = 3.0 V to 5.5 V,  $T_A$  =  $T_L$  to  $T_H$ .

2. For further information on  $t_{cyc}$ , see Table 3.

3. Applies when IRQ/NMI pins are configured for rising edge or falling edge events, but not both.

Figure 24. External interrupt timing

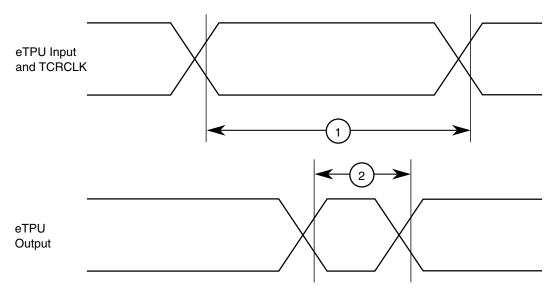

### 3.13.6 eTPU timing Table 36. eTPU timing<sup>1</sup>

| Spec | Characteristic                  | Symbol            | Min            | Max | Unit                               |

|------|---------------------------------|-------------------|----------------|-----|------------------------------------|

| 1    | eTPU Input Channel Pulse Width  | t <sub>ICPW</sub> | 4              | —   | t <sub>CYC_ETPU</sub> <sup>2</sup> |

| 2    | eTPU Output Channel Pulse Width | t <sub>OCPW</sub> | 1 <sup>3</sup> | —   | t <sub>CYC_ETPU</sub> <sup>2</sup> |

- 1. eTPU timing specified at  $V_{DD}$  = 1.08 V to 1.32 V,  $V_{DDEH}$  = 3.0 V to 5.5 V,  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 200 pF with SRC = 0b00.

- 2. For further information on  $_{tCYC\_ETPU}$ , see Table 3.

- 3. This specification does not include the rise and fall times. When calculating the minimum eTPU pulse width, include the rise and fall times defined in the slew rate control fields (SRC) of the pad configuration registers (PCR).

Figure 25. eTPU timing

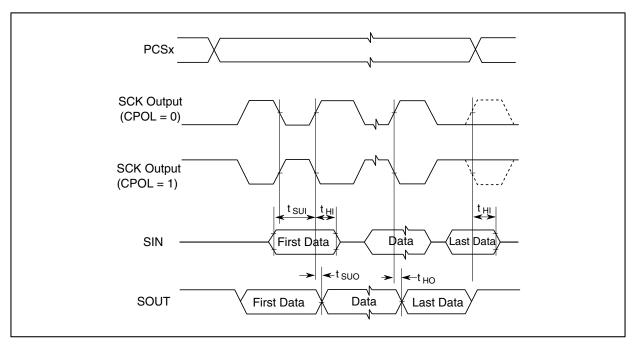

### Table 40. DSPI CMOS master modified timing (full duplex and output only) – MTFE = 1, CPHA = 0 or $1^1$ (continued)

| #  | Cumhal             | Oberesteristic         | Condition              | 1 <sup>2</sup>         | Value                                 | 3                                    | Unit |

|----|--------------------|------------------------|------------------------|------------------------|---------------------------------------|--------------------------------------|------|

| #  | Symbol             | Characteristic -       | Pad drive <sup>4</sup> | Load (C <sub>L</sub> ) | Min                                   | Мах                                  |      |

| 7  | t <sub>SUI</sub>   | SIN setup time to      | PCR[SRC]=11b           | 25 pF                  | $29 - (P^{11} \times t_{SYS}^{, 6})$  |                                      | ns   |

|    |                    | SCK                    | PCR[SRC]=10b           | 50 pF                  | $31 - (P^{11} \times t_{SYS}, 6)$     |                                      |      |

|    |                    | CPHA = 0 <sup>10</sup> | PCR[SRC]=01b           | 50 pF                  | $62 - (P^{11} \times t_{SYS}, 6)$     |                                      | 1    |

|    |                    | SIN setup time to      | PCR[SRC]=11b           | 25 pF                  | 29.0                                  | —                                    | ns   |

|    |                    | SCK                    | PCR[SRC]=10b           | 50 pF                  | 31.0                                  | _                                    | 1    |

|    |                    | CPHA = 1 <sup>10</sup> | PCR[SRC]=01b           | 50 pF                  | 62.0                                  |                                      | 1    |

|    |                    | <u> </u>               | SIN ho                 | ld time                |                                       |                                      |      |