#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                 |

|----------------------------|----------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                          |

| Core Size                  | 32-Bit Single-Core                                       |

| Speed                      | 40MHz                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT |

| Number of I/O              | 30                                                       |

| Program Memory Size        | 64KB (64K x 8)                                           |

| Program Memory Type        | FLASH                                                    |

| EEPROM Size                | -                                                        |

| RAM Size                   | 4K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 5.5V                                              |

| Data Converters            | A/D 12x12b                                               |

| Oscillator Type            | Internal                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                       |

| Mounting Type              | Surface Mount                                            |

| Package / Case             | 32-LQFP                                                  |

| Supplier Device Package    | 32-LQFP (7x7)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z32f06423ake  |

|                            |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## FY[]gh¥fg<sup>·</sup>

The base address of the PCU block is 0x4000\_1000.

Register access is globally masked by the PORTEN register. To change register values except the PORTEN register, enable port access in advance.

| B5 A 9 <sup>·</sup> | 65G9 <sup>-</sup> 588F9GG <sup>-</sup> |

|---------------------|----------------------------------------|

| PCA                 | 0x4000_1000                            |

| PCB                 | 0x4000_1100                            |

| PCC                 | 0x4000_1200                            |

| PCD                 | 0x4000_1300                            |

HUV`Y`) !&`6 UgY`5 XXfYgg`cZ9 UW `Dcfh7 cblfc``

| B5 A 9 <sup>·</sup> | C::G9H | HMD9 <sup>·</sup> | 89G7F=DH=CB                              |

|---------------------|--------|-------------------|------------------------------------------|

| PC <i>n.</i> MR     | 0x00   | RW                | Port <i>n</i> pin mux select register    |

| PC <i>n.</i> CR     | 0x04   | RW                | Port n pin control register              |

| PC <i>n.</i> PCR    | 0x08   | RW                | Port n internal pull-up control register |

| PCn.DER             | 0x0C   | RW                | Port n debounce control register         |

| PCn.IER             | 0x10   | RW                | Port <i>n</i> interrupt enable register  |

| PCn.ISR             | 0x14   | RW                | Port <i>n</i> interrupt status register  |

| PCn.ICR             | 0x18   | RW                | Port <i>n</i> interrupt control register |

|                     | 0x1C   |                   | Reserved                                 |

|                     |        |                   |                                          |

| PORTEN              | 0x1FF0 | RW                | Port Access enable                       |

## HUV`Y`) !' 'D7 I 'F Y[ ]ghYf A Ud'

## D7 7 '7 F DC F H 7 D]b 7 cbfc F Y[ ]ghYf

This register is used for input or output control of each port pin. Each pin can be configured as input pin, output pin, or open-drain pin.

| PCC.CR=0x4000_12 | 04 |

|------------------|----|

|------------------|----|

| 3 | 1  | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21         | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7 | 6  | 5 | 4 | 3 | 2 | 1  | 0 |

|---|----|----|----|----|----|----|----|----|----|----|------------|----|----|----|----|----|----|----|----|----|----|----|---|----|---|----|---|---|---|---|----|---|

|   | P1 | .5 | P  | 14 | P1 | 13 | P  | 12 | P  | 11 | <b>P</b> 1 | LO | F  | 9  | P  | 8  | Р  | 7  | F  | 96 | F  | 5  | F | 24 | F | 3  | F | 2 | Р | 1 | Ρ  | 0 |

|   | 11 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1          | 0  | 1  | 11 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | .1 | 1 | 11 | 1 | .1 | 1 | 1 | 1 | 0 | 1  | 0 |

|   | RV | N  | R  | w  | R  | w  | R  | N  | R  | w  | R          | N  | R  | w  | R  | w  | R  | w  | R  | w  | R  | w  | R | w  | R | w  | R | w | R | N | R۱ | N |

| Pn | Port | control           |

|----|------|-------------------|

|    | 00   | Push-pull output  |

|    | 01   | Open-drain output |

|    | 10   | Input             |

|    | 11   | Analog            |

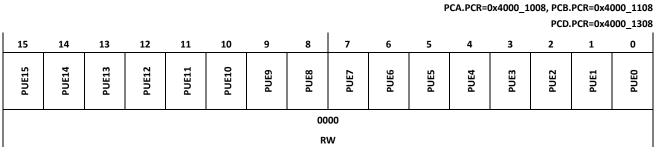

### D7 b'D7 F' DCFH'b'Di``!i d'FYg]ghcf'7 cbhfc``FY[]ghYf'f91 WYdh'Zcf`` D7 7 'D7 FŁ'

Every pin in the port has on-chip pull-up resistors which can be configured by the PCn.PCR registers.

| n | PUEn | Port pull-up control       |

|---|------|----------------------------|

|   |      | 0 Disable pull-up resistor |

|   |      | 1 Enable pull-up resister  |

### : A '8 = F HM' : `Uq\'

## :`Ug\`A Ya cfmi8]fhmi6]hF Y[]ghYf`

FMDRTY is the internal Flash memory dirty bit clear register.

|    |    |    |    |    |    |    |    |    |    |    |      |    |    |    |      |       |     |      |      |      |      |        |       |        |       |      | FN   | 1.DR | =0x4 | 000_ | 011 |

|----|----|----|----|----|----|----|----|----|----|----|------|----|----|----|------|-------|-----|------|------|------|------|--------|-------|--------|-------|------|------|------|------|------|-----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20   | 19 | 18 | 17 | 16   | 15    | 14  | 13   | 12   | 11   | 10   | 9      | 8     | 7      | 6     | 5    | 4    | 3    | 2    | 1    | 0   |

|    |    |    |    |    |    |    |    |    |    |    |      |    |    |    | FDI  | RTY   |     |      |      |      |      |        |       |        |       |      |      |      |      |      |     |

|    |    |    |    |    |    |    |    |    |    |    |      |    |    | 0  | 0000 | 0 00  | 00  |      |      |      |      |        |       |        |       |      |      |      |      |      |     |

|    |    |    |    |    |    |    |    |    |    |    |      |    |    | •  |      | /0    |     |      |      |      |      |        |       |        |       |      |      |      |      |      |     |

|    |    |    |    |    |    |    |    |    |    |    |      |    |    |    |      |       |     |      |      |      |      |        |       |        |       |      |      |      |      |      |     |

|    |    |    |    |    |    |    |    | 3  | 1  | F  | DIRT | Y  |    |    | V    | Vrite | any | valı | ue h | ere, | cach | ie lir | ne fi | ll fla | g wil | l be | clea | red  |      |      |     |

|    |    |    |    |    |    |    |    | 0  |    |    |      |    |    |    |      |       |     |      |      |      |      |        |       |        |       |      |      |      |      |      |     |

### : A 'H=7 ?:`Ug\ `A Ya cfmiH]W\_`H]a Yf `F Y[ ]ghYf`

This is an internal Flash memory tick timer register.

FM.TICK=0x4000\_011C

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23     | 22 | 21 | 20   | 19 | 18 | 17 | 16 | 15  | 14  | 13   | 12   | 11   | 10 | 9   | 8    | 7 | 6 | 5 | 4 | 3 | 2              | 1 | 0 |

|----|----|----|----|----|----|----|----|--------|----|----|------|----|----|----|----|-----|-----|------|------|------|----|-----|------|---|---|---|---|---|----------------|---|---|

|    |    |    |    |    |    |    |    |        |    |    |      |    |    |    |    |     |     |      |      |      |    | FT  | іск  |   |   |   |   |   |                |   |   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0  | 0  | 0    | 0  | 0  |    |    |     |     |      |      |      |    | 0x0 | 0000 |   |   |   |   |   |                |   |   |

|    |    |    |    |    |    |    |    |        |    |    |      |    |    |    |    |     |     |      |      |      |    | R   | w    |   |   |   |   |   |                |   |   |

|    |    |    |    |    |    |    |    | 1<br>0 | -  |    | FTIC | К  |    |    | F  | CLK | clo | ck w | hile | Flas |    | GΜ  |      |   |   |   |   |   | /IR ru<br>wher |   |   |

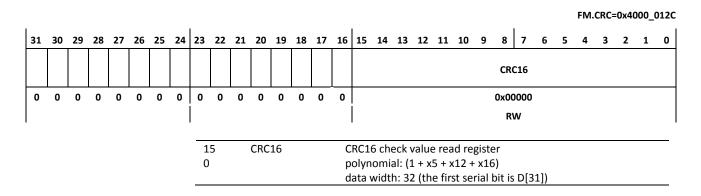

## : A '7 F7 : `Ug\ '7 F7 '7 \ YW\_ FY[ ]ghYf '

FMCRC is the CRC value resulting from read accesses on internal Flash memory.

## :ibWijcbU`8YgW]dhjcb`

The Flash memory controller is an internal Flash memory interface controller which primarily controls the programming of Flash memory and preparing read data to be requested from the bus.

## :`Ug\'Cf[Ub]nUhjcb'

The 64 Kbytes code Flash memory consists of 512 pages which have a uniform 128 byte page size. The Flash controller allows reading or writing of Flash memory data. This memory is located at 0x0000\_0000 address on the system memory map. The system expects the code to be executed on boot to be located at address 0x0000\_0000. There is no ability to change this address on the Cortex M0.

## :`Ug\`FYUX`CdYfUhjcb`

The Flash data read operation is requested from the bus. The Flash controller responds to the request. The wait time should be correctly defined because the bus speed is usually faster than the Flash data access time. The Flash data access time is 20 Mhz on the Z32F0642 device.

## :`Ug\`Dfc[fUa`CdYfUh]cb`

Erase and Program access of Flash memory is available only in Flash mode. Once in Flash mode, Flash cannot be read normally; therefore, self-programming is not supported. The Flash program erase operations must be performed by the execution program in SRAM memory.

For every erase operation, a pre-program operation MUST be performed first, to prevent over-erase of Flash memory cells. Programming and erase operations use the 40 Mhz internal oscillator, so the HSI internal oscillator must be enabled and selected.

Erase operations can be either a page (32 words) or the entire chip. Programming can be a single word or a page.

## :`Ug\'9fUgY'UbX'Dfc[fUa'9|Uad`Yg"

To erase a sector:

- A. Flash mode enable to write FM.CR register (write 0x5A and then write 0xA5 into FMMR)

- B. Set PMODE bit first

- C. Wait until IDLE bit of FM.MR register becomes "1"

- D. Set target Page address in FM.AR

- E. Set FM.TMR register to be 0.5ms operation (based on 40MHz Int OSC clock)

- F. set PPGM, WE, PGM bits of FMCR

- G. Wait until IDLE bit of FM.MR register become "1" after pre-program

- H. Clear WE, PGM bits of FMCR

- I. Wait 5us

- J. Clear PPGM bit of FM.CR

- K. Wait 30us before returning to normal operation

- L. Clear PMODE bit of FM.CR

- M. Clear Flash mode (write 0x00 into FM.MR)

- N. Insert at least 2 NOPs, and return to normal operation

- O. Flash mode enable to write FM.CR register (write 0x5A and then write 0xA5 into FM.MR)

- P. Set PMODE bit first

### K8H7CB' KUHWX

KUHWYXc['H]aYf'7cbhfc``FY[]ghYf'

The WDT module should be configured properly before running. When the target purpose is defined, WDT can be configured in the WDTCON register.

|      |    |    |    |    |    |   |     |       |       |   |       |       | WDT.     | CON=0x40 | 00_0208 |

|------|----|----|----|----|----|---|-----|-------|-------|---|-------|-------|----------|----------|---------|

| 15   | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7     | 6     | 5 | 4     | 3     | 2        | 1        | 0       |

| WDBG |    |    |    |    |    |   | WUF | WDTIE | WDTRE |   | WDTEN | CKSEL |          | WPRS     |         |

| 1    | 0  | 0  | 0  | 0  | 0  | 0 | 0   | 0     | 1     | 0 | 1     | 1     | <u>.</u> | 100      |         |

| RW   |    |    |    |    |    |   | RW  | RW    | RW    |   | RW    | RW    |          | RW       |         |

| 15 | WDBG      | Watchdog operation control in debug mode          |

|----|-----------|---------------------------------------------------|

|    |           | 0 Watchdog counter running when debug mode        |

|    |           | 1 Watchdog counter stopped when debug mode        |

| 8  | WUF       | Watchdog timer underflow flag                     |

|    |           | 0 No underflow                                    |

|    |           | 1 Underflow is pending                            |

| 7  | WDTIE     | Watchdog timer counter underflow interrupt enable |

|    |           | 0 Disable interrupt                               |

|    |           | 1 Enable interrupt                                |

| 6  | WDTRE     | Watchdog timer counter underflow interrupt enable |

|    |           | 0 Disable reset                                   |

|    |           | 1 Enable reset                                    |

| 4  | WDTEN     | Watchdog Counter enable                           |

|    |           | 0 Watch dog counter disabled                      |

|    |           | 1 Watch dog counter enabled                       |

| 3  | CKSEL     | WDTCLKIN clock source select                      |

|    |           | 0 PCLK                                            |

|    |           | 1 External clock                                  |

| 2  | WPRS[2:0] | Counter clock prescaler                           |

| 0  |           | WDTCLK = WDTCLKIN/WPRS                            |

|    |           | 000 WDTCLKIN                                      |

|    |           | 001 WDTCLKIN / 4                                  |

|    |           | 010 WDTCLKIN / 8                                  |

|    |           | 011 WDTCLKIN / 16                                 |

|    |           | 100 WDTCLKIN / 32                                 |

|    |           | 101 WDTCLKIN / 64                                 |

|    |           | 110 WDTCLKIN / 128                                |

|    |           | 111 WDTCLKIN / 256                                |

## :ibWijcbU'8YgWjdhjcb

The watchdog timer count can be enabled by setting WDTEN (WDT.CON[4]) to '1'. As the watchdog timer is enabled, the down counter starts counting from the Load Value. If WDTRE (WDT.CON[6]) is set as '1', WDT reset will be asserted when the WDT counter value reaches '0' (underflow event) from the WDT.LR value. Before the WDT counter goes down to 0, the software can write a certain value to the WDT.LR register to reload the WDT counter.

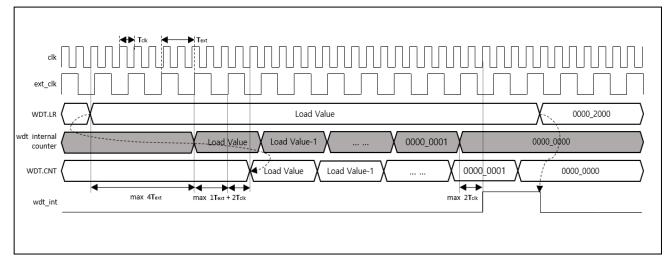

## Hja jb[ '8 jU[ fUa '

### :][ifY`-!&`H]a]b[`8]U[fUa`]b`=bhYffidh`AcXY`CdYfUh]cb`k \Yb`K 8H`7`cW\_`]g`9IhYfbU`7`cW\_`

In WDT interrupt mode, after WDT underflow occurs, a certain count value is reloaded to prevent the next WDT interrupt in a short time period and this reloading action can only be activated when the watchdog timer counter is set to be in Interrupt mode (set WDTIE of WDT.CON). It takes up to 5 cycles from the Load value to the CNT value. The WDT interrupt signal and CNT value data might be delayed by a maximum of 2 system bus clocks in synchronous logic.

### Df YgWU Y'HUV'Y'

The WDT includes a 32-bit down counter with programmable pre-scaler to define different time-out intervals.

The clock sources of the watchdog timer include the peripheral clock (PCLK) or one of five external clock sources. An external clock source can be enabled by setting CKSEL (WDT.CON[3]) to '1'. The external clock source is chosen in the MCCR3 register of the SCU (system control unit) block.

To make the WDT counter base clock, users can control 3-bit pre-scaler WPRS [2:0] in the WDT.CON register and the maximum pre-scaled value is "clock source frequency/256". The pre-scaled WDT counter clock frequency values are listed in following table.

#### Selectable clock source (40 kHz ~ 16 MHz) and the time out interval when 1 count Time out period = {(Load Value) \* (1/pre-scaled WDT counter clock frequency) + max 5Text} + max 4Tclk

\*Time out period (time out period from load Value to interrupt set '1')

## :ibWfjcbU`8YgWfjdhjcb`

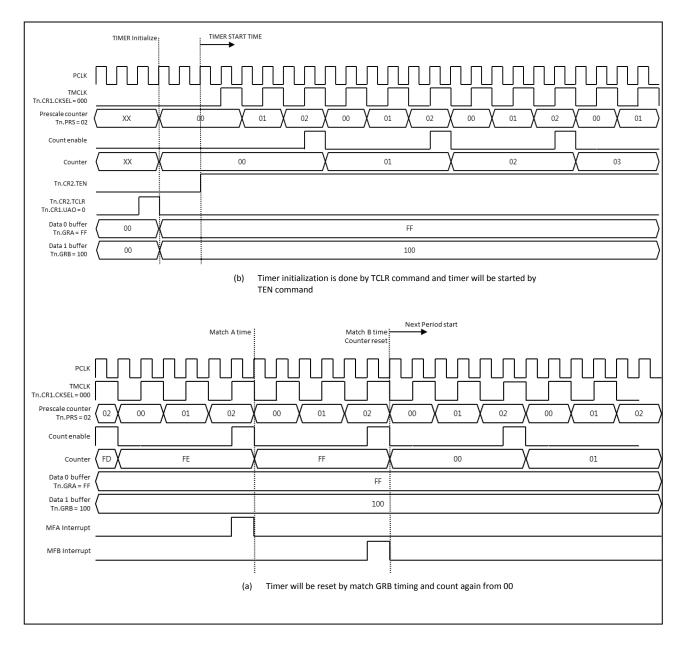

## Hja Yf 6 UgjWCdYfUhjcb

TMCLK in Figure 10-2 is a reference clock for operation of the timer. This clock is divided by the prescaler setting for the counting clock to work. Figure 10-2 shows the starting point of the counter and the ending of the period point of the counter in normal periodic mode.

### :][ifY`%\$!&`6Ug]WGHUfhUbX`AUHW\_`CdYfUh]cb`

The period of timer count can be calculated using the following equation:

The period = TMCLK Period \* Tn.GRB value. Match A interrupt time = TMCLK Period \* Tn.GRA value.

## FY[]ghYfg<sup>-</sup>

The base address of UART is 0x4000\_8000 and the register map is described in Table 12-2 and Table 12-3.

#### HUV`Y`%&!&`6 UgY`5 XXfYgg`cZ9 UW(`Dcfhi

| B5 A 9 <sup>-</sup> | 6 5 G9 5 8 8 F 9 GG |

|---------------------|---------------------|

| U0                  | 0x4000_8000         |

| U1                  | 0x4000_8100         |

#### HUV`Y`%&!' `I 5 F H`F Y[ ]ghYf`A Ud`

| B5 A 9 <sup>-</sup> | C::G9H | HMD9 <sup>°</sup> | 89G7F=DH=CB                        | F9G9H <sup>°</sup><br>J5@29 <sup>°</sup> |

|---------------------|--------|-------------------|------------------------------------|------------------------------------------|

| Un.RBR              | 0x00   | R                 | Receive Data Buffer Register       | 0x00                                     |

| Un.THR              | 0x00   | W                 | Transmit Data Hold Register        | 0x00                                     |

| Un.IER              | 0x04   | RW                | Interrupt Enable Register          | 0x00                                     |

| Un.IIR              | 0x08   | R                 | Interrupt ID Register              | 0x01                                     |

| -                   | 0x08   | -                 | Reserved                           | -                                        |

| Un.LCR              | 0x0C   | RW                | Line Control Register              | 0x00                                     |

| Un.DCR              | 0x10   | RW                | Data Control Register              |                                          |

| Un.LSR              | 0x14   | R                 | Line Status Register               | 0x00                                     |

| -                   | 0x18   | -                 | Reserved                           | -                                        |

| Un.SCR              | 0x1C   | RW                | Scratch Pad Register               | 0x00                                     |

| Un.BDR              | 0x20   | RW                | Baud rate Divisor Latch Register   | 0x0000                                   |

| Un.BFR              | 0x24   | RW                | Baud rate Fractional Counter Value | 0x00                                     |

| Un.IDTR             | 0x30   | RW                | Inter-frame Delay Time Register    | 0x80                                     |

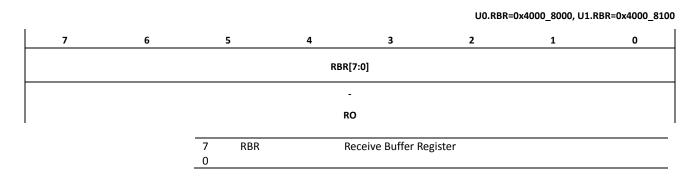

## I b'F6F'FYWY]jY'6iZ2Yf'FY[]ghYf'

The UART Receive Buffer register is an 8-bit read-only register. Received data is read out from this register. The maximum length of data is 8 bits. The last data received will be maintained in this register until a new byte is received.

## I b'6: F`6Ui X`FUhY`: fUWN]cb'7ci bhYf`FY[]ghYf`

The Baud Rate Fraction Counter register is an 8-bit register.

|   |   |      |       |               | U0.BFR                                | =0x4000_8024, U1 | .BFR=0x4000_812 |

|---|---|------|-------|---------------|---------------------------------------|------------------|-----------------|

| 7 | 6 | 5    | 4     | 3             | 2                                     | 1                | 0               |

|   |   |      | BFR   |               |                                       |                  |                 |

|   |   |      | 0x00  |               |                                       |                  |                 |

|   |   |      | RW    |               |                                       |                  |                 |

|   |   | 7 BF | R Fra | ctions counte | r value.                              |                  |                 |

|   |   | 0    | 0     | Fraction co   | ounter is disabled                    |                  |                 |

|   |   |      | N     |               | ounter enabled. F<br>Fraction counter |                  |                 |

#### HUV`Y`%&!+`9|Uad`Y`cZ6UiX`FUhY'7U`Wi`Uhjcb`

| I 5 F H <sub>₩c Ψ</sub> <sup>·</sup> 1(\$ <sup>•</sup> A < n <sup>·</sup> |                        |        |            |  |  |  |  |  |  |

|---------------------------------------------------------------------------|------------------------|--------|------------|--|--|--|--|--|--|

| 6 UiX 'fUHY'                                                              | 8 ]j ]XYf <sup>.</sup> | : 7 BH | 9ffcf`fl 분 |  |  |  |  |  |  |

| 1200                                                                      | 2083                   | 85     | 0.00%      |  |  |  |  |  |  |

| 2400                                                                      | 1041                   | 170    | 0.00%      |  |  |  |  |  |  |

| 4800                                                                      | 520                    | 213    | 0.00%      |  |  |  |  |  |  |

| 9600                                                                      | 260                    | 106    | 0.00%      |  |  |  |  |  |  |

| 19200                                                                     | 130                    | 53     | 0.00%      |  |  |  |  |  |  |

| 38400                                                                     | 65                     | 262    | 0.00%      |  |  |  |  |  |  |

| 57600                                                                     | 43                     | 103    | 0.00%      |  |  |  |  |  |  |

| 115200                                                                    | 21                     | 179    | 0.01%      |  |  |  |  |  |  |

FCNT = Float \* 256

The FCNT value is calculated using the equation above. For example, when the target baud rate is 4800 bps and UART<sub>clock</sub> is 40MHz, the BDR value is 520.8333. The integer number 520 should be the BDR value and the floating number 0.8333 will result in the FCNT value of 213, as shown below:

FCNT = 0.8333 \* 256 = 213.3333, so the FCNT value is 213.

The 8-bit fractional counter will count up by FCNT value every (baud rate)/16 periods and when the fractional counter overflows, the divisor value increments by 1. Therefore, this period will be compensated. In the next period, the divisor value will return to the original set value.

## D]b<sup>·</sup>8 Yg**W**]dh**]**cb<sup>·</sup>

### HUV`Y`%(!%=<sup>\$</sup>7`+bhYfZJWY`91 hYfbU`D]bg`

| D=B`B5A9` | HMD9 | 89G7F=DH=CB                                                 |

|-----------|------|-------------------------------------------------------------|

| SCL       | I/O  | I <sup>2</sup> C channel Serial clock bus line (open-drain) |

| SDA       | I/O  | I <sup>2</sup> C channel Serial data bus line (open-drain)  |

## FY[]ghYfg<sup>·</sup>

The base address of  $I^2C$  is 0x4000\_A000. The register map is described in Table 14-2 and Table 14-3.

### HUV`Y`%(!&`=<sup>\$</sup>7 `=bhYfZUWY`6 UgY`5 XXfYgg`

| B5A9 <sup>.</sup> | 6 5 G9 5 8 8 F 9 GG |

|-------------------|---------------------|

| l <sup>2</sup> C  | 0x4000 A000         |

#### HUV`Y`%{!' <sup>\*</sup>≜7 <sup>•</sup>F Y[ ]ghYf <sup>•</sup>A Ud<sup>•</sup>

| B5 A 9 <sup>.</sup> | C::G9H | HMD9 <sup>°</sup> | 89G7F=DH=CB                                 | F9G9H <sup>-</sup><br>J5@9 <sup>-</sup> |

|---------------------|--------|-------------------|---------------------------------------------|-----------------------------------------|

| IC.DR               | 0x00   | RW                | I <sup>2</sup> C Data Register              | 0xFF                                    |

| IC.SR               | 0x08   | R, RW             | I <sup>2</sup> C Status Register            | 0x00                                    |

| IC.SAR              | 0x0C   | RW                | I <sup>2</sup> C Slave Address Register     | 0x00                                    |

| IC.CR               | 0x14   | RW                | I <sup>2</sup> C Control Register           | 0x00                                    |

| IC.SCLL             | 0x18   | RW                | I <sup>2</sup> C SCL LOW duration Register  | 0xFFFF                                  |

| IC.SCLH             | 0x1C   | RW                | I <sup>2</sup> C SCL HIGH duration Register | 0xFFFF                                  |

| IC.SDH              | 0x20   | RW                | I <sup>2</sup> C SDA Hold Register          | 0x7F                                    |

# %) "Achcf Di`gY K ]Xh `AcXi`Uhcf fADK AŁ

## Cj Yfj ]Yk <sup>·</sup>

Motor Pulse Width Modulator (MPWM) is a programmable motor controller which is optimized for 3-phase AC and DC motor control applications. It can be used in many other applications that require timing, counting, and comparison features.

MPWM includes 3 channels, each of which controls a pair of outputs that can control a motor.

- 16-bit counter

- 6-channel outputs for motor control

- Dead-time support

- Protection event and over voltage event handling

- 6 ADC trigger outputs

- Interval interrupt mode (period interrupt only)

- Up-down count mode

The MPWM clock source which is MPWM counter clock source will be provided from the SCU block. The MPWM resolution and period will be defined by this MPWM clock configuration. The default MPWM clock is the same as the RINGOSC clock. Prior to enabling the MPWM module, proper MPWM clock selection is required.

## FY[]gh¥fg<sup>·</sup>

The base address of MPWM is shown in Table 15-2.

#### HUV`Y'%) !& A DK A '6 UgY'5 XXf Ygg'

| B5A9 <sup>.</sup> | 6 5 G9 5 8 8 F 9 GG |

|-------------------|---------------------|

| MPWM              | 0x4000 4000         |

Table 15-3 shows the register memory map.

#### HUV`Y'%) !' `A DK A 'F Y[ ]ghYf `A Ud`

| B5 A 9 <sup>-</sup> | C::G9H | HMD9 <sup>°</sup> | 89G7F=DH=CB                        | F9G9H'J5@9'  |

|---------------------|--------|-------------------|------------------------------------|--------------|

| MP.MR               | 0x0000 | RW                | MPWM Mode register                 | 0x0000_0000  |

| MP.OLR              | 0x0004 | RW                | MPWM Output Level register         | 0x0000_0000  |

| MP.FOR              | 0x0008 | RW                | MPWM Force Output register         | 0x0000_0000  |

| MP.PRD              | 0x000C | RW                | MPWM Period register               | 0x0000_0002  |

| MP.DUH              | 0x0010 | RW                | MPWM Duty UH register              | 0x0000_0001  |

| MP.DVH              | 0x0014 | RW                | MPWM Duty VH register              | 0x0000_0001  |

| MP.DWH              | 0x0018 | RW                | MPWM Duty WH register              | 0x0000_0001  |

| MP.DUL              | 0x001C | RW                | MPWM Duty UL register              | 0x0000_0001  |

| MP.DVL              | 0x0020 | RW                | MPWM Duty VL register              | 0x0000_0001  |

| MP.DWL              | 0x0024 | RW                | MPWM Duty WL register              | 0x0000_0001  |

| MP.CR1              | 0x0028 | RW                | MPWM Control register 1            | 0x0000_0000  |

| MP.CR2              | 0x002C | RW                | MPWM Control register 2            | 0x0000_0000  |

| MP.SR               | 0x0030 | R                 | MPWM Status register               | 0x0000_0000  |

| MP.IER              | 0x0034 | RW                | MPWM Interrupt Enable              | 0x0000_0000  |

| MP.CNT              | 0x0038 | R                 | MPWM counter register              | 0x0000_0001  |

| MP.DTR              | 0x003C | RW                | MPWM dead time control             | 0x0000_0000  |

| MP.PCR0             | 0x0040 | RW                | MPWM protection 0 control register | 0x0000_0000  |

| MP.PSR0             | 0x0044 | RW                | MPWM protection 0 status register  | 0x0000_0080  |

| MP.PCR1             | 0x0048 | RW                | MPWM protection 1 control register | 0x0000_0000  |

| MP.PSR1             | 0x004C | RW                | MPWM protection 1 status register  | 0x0000_0000  |

| -                   | 0x0054 | -                 | Reserved                           | -            |

| MP.ATR1             | 0x0058 | RW                | MPWM ADC Trigger reg1              | 0x0000_0000  |

| MP.ATR2             | 0x005C | RW                | MPWM ADC Trigger reg2              | 0x0000_0000  |

| MP.ATR3             | 0x0060 | RW                | MPWM ADC Trigger reg3              | 0x0000_0000  |

| MP.ATR4             | 0x0064 | RW                | MPWM ADC Trigger reg4              | 0x0000_0000  |

| MP.ATR5             | 0x0068 | RW                | MPWM ADC Trigger reg5              | 0x0000_00000 |

| MP.ATR6             | 0x006C | RW                | MPWM ADC Trigger reg6              | 0x0000_00000 |

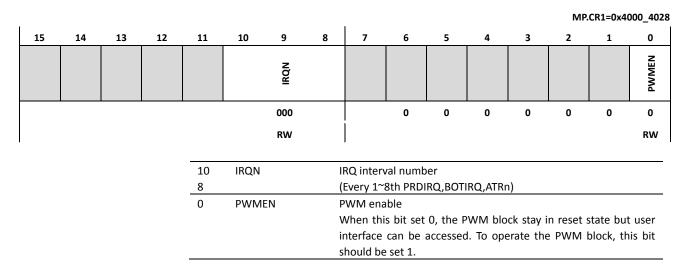

### A D'7 F % A DK A '7 cblfc``F Y[ ]ghYf '%

The PWM Control Register 1 is a 16-bit register.

Basically, PRDIRQ and BOTIRQ are generated every period. However, the interrupt interval can be controlled from 0 to 8 periods. When IRQN.CR1 = 0, the interrupt is requested every period, otherwise the interrupt is requested every (IRQN+1) times of period.

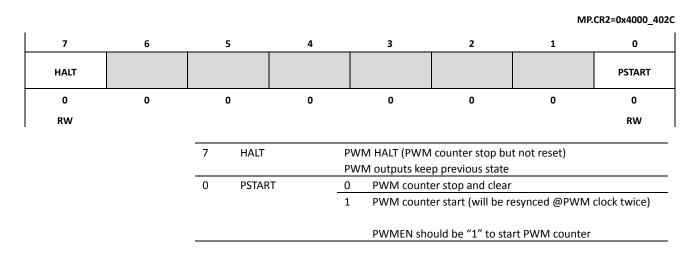

## A D'7 F & A DK A '7 cblfc``F Y[ ]ghYf '&

The PWM Control Register 2 is an 8-bit register.

### AD'D7Fb

## ADKA DfchYWFjcb \$2%7 cbffc``FY[]ghYf

The PWM Protection Control register is a 16-bit register.

|        |         |    |    |    |    |       |   |        |   | М              | P.PCR0=0 | x4000_4 | 040, MP.P | CR1=0x4 | 000_4048 |

|--------|---------|----|----|----|----|-------|---|--------|---|----------------|----------|---------|-----------|---------|----------|

| 15     | 14      | 13 | 12 | 11 | 10 | 9     | 8 | 7      | 6 | 5              | 4        | 3       | 2         | 1       | 0        |

| PROTEN | PROTPOL |    |    |    |    | PROTD |   | PROTIE |   | <b>WHPROTM</b> | ИНРКОТМ  | UHPROTM | WLPROTM   | VLPROTM | ULPROTM  |

| 0      | 0       |    |    |    |    | 000   |   | 0      |   | 0              | 0        | 0       | 0         | 0       | 0        |

| RW     | RW      |    |    |    |    | RW    |   | RW     |   | RW             | RW       | RW      | RW        | RW      | RW       |

| 15 | PROTOEN  | Enable Protection Input 0                 |

|----|----------|-------------------------------------------|

| 14 | PROTOPOL | Select Protection Input Polarity          |

|    |          | 0: Low-Active                             |

|    |          | 1: High-Active                            |

| 10 | PROTD    | Protection Input debounce                 |

| 8  |          | 0 – no debounce                           |

|    |          | 1~7 – debounce by (MPWMCLK * PROTD[2:0])  |

| 7  | PROTIE   | Protection Interrupt enable               |

|    |          | 0 Disable protection interrupt            |

|    |          | 1 Enable protection interrupt             |

| 5  | WHPROTM  | Activate W-phase H-side protection output |

|    |          | 0 Disable Protection Output               |

|    |          | 1 Enable Protection Output with FOR value |

| 4  | VHPROTM  | Activate V-phase H-side protection output |

|    |          | 0 Disable Protection Output               |

|    |          | 1 Enable Protection Output with FOR value |

| 3  | UHPROTM  | Activate U-phase H-side protection output |

|    |          | 0 Disable Protection Output               |

|    |          | 1 Enable Protection Output with FOR value |

| 2  | WLPROTM  | Activate W-phase L-side protection output |

|    |          | 0 Disable Protection Output               |

|    |          | 1 Enable Protection Output with FOR value |

| 1  | VLPROTM  | Activate V-phase L-side protection output |

|    |          | 0 Disable Protection Output               |

|    |          | 1 Enable Protection Output with FOR value |

| 0  | ULPROTM  | Activate U-phase L-side protection output |

|    |          | 0 Disable Protection Output               |

|    |          | 1 Enable Protection Output with FOR value |

Note: MP.PCR0 is related to the PRTIN pin and MP.PCR1 is related to OVIN.

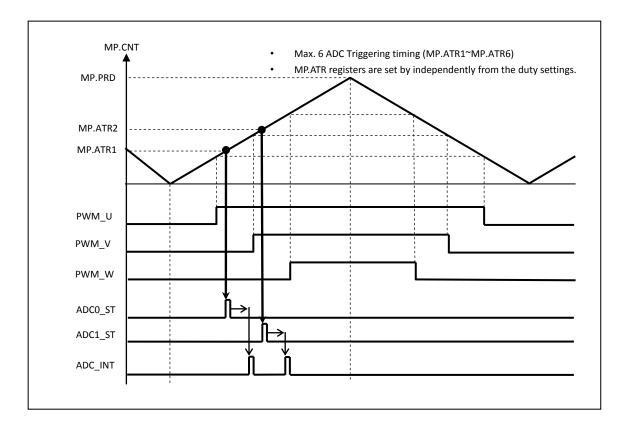

## 8 YgWf]dh]cb'cZ5 8 7 'Hf][[Yf]b[':ibWf]cb'

A total of six ADC trigger timing registers are provided. This dedicated register triggers a signal to start ADC conversion. The conversion channel of ADC is defined in the ADC Control register.

:][ifY`%)!%\*`587`Hf][[Yf]b[`:ibWf]cb`H]a]b[`8]U[fUa`

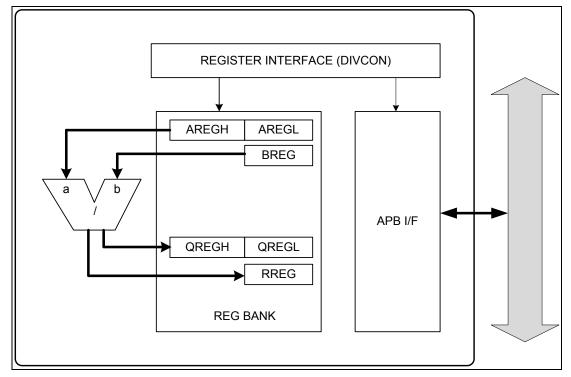

## % "8]j]XYf fB =J \* ( Ł

## Cj Yfj ]Yk <sup>·</sup>

The divider module provides the hardware divider the ability to accelerate complicated calculations. This divider is a sequential 64-bit/32-bit divider and requires 32 clock cycles for one operation.

The equation for this operation is:

(AREGH,AREGL)/BREG = (QREGH,QREGL)

- Unsigned 64-bit dividend

- Unsigned 32-bit divisor

- Unsigned 64-bit quotient

- Unsigned 32-bit remainder

- Unsigned 32-cycle operating time

#### : ][ i fY'% !%6`cW\_'8 ]U[ fUa '

## EF9; @ `EF9; `fEich]YbhL`@ck Yf '' &!V]hFY[ ]ghYf `

The divider stores the lower 32-bit value of the quotient in this register.

|    |             |    |    |    |    |    |    |    |    |    |     |    |    |    |    |     |      |       |       |       |     |      |    |   |   |   | QF | REGL | =0x4 | 000_ | 0510 |

|----|-------------|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|-----|------|-------|-------|-------|-----|------|----|---|---|---|----|------|------|------|------|

| 31 | 30          | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20  | 19 | 18 | 17 | 16 | 15  | 14   | 13    | 12    | 11    | 10  | 9    | 8  | 7 | 6 | 5 | 4  | 3    | 2    | 1    | 0    |

|    | QREGL[31:0] |    |    |    |    |    |    |    |    |    |     |    |    |    |    |     |      |       |       |       |     |      |    |   |   |   |    |      |      |      |      |

|    | 0x0000_0000 |    |    |    |    |    |    |    |    |    |     |    |    |    |    |     |      |       |       |       |     |      |    |   |   |   |    |      |      |      |      |

|    |             |    |    |    |    |    |    |    |    |    |     |    |    |    | I  | R   |      |       |       |       |     |      |    |   |   |   |    |      |      |      |      |

|    |             |    |    |    |    |    |    | 3  |    | Q  | REG | L  |    |    | L  | owe | r 32 | bit v | value | e for | quo | tien | t. |   |   |   |    |      |      |      |      |

## EF9; < ``EF9; 'fEi ch]Ybh2<][ \ '' &!V]hFY[ ]ghYf`

The divider stores the high 32-bit value of the quotient in this register.

| 0050U 0 4000 | 0544  |

|--------------|-------|

| QREGH=0x4000 | _0514 |

| 31 | 30           | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22      | 21 | 20  | 19 | 18 | 17 | 16 | 15   | 14   | 13    | 12  | 11    | 10   | 9    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|--------------|----|----|----|----|----|----|----|---------|----|-----|----|----|----|----|------|------|-------|-----|-------|------|------|---|---|---|---|---|---|---|---|---|

|    | QREGH[63:32] |    |    |    |    |    |    |    |         |    |     |    |    |    |    |      |      |       |     |       |      |      |   |   |   |   |   |   |   |   |   |

|    | 0x0000_0000  |    |    |    |    |    |    |    |         |    |     |    |    |    |    |      |      |       |     |       |      |      |   |   |   |   |   |   |   |   |   |

|    | R            |    |    |    |    |    |    |    |         |    |     |    |    |    |    |      |      |       |     |       |      |      |   |   |   |   |   |   |   |   |   |

|    |              |    |    |    |    |    |    | 3  | 31<br>) | Q  | REG | H  |    |    | F  | ligh | 32 b | it va | lue | for q | uoti | ent. |   |   |   |   |   |   |   |   |   |

## FF9; FF9; FF9; FFYa UjbhYfŁFY[ ]ghYf

The divider stores the 32-bit value of the remainder in this register.

|    |                                     |    |    |    |    |    |    |        |    |    |     |    |    |    |    |      |       |     |      |        |       |   |   |   |   |   | R | REG | =0x4 | 000_ | 0518 |

|----|-------------------------------------|----|----|----|----|----|----|--------|----|----|-----|----|----|----|----|------|-------|-----|------|--------|-------|---|---|---|---|---|---|-----|------|------|------|

| 31 | 30                                  | 29 | 28 | 27 | 26 | 25 | 24 | 23     | 22 | 21 | 20  | 19 | 18 | 17 | 16 | 15   | 14    | 13  | 12   | 11     | 10    | 9 | 8 | 7 | 6 | 5 | 4 | 3   | 2    | 1    | 0    |

|    | RREG[31:0]                          |    |    |    |    |    |    |        |    |    |     |    |    |    |    |      |       |     |      |        |       |   |   |   |   |   |   |     |      |      |      |

|    | 0x0000_0000                         |    |    |    |    |    |    |        |    |    |     |    |    |    |    |      |       |     |      |        |       |   |   |   |   |   |   |     |      |      |      |

|    | R                                   |    |    |    |    |    |    |        |    |    |     |    |    |    |    |      |       |     |      |        |       |   |   |   |   |   |   |     |      |      |      |

|    | 31 RREG 32 bit value for remainder. |    |    |    |    |    |    |        |    |    |     |    |    |    |    |      |       |     |      |        |       |   |   |   |   |   |   |     |      |      |      |

|    |                                     |    |    |    |    |    |    | 3<br>0 | -  | ĸ  | NEG |    |    |    | 3  | 2 01 | L VdI | uen | Jire | IIIdli | nuer. |   |   |   |   |   |   |     |      |      |      |

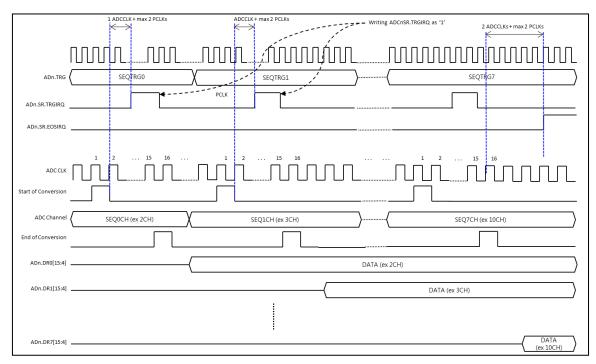

## 587 GYei YbhjU 7 cbj Yfg]cb A c XY Hja ]b[ 8 JU[ fUa

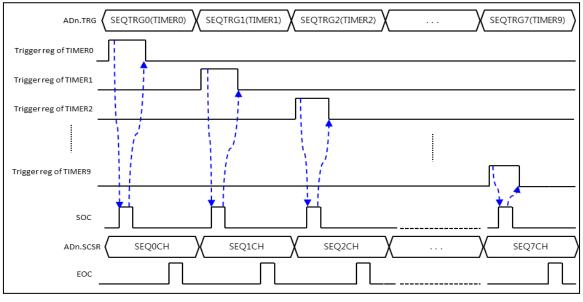

Single Sequential Conversion mode (Single Sequential mode) occurs when AD.MR.ADMOD is 0x0 and AD.MR.SEQCNT is not 0x0. To set Sequential Conversion mode, AD.MR.AMOD is 2'b00 and AD.MR.SEQCNT is not 2'b00.

The operation of Sequential mode is almost the same as the Burst mode. The difference is the source of SOC. Each SOC is made by the trigger of SEQTRGx as each SEQCNT. See Figure 17-5.

:][ifY`%+!)`587`GYeiYbh]U`AcXY`H]a]b[`fK\Yb`58"AF"5AC8`1'Ï\$`UbX`58"AF"G9E7BH©` Ï\$B2

## % "9`YWf]WU'7\UfUWfYf]gh]Wg'

## 87'7\UfUWN/f]ghjWg'

## 5 Vgc`ihY'AUI]aia'FUhjb[g`

Absolute maximum ratings are limiting values of operating and environmental conditions which should not be exceeded under the worst possible conditions.

| DUFUa YhYf'                 | Gma Vc`'          | A]b <sup>°</sup> | AUI.    | l b]h |

|-----------------------------|-------------------|------------------|---------|-------|

| Power Supply (VDD)          | VDD               | -0.5             | +6      | V     |

| Analog Power Supply (AVDD)  | AVDD              | -0.5             | +6      | V     |

| VDC Output Voltage          | VDD18             |                  |         | V     |

| Input High Voltage          |                   | -                | VDD+0.5 | V     |

| Input Low Voltage           |                   | VSS – 0.5        | -       | V     |

| Output Low Current per pin  | I <sub>OL</sub>   |                  | 5       | mA    |

| Output Low Current Total    | Σ I <sub>OL</sub> |                  | 40      | mA    |

| Output High Current per pin | I <sub>OH</sub>   |                  | 5       | mA    |

| Output Low Current Total    | Σ I <sub>OH</sub> |                  | 40      | mA    |

| Power consumption           |                   |                  |         | mW    |

| Input Main Clock Range      |                   | 4                | 16      | MHz   |

| Operating Frequency         |                   | -                | 40      | MHz   |

| Storage Temperature         | Tst               | -55              | +125    | Ĵ     |

| Operating Temperature       | Тор               | -40              | +105    | Ĵ     |

#### HUV`Y`%, !%5 Vgc`ihY`AUI]aia`FUh]b[`

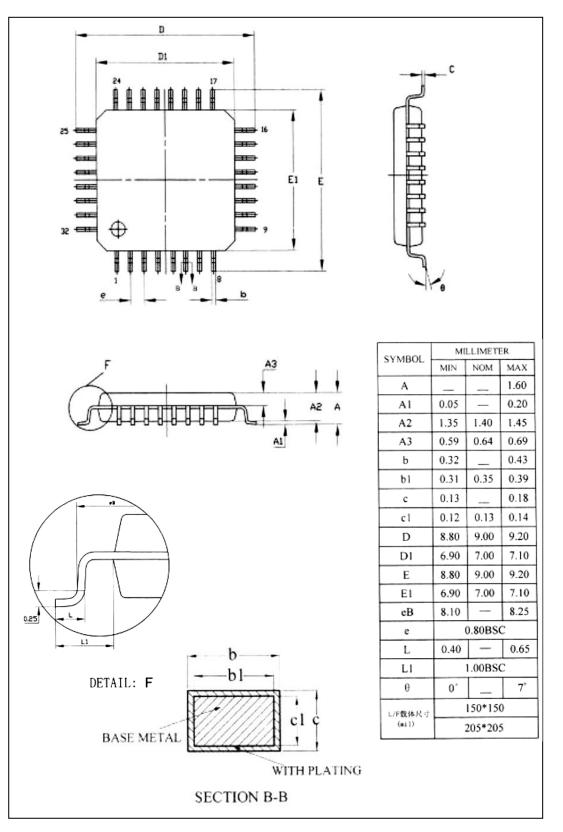

## % "DU<u>V</u> Ų Y

## @E: D!' & DUW\_U[ Y'8]a Ybg]cb'