#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                        |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 24MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IEBus, SIO, UART/USART                               |

| Peripherals                | DMA, WDT                                                                       |

| Number of I/O              | 111                                                                            |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 31K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                      |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 128-LQFP                                                                       |

| Supplier Device Package    | 128-LFQFP (14x20)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m306nnfjgp-u3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# M16C/6N Group (M16C/6NL, M16C/6NN)

Renesas MCU

REJ03B0061-0210 Rev.2.10 Aug 25, 2006

## 1. Overview

The M16C/6N Group (M16C/6NL, M16C/6NN) of MCUs are built using the high-performance silicon gate CMOS process using the M16C/60 Series CPU core and are packaged in 100-pin and 128-pin plastic molded LQFP. These MCUs operate using sophisticated instructions featuring a high level of instruction efficiency. With 1 Mbyte of address space, they are capable of executing instructions at high speed. Being equipped with one CAN (Controller Area Network) module in the M16C/6N Group (M16C/6NL, M16C/6NN), the MCU is suited to drive automotive and industrial control systems. The CAN module complies with the 2.0B specification. In addition, this MCU contains a multiplier and DMAC which combined with fast instruction processing capability, makes it suitable for control of various OA, communication equipment which requires high-speed arithmetic/logic operations.

## **1.1 Applications**

· Car audio and industrial control systems, other

Specifications written in this manual are believed to be accurate, but are not guaranteed to be entirely free of error. Specifications in this manual may be changed for functional or performance improvements. Please make sure your manual is the latest edition.

## **1.2 Performance Overview**

Tables 1.1 and 1.2 list the Functions and Specifications for M16C/6N Group (M16C/6NL, M16C/6NN).

| Item            |                         |                   | Specification                                                                       |  |  |  |

|-----------------|-------------------------|-------------------|-------------------------------------------------------------------------------------|--|--|--|

| CPU             | Number of fund          | damental          | 91 instructions                                                                     |  |  |  |

|                 | instructions            |                   |                                                                                     |  |  |  |

|                 | Minimum instruction     | on execution time | 41.7ns (f(BCLK) = 24 MHz, 1/1 prescaler, without software wait                      |  |  |  |

|                 | Operating mode          |                   | Single-chip, memory expansion and microprocessor modes                              |  |  |  |

|                 | Address space           | )                 | 1 Mbyte                                                                             |  |  |  |

|                 | Memory capacity         |                   | Refer to Table 1.3 Product Information                                              |  |  |  |

| Peripheral      | Ports                   |                   | Input/Output: 87 pins, Input: 1 pin                                                 |  |  |  |

| Function        | Multifunction tir       | ners              | Timer A: 16 bits $\times$ 5 channels                                                |  |  |  |

|                 |                         |                   | Timer B: 16 bits $\times$ 6 channels                                                |  |  |  |

|                 |                         |                   | Three-phase motor control circuit                                                   |  |  |  |

|                 | Serial interface        | es                | 3 channels                                                                          |  |  |  |

|                 |                         |                   | Clock synchronous, UART, I <sup>2</sup> C-bus <sup>(1)</sup> , IEBus <sup>(2)</sup> |  |  |  |

|                 |                         |                   | 2 channels                                                                          |  |  |  |

|                 |                         |                   | Clock synchronous                                                                   |  |  |  |

|                 | A/D converter           |                   | 10-bit A/D converter: 1 circuit, 26 channels                                        |  |  |  |

|                 | D/A converter           |                   | 8 bits $\times$ 2 channels                                                          |  |  |  |

|                 | DMAC                    |                   | 2 channels                                                                          |  |  |  |

|                 | CRC calculation circuit |                   | CRC-CCITT                                                                           |  |  |  |

|                 | CAN module              |                   | 1 channel with 2.0B specification                                                   |  |  |  |

|                 | Watchdog timer          |                   | 15 bits $\times$ 1 channel (with prescaler)                                         |  |  |  |

|                 | Interrupts              |                   | Internal: 30 sources, External: 9 sources                                           |  |  |  |

|                 |                         |                   | Software: 4 sources, Priority levels: 7 levels                                      |  |  |  |

|                 | Clock generati          | on circuits       | 4 circuits                                                                          |  |  |  |

|                 |                         |                   | Main clock oscillation circuit (*)                                                  |  |  |  |

|                 |                         |                   | Sub clock oscillation circuit (*)                                                   |  |  |  |

|                 |                         |                   | On-chip oscillator                                                                  |  |  |  |

|                 |                         |                   | PLL frequency synthesizer                                                           |  |  |  |

|                 |                         |                   | (*) Equipped with on-chip feedback resistor                                         |  |  |  |

|                 | Oscillation-stop        | ped detector      | Main clock oscillation stop and re-oscillation detection function                   |  |  |  |

| Electrical      | Supply voltage          | •                 | VCC = 3.0 to 5.5 V                                                                  |  |  |  |

| Characteristics |                         |                   | (f(BCLK) = 24 MHz, 1/1 prescaler, without software wait)                            |  |  |  |

|                 | Consumption             | Mask ROM          | 19mA (f(BCLK) = 24 MHz, PLL operation, no division)                                 |  |  |  |

|                 | current                 | Flash memory      | 21mA (f(BCLK) = 24 MHz, PLL operation, no division)                                 |  |  |  |

|                 |                         | Mask ROM          | 3µA (f(BCLK) = 32 kHz, Wait mode, Oscillation capacity Low)                         |  |  |  |

|                 |                         | Flash memory      | 0.8µA (Stop mode, Topr = 25°C)                                                      |  |  |  |

| Flash Memory    | Programming and         | erasure voltage   | $3.3 \pm 0.3$ V or $5.0 \pm 0.5$ V                                                  |  |  |  |

| Version         | Programming and e       |                   |                                                                                     |  |  |  |

| I/O             | I/O withstand v         |                   | 5.0 V                                                                               |  |  |  |

| Characteristics | Output current          |                   | 5m A                                                                                |  |  |  |

|                 | bient Tempera           |                   | -40 to 85°C                                                                         |  |  |  |

| Device Config   | guration                |                   | CMOS high-performance silicon gate                                                  |  |  |  |

| Package         |                         |                   | 100-pin molded-plastic LQFP                                                         |  |  |  |

|                 |                         |                   | , . ,                                                                               |  |  |  |

NOTES:

1. I<sup>2</sup>C-bus is a trademark of Koninklijke Philips Electronics N.V.

2. IEBus is a trademark of NEC Electronics Corporation.

| Pin No.   | Control<br>Pin | Port         | Interrupt<br>Pin | Timer Pin | UART Pin | Analog<br>Pin  | CAN Module<br>Pin | Pin                      |

|-----------|----------------|--------------|------------------|-----------|----------|----------------|-------------------|--------------------------|

| 51        |                | P5_6         |                  |           |          |                |                   | ALE                      |

| 52        |                | P5_5         |                  |           |          |                |                   | HOLD                     |

| 53        |                | P5_4         |                  |           |          |                |                   | HLDA                     |

| 54        |                | P13_3        |                  |           |          |                |                   |                          |

| 55        |                | P13_2        |                  |           |          |                |                   |                          |

| 56        |                | P13_1        |                  |           |          |                |                   |                          |

| 57        |                | P13_0        |                  |           |          |                |                   |                          |

| 58        |                | P5_3         |                  |           |          |                |                   | BCLK                     |

| 59        |                | P5_2         |                  |           |          |                |                   | RD                       |

| 60        |                | P5_1         |                  |           |          |                |                   | WRH/BHE                  |

| 61        |                | P5_0         |                  |           |          |                |                   | WRL/WR                   |

| 62        |                | P12_7        |                  |           |          |                |                   |                          |

| 63        |                | P12_6        |                  |           |          |                |                   |                          |

| 64        |                | P12_5        |                  |           |          |                |                   |                          |

| 65        |                | P4_7         |                  |           |          |                |                   | CS3                      |

| 66        |                | <br>P4_6     |                  |           |          |                |                   | CS2                      |

| 67        |                | <br>P4_5     |                  |           |          |                |                   | CS1                      |

| 68        |                | P4_4         |                  |           |          |                |                   | <u>CS0</u>               |

| 69        |                | P4_3         |                  |           |          |                |                   | A19                      |

| 70        |                | P4_2         |                  |           |          |                |                   | A18                      |

| 71        |                | P4_1         |                  |           |          |                |                   | A17                      |

| 72        |                | P4_0         |                  |           |          |                |                   | A16                      |

| 73        |                | P3_7         |                  |           |          |                |                   | A15                      |

| 74        |                | P3_6         |                  |           |          |                |                   | A14                      |

| 75        |                | P3_5         |                  |           |          |                |                   | A13                      |

| 76        |                | P3_4         |                  |           |          |                |                   | A12                      |

| 77        |                | P3_3         |                  |           |          |                |                   | A11                      |

| 78        |                | P3_2         |                  |           |          |                |                   | A10                      |

| 79        |                | P3_1         |                  |           |          |                |                   | A9                       |

| 80        |                | P12_4        |                  |           |          |                |                   | 7.5                      |

| 81        |                | P12_3        |                  |           |          |                |                   |                          |

| 82        |                | P12_2        |                  |           |          |                |                   |                          |

| 83        |                | P12_1        |                  |           |          |                |                   |                          |

| 84        |                | P12_0        |                  |           |          |                |                   |                          |

| 85        | VCC2           | 1 12_0       |                  |           |          |                |                   |                          |

| 86        | 1002           | P3_0         |                  |           |          |                |                   | A8(/-/D7)                |

| 87        | vss            | 1.5_0        |                  |           |          |                |                   | 70(/7/07)                |

| 88        | 1000           | P2_7         |                  |           |          | AN2_7          |                   | A7(/D7/D6)               |

| 89        |                | P2_7         |                  |           |          | AN2_7<br>AN2_6 |                   | A6(/D6/D5)               |

| 90        |                | P2_0<br>P2_5 |                  |           |          | AN2_6          |                   | A5(/D5/D4)               |

| 90        |                | P2_5         |                  |           |          | AN2_3          |                   | A3(/D3/D4)<br>A4(/D4/D3) |

| 91        |                | P2_4         |                  |           |          | AN2_4          |                   | A4(/D4/D3)<br>A3(/D3/D2) |

| 92        |                | P2_3<br>P2_2 |                  |           |          | AN2_3          |                   | A3(/D3/D2)<br>A2(/D2/D1) |

| 93        |                | P2_2<br>P2_1 |                  |           |          | AN2_2<br>AN2_1 |                   | A1(/D1/D0)               |

| 94<br>95  |                |              |                  |           |          |                |                   | A0(/D0/-)                |

| 95<br>96  |                | P2_0<br>P1_7 | INT5             |           |          | AN2_0          |                   | D15                      |

|           |                |              | INT5<br>INT4     |           |          |                |                   | D15<br>D14               |

| 97        |                | P1_6         | INT3             |           |          |                |                   | D14<br>D13               |

| 98<br>99  |                | P1_5         | 11113            |           |          |                |                   | D13<br>D12               |

| 99<br>100 |                | P1_4<br>P1_3 |                  |           |          |                |                   | D12<br>D11               |

## 1.6 Pin Functions

Tables 1.9 to 1.11 list the Pin Functions.

| Signal Name   | Pin Name             | I/O Type       | Description                                                                                                       |

|---------------|----------------------|----------------|-------------------------------------------------------------------------------------------------------------------|

| Power supply  | VCC1, VCC2,          | I              | Apply 3.0 to 5.5 V to the VCC1 and VCC2 pins and 0 V to the VSS                                                   |

| input         | VSS                  |                | pin. The VCC apply condition is that VCC2 = VCC1 $^{(1)}$ .                                                       |

| Analog power  | AVCC, AVSS           |                | Applies the power supply for the A/D converter. Connect the AVCC                                                  |

| supply input  | ,                    |                | pin to VCC1. Connect the AVSS pin to VSS.                                                                         |

| Reset input   | RESET                |                | The MCU is in a reset state when applying "L" to the this pin.                                                    |

| CNVSS         | CNVSS                |                | Switches processor mode. Connect this pin to VSS to when after                                                    |

|               |                      |                | a reset to start up in single-chip mode. Connect this pin to VCC1                                                 |

|               |                      |                | to start up in microprocessor mode.                                                                               |

| External data | BYTE                 | 1              | Switches the data bus in external memory space. The data bus                                                      |

| bus width     |                      |                | is 16-bit long when the this pin is held "L" and 8-bit long when                                                  |

| select input  |                      |                | the this pin is held "H". Set it to either one. Connect this pin to                                               |

| Select Input  |                      |                | VSS when single-chip mode.                                                                                        |

| Bus control   | D0 to D7             | I/O            | Inputs and outputs data (D0 to D7) when these pins are set as                                                     |

|               |                      | 1/0            | the separate bus.                                                                                                 |

| pins          |                      | 1/0            | · · ·                                                                                                             |

|               | D8 to D15            | I/O            | Inputs and outputs data (D8 to D15) when external 16-bit data                                                     |

|               |                      |                | bus is set as the separate bus.                                                                                   |

|               | A0 to A19            | 0              | Output address bits (A0 to A19).                                                                                  |

|               | A0/D0 to A7/D7       | I/O            | Input and output data (D0 to D7) and output address bits (A0 to                                                   |

|               |                      |                | A7) by time-sharing when external 8-bit data bus are set as the                                                   |

|               |                      |                | multiplexed bus.                                                                                                  |

|               | A1/D0 to A8/D7       | I/O            | Input and output data (D0 to D7) and output address bits (A1 to                                                   |

|               |                      |                | A8) by time-sharing when external 16-bit data bus are set as the                                                  |

|               |                      |                | multiplexed bus.                                                                                                  |

|               | CS0 to CS3           | 0              | Output $\overline{CS0}$ to $\overline{CS3}$ signals. $\overline{CS0}$ to $\overline{CS3}$ are chip-select signals |

|               |                      |                | to specify an external space.                                                                                     |

|               | WRL/WR               | 0              | Output WRL, WRH, (WR, BHE), RD signals. WRL and WRH or                                                            |

|               | WRH/BHE              |                | BHE, and WR can be switched by program.                                                                           |

|               | RD                   |                | <ul> <li>WRL, WRH, and RD are selected</li> </ul>                                                                 |

|               |                      |                | The WRL signal becomes "L" by writing data to an even address                                                     |

|               |                      |                | in an external memory space.                                                                                      |

|               |                      |                | The WRH signal becomes "L" by writing data to an odd address                                                      |

|               |                      |                | in an external memory space.                                                                                      |

|               |                      |                | The RD pin signal becomes "L" by reading data in an external                                                      |

|               |                      |                | memory space.                                                                                                     |

|               |                      |                | • WR, BHE, and RD are selected                                                                                    |

|               |                      |                | The WR signal becomes "L" by writing data in an external                                                          |

|               |                      |                | memory space.                                                                                                     |

|               |                      |                | The RD signal becomes "L" by reading data in an external                                                          |

|               |                      |                | memory space.                                                                                                     |

|               |                      |                | The BHE signal becomes "L" by accessing an odd address.                                                           |

|               |                      |                | Select WR, BHE, and RD for an external 8-bit data bus.                                                            |

|               |                      | 0              | ALE is a signal to latch the address.                                                                             |

|               | ALE                  | 0              | While the HOLD pin is held "L", the MCU is placed in a hold                                                       |

|               | HOLD                 | I              |                                                                                                                   |

|               |                      |                | state.                                                                                                            |

|               | HLDA                 | 0              | In a hold state, HLDA outputs a "L" signal.                                                                       |

|               | RDY                  |                | While applying a "L" signal to the RDY pin, the MCU is placed in                                                  |

|               | <br>: Output I/O: Ir | <br> put/Outpu | a wait state.                                                                                                     |

## Table 1.9 Pin Functions (100-pin and 128-pin Versions) (1)

I: Input O: Output I/O: Input/Output

NOTE:

1. In this manual, hereafter, VCC refers to VCC1 unless otherwise noted.

RENESAS

1. Overview

## Table 1.10 Pin Functions (100-pin and 128-pin Versions) (2)

| Signal Name           | Pin Name                                                       | I/O Type  |                                                                       |

|-----------------------|----------------------------------------------------------------|-----------|-----------------------------------------------------------------------|

| Main clock            | XIN                                                            | I         | I/O pins for the main clock oscillation circuit. Connect a ceramic    |

| input                 |                                                                |           | resonator or crystal oscillator between XIN and XOUT <sup>(1)</sup> . |

| Main clock            | XOUT                                                           | 0         | To use the external clock, input the clock from XIN and leave         |

| output                |                                                                |           | XOUT open.                                                            |

| Sub clock             | XCIN                                                           | I         | I/O pins for a sub clock oscillation circuit. Connect a crysta        |

| input                 |                                                                |           | oscillator between XCIN and XCOUT <sup>(1)</sup> .                    |

| Sub clock             | XCOUT                                                          | 0         | To use the external clock, input the clock from XCIN and leave        |

| output                |                                                                |           | XCOUT open.                                                           |

| BCLK output           | BCLK                                                           | 0         | Outputs the BCLK signal.                                              |

| Clock output          | CLKOUT                                                         | 0         | The clock of the same cycle as fC, f8, or f32 is output.              |

| INT interrupt input   | NT0 to INT8 (2)                                                | I         | Input pins for the INT interrupt.                                     |

| NMI interrupt         | NMI                                                            | I         | Input pin for the NMI interrupt.                                      |

| input                 |                                                                |           |                                                                       |

| Key input             | KI0 to KI3                                                     | I         | Input pins for the key input interrupt.                               |

| interrupt input       |                                                                |           |                                                                       |

| Timer A               | TA0OUT to TA4OUT                                               | I/O       | These are timer A0 to timer A4 I/O pins.                              |

|                       | TA0IN to TA4IN                                                 | I         | These are timer A0 to timer A4 input pins.                            |

|                       | ZP                                                             | I         | Input pin for the Z-phase.                                            |

| Timer B               | TB0IN to TB5IN                                                 |           | These are timer B0 to timer B5 input pins.                            |

| Three-phase motor     | $\overline{U, \overline{U}, V, \overline{V}, W, \overline{W}}$ | 0         | These are Three-phase motor control output pins.                      |

| control output        |                                                                |           |                                                                       |

| Serial interface      | CTS0 to CTS2                                                   | I         | These are transmit control input pins.                                |

|                       | RTS0 to RTS2                                                   | 0         | These are receive control output pins.                                |

|                       | CLK0 to CLK6 <sup>(2)</sup>                                    | I/O       | These are transfer clock I/O pins.                                    |

|                       | RXD0 to RXD2                                                   | I         | These are serial data input pins.                                     |

|                       | SIN3 to SIN6 (2)                                               | I         | These are serial data input pins.                                     |

|                       | TXD0 to TXD2                                                   | 0         | These are serial data output pins.                                    |

|                       | SOUT3 to SOUT6 (2)                                             | 0         | These are serial data output pins.                                    |

|                       | CLKS1                                                          | 0         | This is output pin for transfer clock output from multiple pins       |

|                       |                                                                |           | function.                                                             |

| I <sup>2</sup> C mode | SDA0 to SDA2                                                   | I/O       | These are serial data I/O pins.                                       |

|                       | SCL0 to SCL2                                                   | I/O       | These are transfer clock I/O pins. (however, SCL2 for                 |

|                       |                                                                |           | the N-channel open drain output.)                                     |

| Reference             | VREF                                                           | I         | Applies the reference voltage for the A/D converter and D/A           |

| voltage input         |                                                                |           | converter.                                                            |

| A/D converter         | AN0 to AN7                                                     |           | Analog input pins for the A/D converter.                              |

|                       | AN0_0 to AN0_7                                                 |           |                                                                       |

|                       | AN2_0 to AN2_7                                                 |           |                                                                       |

|                       | ADTRG                                                          |           | This is an A/D trigger input pin.                                     |

|                       | ANEX0                                                          | I/O       | This is the extended analog input pin for the A/D converter           |

|                       |                                                                |           | and is the output in external op-amp connection mode.                 |

|                       | ANEX1                                                          |           | This is the extended analog input pin for the A/D converter.          |

| D/A converter         | DA0, DA1                                                       | 0         | These are the output pins for the D/A converter.                      |

| CAN module            | CRX0                                                           |           | This is the input pin for the CAN module.                             |

|                       | СТХО                                                           | 0         | This is the output pin for the CAN module.                            |

| : Input O:            |                                                                | put/Outpu |                                                                       |

I: Input O: Output I/O: Input/Output

#### NOTES:

1. Ask the oscillator maker the oscillation characteristic.

2. INT6 to INT8, CLK5, CLK6, SIN5, SIN6, SOUT5, SOUT6 are only in the 128-pin version.

## Table 4.4 SFR Information (4)

| Address        | Register                              | Symbol | After Reset |

|----------------|---------------------------------------|--------|-------------|

| 00C0h          |                                       |        | XXh         |

| 00C1h          |                                       |        | XXh         |

| 00C2h          | CAN0 Message Box 6: Identifier / DLC  |        | XXh         |

| 00C3h          |                                       |        | XXh         |

| 00C4h          |                                       |        | XXh         |

| 00C5h          |                                       |        | XXh<br>XXh  |

| 00C6h<br>00C7h |                                       |        | XXh         |

| 00C7h<br>00C8h |                                       |        | XXh         |

| 00C9h          | CANO Massage Day & Data Field         |        | XXh         |

| 00CAh          | CAN0 Message Box 6: Data Field        |        | XXh         |

| 00CBh          |                                       |        | XXh         |

| 00CCh          |                                       |        | XXh         |

| 00CDh          |                                       |        | XXh         |

| 00CEh          | CAN0 Message Box 6: Time Stamp        |        | XXh         |

| 00CFh<br>00D0h |                                       |        | XXh<br>XXh  |

| 00D0h          |                                       |        | XXh         |

| 00D1h<br>00D2h |                                       |        | XXh         |

| 00D2h          | CAN0 Message Box 7: Identifier / DLC  |        | XXh         |

| 00D4h          |                                       |        | XXh         |

| 00D5h          |                                       |        | XXh         |

| 00D6h          |                                       |        | XXh         |

| 00D7h          |                                       |        | XXh         |

| 00D8h          |                                       |        | XXh         |

| 00D9h          | CAN0 Message Box 7: Data Field        |        | XXh<br>XXh  |

| 00DAh<br>00DBh |                                       |        | XXn<br>XXh  |

| 00DBh<br>00DCh |                                       |        | XXh         |

| 00DDh          |                                       |        | XXh         |

| 00DEh          | CANO Massage Day 7: Time Otoma        |        | XXh         |

| 00DFh          | CAN0 Message Box 7: Time Stamp        |        | XXh         |

| 00E0h          |                                       |        | XXh         |

| 00E1h          |                                       |        | XXh         |

| 00E2h          | CAN0 Message Box 8: Identifier / DLC  |        | XXh         |

| 00E3h          | -                                     |        | XXh<br>XXh  |

| 00E4h<br>00E5h |                                       |        | XXh         |

| 00E5h          |                                       |        | XXh         |

| 00E7h          |                                       |        | XXh         |

| 00E8h          |                                       |        | XXh         |

| 00E9h          | CAN0 Message Box 8: Data Field        |        | XXh         |

| 00EAh          | Or the message box o. Data Fleid      |        | XXh         |

| 00EBh          |                                       |        | XXh         |

| 00ECh          |                                       |        | XXh         |

| 00EDh<br>00EEh |                                       |        | XXh<br>XXh  |

| 00EEh          | CAN0 Message Box 8: Time Stamp        |        | XXh         |

| 00E111         |                                       |        | XXh         |

| 00F1h          |                                       |        | XXh         |

| 00F2h          | CANO Massaga Bax 0: Identifiar / DI C |        | XXh         |

| 00F3h          | CAN0 Message Box 9: Identifier / DLC  |        | XXh         |

| 00F4h          |                                       |        | XXh         |

| 00F5h          |                                       |        | XXh         |

| 00F6h          |                                       |        | XXh         |

| 00F7h          |                                       |        | XXh<br>XXh  |

| 00F8h<br>00F9h |                                       |        | XXh         |

| 00F9h          | CAN0 Message Box 9: Data Field        |        | XXh         |

| 00FBh          |                                       |        | XXh         |

| 00FCh          |                                       |        | XXh         |

| 00FDh          |                                       |        | XXh         |

| 00FEh          | CAN0 Message Box 9: Time Stamp        |        | XXh         |

| 00FFh          |                                       |        | XXh         |

X: Undefined

## Table 4.7 SFR Information (7) (2)

| Address        | Register                                       | Symbol  | After Reset |

|----------------|------------------------------------------------|---------|-------------|

| 0180h          | ×                                              | · ·     |             |

| 0181h          |                                                |         |             |

| 0182h          |                                                |         |             |

| 0183h          |                                                |         |             |

| 0184h          |                                                |         |             |

| 0185h          |                                                |         |             |

| 0186h          |                                                |         |             |

| 0187h          |                                                |         |             |

| 0188h<br>0189h |                                                |         |             |

| 018Ah          |                                                |         |             |

| 018Bh          |                                                |         |             |

| 018Ch          |                                                |         |             |

| 018Dh          |                                                |         |             |

| 018Eh          |                                                |         |             |

| 018Fh          |                                                |         |             |

| 0190h          |                                                |         |             |

| 0191h          |                                                |         |             |

| 0192h          |                                                |         |             |

| 0193h          |                                                |         |             |

| 0194h<br>0195h |                                                |         |             |

| 0195h          |                                                |         |             |

| 0197h          |                                                |         |             |

| 0198h          |                                                |         |             |

| 0199h          |                                                |         |             |

| 019Ah          |                                                |         |             |

| 019Bh          |                                                |         |             |

| 019Ch          |                                                |         |             |

| 019Dh          |                                                |         |             |

| 019Eh<br>019Fh |                                                |         |             |

| 01A0h          |                                                |         |             |

| 01A1h          |                                                |         |             |

| 01A2h          |                                                |         |             |

| 01A3h          |                                                |         |             |

| 01A4h          |                                                |         |             |

| 01A5h          |                                                |         |             |

| 01A6h          |                                                |         |             |

| 01A7h<br>01A8h |                                                |         |             |

| 01A9h          |                                                |         |             |

| 01AAh          |                                                |         |             |

| 01ABh          |                                                |         |             |

| 01ACh          |                                                |         |             |

| 01ADh          |                                                |         |             |

| 01AEh          |                                                |         |             |

| 01AFh          |                                                |         |             |

| 01B0h          |                                                |         |             |

| 01B1h<br>01B2h |                                                |         |             |

| 01B2h<br>01B3h |                                                |         |             |

| 01B3n          |                                                |         |             |

| 01B5h          | Flash Memory Control Register 1 (1)            | FMR1    | 0X00XX0Xb   |

| 01B6h          |                                                |         |             |

| 01B7h          | Flash Memory Control Register 0 <sup>(1)</sup> | FMR0    | 0000001b    |

| 01B8h          |                                                |         | 00h         |

| 01B9h          | Address Match Interrupt Register 2             | RMAD2   | 00h         |

| 01BAh          | Address Match Islands Frankla Davida A         |         | X0h         |

| 01BBh          | Address Match Interrupt Enable Register 2      | AIER2   | XXXXXX00b   |

| 01BCh<br>01BDh | Address Match Interrupt Register 3             | RMAD3   | 00h<br>00h  |

| 01BDh<br>01BEh | Auress maith interrupt negister s              | NIVIAD3 | X0h         |

| 01BFh          |                                                |         | 700         |

| X: Undefine    |                                                | 1       | ı I         |

X: Undefined

NOTES:

These registers are included in the flash memory version. Cannot be accessed by users in the mask ROM version.

Blank spaces are reserved. No access is allowed.

## Table 4.8 SFR Information (8) <sup>(3)</sup>

| Address    | Register                                                                   | Symbol         | After Reset |

|------------|----------------------------------------------------------------------------|----------------|-------------|

| 01C0h      | Timer B3, B4, B5 Count Start Flag                                          | TBSR           | 000XXXXXb   |

| 01C0n      | Timer B3, B4, B5 Count Start Flag                                          | IBSR           | 000/////    |

|            |                                                                            |                | XXh         |

| 01C2h      | Timer A1-1 Register                                                        | TA11           | XXh         |

| 01C3h      | -                                                                          |                | XXh         |

| 01C4h      | Timer A2-1 Register                                                        | TA21           | XXh         |

| 01C5h      |                                                                            |                | XXh         |

| 01C6h      | Timer A4-1 Register                                                        | TA41           | XXh         |

| 01C7h      |                                                                            |                |             |

| 01C8h      | Three-Phase PWM Control Register 0                                         | INVC0<br>INVC1 | 00h         |

| 01C9h      | Three-Phase PWM Control Register 1<br>Three-Phase Output Buffer Register 0 | IDB0           | 00h         |

| 01CAh      |                                                                            |                | 00111111b   |

| 01CBh      | Three-Phase Output Buffer Register 1 Dead Time Timer                       | IDB1           | 00111111b   |

| 01CCh      |                                                                            | DTT            | XXh         |

| 01CDh      | Timer B2 Interrupt Generation Frequency Set Counter                        | ICTB2          | XXh         |

| 01CEh      | Laterary October Designer O                                                | 15050          | Vaaaaaa     |

| 01CFh      | Interrupt Source Select Register 2                                         | IFSR2          | X000000b    |

| 01D0h      | Timer B3 Register                                                          | ТВЗ            | XXh         |

| 01D1h      |                                                                            |                | XXh         |

| 01D2h      | Timer B4 Register                                                          | ТВ4            | XXh         |

| 01D3h      | 5                                                                          |                | XXh         |

| 01D4h      | Timer B5 Register                                                          | ТВ5            | XXh         |

| 01D5h      |                                                                            |                | XXh         |

| 01D6h      | SI/O6 Transmit/Receive Register (1)                                        | S6TRR          | XXh         |

| 01D7h      |                                                                            |                | 01000000    |

| 01D8h      | SI/O6 Control Register <sup>(1)</sup>                                      | S6C            | 0100000b    |

| 01D9h      | SI/O6 Bit Rate Register <sup>(1)</sup>                                     | S6BRG          | XXh         |

| 01DAh      | SI/O3, 4, 5, 6 Transmit/Receive Register <sup>(2)</sup>                    | S3456TRR       | XXXX0000b   |

| 01DBh      | Timer B3 Mode Register                                                     | TB3MR          | 00XX0000b   |

| 01DCh      | Timer B4 Mode Register                                                     | TB4MR          | 00XX0000b   |

| 01DDh      | Timer B5 Mode Register                                                     | TB5MR          | 00XX0000b   |

| 01DEh      | Interrupt Source Select Register 0                                         | IFSR0          | 00h         |

| 01DFh      | Interrupt Source Select Register 1                                         | IFSR1          | 00h         |

| 01E0h      | SI/O3 Transmit/Receive Register                                            | S3TRR          | XXh         |

| 01E1h      |                                                                            |                |             |

| 01E2h      | SI/O3 Control Register                                                     | S3C            | 0100000b    |

| 01E3h      | SI/O3 Bit Rate Register                                                    | S3BRG          | XXh         |

| 01E4h      | SI/O4 Transmit/Receive Register                                            | S4TRR          | XXh         |

| 01E5h      |                                                                            |                |             |

| 01E6h      | SI/O4 Control Register                                                     | S4C            | 0100000b    |

| 01E7h      | SI/O4 Bit Rate Register                                                    | S4BRG          | XXh         |

| 01E8h      | SI/O5 Transmit/Receive Register (1)                                        | S5TRR          | XXh         |

| 01E9h      |                                                                            |                |             |

| 01EAh      | SI/O5 Control Register <sup>(1)</sup>                                      | S5C            | 0100000b    |

| 01EBh      | SI/O5 Bit Rate Register <sup>(1)</sup>                                     | S5BRG          | XXh         |

| 01ECh      | UARTO Special Mode Register 4                                              | U0SMR4         | 00h         |

| 01EDh      | UARTO Special Mode Register 3                                              | U0SMR3         | 000X0X0Xb   |

| 01EEh      | UART0 Special Mode Register 2                                              | U0SMR2         | X000000b    |

| 01EFh      | UART0 Special Mode Register                                                | U0SMR          | X000000b    |

| 01F0h      | UART1 Special Mode Register 4                                              | U1SMR4         | 00h         |

| 01F1h      | UART1 Special Mode Register 3                                              | U1SMR3         | 000X0X0Xb   |

| 01F2h      | UART1 Special Mode Register 2                                              | U1SMR2         | X000000b    |

| 01F3h      | UART1 Special Mode Register                                                | U1SMR          | X000000b    |

| 01F4h      | UART2 Special Mode Register 4                                              | U2SMR4         | 00h         |

| 01F5h      | UART2 Special Mode Register 3                                              | U2SMR3         | 000X0X0Xb   |

| 01F6h      | UART2 Special Mode Register 2                                              | U2SMR2         | X000000b    |

| 01F7h      | UART2 Special Mode Register                                                | U2SMR          | X000000b    |

| 01F8h      | UART2 Transmit/Receive Mode Register                                       | U2MR           | 00h         |

| 01F9h      | UART2 Bit Rate Register                                                    | U2BRG          | XXh         |

| 01FAh      | UART2 Transmit Buffer Register                                             | U2TB           | XXh         |

| 01FBh      | UALTZ HANSINIL DUNEL NEYISLEN                                              | 0210           | XXh         |

| 01FCh      | UART2 Transmit/Receive Control Register 0                                  | U2C0           | 00001000b   |

| 01FDh      | UART2 Transmit/Receive Control Register 1                                  | U2C1           | 00000010b   |

| 01FEh      | LIARTO Receive Ruffer Register                                             |                | XXh         |

| 01FFh      | UART2 Receive Buffer Register                                              | U2RB           | XXh         |

| V: Undofin |                                                                            | •              |             |

X: Undefined

NOTES:

These registers exist only in the 128-pin version.

Bits S5TRF and S6TRF in the S3456TRR register are used in the 128-pin version.

Blank spaces are reserved. No access is allowed.

## Table 5.3 Recommended Operating Conditions (2) (1)

| Sumbol   | Parameter                              |                                                                          |                     |  |      | Unit |      |      |

|----------|----------------------------------------|--------------------------------------------------------------------------|---------------------|--|------|------|------|------|

| Symbol   |                                        |                                                                          |                     |  | Min. | Тур. | Max. | Unit |

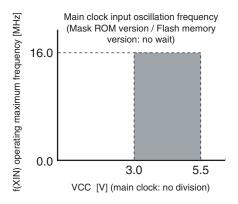

| f(XIN)   | Main clock input oscillation           | Main clock input oscillation No wait Mask ROM version VCC = 3.0 to 5.5 V |                     |  |      |      |      | MHz  |

|          | frequency (2) (3) (4)                  | frequency (2) (3) (4) Flash memory version                               |                     |  |      |      |      |      |

| f(XCIN)  | Sub clock oscillation fre              | Sub clock oscillation frequency                                          |                     |  |      |      |      | kHz  |

| f(Ring)  | On-chip oscillation frequencies        | On-chip oscillation frequency                                            |                     |  |      |      |      | MHz  |

| f(PLL)   | PLL clock oscillation frequency        |                                                                          |                     |  |      |      | 24   | MHz  |

| f(BCLK)  | CPU operation clock VCC = 3.0 to 5.5 V |                                                                          |                     |  |      |      | 24   | MHz  |

| tsu(PLL) | PLL frequency synthesi                 | zer stab                                                                 | ilization wait time |  |      |      | 20   | ms   |

NOTES:

- 1. Referenced to VCC = 3.0 to 5.5 V at Topr = -40 to 85°C unless otherwise specified.

- 2. Relationship between main clock oscillation frequency and supply voltage is shown right.

- 3. Execute program/erase of flash memory by VCC = 3.3  $\pm$  0.3 V or VCC = 5.0  $\pm$  0.5 V.

- 4. When using 16 MHz and over, use PLL clock. PLL clock oscillation frequency which can be used is 16 MHz, 20 MHz or 24 MHz.

| Symbol        | Parameter               |                 | Measuring Condition |                                            | Standard |      |      | Unit |

|---------------|-------------------------|-----------------|---------------------|--------------------------------------------|----------|------|------|------|

| Symbol        | Falali                  | letei           |                     |                                            |          | Тур. | Max. | Unit |

| _             | Resolution              |                 | VREF :              | VREF = VCC                                 |          |      | 10   | Bit  |

| INL           | Integral                | 10 bits         | VREF                | ANEX0, ANEX1 input, AN0 to AN7 input,      |          |      | ±3   | LSB  |

|               | nonlinearity            |                 | = VCC               | AN0_0 to AN0_7 input, AN2_0 to AN2_7 input |          |      |      |      |

|               | error                   |                 | = 5 V               | External operation amp connection mode     |          |      | ±7   | LSB  |

|               |                         |                 | VREF                | ANEX0, ANEX1 input, AN0 to AN7 input,      |          |      | ±5   | LSB  |

|               |                         |                 | = VCC               | AN0_0 to AN0_7 input, AN2_0 to AN2_7 input |          |      |      |      |

|               |                         |                 | = 3.3 V             | External operation amp connection mode     |          |      | ±7   | LSB  |

|               |                         | 8 bits          | VREF :              | = AVCC = VCC = 3.3 V                       |          |      | ±2   | LSB  |

| _             | Absolute                | 10 bits         | VREF                | ANEX0, ANEX1 input, AN0 to AN7 input,      |          |      | ±3   | LSB  |

|               | accuracy                |                 | = VCC               | AN0_0 to AN0_7 input, AN2_0 to AN2_7 input |          |      |      |      |

|               |                         |                 | = 5 V               | External operation amp connection mode     |          |      | ±7   | LSB  |

|               |                         |                 | VREF                | ANEX0, ANEX1 input, AN0 to AN7 input,      |          |      | ±5   | LSB  |

|               |                         |                 | = VCC               | AN0_0 to AN0_7 input, AN2_0 to AN2_7 input |          |      |      |      |

|               |                         |                 | = 3.3 V             | External operation amp connection mode     |          |      | ±7   | LSB  |

|               |                         | 8 bits          | VREF :              | = AVCC = VCC = 3.3 V                       |          |      | ±2   | LSB  |

| DNL           | Differential non        | linearity error |                     |                                            |          |      | ±1   | LSB  |

| -             | Offset error            |                 |                     |                                            |          |      | ±3   | LSB  |

| -             | Gain error              |                 |                     |                                            |          |      | ±3   | LSB  |

| RLADDER       | Resistor ladde          | r               | VREF :              | = VCC                                      | 10       |      | 40   | kΩ   |

| tconv         | 10-bit conversi         | on time,        | VREF :              | = VCC = 5 V, φAD = 10 MHz                  | 3.3      |      |      | μs   |

|               | sample & hold available |                 |                     |                                            |          |      |      |      |

|               | 8-bit conversion time,  |                 | VREF :              | = VCC = 5 V,                               | 2.8      |      |      | μs   |

|               | sample & hold available |                 |                     |                                            |          |      |      |      |

| <b>t</b> SAMP | Sampling time           |                 |                     |                                            | 0.3      |      |      | μs   |

| VREF          | Reference volt          | age             |                     |                                            | 2.0      |      | Vcc  | V    |

| VIA           | Analog input ve         | oltage          |                     |                                            | 0        |      | VREF | V    |

NOTES:

1. Referenced to VCC = AVCC = VREF = 3.3 to 5.5 V, VSS = AVSS = 0 V, -40 to 85°C unless otherwise specified.

2.  $\phi$ AD frequency must be 10 MHz or less.

When sample & hold is disabled, φAD frequency must be 250 kHz or more in addition to a limit of NOTE 2.

When sample & hold is enabled, φAD frequency must be 1 MHz or more in addition to a limit of NOTE 2.

Table 5.7 D/A conversion Characteristics (1)

| Symbol | Parameter                            | Measuring Condition | Standard |      |      | Unit |

|--------|--------------------------------------|---------------------|----------|------|------|------|

|        |                                      | Measuring Condition | Min.     | Тур. | Max. | Onit |

| -      | Resolution                           |                     |          |      | 8    | Bits |

| -      | Absolute accuracy                    |                     |          |      | 1.0  | %    |

| tsu    | Setup time                           |                     |          |      | 3    | μs   |

| Ro     | Output resistance                    |                     | 4        | 10   | 20   | kΩ   |

| IVREF  | Reference power supply input current | (NOTE 2)            |          |      | 1.5  | mA   |

NOTES:

1. Referenced to VCC = AVCC = VREF = 3.3 to 5.5 V, VSS = AVSS = 0 V, -40 to 85°C unless otherwise specified.

2. This applies when using one D/A converter, with the DAi register (i = 0, 1) for the unused D/A converter set to 00h. The resistor ladder of the A/D converter is not included. Also, the IVREF will flow even if VREF is disconnected by the ADCON1 register.

| Sumbol | Parameter                        |                       |      | Standard |           | Unit  |

|--------|----------------------------------|-----------------------|------|----------|-----------|-------|

| Symbol |                                  |                       | Min. | Тур.     | Max.      |       |

| -      | Programming and erasure end      | urance <sup>(2)</sup> | 100  |          |           | cycle |

| -      | Word program time (VCC = 5.0     | • V)                  |      | 25       | 200       | μs    |

| -      | Lock bit program time            |                       |      | 25       | 200       | μs    |

| -      | Block erase time                 | 4-Kbyte block         |      | 0.3      | 4         | s     |

|        | (VCC = 5.0 V)                    | 8-Kbyte block         |      | 0.3      | 4         | s     |

|        |                                  | 32-Kbyte block        |      | 0.5      | 4         | s     |

|        |                                  | 64-Kbyte block        |      | 0.8      | 4         | S     |

| -      | Erase all unlocked blocks time   |                       |      |          | 4 × n (3) | S     |

| tps    | Flash memory circuit stabilizati | on wait time          |      |          | 15        | μs    |

## Table 5.8 Flash Memory Version Electrical Characteristics (1)

NOTES:

1. Referenced to VCC = 4.5 to 5.5 V, 3.0 to 3.6 V, Topr = 0 to  $60^{\circ}$ C unless otherwise specified.

2. Programming and erasure endurance refers to the number of times a block erase can be performed.

If the programming and erasure endurance is n (n = 100), each block can be erased n times. For example, if a 4-Kbyte block A is erased after writing 1 word data 2,048 times, each to a different address, this counts as one programming and erasure endurance. Data cannot be written to the same address more than once without erasing the block (rewrite prohibited).

3. n denotes the number of blocks to erase.

## Table 5.9 Flash Memory Version Program/Erase Voltage and Read Operation Voltage Characteristics (at Topr = 0 to 60°C)

| Flash Program, Erase Voltage     | Flash Read Operation Voltage |

|----------------------------------|------------------------------|

| VCC = 3.3 ± 0.3 V or 5.0 ± 0.5 V | VCC = 3.0 to 5.5 V           |

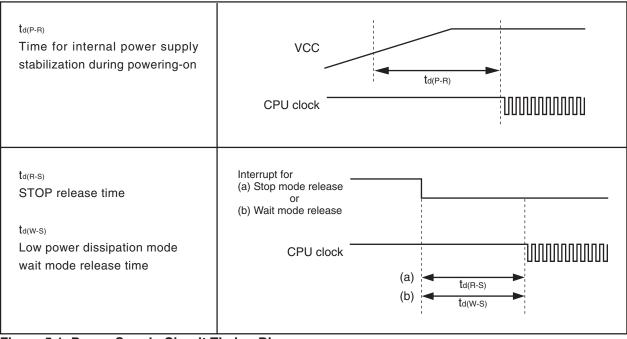

#### Table 5.10 Power Supply Circuit Timing Characteristics

| Symbol  | Parameter                                                       | Measuring          | S    | standar | d    | Unit |

|---------|-----------------------------------------------------------------|--------------------|------|---------|------|------|

| Symbol  |                                                                 | Condition          | Min. | Тур.    | Max. | Onit |

| td(P-R) | Time for internal power supply stabilization during powering-on | VCC = 3.0 to 5.5 V |      |         | 2    | ms   |

| td(R-S) | STOP release time                                               |                    |      |         | 150  | μs   |

| td(W-S) | Low power dissipation mode wait mode release time               |                    |      |         | 150  | μs   |

Figure 5.1 Power Supply Circuit Timing Diagram

## Timing Requirements VCC = 5 V(Referenced to VCC = 5 V, VSS = 0 V, at Topr = -40 to 85°C unless otherwise specified)

## Table 5.11 External Clock Input (XIN Input)

| Symbol            | Parameter                             | Stan | Unit |      |

|-------------------|---------------------------------------|------|------|------|

| Symbol            | Falailletei                           | Min. | Max. | Unit |

| tc                | External clock input cycle time       | 62.5 |      | ns   |

| t <sub>w(H)</sub> | External clock input HIGH pulse width | 25   |      | ns   |

| tw(L)             | External clock input LOW pulse width  | 25   |      | ns   |

| tr                | External clock rise time              |      | 15   | ns   |

| tr                | External clock fall time              |      | 15   | ns   |

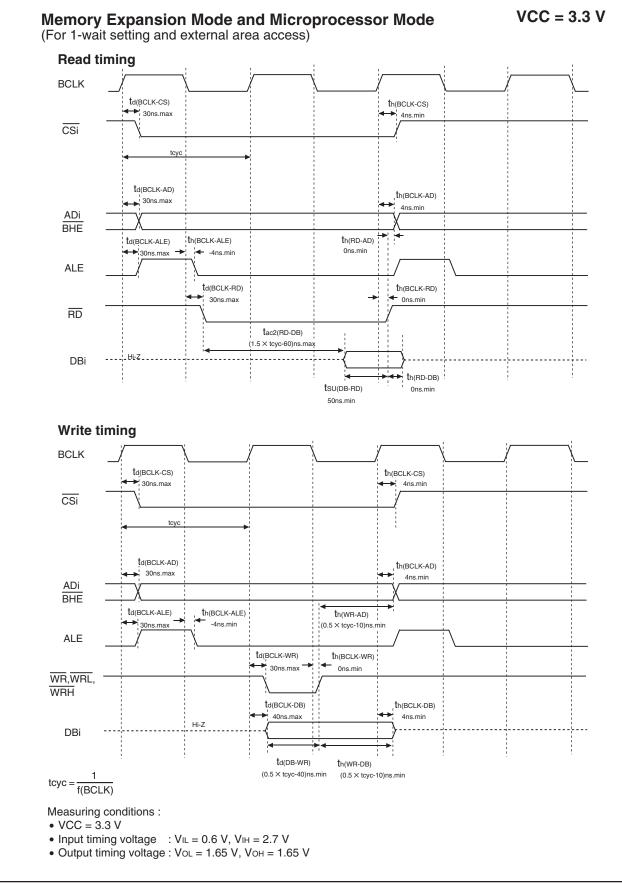

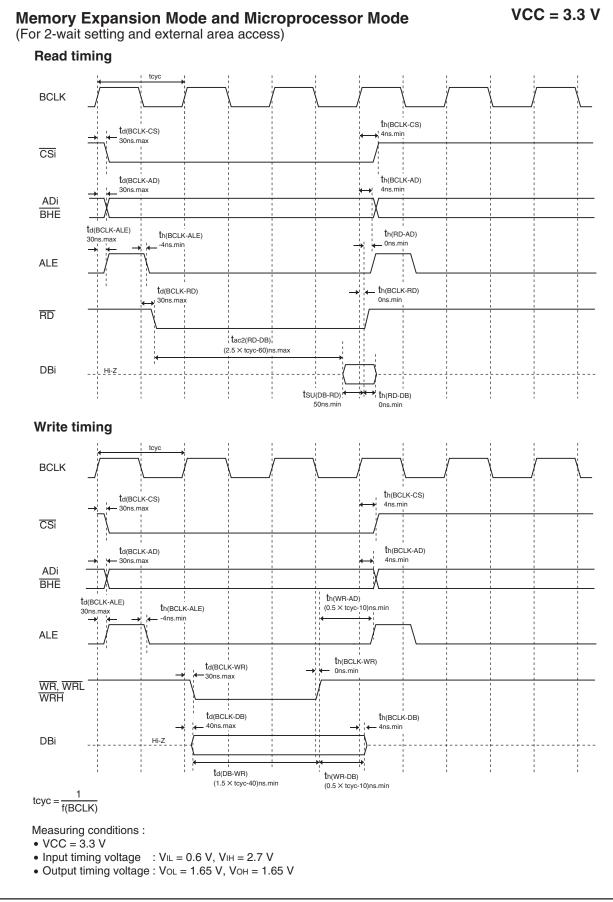

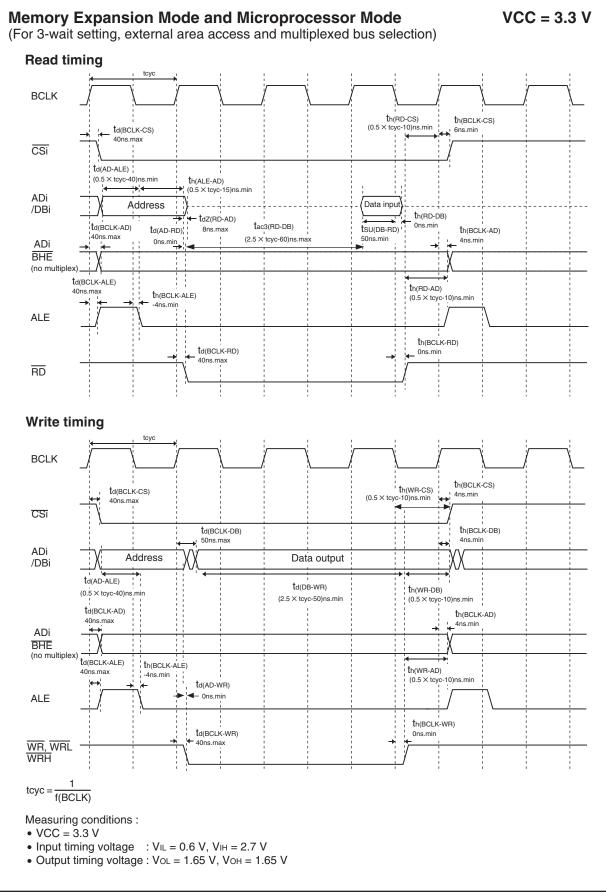

## Table 5.12 Memory Expansion Mode and Microprocessor Mode

| Symbol         | Parameter                                                    | Standard |          | Unit |

|----------------|--------------------------------------------------------------|----------|----------|------|

| Symbol         | Falameter                                                    | Min.     | Max.     | Unit |

| tac1(RD-DB)    | Data input access time (for setting with no wait)            |          | (NOTE 1) | ns   |

| tac2(RD-DB)    | Data input access time (for setting with wait)               |          | (NOTE 2) | ns   |

| tac3(RD-DB)    | Data input access time (when accessing multiplexed bus area) |          | (NOTE 3) | ns   |

| tsu(DB-RD)     | Data input setup time                                        | 40       |          | ns   |

| tsu(RDY-BCLK)  | RDY input setup time                                         | 30       |          | ns   |

| tsu(HOLD-BCLK) | HOLD input setup time                                        | 40       |          | ns   |

| th(RD-DB)      | Data input hold time                                         | 0        |          | ns   |

| th(BCLK-RDY)   | RDY input hold time                                          | 0        |          | ns   |

| th(BCLK-HOLD)  | HOLD input hold time                                         | 0        |          | ns   |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{\text{f(BCLK)}} - 45 \text{ [ns]}$$

2. Calculated according to the BCLK frequency as follows:

$\frac{(n-0.5) \times 10^9}{f(BCLK)} - 45 \text{ [ns]}$  n is "2" for 1-wait setting, "3" for 2-wait setting and "4" for 3-wait setting.

3. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5) \times 10^9}{f(BCLK)} - 45 \text{ [ns]} \qquad n \text{ is "2" for 2-wait setting, "3" for 3-wait setting.}$$

## Timing Requirements VCC = 5 V (Referenced to VCC = 5 V, VSS = 0 V, at Topr = -40 to 85°C unless otherwise specified)

## Table 5.19 Timer B Input (Counter Input in Event Counter Mode)

| Symbol              | Parameter                                            | Stan | Unit |      |

|---------------------|------------------------------------------------------|------|------|------|

|                     | Farameter                                            | Min. | Max. | Unit |

| tc(TB)              | TBiIN input cycle time (counted on one edge)         | 100  |      | ns   |

| t <sub>w(TBH)</sub> | TBiIN input HIGH pulse width (counted on one edge)   | 40   |      | ns   |

| tw(TBL)             | TBiIN input LOW pulse width (counted on one edge)    | 40   |      | ns   |

| tc(TB)              | TBiIN input cycle time (counted on both edges)       | 200  |      | ns   |

| t <sub>w(TBH)</sub> | TBiIN input HIGH pulse width (counted on both edges) | 80   |      | ns   |

| tw(TBL)             | TBiIN input LOW pulse width (counted on both edges)  | 80   |      | ns   |

#### Table 5.20 Timer B Input (Pulse Period Measurement Mode)

| Symbol             | Parameter                    | Stan | Unit |      |

|--------------------|------------------------------|------|------|------|

|                    |                              | Min. | Max. | Unit |

| t <sub>c(TB)</sub> | TBIIN input cycle time       | 400  |      | ns   |

| tw(TBH)            | TBiIN input HIGH pulse width | 200  |      | ns   |

| tw(TBL)            | TBiIN input LOW pulse width  | 200  |      | ns   |

#### Table 5.21 Timer B Input (Pulse Width Measurement Mode)

| Symbol             | Parameter                    | Stan | Unit |    |

|--------------------|------------------------------|------|------|----|

|                    | Farameter                    | Min. | Max. |    |

| t <sub>c(TB)</sub> | TBiIN input cycle time       | 400  |      | ns |

| tw(TBH)            | TBiIN input HIGH pulse width | 200  |      | ns |

| tw(TBL)            | TBiIN input LOW pulse width  | 200  |      | ns |

#### Table 5.22 A/D Trigger Input

| Cumbol  | Parametar                                     | Stan | Linit |      |

|---------|-----------------------------------------------|------|-------|------|

| Symbol  | Parameter                                     | Min. | Max.  | Unit |

| tc(AD)  | ADTRG input cycle time (trigger able minimum) | 1000 |       | ns   |

| tw(ADL) | ADTRG input LOW pulse width                   | 125  |       | ns   |

## Table 5.23 Serial Interface

| Symbol              | Parameter                   | Stan | Unit |      |

|---------------------|-----------------------------|------|------|------|

|                     |                             | Min. | Max. | Unit |

| tc(CK)              | CLKi input cycle time       | 200  |      | ns   |

| t <sub>w(CKH)</sub> | CLKi input HIGH pulse width | 100  |      | ns   |

| tw(CKL)             | CLKi input LOW pulse width  | 100  |      | ns   |

| td(C-Q)             | TXDi output delay time      |      | 80   | ns   |

| th(C-Q)             | TXDi hold time              | 0    |      | ns   |

| tsu(D-C)            | RXDi input setup time       | 70   |      | ns   |

| th(C-D)             | RXDi input hold time        | 90   |      | ns   |

#### Table 5.24 External Interrupt INTi Input

| Symbol              | Symbol Parameter            | Stan | Unit |      |

|---------------------|-----------------------------|------|------|------|

| Symbol              |                             | Min. | Max. | Unit |

| t <sub>w(INH)</sub> | INTi input HIGH pulse width | 250  |      | ns   |

| t <sub>w(INL)</sub> | INTi input LOW pulse width  | 250  |      | ns   |

## Switching Characteristics VCC = 5 V(Referenced to VCC = 5 V, VSS = 0 V, at Topr = -40 to 85 °C unless otherwise specified)

| Symbol           | Parameter                                          | Measuring  | Standard |      | Unit |

|------------------|----------------------------------------------------|------------|----------|------|------|

| Symbol           | Falalletei                                         | Condition  | Min.     | Max. | Onit |

| td(BCLK-AD)      | Address output delay time                          | Figure 5.2 |          | 25   | ns   |

| th(BCLK-AD)      | Address output hold time (in relation to BCLK)     |            | 4        |      | ns   |

| th(RD-AD)        | Address output hold time (in relation to RD)       |            | 0        |      | ns   |

| th(WR-AD)        | Address output hold time (in relation to WR)       |            | (NOTE 1) |      | ns   |

| td(BCLK-CS)      | Chip select output delay time                      |            |          | 25   | ns   |