# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT       |

| Number of I/O              | 66                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 64K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                            |

| Data Converters            | A/D 1x16b; D/A 1x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mks22fn256vll12 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1 System features

The following sections describe the high-level system features.

# 2.1.1 ARM Cortex-M4 core

The ARM Cortex-M4 is the member of the Cortex M Series of processors targeting microcontroller cores focused on very cost sensitive, deterministic, interrupt driven environments. The Cortex M4 processor is based on the ARMv7 Architecture and Thumb®-2 ISA and is upward compatible with the Cortex M3, Cortex M1, and Cortex M0 architectures. Cortex M4 improvements include an ARMv7 Thumb-2 DSP (ported from the ARMv7-A/R profile architectures) providing 32-bit instructions with SIMD (single instruction multiple data) DSP style multiply-accumulates and saturating arithmetic.

# 2.1.2 NVIC

The Nested Vectored Interrupt Controller supports nested interrupts and 16 priority levels for interrupts. In the NVIC, each source in the IPR registers contains 4 bits. It also differs in number of interrupt sources and supports 240 interrupt vectors.

The Cortex-M family uses a number of methods to improve interrupt latency. It also can be used to wake the MCU core from Wait and VLPW modes.

# 2.1.3 AWIC

The asynchronous wake-up interrupt controller (AWIC) is used to detect asynchronous wake-up events in Stop mode and signal to clock control logic to resume system clocking. After clock restarts, the NVIC observes the pending interrupt and performs the normal interrupt or event processing. The AWIC can be used to wake MCU core from Partial Stop, Stop and VLPS modes.

| Reset       | Descriptions         | Modules        |                |                |                |      |                            |     |           |        |

|-------------|----------------------|----------------|----------------|----------------|----------------|------|----------------------------|-----|-----------|--------|

| sources     |                      | РМС            | SIM            | SMC            | RCM            | LLWU | Reset<br>pin is<br>negated | RTC | LPTM<br>R | Others |

|             | MDM DAP system reset | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>4</sup> | Y <sup>5</sup> | Y    | Y                          | Ν   | Ν         | Y      |

| Debug reset | Debug reset          | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>4</sup> | Y <sup>5</sup> | Y    | Y                          | Ν   | Ν         | Y      |

Table 3. Reset source (continued)

1. Except PMC\_LVDSC1[LVDV] and PMC\_LVDSC2[LVWV]

2. Except SIM\_SOPT1

3. Only if  $\overline{\text{RESET}}$  is used to wake from VLLS mode.

4. Except SMC\_PMCTRL, SMC\_STOPCTRL, SMC\_PMSTAT

5. Except RCM\_RPFC, RCM\_RPFW, RCM\_FM

This device supports booting from:

• internal flash

# 2.1.6 Clock options

The MCG module controls which clock source is used to derive the system clocks. The clock generation logic divides the selected clock source into a variety of clock domains, including the clocks for the system bus masters, system bus slaves, and flash memory. The clock generation logic also implements module-specific clock gating to allow granular shutoff of modules.

The primary clocks for the system are generated from the MCGOUTCLK clock. The clock generation circuitry provides several clock dividers that allow different portions of the device to be clocked at different frequencies. This allows for trade-offs between performance and power dissipation.

Various modules, such as the USB OTG Controller, have module-specific clocks that can be generated from the IRC48MCLK or MCGPLLCLK or MCGFLLCLK clock. In addition, there are various other module-specific clocks that have other alternate sources. Clock selection for most modules is controlled by the SOPT registers in the SIM module.

For more details on the clock operations and configurations, see the Clock Distribution chapter in the Reference Manual.

The following figure is a high level block diagram of the clock generation.

# 2.2.1 eDMA and DMAMUX

The eDMA is a highly programmable data-transfer engine optimized to minimize any required intervention from the host processor. It is intended for use in applications where the data size to be transferred is statically known and not defined within the transferred data itself. The DMA controller in this device implements 16 channels which can be routed from up to 63 DMA request sources through DMA MUX module.

Main features of eDMA are listed below:

- All data movement via dual-address transfers: read from source, write to destination

- 16-channel implementation that performs complex data transfers with minimal intervention from a host processor

- Transfer control descriptor (TCD) organized to support two-deep, nested transfer operations

- Channel activation via one of three methods

- Fixed-priority and round-robin channel arbitration

- Channel completion reported via programmable interrupt requests

- Programmable support for scatter/gather DMA processing

- Support for complex data structures

# 2.2.2 TPM

This device contains three low power Timer/PWM Modules (TPM), one with 6 channels and the other two with 2 channels. All TPM modules are functional in Stop/VLPS mode if the clock source is enabled.

The TPM features are as follows:

- TPM clock mode is selectable (can increment on every edge of the asynchronous counter clock, or only on on rising edge of an external clock input synchronized to the asynchronous counter clock)

- Prescaler divide-by 1, 2, 4, 8, 16, 32, 64, or 128

- Include a 16-bit counter

- Include 6 or 2 channels (1×6ch, 2×2ch) that can be configured for input capture, output compare, edge-aligned PWM mode, or center-aligned PWM mode

- Support the generation of an interrupt and/or DMA request per channel or counter overflow

# 4.3.3 Clock Modules

| Chip signal name | Module signal<br>name | Description                     | I/O |

|------------------|-----------------------|---------------------------------|-----|

| EXTAL0           | EXTAL                 | External clock/Oscillator input | I   |

| XTAL0            | XTAL                  | Oscillator output               | 0   |

Table 13.

OSC Signal Descriptions

#### Table 14. RTC OSC Signal Descriptions

| Chip signal name | Module signal<br>name | Description                  | I/O |

|------------------|-----------------------|------------------------------|-----|

| EXTAL32          | EXTAL32               | 32.768 kHz oscillator input  | I   |

| XTAL32           | XTAL32                | 32.768 kHz oscillator output | 0   |

# 4.3.4 Analog

#### Table 15. ADC 0 Signal Descriptions

| Chip signal name | Module signal<br>name | Description                        | I/O |

|------------------|-----------------------|------------------------------------|-----|

| ADC0_DP[3:0]     | DADP3-DADP0           | Differential Analog Channel Inputs | I   |

| ADC0_DM[3:0]     | DADM3-DADM0           | Differential Analog Channel Inputs | I   |

| ADC0_SEn         | ADn                   | Single-Ended Analog Channel Inputs | I   |

| VREFH            | V <sub>REFSH</sub>    | Voltage Reference Select High      | I   |

| VREFL            | V <sub>REFSL</sub>    | Voltage Reference Select Low       | I   |

| VDDA             | V <sub>DDA</sub>      | Analog Power Supply                | I   |

| VSSA             | V <sub>SSA</sub>      | Analog Ground                      | I   |

#### Table 16. CMP 0 Signal Descriptions

| Chip signal name | Module signal<br>name | Description           | I/O |

|------------------|-----------------------|-----------------------|-----|

| CMP0_IN[5:0]     | IN[5:0]               | Analog voltage inputs | I   |

| CMP0_OUT         | CMPO                  | Comparator output     | 0   |

### Table 17. DAC 0 Signal Descriptions

| Chip signal name | Module signal<br>name | Description | I/O |

|------------------|-----------------------|-------------|-----|

| DAC0_OUT         | _                     | DAC output  | 0   |

| Chip signal name | Module signal<br>name | Description      | I/O    |

|------------------|-----------------------|------------------|--------|

| CAN1_RX          | CAN Rx                | CAN Receive Pin  | Input  |

| CAN1_TX          | CAN Tx                | CAN Transmit Pin | Output |

### Table 26. CAN 1 (for KS22 only) Signal Descriptions

### Table 27. SPI 0 Signal Descriptions

| Chip signal name | Module signal<br>name | Description                                             | I/O |

|------------------|-----------------------|---------------------------------------------------------|-----|

| SPI0_PCS0        | PCS0/SS               | Peripheral Chip Select 0 (O)                            | I/O |

| SPI0_PCS[3:1]    | PCS[1:3]              | Peripheral Chip Selects 1–3                             | 0   |

| SPI0_PCS4        | PCS4                  | Peripheral Chip Select 4                                | 0   |

| SPI0_PCS5        | PCS5/ PCSS            | Peripheral Chip Select 5 /Peripheral Chip Select Strobe | 0   |

| SPI0_SIN         | SIN                   | Serial Data In                                          | I   |

| SPI0_SOUT        | SOUT                  | Serial Data Out                                         | 0   |

| SPI0_SCK         | SCK                   | Serial Clock (O)                                        | I/O |

### Table 28. SPI 1 Signal Descriptions

| Chip signal name | Module signal<br>name | Description                  | I/O |

|------------------|-----------------------|------------------------------|-----|

| SPI1_PCS0        | PCS0/SS               | Peripheral Chip Select 0 (O) | I/O |

| SPI1_PCS[3:1]    | PCS[1:3]              | Peripheral Chip Selects 1–3  | 0   |

| SPI1_SIN         | SIN                   | Serial Data In               | I   |

| SPI1_SOUT        | SOUT                  | Serial Data Out              | 0   |

| SPI1_SCK         | SCK                   | Serial Clock (O)             | I/O |

### Table 29. LPI<sup>2</sup>C 0 Signal Descriptions

| Chip signal name | Module signal<br>name | Description                                                                                                        | I/O |

|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------|-----|

| LPI2C0_SCL       | SCL                   | LPI2C clock line.                                                                                                  | I/O |

| LPI2C0_SDA       | SDA                   | LPI2C data line.                                                                                                   | I/O |

| LPI2C0_HREQ      | HREQ                  | Host request, can initiate an LPI2C master transfer if asserted and the I2C bus is idle.                           | I   |

| LPI2C0_SCLS      | SCLS                  | Secondary I2C clock line. If LPI2C master/slave are configured to use separate pins, this the LPI2C slave SCL pin. | I/O |

| LPI2C0_SDAS      | SDAS                  | Secondary I2C data line. If LPI2C master/slave are configured to use separate pins, this the LPI2C slave SDA pin.  | I/O |

#### Pinouts

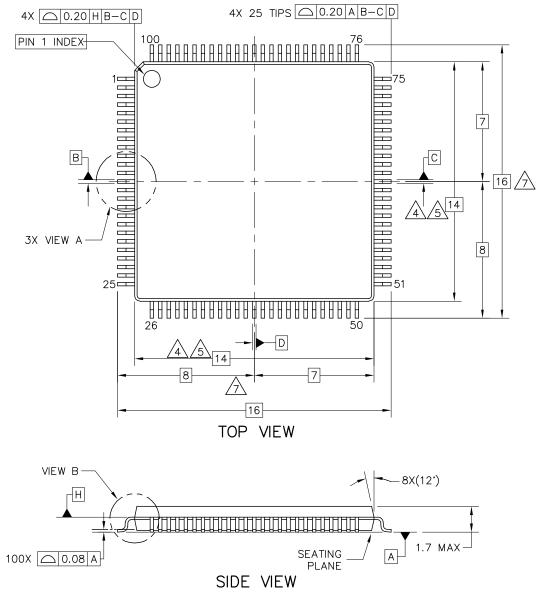

Figure 9. 100-pin LQFP package dimensions 1

| Symbol | Description                    | Min. | Тур. | Max. | Unit | Notes |

|--------|--------------------------------|------|------|------|------|-------|

|        | <ul> <li>LLS2 → RUN</li> </ul> |      |      |      |      |       |

|        |                                | —    |      | 6    | μs   |       |

|        | • LLS3 → RUN                   |      |      |      |      |       |

|        |                                | —    | —    | 6    | μs   |       |

|        | <ul> <li>VLPS → RUN</li> </ul> |      |      |      |      |       |

|        |                                | —    | —    | 5.7  | μs   |       |

|        | <ul> <li>STOP → RUN</li> </ul> |      |      |      |      |       |

|        |                                | —    | —    | 5.7  | μs   |       |

Table 44. Power mode transition operating behaviors (continued)

1. Normal boot (FTFA\_FOPT[LPBOOT]=1)

### 5.3.2.5 Power consumption operating behaviors

The maximum values stated in the following table represent the characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

### NOTE

The while(1) test is executed with flash cache enabled.

| Symbol                | Description                                                                                                      | Min. | Тур.  | Max.     | Unit | Notes   |

|-----------------------|------------------------------------------------------------------------------------------------------------------|------|-------|----------|------|---------|

| I <sub>DDA</sub>      | Analog supply current                                                                                            |      |       | See note | mA   | 1       |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current - all peripheral<br>clocks disabled, CoreMark benchmark code<br>executing from flash |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           | —    | 24.17 | 26.215   | mA   | 2, 3, 4 |

|                       | @ 3.0V                                                                                                           | —    | 24.20 | 26.292   | mA   |         |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current - all peripheral clocks disabled, code executing from flash                          |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           | —    | 20.97 | 23.015   | mA   | 2       |

|                       | @ 3.0V                                                                                                           | —    | 20.97 | 23.062   | mA   |         |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current — all peripheral clocks enabled, code executing from flash                           |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           | —    | 27.77 | 30.028   | mA   | 5       |

|                       | @ 3.0V                                                                                                           | —    | 27.79 | 30.083   | mA   |         |

| I <sub>DD_RUN</sub>   | Run mode current in Compute operation —<br>CoreMark benchmark code executing from<br>flash                       |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           | —    | 15.58 | 16.790   | mA   | 3, 4, 6 |

|                       | @ 3.0V                                                                                                           | —    | 16.19 | 17.457   | mA   |         |

Table 45.

Power consumption operating behaviors

Table continues on the next page ...

| Symbol                | Description                                                                    | Min. | Тур.  | Max.   | Unit | Notes                 |

|-----------------------|--------------------------------------------------------------------------------|------|-------|--------|------|-----------------------|

|                       | @ -40°C                                                                        |      | 1.55  | 2.485  | μA   | Ì                     |

|                       | @ 70°C                                                                         | _    | 5.81  | 9.658  | μA   |                       |

|                       | @ 85°C                                                                         | _    | 10.06 | 16.695 | μA   |                       |

|                       | @ 105°C                                                                        |      | 22.30 | 35.783 | μA   |                       |

| I <sub>DD_VLLS2</sub> | Very low-leakage stop mode 2 current at 3.0 V                                  |      |       |        |      |                       |

|                       | @ 25°C                                                                         | _    | 1.76  | 2.298  | μA   |                       |

|                       | @ -40°C                                                                        | _    | 1.51  | 1.963  | μA   |                       |

|                       | @ 70°C                                                                         | _    | 3.73  | 5.221  | μA   |                       |

|                       | @ 85°C                                                                         | _    | 6.12  | 8.624  | μA   |                       |

|                       | @ 105°C                                                                        |      | 13.22 | 18.408 | μA   |                       |

| I <sub>DD_VLLS1</sub> | Very low-leakage stop mode 1 current at 3.0 V                                  |      |       |        |      |                       |

|                       | @ 25°C                                                                         | _    | 0.64  | 0.835  | μA   |                       |

|                       | @ -40°C                                                                        | _    | 0.55  | 0.795  | μA   |                       |

|                       | @ 70°C                                                                         | _    | 1.88  | 2.427  | μA   |                       |

|                       | @ 85°C                                                                         |      | 3.52  | 4.640  | μA   |                       |

|                       | @ 105°C                                                                        | —    | 8.62  | 11.273 | μA   |                       |

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current at 3.0 V with POR detect circuit enabled  |      |       |        |      |                       |

|                       | @ 25°C                                                                         | _    | 0.36  | 0.525  | μA   |                       |

|                       | @ -40°C                                                                        |      | 0.29  | 0.513  | μA   |                       |

|                       | @ 70°C                                                                         |      | 1.58  | 2.108  | μA   |                       |

|                       | @ 85°C                                                                         |      | 3.19  | 4.289  | μA   |                       |

|                       | @ 105°C                                                                        | _    | 8.20  | 10.838 | μA   |                       |

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current at 3.0 V with POR detect circuit disabled |      |       |        |      |                       |

|                       | @ 25°C                                                                         | _    | 0.093 | 0.249  | μA   |                       |

|                       | @ -40°C                                                                        | _    | 0.016 | 0.145  | μA   |                       |

|                       | @ 70°C                                                                         | _    | 1.30  | 1.821  | μA   |                       |

|                       | @ 85°C                                                                         | _    | 2.91  | 3.994  | μA   |                       |

|                       | @ 105°C                                                                        |      | 7.92  | 10.501 | μA   |                       |

| I <sub>DD_VBAT</sub>  | Average current with RTC and 32kHz disabled at 3.0 V                           |      |       |        |      | V <sub>DD</sub> is of |

|                       | @ 25°C                                                                         |      | 0.21  | 0.245  | μA   |                       |

|                       | @ -40°C                                                                        |      | 0.14  | 0.163  | μA   |                       |

|                       | @ 70°C                                                                         |      | 1.15  | 1.498  | μA   |                       |

|                       | @ 85°C                                                                         |      | 2.44  | 3.596  | μA   |                       |

|                       | @ 105°C                                                                        |      | 6.49  | 9.557  | μA   |                       |

| I <sub>DD_VBAT</sub>  | Average current when CPU is not accessing RTC registers at 3.0 V               |      |       |        |      | V <sub>DD</sub> is of |

|                       | • @ 25°C                                                                       |      | 0.76  | 0.899  | μA   |                       |

Table 45.

Power consumption operating behaviors (continued)

Table continues on the next page...

| Symbol                   | Description                                            | Min. | Max.  | Unit |

|--------------------------|--------------------------------------------------------|------|-------|------|

|                          | High Speed run mode                                    |      | ł     |      |

| f <sub>SYS</sub>         | System and core clock                                  | _    | 120   | MHz  |

| f <sub>BUS</sub>         | Bus clock                                              |      | 60    | MHz  |

|                          | Normal run mode                                        |      |       |      |

| f <sub>SYS</sub>         | System and core clock                                  |      | 80    | MHz  |

| f <sub>SYS_USB</sub>     | System and core clock when Full Speed USB in operation | 20   | _     | MHz  |

| f <sub>BUS</sub>         | Bus clock                                              |      | 50    | MHz  |

| f <sub>FLASH</sub>       | Flash clock                                            |      | 26.67 | MHz  |

| f <sub>LPTMR</sub>       | LPTMR clock                                            |      | 25    | MHz  |

|                          | VLPR and VLPS modes <sup>1</sup>                       |      | ·     |      |

| f <sub>SYS</sub>         | System and core clock                                  |      | 4     | MHz  |

| f <sub>BUS</sub>         | Bus clock                                              |      | 4     | MHz  |

| f <sub>FLASH</sub>       | Flash clock                                            |      | 1     | MHz  |

| f <sub>ERCLK</sub>       | External reference clock                               |      | 16    | MHz  |

| f <sub>LPTMR_pin</sub>   | LPTMR clock                                            |      | 25    | MHz  |

| f <sub>LPTMR_ERCLK</sub> | LPTMR external reference clock                         |      | 16    | MHz  |

| f <sub>I2S_MCLK</sub>    | I2S master clock                                       | _    | 12.5  | MHz  |

| f <sub>I2S_BCLK</sub>    | I2S bit clock                                          | _    | 4     | MHz  |

| f <sub>FlexIO</sub>      | FlexIO clock                                           | —    | 16    | MHz  |

| f <sub>LPI2C</sub>       | LPI2C clock                                            | _    | 16    | MHz  |

| f <sub>FlexCAN</sub>     | FlexCAN clock                                          |      | 4     | MHz  |

### 5.3.3.1 Device clock specifications Table 48. Device clock specifications

The frequency limitations in VLPR and VLPS modes here override any frequency specification listed in the timing specification for any other module. These same frequency limits apply to VLPS, whether VLPS was entered from RUN or from VLPR.

# 5.3.3.2 General switching specifications

These general purpose specifications apply to all signals configured for GPIO, UART, and timers.

| Symbol | Description                                                                        | Min. | Max. | Unit                | Notes |

|--------|------------------------------------------------------------------------------------|------|------|---------------------|-------|

|        | GPIO pin interrupt pulse width (digital glitch filter disabled) — Synchronous path | 1.5  | —    | Bus clock<br>cycles | 1, 2  |

|        | External RESET and NMI pin interrupt pulse width — Asynchronous path               | 100  |      | ns                  | 3     |

Table 49. General switching specifications

Table continues on the next page...

| Board type        | Symbol            | Description                                                                                              | 100<br>LQFP | 64 LQFP | 48 QFN | Unit | Notes     |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|-------------|---------|--------|------|-----------|

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 46          | 43      | 28     | °C/W | 1, 2, 3,4 |

| Single-layer (1s) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 48          | 49      | 66     | °C/W | 1, 4, 5   |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 40          | 36      | 23     | °C/W | 1, 4, 5   |

| _                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 31          | 25      | 11     | °C/W | 6         |

| _                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 16          | 13      | 1.3    | °C/W | 7         |

| _                 | Ψ <sub>JT</sub>   | Thermal characterization<br>parameter, junction to package<br>top outside center (natural<br>convection) | 2           | 2       | 2      | °C/W | 8         |

| _                 | Ψ <sub>JB</sub>   | Thermal characterization<br>parameter, junction to package<br>bottom (natural convection)                | -           | -       | -      | °C/W | 9         |

| Table 51. | Thermal attributes | s (continued) |

|-----------|--------------------|---------------|

|-----------|--------------------|---------------|

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 4. Per JEDEC JESD51-6 with the board horizontal.

- 5. Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 6. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 7. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 8. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 9. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

# 5.4 Peripheral operating requirements and behaviors

# 5.4.1 Debug modules

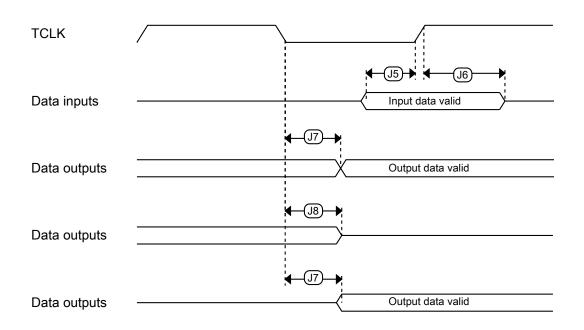

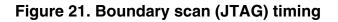

| Symbol               | Description                               | Min. | Тур. | Max. | Unit | Notes |

|----------------------|-------------------------------------------|------|------|------|------|-------|

| t <sub>pgm4</sub>    | Program Longword execution time           | —    | 65   | 145  | μs   | —     |

| t <sub>ersscr</sub>  | Erase Flash Sector execution time         | —    | 14   | 114  | ms   | 2     |

| t <sub>rd1all</sub>  | Read 1s All Blocks execution time         | —    | —    | 1.8  | ms   | 1     |

| t <sub>rdonce</sub>  | Read Once execution time                  | —    | —    | 30   | μs   | 1     |

| t <sub>pgmonce</sub> | Program Once execution time               | —    | 100  | —    | μs   | _     |

| t <sub>ersall</sub>  | Erase All Blocks execution time           | —    | 175  | 1300 | ms   | 2     |

| t <sub>vfykey</sub>  | Verify Backdoor Access Key execution time | —    | —    | 30   | μs   | 1     |

#### Table 62. Flash command timing specifications (continued)

1. Assumes 25 MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

### 5.4.4.1.3 Flash high voltage current behaviors Table 63. Flash high voltage current behaviors

| Symbol              | Description                                                              | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage<br>flash programming operation | —    | 2.5  | 6.0  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation          |      | 1.5  | 4.0  | mA   |

#### 5.4.4.1.4 Reliability specifications Table 64. NVM reliability specifications

| Symbol                  | Description                            | Min.    | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|-------------------------|----------------------------------------|---------|-------------------|------|--------|-------|

|                         | Program                                | n Flash |                   |      |        |       |

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5       | 50                | _    | years  | _     |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20      | 100               | _    | years  | _     |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K    | 50 K              | _    | cycles | 2     |

1. Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25 °C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40 °C  $\leq$  T<sub>i</sub>  $\leq$  125 °C.

# 5.4.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

| Symbol          | Description                     | Conditions <sup>1</sup>                                                     | Min.         | Typ. <sup>2</sup> | Max.            | Unit             | Notes                    |

|-----------------|---------------------------------|-----------------------------------------------------------------------------|--------------|-------------------|-----------------|------------------|--------------------------|

|                 |                                 | • ADLPC = 1, ADHSC = 1                                                      | 2.4          | 4.0               | 6.1             | MHz              |                          |

|                 |                                 | • ADLPC = 0, ADHSC = 0                                                      | 3.0          | 5.2               | 7.3             | MHz              |                          |

|                 |                                 | • ADLPC = 0, ADHSC = 1                                                      | 4.4          | 6.2               | 9.5             | MHz              |                          |

|                 | Sample Time                     | See Reference Manual chapter                                                | for sample   | times             |                 |                  |                          |

| TUE             | Total unadjusted                | <ul> <li>12-bit modes</li> </ul>                                            | _            | ±4                | ±6.8            | LSB <sup>4</sup> | 5                        |

|                 | error                           | • <12-bit modes                                                             | —            | ±1.4              | ±2.1            |                  |                          |

| DNL             | Differential non-<br>linearity  | 12-bit modes                                                                | _            | ±0.7              | -1.1 to<br>+1.9 | LSB <sup>4</sup> | 5                        |

|                 | linearity                       | <ul> <li>&lt;12-bit modes</li> </ul>                                        | —            | ±0.2              | -0.3 to<br>0.5  |                  |                          |

| INL             | Integral non-linearity          | 12-bit modes                                                                | —            | ±1.0              | -2.7 to<br>+1.9 | LSB <sup>4</sup> | 5                        |

|                 |                                 | <ul> <li>&lt;12-bit modes</li> </ul>                                        | _            | ±0.5              | -0.7 to<br>+0.5 |                  |                          |

| E <sub>FS</sub> | Full-scale error                | 12-bit modes                                                                | _            | -4                | -5.4            | LSB <sup>4</sup> | $V_{ADIN} = V_{DDA}^{4}$ |

|                 |                                 | <ul> <li>&lt;12-bit modes</li> </ul>                                        | _            | -1.4              | -1.8            |                  |                          |

| EQ              | Quantization error              | 16-bit modes                                                                |              | -1 to 0           | _               | LSB <sup>4</sup> |                          |

|                 |                                 | <ul> <li>≤13-bit modes</li> </ul>                                           | —            | _                 | ±0.5            |                  |                          |

| ENOB            | Effective number of             | 16-bit differential mode                                                    |              |                   |                 |                  | 6                        |

|                 | bits                            | • Avg = 32                                                                  | 12.8         | 14.5              | —               | bits             |                          |

|                 |                                 | • Avg = 4                                                                   | 11.9         | 13.8              | _               | bits             |                          |

|                 |                                 | <ul><li>16-bit single-ended mode</li><li>Avg = 32</li><li>Avg = 4</li></ul> | 12.2<br>11.4 | 13.9<br>13.1      | _               | bits             |                          |

| SINAD           | Signal-to-noise plus distortion | See ENOB                                                                    | 6.02 ×       | ENOB +            | 1.76            | dB               |                          |

| THD             | Total harmonic distortion       | 16-bit differential mode                                                    |              |                   |                 | dB               | 7                        |

|                 |                                 | • Avg = 32                                                                  | —            | -94               | _               | dB               |                          |

|                 |                                 | <ul><li>16-bit single-ended mode</li><li>Avg = 32</li></ul>                 | _            | -85               | _               |                  |                          |

| SFDR            | Spurious free<br>dynamic range  | 16-bit differential mode                                                    | 82           | 95                |                 | dB               | 7                        |

|                 |                                 | • Avg = 32                                                                  | <u>,</u>     |                   | _               | dB               |                          |

|                 |                                 | <ul><li>16-bit single-ended mode</li><li>Avg = 32</li></ul>                 | 78           | 90                |                 |                  |                          |

Table continues on the next page...

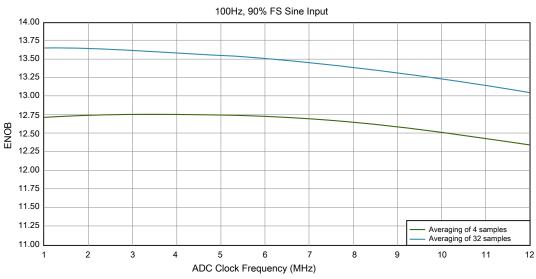

Typical ADC 16-bit Single-Ended ENOB vs ADC Clock

Figure 26. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

#### CMP and 6-bit DAC electrical specifications 5.4.6.2 Table 67. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit             |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------------------|

| V <sub>DD</sub>    | Supply voltage                                      | 1.71                  |      | 3.6             | V                |

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)     | —                     |      | 200             | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)      | —                     | _    | 20              | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                | V <sub>SS</sub> – 0.3 | _    | V <sub>DD</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage                         | —                     | _    | 20              | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |                  |

|                    | • CR0[HYSTCTR] = 00                                 | _                     | 5    | _               | mV               |

|                    | • CR0[HYSTCTR] = 01                                 | _                     | 10   | _               | mV               |

|                    | • CR0[HYSTCTR] = 10                                 | _                     | 20   | _               | mV               |

|                    | • CR0[HYSTCTR] = 11                                 | —                     | 30   | _               | mV               |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 |      | _               | V                |

| V <sub>CMPOI</sub> | Output low                                          | _                     |      | 0.5             | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> | _                     | _    | 40              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   | —                     | 7    | —               | μA               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5                  | _    | 0.5             | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3                  | _    | 0.3             | LSB              |

1. Typical hysteresis is measured with input voltage range limited to 0.6 to V\_{DD}-0.6 V.

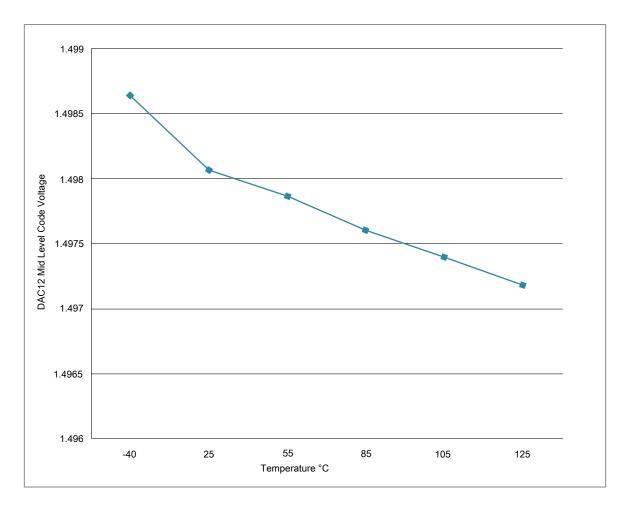

Figure 30. Offset at half scale vs. temperature

# 5.4.7 Timers

See General switching specifications.

# 5.4.8 Communication interfaces

# 5.4.8.1 USB electrical specifications

The USB electricals for the USB On-the-Go module conform to the standards documented by the Universal Serial Bus Implementers Forum. For the most up-to-date standards, visit **usb.org**.

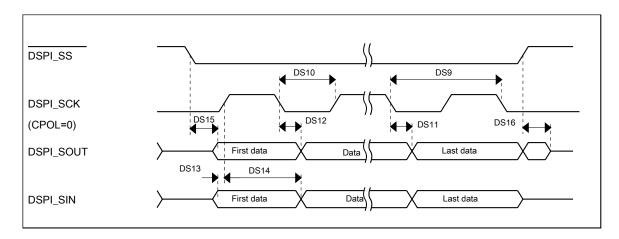

| Num  | Description                              | Min.                      | Max.                     | Unit |

|------|------------------------------------------|---------------------------|--------------------------|------|

|      | Operating voltage                        | 1.71                      | 3.6                      | V    |

|      | Frequency of operation                   | —                         | 7.5                      | MHz  |

| DS9  | DSPI_SCK input cycle time                | 8 x t <sub>BUS</sub>      | _                        | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) - 4 | (t <sub>SCK/2)</sub> + 4 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | —                         | 29.5                     | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                        | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 3.2                       | _                        | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | —                        | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | _                         | 25                       | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | _                         | 25                       | ns   |

# 5.4.8.4 LPI<sup>2</sup>C

| Symbol           | Description         |                           | Min. | Max. | Unit | Notes |

|------------------|---------------------|---------------------------|------|------|------|-------|

| f <sub>SCL</sub> | SCL clock frequency | Standard mode (Sm)        | 0    | 100  | kHz  | 1     |

|                  |                     | Fast mode (Fm)            | 0    | 400  |      | 1, 2  |

|                  |                     | Fast mode Plus (Fm+)      | 0    | 1000 |      | 1, 3  |

|                  |                     | Ultra Fast mode (UFm)     | 0    | 5000 |      | 1, 4  |

|                  |                     | High speed mode (Hs-mode) | 0    | 3400 |      | 1, 5  |

1. See General switching specifications, measured at room temperature.

2. Measured with the maximum bus loading of 400pF at 3.3V VDD with pull-up Rp =  $220\Omega$ , and at 1.8V VDD with Rp =  $880\Omega$ . For all other cases, select appropriate Rp per I2C Bus Specification and the pin drive capability.

Fm+ is only supported on high drive pin with high drive enabled. It is measured with the maximum bus loading of 400pF at 3.3V VDD with Rp = 220Ω. For all other cases, select appropriate Rp per I2C Bus Specification and the pin drive capability.

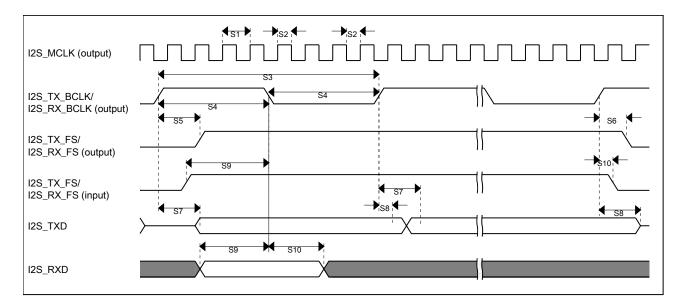

#### Figure 39. I2S/SAI timing — master modes

### Table 80. I2S/SAI slave mode timing in VLPR, VLPW, and VLPS modes (full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                        | 250  | _    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)              | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before<br>I2S_TX_BCLK/I2S_RX_BCLK | 30   | —    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK   | 7    | _    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                     | —    |      | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                   | 0    | _    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                  | 30   | _    | ns          |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                    | 4    | _    | ns          |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup>    |      | 72   | ns          |

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

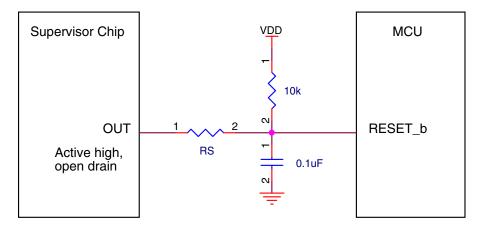

When an external supervisor chip is connected to the RESET\_b pin, a series resistor must be used to avoid damaging the supervisor chip or the RESET\_b pin, as shown in the following figure. The series resistor value (RS below) must be in the range of  $100 \Omega$  to  $1 k\Omega$  depending on the external reset chip drive strength. The supervisor chip must have an active high, open-drain output.

Figure 44. Reset signal connection to external reset chip

• NMI pin

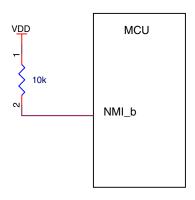

Do not add a pull-down resistor or capacitor on the NMI\_b pin, because a low level on this pin will trigger non-maskable interrupt. When this pin is enabled as the NMI function, an external pull-up resistor ( $10 \text{ k}\Omega$ ) as shown in the following figure is recommended for robustness.

If the NMI\_b pin is used as an I/O pin, the non-maskable interrupt handler is required to disable the NMI function by remapping to another function. The NMI function is disabled by programming the FOPT[NMI\_DIS] bit to zero.

Figure 45. NMI pin biasing

• Debug interface

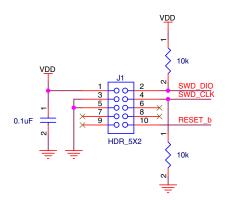

This MCU uses the standard ARM SWD interface protocol as shown in the following figure. While pull-up or pull-down resistors are not required (SWD\_DIO has an internal pull-up and SWD\_CLK has an internal pull-down), external 10 k $\Omega$  pull resistors are recommended for system robustness. The RESET\_b pin recommendations mentioned above must also be considered.

Figure 46. SWD debug interface

• Low leakage stop mode wakeup

Select low leakage wakeup pins (LLWU\_Px) to wake the MCU from one of the low leakage stop modes (LLS/VLLSx). See the pinout table for pin selection.

• Unused pin

Unused GPIO pins must be left floating (no electrical connections) with the MUX field of the pin's PORTx\_PCRn register equal to 0:0:0. This disables the digital input path to the MCU.

If the USB module is not used, leave the USB data pins (USB0\_DP, USB0\_DM) floating. Connect USB\_VDD to ground through a 10 k $\Omega$  resistor if the USB module is not used.

# 6.1.5 Crystal oscillator

When using an external crystal or ceramic resonator as the frequency reference for the MCU clock system, refer to the following table and diagrams.

The feedback resistor, RF, is incorporated internally with the low power oscillators. An external feedback is required when using high gain (HGO=1) mode.

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, Freescale, the Freescale logo and Kinetis are trademarks of NXP B.V.All other product or service names are the property of their respective owners. ARM and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

©2016 NXP B.V.

Document Number KS22P100M120SF0 Revision 3, 04/2016