# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                             |

|----------------------------|--------------------------------------------------------------------|

| Core Processor             | ARM7®                                                              |

| Core Size                  | 16/32-Bit                                                          |

| Speed                      | 10MHz                                                              |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                         |

| Number of I/O              | 14                                                                 |

| Program Memory Size        | 32KB (16K x 16)                                                    |

| Program Memory Type        | FLASH                                                              |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 1K x 32                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.375V ~ 2.625V                                                    |

| Data Converters            | A/D 5x24b, 8x24b; D/A 1x14b                                        |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                      |

| Package / Case             | 48-LQFP                                                            |

| Supplier Device Package    | 48-LQFP (7x7)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7060bstz32 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

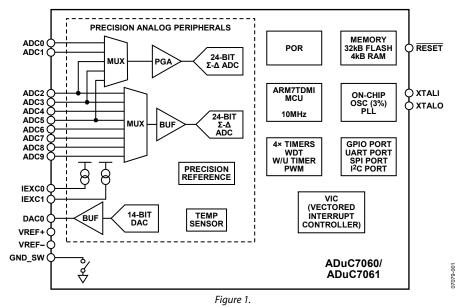

### FUNCTIONAL BLOCK DIAGRAM

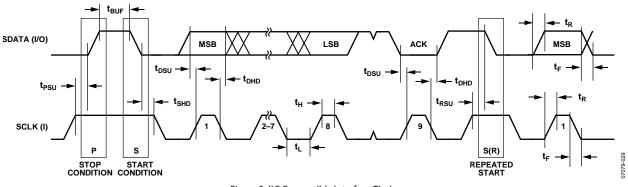

### TIMING SPECIFICATIONS

### I<sup>2</sup>C Timing

### Table 2. I<sup>2</sup>C° Timing in Standard Mode (100 kHz)

|                  |                                                              |    | Slave   |      |

|------------------|--------------------------------------------------------------|----|---------|------|

| Parameter        | Description                                                  | м  | lin Max | Unit |

| tL               | SCLOCK low pulse width                                       | 4. | 7       | μs   |

| tн               | SCLOCK high pulse width                                      | 4. | 0       | ns   |

| t <sub>shd</sub> | Start condition hold time                                    | 4. | 0       | μs   |

| t <sub>DSU</sub> | Data setup time                                              | 25 | 50      | ns   |

| t <sub>DHD</sub> | Data hold time                                               | 0  | 3.45    | μs   |

| t <sub>RSU</sub> | Setup time for repeated start                                | 4. | 7       | μs   |

| t <sub>PSU</sub> | Stop condition setup time                                    | 4. | 0       | μs   |

| t <sub>BUF</sub> | Bus-free time between a stop condition and a start condition | 4. | 7       | μs   |

| t <sub>R</sub>   | Rise time for both CLOCK and SDATA                           |    | 1       | μs   |

| t <sub>F</sub>   | Fall time for both CLOCK and SDATA                           |    | 300     | ns   |

Figure 2. I<sup>2</sup>C Compatible Interface Timing

### Data Sheet

such as C, it is necessary to ensure that the stack does not overflow. This is dependent on the performance of the compiler that is used.

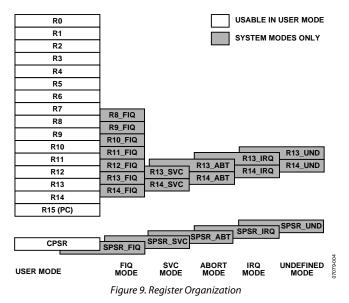

When an exception occurs, some of the standard registers are replaced with registers specific to the exception mode. All exception modes have replacement banked registers for the stack pointer (R13) and the link register (R14) as represented in Figure 9. The FIQ mode has more registers (R8 to R12) supporting faster interrupt processing. With the increased number of noncritical registers, the interrupt can be processed without the need to save or restore these registers, thereby reducing the response time of the interrupt handling process.

More information relative to the programmer's model and the ARM7TDMI core architecture can be found in ARM7TDMI technical and ARM architecture manuals available directly from ARM Ltd.

### INTERRUPT LATENCY

The worst-case latency for an FIQ consists of the longest time that the request can take to pass through the synchronizer, plus the time for the longest instruction to complete (the longest instruction is an LDM) that loads all the registers including the PC, plus the time for the data abort entry, plus the time for FIQ entry. At the end of this time, the ARM7TDMI is executing the instruction at 0x1C (FIQ interrupt vector address). The maximum total time is 50 processor cycles, or just over 4.88 µs in a system using a continuous 10.24 MHz processor clock. The maximum IRQ latency calculation is similar but must allow for the FIQ having higher priority, which can delay entry into the IRQ handling routine for an arbitrary length of time. This time can be reduced to 42 cycles if the LDM command is not used; some compilers have an option to compile without using this command. Another option is to run the part in Thumb mode where this time is reduced to 22 cycles.

The minimum latency for FIQ or IRQ interrupts is five cycles. This consists of the shortest time that the request can take through the synchronizer plus the time to enter the exception mode. Note that the ARM7TDMI initially (first instruction) runs in ARM (32-bit) mode when an exception occurs. The user can immediately switch from ARM mode to Thumb mode if required, for example, when executing interrupt service routines.

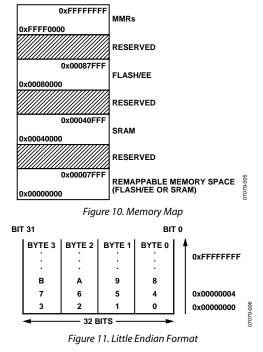

### **MEMORY ORGANIZATION**

The ARM7, a von Neumann architecture MCU core, sees memory as a linear array of 232-byte locations. As shown in Figure 10, the ADuC7060/ADuC7061 maps this into four distinct user areas: a memory area that can be remapped, an SRAM area, a Flash/EE area, and a memory mapped register (MMR) area.

The first 30 kB of this memory space is used as an area into which the on-chip Flash/EE or SRAM can be remapped. Any access, either reading or writing, to an area not defined in the memory map results in a data abort exception.

### **Memory Format**

The ADuC7060/ADuC7061 memory organization is configured in little endian format: the least significant byte is located in the lowest byte address and the most significant byte in the highest byte address (see Figure 11).

### SRAM

The ADuC7060/ADuC7061 features 4 kB of SRAM, organized as  $1024 \times 32$  bits, that is, 1024 words located at 0x40000. The RAM space can be used as data memory as well as volatile program space.

ARM code can run directly from SRAM at full clock speed given that the SRAM array is configured as a 32-bit wide memory array. SRAM is read/writable in 8-, 16-, and 32-bit segments.

|         |        |       | Access |               |                                  |

|---------|--------|-------|--------|---------------|----------------------------------|

| Address | Name   | Bytes | Туре   | Default Value | Description                      |

| 0x0320  | TOLD   | 4     | R/W    | 0x00000000    | Timer0 load register.            |

| 0x0324  | TOVAL  | 4     | R      | 0xFFFFFFF     | Timer0 value register.           |

| 0x0328  | TOCON  | 4     | R/W    | 0x01000000    | Timer0 control MMR.              |

| 0x032C  | TOCLRI | 1     | W      | N/A           | Timer0 interrupt clear register. |

| 0x0330  | TOCAP  | 4     | R      | 0x00000000    | Timer0 capture register.         |

| 0x0340  | T1LD   | 4     | R/W    | 0x00000000    | Timer1 load register.            |

| 0x0344  | T1VAL  | 4     | R      | 0xFFFFFFFF    | Timer1 value register.           |

| 0x0348  | T1CON  | 2     | R/W    | 0x0000        | Timer1 control MMR.              |

| 0x034C  | T1CLRI | 1     | W      | N/A           | Timer1 interrupt clear register. |

| 0x0360  | T2LD   | 2     | R/W    | 0x3BF8        | Timer2 load register.            |

| 0x0364  | T2VAL  | 2     | R      | 0x3BF8        | Timer2 value register.           |

| 0x0368  | T2CON  | 2     | R/W    | 0x0000        | Timer2 control MMR.              |

| 0x036C  | T2CLRI | 1     | W      | N/A           | Timer2 interrupt clear register. |

| 0x0380  | T3LD   | 2     | R/W    | 0x0000        | Timer3 load register.            |

| 0x0384  | T3VAL  | 2     | R      | 0xFFFF        | Timer3 value register.           |

| 0x0388  | T3CON  | 4     | R/W    | 0x00000000    | Timer3 control MMR.              |

| 0x038C  | T3CLRI | 1     | W      | N/A           | Timer3 interrupt clear register. |

| 0x0390  | T3CAP  | 2     | R      | 0x0000        | Timer3 capture register.         |

### Table 19. Timer Address Base = 0xFFFF0300

### Table 20. PLL Base Address = 0xFFFF0400

| Address | Name    | Bytes | Access<br>Type | Default Value | Description                                                                                                        |

|---------|---------|-------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------|

| 0x0404  | POWKEY1 | 2     | W              | 0xXXXX        | POWCON0 prewrite key.                                                                                              |

| 0x0408  | POWCON0 | 1     | R/W            | 0x7B          | Power control and core speed control register.                                                                     |

| 0x040C  | POWKEY2 | 2     | W              | 0xXXXX        | POWCON0 postwrite key.                                                                                             |

| 0x0410  | PLLKEY1 | 2     | W              | 0xXXXX        | PLLCON prewrite key.                                                                                               |

| 0x0414  | PLLCON  | 1     | R/W            | 0x00          | PLL clock source selection MMR.                                                                                    |

| 0x0418  | PLLKEY2 | 2     | W              | 0xXXXX        | PLLCON postwrite key.                                                                                              |

| 0x0434  | POWKEY3 | 2     | W              | 0xXXXX        | POWCON1 prewrite key.                                                                                              |

| 0x0438  | POWCON1 | 2     | R/W            | 0x124         | Power control register.                                                                                            |

| 0x043C  | POWKEY4 | 2     | W              | 0xXXXX        | POWCON1 postwrite key.                                                                                             |

| 0x0464  | GP0KEY1 | 2     | W              | 0xXXXX        | GP0CON1 prewrite key.                                                                                              |

| 0x0468  | GP0CON1 | 1     | R/W            | 0x00          | Configures P0.0, P0.1, P0.2, and P0.3 as analog inputs or digital I/Os. Also enables SPI or I <sup>2</sup> C mode. |

| 0x046C  | GP0KEY2 | 2     | W              | 0xXXXX        | GP0CON1 postwrite key.                                                                                             |

### Table 21. ADC Address Base = 0xFFFF0500

|         |                     |       | Access |                                           |                                                                                                      |

|---------|---------------------|-------|--------|-------------------------------------------|------------------------------------------------------------------------------------------------------|

| Address | Name                | Bytes | Туре   | Default Value                             | Description                                                                                          |

| 0x0500  | ADCSTA              | 2     | R      | 0x0000                                    | ADC status MMR.                                                                                      |

| 0x0504  | ADCMSKI             | 2     | R/W    | 0x0000                                    | ADC interrupt source enable MMR.                                                                     |

| 0x0508  | ADCMDE              | 1     | R/W    | 0x03                                      | ADC mode register.                                                                                   |

| 0x050C  | ADC0CON             | 2     | R/W    | 0x8000                                    | Primary ADC control MMR.                                                                             |

| 0x0510  | ADC1CON             | 2     | R/W    | 0x0000                                    | Auxiliary ADC control MMR.                                                                           |

| 0x0514  | ADCFLT              | 2     | R/W    | 0x0007                                    | ADC filter control MMR.                                                                              |

| 0x0518  | ADCCFG              | 1     | R/W    | 0x00                                      | ADC configuration MMR.                                                                               |

| 0x051C  | ADC0DAT             | 4     | R      | 0x0000000                                 | Primary ADC result MMR.                                                                              |

| 0x0520  | ADC1DAT             | 4     | R      | 0x0000000                                 | Auxiliary ADC result MMR                                                                             |

| 0x0524  | ADC0OF <sup>1</sup> | 2     | R/W    | 0x0000, part specific, factory programmed | Primary ADC offset calibration setting.                                                              |

| 0x0528  | ADC10F <sup>1</sup> | 2     | R/W    | 0x0000, part specific, factory programmed | Auxiliary ADC offset MMR.                                                                            |

| 0x052C  | ADC0GN1             | 2     | R/W    | 0x5555                                    | Primary ADC offset MMR.                                                                              |

| 0x0530  | ADC1GN <sup>1</sup> | 2     | R/W    | 0x5555                                    | Auxiliary ADC offset MMR. See the ADC operation mode configuration bit (ADCLPMCFG[1:0]) in Table 42. |

| 0x0534  | ADCORCR             | 2     | R/W    | 0x0001                                    | Primary ADC result counter/reload MMR.                                                               |

| 0x0538  | ADCORCV             | 2     | R      | 0x0000                                    | Primary ADC result counter MMR.                                                                      |

| 0x053C  | ADC0TH              | 2     | R/W    | 0x0000                                    | Primary ADC 16-bit comparator threshold MMR.                                                         |

| 0x0540  | ADC0THC             | 2     | R/W    | 0x0001                                    | Primary ADC 16-bit comparator threshold counter limit.                                               |

| 0x0544  | ADC0THV             | 2     | R      | 0x0000                                    | ADC0 8-bit threshold exceeded counter register                                                       |

| 0x0548  | ADC0ACC             | 4     | R      | 0x0000000                                 | Primary ADC accumulator.                                                                             |

| 0x054C  | ADC0ATH             | 4     | R/W    | 0x0000000                                 | Primary ADC 32-bit comparator threshold MMR.                                                         |

| 0x0570  | IEXCON              | 1     | R/W    | 0x00                                      | Excitation current sources control register.                                                         |

<sup>1</sup> Updated by the kernel to part specific calibration value.

#### Table 22. DAC Control Address Base = 0xFFFF0600

| Address | Name    | Bytes | Access<br>Type | Default Value | Description               |

|---------|---------|-------|----------------|---------------|---------------------------|

| 0x0600  | DAC0CON | 2     | R/W            | 0x0200        | DAC control register.     |

| 0x0604  | DAC0DAT | 4     | R/W            | 0x0000000     | DAC output data register. |

### Table 23. UART Base Address = 0xFFFF0700

|         |         |       | Access |               |                                                    |

|---------|---------|-------|--------|---------------|----------------------------------------------------|

| Address | Name    | Bytes | Туре   | Default Value | Description                                        |

| 0x0700  | COMTX   | 1     | W      | N/A           | UART transmit register.                            |

| 0x0700  | COMRX   | 1     | R      | 0x00          | UART receive register.                             |

| 0x0700  | COMDIV0 | 1     | R/W    | 0x00          | UART Standard Baud Rate Generator Divisor Value 0. |

| 0x0704  | COMIEN0 | 1     | R/W    | 0x00          | UART Interrupt Enable MMR 0.                       |

| 0x0704  | COMDIV1 | 1     | R/W    | 0x00          | UART Standard Baud Rate Generator Divisor Value 1. |

| 0x0708  | COMIID0 | 1     | R      | 0x01          | UART Interrupt Identification 0.                   |

| 0x070C  | COMCON0 | 1     | R/W    | 0x00          | UART Control Register 0.                           |

| 0x0710  | COMCON1 | 1     | R/W    | 0x00          | UART Control Register 1.                           |

| 0x0714  | COMSTA0 | 1     | R      | 0x60          | UART Status Register 0.                            |

| 0x0718  | COMSTA1 | 1     | R      | 0x00          | UART Status Register 1.                            |

| 0X072C  | COMDIV2 | 2     | R/W    | 0x0000        | UART fractional divider MMR.                       |

### ADC Interrupt Mask Register

| •              | •                                                                                                                                                                                                                                                                                                                         |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name:          | ADCMSKI                                                                                                                                                                                                                                                                                                                   |

| Address:       | 0xFFFF0504                                                                                                                                                                                                                                                                                                                |

| Default value: | 0x0000                                                                                                                                                                                                                                                                                                                    |

| Access:        | Read and write                                                                                                                                                                                                                                                                                                            |

| Function:      | This register allows the ADC interrupt sources to be enabled individually. The bit positions in this register are the same as the lower eight bits in the ADCSTA MMR. If a bit is set by user code to 1, the respective interrupt is enabled. By default, all bits are 0, meaning all ADC interrupt sources are disabled. |

| Bit | Name            | Description                                                                                        |  |  |  |

|-----|-----------------|----------------------------------------------------------------------------------------------------|--|--|--|

| 7   |                 | Not used. This bit is reserved for future functionality and should not be monitored by user code.  |  |  |  |

| 6   | ADC0ATHEX_INTEN | ADC0 accumulator comparator threshold exceeded interrupt enable bit.                               |  |  |  |

|     |                 | When set to 1, this bit enables an interrupt when the ADC0ATHEX bit in the ADCSTA register is set. |  |  |  |

|     |                 | When this bit is cleared, this interrupt source is disabled.                                       |  |  |  |

| 5   |                 | Not used. This bit is reserved for future functionality and should not be monitored by user code.  |  |  |  |

| 4   | ADC0THEX_INTEN  | Primary channel ADC comparator threshold exceeded interrupt enable bit.                            |  |  |  |

|     |                 | When set to 1, this bit enables an interrupt when the ADC0THEX bit in the ADCSTA register is set.  |  |  |  |

|     |                 | When this bit is cleared, this interrupt source is disabled.                                       |  |  |  |

| 3   | ADC0OVR_INTEN   | When set to 1, this bit enables an interrupt when the ADC0OVR bit in the ADCSTA register is set.   |  |  |  |

|     |                 | When this bit is cleared, this interrupt source is disabled.                                       |  |  |  |

| 2   |                 | Not used. This bit is reserved for future functionality and should not be monitored by user code.  |  |  |  |

| 1   | ADC1RDY_INTEN   | Auxiliary ADC result ready bit.                                                                    |  |  |  |

|     |                 | When set to 1, this bit enables an interrupt when the ADC1RDY bit in the ADCSTA register is set.   |  |  |  |

|     |                 | When this bit is cleared, this interrupt source is disabled.                                       |  |  |  |

| 0   | ADCORDY_INTEN   | Primary ADC result ready bit.                                                                      |  |  |  |

|     |                 | When set to 1, this bit enables an interrupt when the ADC0RDY bit in the ADCSTA register is set.   |  |  |  |

|     |                 | When this bit is cleared, this interrupt source is disabled.                                       |  |  |  |

### Table 41. ADCMSKI MMR Bit Designations

### ADC Mode Register

| Name:          | ADCMDE                                                                                            |

|----------------|---------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF0508                                                                                        |

| Default value: | 0x03                                                                                              |

| Access:        | Read and write                                                                                    |

| Function:      | The ADC mode MMR is an 8-bit register that configures the mode of operation of the ADC subsystem. |

### Table 42. ADCMDE MMR Bit Designations

| Bit | Name      | Description                                                                                        |  |  |  |

|-----|-----------|----------------------------------------------------------------------------------------------------|--|--|--|

| 7   | ADCCLKSEL | Set this bit to 1 to enable ADCCLK = 512 kHz. This bit should be set for normal ADC operation.     |  |  |  |

|     |           | Clear this bit to enable ADCCLK = 131 kHz. This bit should be cleared for low power ADC operation. |  |  |  |

| 6   |           | Not used. This bit is reserved for future functionality and should not be monitored by user code.  |  |  |  |

| 5   | ADCLPMEN  | Enable low power mode. This bit has no effect if ADCMDE[4:3] = 00 (ADC is in normal mode).         |  |  |  |

|     |           | This bit must be set to 1 in low power mode.                                                       |  |  |  |

|     |           | Clearing this bit in low power mode results in erratic ADC results.                                |  |  |  |

### **Data Sheet**

## ADuC7060/ADuC7061

### Primary Channel ADC Data Register

| Name:          | ADC0DAT                                                                                                                                                                                                                                                             |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF051C                                                                                                                                                                                                                                                          |

| Default value: | 0x00000000                                                                                                                                                                                                                                                          |

| Access:        | Read only                                                                                                                                                                                                                                                           |

| Function:      | This ADC data MMR holds the 24-bit<br>conversion result from the primary ADC. The<br>ADC does not update this MMR if the ADC0<br>conversion result ready bit (ADCSTA[0]) is<br>set. A read of this MMR by the MCU clears<br>all asserted ready flags (ADCSTA[1:0]). |

#### Table 49. ADC0DAT MMR Bit Designations

| Bit  | Description                    |

|------|--------------------------------|

| 23:0 | ADC0 24-bit conversion result. |

#### Auxiliary Channel ADC Data Register

| Name:          | ADC1DAT                                                                                                                                                                               |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF0520                                                                                                                                                                            |

| Default value: | 0x0000000                                                                                                                                                                             |

| Access:        | Read only                                                                                                                                                                             |

| Function:      | This ADC data MMR holds the 24-bit<br>conversion result from the auxiliary ADC.<br>The ADC does not update this MMR if the<br>ADC0 conversion result ready bit<br>(ADCSTA[1]) is set. |

#### Table 50. ADC1DAT MMR Bit Designations

| Bit  | Description                    |

|------|--------------------------------|

| 23:0 | ADC1 24-bit conversion result. |

### Primary Channel ADC Offset Calibration Register

| Name:          | ADC0OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF0524                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Default value: | Part specific, factory programmed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Access:        | Read and write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Function:      | This ADC offset MMR holds a 16-bit offset<br>calibration coefficient for the primary ADC.<br>The register is configured at power-on with a<br>factory default value. However, this register<br>automatically overwrites if an offset<br>calibration of the primary ADC is initiated by<br>the user via bits in the ADCMDE MMR. User<br>code can write to this calibration register only<br>if the ADC is in idle mode. An ADC must be<br>enabled and in idle mode before being<br>written to any offset or gain register. The<br>ADC must be in idle mode for at least 23 µs. |

### Table 51. ADCOOF MMR Bit Designations

| Tuble 31. The over mining bit designations |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15:0                                       | ADC0 16-bit offset calibration value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| •                                          | Channel ADC Offset Calibration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Name:<br>Address:                          | ADC1OF<br>0xFFFF0528                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Default valu                               | e: Part specific, factory programmed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Access:                                    | Read and write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Function:                                  | This offset MMR holds a 16-bit offset<br>calibration coefficient for the auxiliary<br>channel. The register is configured at power-<br>on with a factory default value. However, this<br>register is automatically overwritten if an<br>offset calibration of the auxiliary channel is<br>initiated by the user via bits in the ADCMDE<br>MMR. User code can write to this calibration<br>register only if the ADC is in idle mode. An<br>ADC must be enabled and in idle mode<br>before being written to any offset or gain<br>register. The ADC must be in idle mode for<br>at least 23 µs. |

### Table 52. ADC1OF MMR Bit Designations

| Bit  | Description                           |

|------|---------------------------------------|

| 15:0 | ADC1 16-bit offset calibration value. |

\_

| <b>Primary Channel</b> | ADC Gain Calibration | Register |

|------------------------|----------------------|----------|

|------------------------|----------------------|----------|

| Name:          | ADCOGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF052C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Default value: | Part specific, factory programmed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Access:        | Read and write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Function:      | This gain MMR holds a 16-bit gain<br>calibration coefficient for scaling the primary<br>ADC conversion result. The register is<br>configured at power-on with a factory default<br>value. However, this register is automatically<br>overwritten if a gain calibration of the<br>primary ADC is initiated by the user via bits<br>in the ADCMDE MMR. User code can write<br>to this calibration register only if the ADC is<br>in idle mode. An ADC must be enabled and<br>in idle mode before being written to any<br>offset or gain register. The ADC must be in<br>idle mode for at least 23 µs. |

| Bits           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0           | ADC0 16-bit calibration gain value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Auxiliary Cha  | nnel Gain Calibration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Name:          | ADC1GN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Address:       | 0xFFFF0530                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Default value: | Part specific, factory programmed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Access:        | Read and write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Function:      | This gain MMR holds a 16-bit gain calibra-<br>tion coefficient for scaling an auxiliary channel<br>conversion result. The register is configured<br>at power-on with a factory default value.<br>However, this register is automatically over-<br>written if a gain calibration of the auxiliary<br>channel is initiated by the user via bits in the<br>ADCMDE MMR. User code can write to this<br>calibration register only if the ADC is in idle<br>mode. An ADC must be enabled and in idle<br>mode before being written to any offset or gain |

### Table 54. ADC1GN MMR Bit Designations

least 23 µs.

| Bits | Description                         |

|------|-------------------------------------|

| 15:0 | ADC1 16-bit gain calibration value. |

register. The ADC must be in idle mode for at

### Primary Channel ADC Result Counter Limit Register

| Name:          | ADCORCR                                                                                                                                                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF0534                                                                                                                                                                                                                                |

| Default value: | 0x0001                                                                                                                                                                                                                                    |

| Access:        | Read and write                                                                                                                                                                                                                            |

| Function:      | This 16-bit MMR sets the number of conversions required before an ADC interrupt is generated. By default, this register is set to 0x01. The ADC counter function must be enabled via the ADC result counter enable bit in the ADCCFG MMR. |

#### Table 55. ADCORCR MMR Bit Designations

| Bits | Description                                |

|------|--------------------------------------------|

| 15:0 | ADC0 result counter limit/reload register. |

### Primary Channel ADC Result Counter Register

| Name:          | ADCORCV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF0538                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Default value: | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Access:        | Read only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Function:      | This 16-bit, read-only MMR holds the<br>current number of primary ADC conversion<br>results. It is used in conjunction with<br>ADC0RCR to mask primary channel ADC<br>interrupts, generating a lower interrupt rate.<br>When ADC0RCV = ADC0RCR, the value in<br>ADC0RCV resets to 0 and recommences<br>counting. It can also be used in conjunction<br>with the accumulator (ADC0ACC) to allow<br>an average calculation to be taken. The<br>result counter is enabled via ADCCFG[0].<br>This MMR is also reset to 0 when the<br>primary ADC is reconfigured, that is, when<br>the ADC0CON or ADCMDE is written. |

### Table 56. ADCORCV MMR Bit Designations

| Bits | Description                   |

|------|-------------------------------|

| 15:0 | ADC0 result counter register. |

### **Data Sheet**

### Primary Channel ADC Threshold Register

| Name:          | ADC0TH                                                                                                                                                                                                                                    |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF053C                                                                                                                                                                                                                                |

| Default value: | 0x0000                                                                                                                                                                                                                                    |

| Access:        | Read and write                                                                                                                                                                                                                            |

| Function:      | This 16-bit MMR sets the threshold against<br>which the absolute value of the primary ADC<br>conversion result is compared. In unipolar<br>mode, ADC0TH[15:0] are compared, and in<br>twos complement mode, ADC0TH[14:0] are<br>compared. |

#### Table 57. ADC0TH MMR Bit Designations Ri+ Description

| BIT  | Description                                |

|------|--------------------------------------------|

| 15:0 | ADC0 16-bit comparator threshold register. |

### Primary Channel ADC Threshold Counter Limit Register

| Name:          | ADC0THC                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF0540                                                                                                                                                                                                                                                                                                                                                                                       |

| Default value: | 0x0001                                                                                                                                                                                                                                                                                                                                                                                           |

| Access:        | Read and write                                                                                                                                                                                                                                                                                                                                                                                   |

| Function:      | This 8-bit MMR determines how many<br>cumulative (values below the threshold<br>decrement or reset the count to 0) primary<br>ADC conversion result readings above<br>ADC0TH must occur before the primary<br>ADC comparator threshold bit is set in the<br>ADCSTA MMR, generating an ADC<br>interrupt. The primary ADC comparator<br>threshold bit is asserted as soon as<br>ADC0THV = ADC0RCR. |

#### Table 58. ADC0THC MMR Bit Designations

| Bit  | Description                                  |  |

|------|----------------------------------------------|--|

| 15:8 | Reserved.                                    |  |

| 7:0  | ADC0 8-bit threshold counter limit register. |  |

## ADuC7060/ADuC7061

### Primary Channel ADC Threshold Counter Register

| Name:          | ADC0THV                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF0544                                                                                                                                                                                                                                                                                                                                                                            |

| Default value: | 0x0000                                                                                                                                                                                                                                                                                                                                                                                |

| Access:        | Read only                                                                                                                                                                                                                                                                                                                                                                             |

| Function:      | This 8-bit MMR is incremented every time<br>the absolute value of a primary ADC<br>conversion result  Result  ≥ ADC0TH. This<br>register is decremented or reset to 0 every<br>time the absolute value of a primary ADC<br>conversion result  Result  < ADC0TH. The<br>configuration of this function is enabled via<br>the primary channel ADC comparator bits in<br>the ADCCFG MMR. |

#### Table 59. ADC0THV MMR Bit Designations

| Bit                                    | Description                                                                                                                                                                                                                                                                                                     |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0                                    | ADC0 8-bit threshold exceeded counter register.                                                                                                                                                                                                                                                                 |

| Primary                                | y Channel ADC Accumulator Register                                                                                                                                                                                                                                                                              |

| Name:                                  | ADC0ACC                                                                                                                                                                                                                                                                                                         |

| Address                                | : 0xFFFF0548                                                                                                                                                                                                                                                                                                    |

| Default                                | value: 0x00000000                                                                                                                                                                                                                                                                                               |

| Access:                                | Read only                                                                                                                                                                                                                                                                                                       |

| Function                               | n: This 32-bit MMR holds the primary ADC<br>accumulator value. The primary ADC ready bit<br>in the ADCSTA MMR should be used to<br>determine when it is safe to read this MMR.<br>The MMR value is reset to 0 by disabling the<br>accumulator in the ADCCFG MMR or by<br>reconfiguring the primary channel ADC. |

| Table 60. ADC0ACC MMR Bit Designations |                                                                                                                                                                                                                                                                                                                 |

| Bit                                    | Description                                                                                                                                                                                                                                                                                                     |

| Bit  | Description                       |

|------|-----------------------------------|

| 31:0 | ADC0 32-bit accumulator register. |

### **Data Sheet**

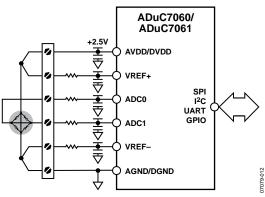

Figure 18. Bridge Interface Circuit

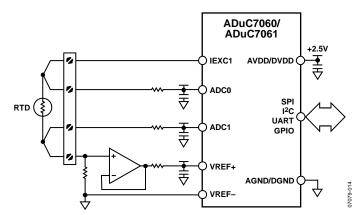

Figure 20. Example of an RTD Interface Circuit

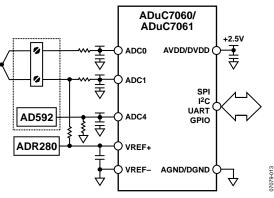

Figure 19. Example of a Thermocouple Interface Circuit

### DACODAT Register

| Name:          | DAC0DAT                                        |

|----------------|------------------------------------------------|

| Address:       | 0xFFFF0604                                     |

| Default value: | 0x00000000                                     |

| Access:        | Read and write                                 |

| Function:      | This 32-bit MMR contains the DAC output value. |

#### Table 64. DAC0DAT MMR Bit Designations

| Bit   | Description                                 |

|-------|---------------------------------------------|

| 31:28 | Reserved.                                   |

| 27:16 | 12-bit data for DAC0.                       |

| 15:12 | Extra four bits used in interpolation mode. |

| 11:0  | Reserved.                                   |

### **USING THE DAC**

The on-chip DAC architecture consists of a resistor string DAC followed by an output buffer amplifier.

The reference source for the DAC is user selectable in software. It can be AVDD, VREF±, or ADCx/EXT\_REF2IN±.

- In 0-to-AVDD mode, the DAC output transfer function spans from 0 V to the voltage at the AVDD pin.

- In VREF± and ADCx/EXT\_REF2IN± modes, the DAC output transfer function spans from negative input voltage to the voltage positive input pin. Note that these voltages must never go below 0 V or above AVDD.

- In 0-to-V<sub>REF</sub> mode, the DAC output transfer function spans from 0 V to the internal 1.2 V reference, V<sub>REF</sub>.

The DAC can be configured in three different user modes: normal mode, DAC interpolation mode, and op amp mode.

### Normal DAC Mode

In this mode of operation, the DAC is configured as a 12-bit voltage output DAC. By default, the DAC buffer is enabled, but the output buffer can be disabled. If the DAC output buffer is disabled, the DAC is capable of driving a capacitive load of only 20 pF. The DAC buffer is disabled by setting the DACBUFBYPASS bit in DAC0CON.

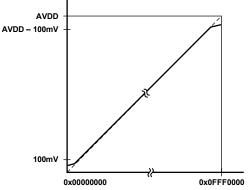

The DAC output buffer amplifier features a true, rail-to-rail output stage implementation. This means that when unloaded, each output is capable of swinging to within less than 5 mV of both AVDD and ground. Moreover, the linearity specification of the DAC (when driving a 5 k $\Omega$  resistive load to ground) is guaranteed through the full transfer function except for Code 0 to Code 100 and, in 0-to- AVDD mode only, Code 3995 to

Code 4095. Linearity degradation near ground and AVDD is caused by saturation of the output amplifier, and a general representation of its effects (neglecting offset and gain error) is illustrated in Figure 21. The dotted line in Figure 21 indicates the ideal transfer function, and the solid line represents what the transfer function may look like with endpoint nonlinearities due to saturation of the output amplifier. Note that Figure 21 represents a transfer function in 0-to-AVDD mode only. In 0-to-V<sub>REF</sub> or, VREF±, and ADCx/EXT\_REF2IN± modes (with V<sub>REF</sub> < AVDD or ADCx/EXT\_REF2IN± < AVDD), the lower nonlinearity is similar. However, the upper portion of the transfer function follows the ideal line all the way to the end (V<sub>REF</sub> in this case, not AVDD), showing no signs of endpoint linearity errors.

Figure 21. Endpoint Nonlinearities Due to Amplifier Saturation

The endpoint nonlinearities conceptually illustrated in Figure 21 worsen as a function of output loading. Most of the ADuC7060/ADuC7061 data sheet specifications in normal mode assume a 5 k $\Omega$  resistive load to ground at the DAC output. As the output is forced to source or sink more current, the nonlinear regions at the top or bottom (respectively) of Figure 21 become larger. With larger current demands, this can significantly limit output voltage swing.

### DAC Interpolation Mode

In interpolation mode, a higher DAC output resolution of 16 bits is achieved with a longer update rate than normal mode. The update rate is controlled by the interpolation clock rate selected in the DAC0CON register. In this mode, an external RC filter is required to create a constant voltage.

### **Op Amp Mode**

In op amp mode, the DAC output buffer is used as an op amp with the DAC itself disabled.

ADC6 is the positive input to the op amp, ADC7 is the negative input, and ADC8 is the output. In this mode, the DAC should be powered down by setting Bit 9 of DAC0CON.

### **NONVOLATILE FLASH/EE MEMORY**

The ADuC7060/ADuC7061 incorporates Flash/EE memory technology on chip to provide the user with nonvolatile, in-circuit reprogrammable memory space.

Like EEPROM, flash memory can be programmed in-system at a byte level, although it must first be erased. The erase is performed in page blocks. As a result, flash memory is often and, more correctly, referred to as Flash/EE memory.

Overall, Flash/EE memory represents a step closer to the ideal memory device that includes nonvolatility, in-circuit programmability, high density, and low cost. Incorporated in the ADuC7060/ADuC7061, Flash/EE memory technology allows the user to update program code space in-circuit, without the need to replace one time programmable (OTP) devices at remote operating nodes.

The ADuC7060/ADuC7061 contains a 32 kB array of Flash/EE memory. The lower 30 kB are available to the user and the upper 2 kB contain permanently embedded firmware, allowing in-circuit serial download. These 2 kB of embedded firmware also contain a power-on configuration routine that downloads factory-calibrated coefficients to the various calibrated peripherals (such as ADC, temperature sensor, and band gap references). This 2 kB embedded firmware is hidden from user code.

### FLASH/EE MEMORY RELIABILITY

The Flash/EE memory arrays on the parts are fully qualified for two key Flash/EE memory characteristics: Flash/EE memory cycling endurance and Flash/EE memory data retention.

Endurance quantifies the ability of the Flash/EE memory to be cycled through many program, read, and erase cycles. A single endurance cycle is composed of four independent, sequential events, defined as

- Initial page erase sequence

- Read/verify sequence for a single Flash/EE

- Byte program sequence memory

- Second read/verify sequence endurance cycle

In reliability qualification, every half word (16-bit wide) location of the three pages (top, middle, and bottom) in the Flash/EE memory is cycled 10,000 times from 0x0000 to 0xFFFF. The Flash/EE memory endurance qualification is carried out in accordance with JEDEC *Retention Lifetime Specification A117* over the industrial temperature range of -40°C to +125°C. The results allow the specification of a minimum endurance figure over a supply temperature of 10,000 cycles.

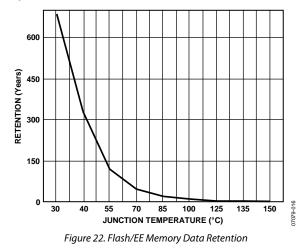

Retention quantifies the ability of the Flash/EE memory to retain its programmed data over time. Again, the parts are qualified in accordance with the formal *JEDEC Retention Lifetime Specification A117* at a specific junction temperature ( $T_J = 85^{\circ}C$ ). As part of this qualification procedure, the Flash/ EE memory is cycled to its specified endurance limit, described previously, before data retention is characterized. This means that the Flash/EE memory is guaranteed to retain its data for its fully specified retention lifetime every time that the Flash/EE memory is reprogrammed. Also note that retention lifetime, based on activation energy of 0.6 eV, derates with  $T_J$ , as shown in Figure 22.

### PROGRAMMING

The 30 kB of Flash/EE memory can be programmed in-circuit, using the serial download mode or the provided JTAG mode.

### Serial Downloading (In-Circuit Programming)

The ADuC7060/ADuC7061 facilitates code download via the standard UART serial port. The parts enter serial download mode after a reset or power cycle if the NTRST/ $\overline{BM}$  pin is pulled low through an external 1 k $\Omega$  resistor. When in serial download mode, the user can download code to the full 30 kB of Flash/EE memory while the device is in-circuit in its target application hardware. An executable PC serial download is provided as part of the development system for serial downloading via the UART.

When the ADuC7060/ADuC7061 enters download mode, the user should be aware that the internal watchdog is enabled with a time-out period of 2 minutes. If the flash erase/write sequence is not completed in this period, a reset occurs.

### JTAG Access

The JTAG protocol uses the on-chip JTAG interface to facilitate code download and debug.

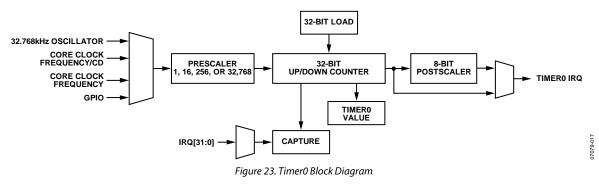

### **TIMER0**

Timer0 is a 32-bit, general-purpose timer, count down or count up, with a programmable prescaler. The prescaler source can be the low power 32.768 kHz oscillator, the core clock, or from one of two external GPIOs. This source can be scaled by a factor of 1, 16, 256, or 32,768. This gives a minimum resolution of 97.66 ns with a prescaler of 1 (ignoring the external GPIOs).

The counter can be formatted as a standard 32-bit value or as hours:minutes:seconds:hundredths.

Timer0 has a capture register (T0CAP) that is triggered by a selected IRQ source initial assertion. When triggered, the current timer value is copied to T0CAP, and the timer continues to run. Use this feature to determine the assertion of an event with increased accuracy. Note that only peripherals that have their IRQ source enabled can be used with the timer capture feature.

The Timer0 interface consists of five MMRS: T0LD, T0VAL, T0CAP, T0CLRI, and T0CON.

- T0LD, T0VAL, and T0CAP are 32-bit registers and hold 32-bit, unsigned integers of which T0VAL and T0CAP are read only.

- TOCLRI is an 8-bit register and writing any value to this register clears the Timer0 interrupt.

- T0CON is the configuration MMR, which is described in Table 80.

Timer0 features a postscaler that allows the user to count between 1 and 256 the number of Timer0 timeouts. To activate the postscaler, the user sets Bit 18 and writes the desired number to count into Bits[24:31] of T0CON. When that number of timeouts is reached, Timer0 can generate an interrupt if T0CON[18] is set.

Note that, if the part is in a low power mode and Timer0 is clocked from the GPIO or low power oscillator source, Timer0 continues to operate.

Timer0 reloads the value from T0LD when Timer0 overflows.

### Timer0 Load Registers

| Name:          | T0LD                                                                                   |

|----------------|----------------------------------------------------------------------------------------|

| Address:       | 0xFFFF0320                                                                             |

| Default value: | 0x0000000                                                                              |

| Access:        | Read and write                                                                         |

| Function:      | T0LD is a 32-bit register that holds the 32-bit value that is loaded into the counter. |

### **Timer0 Clear Register**

| Name:     | TOCLRI                                                                                            |

|-----------|---------------------------------------------------------------------------------------------------|

| Address:  | 0xFFFF032C                                                                                        |

| Access:   | Write only                                                                                        |

| Function: | This 8-bit, write-only MMR is written<br>(with any value) by user code to clear the<br>interrupt. |

#### **Timer0 Value Register**

| Name:          | T0VAL                                                              |

|----------------|--------------------------------------------------------------------|

| Address:       | 0xFFFF0324                                                         |

| Default value: | 0xFFFFFFFF                                                         |

| Access:        | Read only                                                          |

| Function:      | T0VAL is a 32-bit register that holds the current value of Timer0. |

Address:

Access:

Function:

Default value:

0xFFFF0FAC

Read and write

PWM5 output pin goes low when the PWM

timer reaches the count value stored in this

0x0000

register.

| РѠӍ2СОӍ0       | Compare Register                                                                              | PWM2LEN Reg    | PWM2LEN Register                                                                                                                            |  |

|----------------|-----------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|