Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 20000                      |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 6                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1822-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Peripheral Features (Continued)**

- Data Signal Modulator module

- Selectable modulator and carrier sources

- SR Latch:

- Multiple Set/Reset input options

- Emulates 555 Timer applications

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data EEPROM<br>(bytes) | Data SRAM<br>(bytes) | I/O'S <sup>(2)</sup> | 10-bit ADC (ch) | CapSense (ch) | Comparators | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> C <sup>TM</sup> /SPI) | ECCP (Full-Bridge)<br>ECCP (Half-Bridge)<br>CCP | SR Latch | Debug <sup>(1)</sup> | XLP |

|---------------|------------------|---------------------------------|------------------------|----------------------|----------------------|-----------------|---------------|-------------|----------------------|--------|--------------------------------------------|-------------------------------------------------|----------|----------------------|-----|

| PIC12(L)F1822 | (1)              | 2K                              | 256                    | 128                  | 6                    | 4               | 4             | 1           | 2/1                  | 1      | 1                                          | 0/1/0                                           | Y        | I/H                  | Y   |

| PIC12(L)F1840 | (2)              | 4K                              | 256                    | 256                  | 6                    | 4               | 4             | 1           | 2/1                  | 1      | 1                                          | 0/1/0                                           | Y        | I/H                  | Y   |

| PIC16(L)F1823 | (1)              | 2K                              | 256                    | 128                  | 12                   | 8               | 8             | 2           | 2/1                  | 1      | 1                                          | 1/0/0                                           | Y        | I/H                  | Y   |

| PIC16(L)F1824 | (3)              | 4K                              | 256                    | 256                  | 12                   | 8               | 8             | 2           | 4/1                  | 1      | 1                                          | 1/1/2                                           | Y        | I/H                  | Y   |

| PIC16(L)F1825 | (4)              | 8K                              | 256                    | 1024                 | 12                   | 8               | 8             | 2           | 4/1                  | 1      | 1                                          | 1/1/2                                           | Y        | I/H                  | Y   |

| PIC16(L)F1826 | (5)              | 2K                              | 256                    | 256                  | 16                   | 12              | 12            | 2           | 2/1                  | 1      | 1                                          | 1/0/0                                           | Y        | I/H                  | Y   |

| PIC16(L)F1827 | (5)              | 4K                              | 256                    | 384                  | 16                   | 12              | 12            | 2           | 4/1                  | 1      | 2                                          | 1/1/2                                           | Y        | I/H                  | Y   |

| PIC16(L)F1828 | (3)              | 4K                              | 256                    | 256                  | 18                   | 12              | 12            | 2           | 4/1                  | 1      | 1                                          | 1/1/2                                           | Y        | I/H                  | Y   |

| PIC16(L)F1829 | (4)              | 8K                              | 256                    | 1024                 | 18                   | 12              | 12            | 2           | 4/1                  | 1      | 2                                          | 1/1/2                                           | Y        | I/H                  | Y   |

| PIC16(L)F1847 | (6)              | 8K                              | 256                    | 1024                 | 16                   | 12              | 12            | 2           | 4/1                  | 1      | 2                                          | 1/1/2                                           | Y        | I/H                  | Y   |

#### TABLE 1: PIC12(L)F1822/1840/PIC16(L)F182X/1847 FAMILY TYPES

Note 1: I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS41413 PIC12(L)F1822/PIC16(L)F1823 Data Sheet, 8/14-Pin Flash Microcontrollers.

2: DS41441 PIC12(L)F1840 Data Sheet, 8-Pin Flash Microcontrollers.

**3:** DS41419 PIC16(L)F1824/1828 Data Sheet, 28/40/44-Pin Flash Microcontrollers.

4: DS41440 PIC16(L)F1825/1829 Data Sheet, 14/20-Pin Flash Microcontrollers.

5: DS41391 PIC16(L)F1826/1827 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

6: DS41453 PIC16(L)F1847 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit www.microchip.com/packaging or contact your local sales office.

## 1.0 DEVICE OVERVIEW

The PIC12(L)F1822/16(L)F1823 are described within this data sheet. They are available in 8/14 pin packages. Figure 1-1 shows a block diagram of the PIC12(L)F1822/16(L)F1823 devices. Tables 1-2 and 1-3 show the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral               |             | PIC12(L)F1822 | PIC16(L)F1823 |

|--------------------------|-------------|---------------|---------------|

| ADC                      |             | ٠             | •             |

| Capacitive Sensing (CP   | S) Module   | •             | •             |

| Data EEPROM              |             | ٠             | •             |

| Digital-to-Analog Conve  | rter (DAC)  | ٠             | •             |

| Digital Signal Modulator | · (DSM)     | ٠             | •             |

| EUSART                   | •           | •             |               |

| Fixed Voltage Reference  | e (FVR)     | ٠             | •             |

| SR Latch                 |             | •             | •             |

| Capture/Compare/PWM      | Modules     |               |               |

|                          | ECCP1       | •             | •             |

| Comparators              |             |               |               |

|                          | C1          | •             | •             |

|                          | C2          |               | •             |

| Master Synchronous Se    | erial Ports |               |               |

|                          | MSSP        | ٠             | •             |

| Timers                   |             |               |               |

|                          | Timer0      | •             | •             |

|                          | Timer1      | •             | •             |

|                          | Timer2      | ٠             | •             |

| Address             | Name                | Bit 7                          | Bit 6          | Bit 5            | Bit 4           | Bit 3        | Bit 2       | Bit 1   | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------------------|---------------------|--------------------------------|----------------|------------------|-----------------|--------------|-------------|---------|-------|----------------------|---------------------------------|

| Bank 4              |                     |                                |                |                  |                 |              |             |         |       |                      |                                 |

| 200h <sup>(1)</sup> | INDF0               | Addressing th<br>(not a physic |                | es contents of   | FSR0H/FSR0      | L to address | data memory | ,       |       | XXXX XXXX            | XXXX XXXX                       |

| 201h <sup>(1)</sup> | INDF1               | Addressing th<br>(not a physic |                | es contents of   | FSR1H/FSR1      | L to address | data memory | ,       |       | XXXX XXXX            | XXXX XXXX                       |

| 202h <sup>(1)</sup> | PCL                 | Program Cou                    | inter (PC) Lea | st Significant E | Byte            |              |             |         |       | 0000 0000            | 0000 0000                       |

| 203h <sup>(1)</sup> | STATUS              | _                              | _              | _                | TO              | PD           | Z           | DC      | С     | 1 1000               | q quuu                          |

| 204h <sup>(1)</sup> | FSR0L               | Indirect Data                  | Memory Addr    | ess 0 Low Poir   | nter            |              |             |         |       | 0000 0000            | uuuu uuuu                       |

| 205h <sup>(1)</sup> | FSR0H               | Indirect Data                  | Memory Addr    | ess 0 High Poi   | nter            |              |             |         |       | 0000 0000            | 0000 0000                       |

| 206h <sup>(1)</sup> | FSR1L               | Indirect Data                  | Memory Addr    | ess 1 Low Poir   | nter            |              |             |         |       | 0000 0000            | uuuu uuuu                       |

| 207h <sup>(1)</sup> | FSR1H               | Indirect Data                  | Memory Addr    | ess 1 High Poi   | nter            |              |             |         |       | 0000 0000            | 0000 0000                       |

| 208h <sup>(1)</sup> | BSR                 | _                              | _              | _                |                 |              | BSR<4:0>    |         |       | 0 0000               | 0 0000                          |

| 209h <sup>(1)</sup> | WREG                | Working Reg                    | ister          | •                | •               |              |             |         |       | 0000 0000            | uuuu uuuu                       |

| 20Ah <sup>(1)</sup> | PCLATH              | _                              | Write Buffer f | or the upper 7   | bits of the Pro | ogram Counte | er          |         |       | -000 0000            | -000 0000                       |

| 20Bh <sup>(1)</sup> | INTCON              | GIE                            | PEIE           | TMR0IE           | INTE            | IOCIE        | TMR0IF      | INTF    | IOCIF | 0000 000x            | 0000 000u                       |

| 20Ch                | WPUA                | _                              | —              | WPUA5            | WPUA4           | WPUA3        | WPUA2       | WPUA1   | WPUA0 | 11 1111              | 11 1111                         |

| 20Dh                | —                   | Unimplement                    | ted            | •                | •               | •            | •           |         | •     | _                    | _                               |

| 20Eh                | WPUC <sup>(2)</sup> | _                              | _              | WPUC5            | WPUC4           | WPUC3        | WPUC2       | WPUC1   | WPUC0 | 11 1111              | 11 1111                         |

| 20Fh                | —                   | Unimplement                    | ted            | •                |                 |              |             |         | •     | _                    | _                               |

| 210h                | _                   | Unimplement                    | ted            |                  |                 |              |             |         |       | _                    | _                               |

| 211h                | SSP1BUF             | Synchronous                    | Serial Port Re | eceive Buffer/T  | ransmit Regis   | ster         |             |         |       | xxxx xxxx            | uuuu uuuu                       |

| 212h                | SSP1ADD             |                                |                |                  | ADD<            | 7:0>         |             |         |       | 0000 0000            | 0000 0000                       |

| 213h                | SSP1MSK             |                                |                |                  | MSK<            | 7:0>         |             |         |       | 1111 1111            | 1111 1111                       |

| 214h                | SSP1STAT            | SMP                            | CKE            | D/A              | Р               | S            | R/W         | UA      | BF    | 0000 0000            | 0000 0000                       |

| 215h                | SSP1CON1            | WCOL                           | SSPOV          | SSPEN            | CKP             |              | SSPN        | //<3:0> |       | 0000 0000            | 0000 0000                       |

| 216h                | SSP1CON2            | GCEN                           | ACKSTAT        | ACKDT            | ACKEN           | RCEN         | PEN         | RSEN    | SEN   | 0000 0000            | 0000 0000                       |

| 217h                | SSP1CON3            | ACKTIM                         | PCIE           | SCIE             | BOEN            | SDAHT        | SBCDE       | AHEN    | DHEN  | 0000 0000            | 0000 0000                       |

| 218h                | _                   | Unimplement                    | ted            |                  |                 |              |             |         |       | _                    | _                               |

| 219h                | _                   | Unimplement                    | ted            |                  |                 |              |             |         |       | _                    | _                               |

| 21Ah                | _                   | Unimplement                    | ted            |                  |                 |              |             |         |       | _                    | _                               |

| 21Bh                | _                   | Unimplement                    | Jnimplemented  |                  |                 |              |             |         |       | _                    | _                               |

| 21Ch                | _                   | Unimplement                    | ted            |                  |                 |              |             |         |       |                      | _                               |

| 21Dh                | _                   | Unimplement                    | nimplemented   |                  |                 |              |             |         |       |                      | _                               |

| 21Eh                | _                   | Unimplement                    | ted            |                  |                 |              |             |         |       | _                    | _                               |

| 21Fh                | _                   | Unimplement                    | implemented    |                  |                 |              |             |         |       |                      | —                               |

#### TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: PIC16(L)F1823 only.

**3:** Unimplemented. Read as '1'.

4: PIC12(L)F1822 only.

© 2010-2015 Microchip Technology Inc.

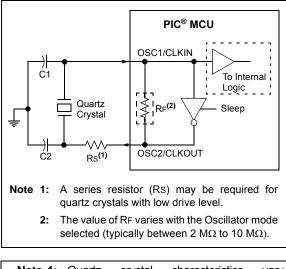

#### FIGURE 5-3:

#### QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

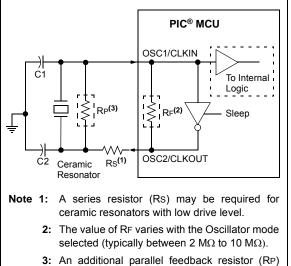

#### FIGURE 5-4:

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

## may be required for proper ceramic resonator operation.

## 5.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see **Section 5.4 "Two-Speed Clock Start-up Mode"**).

#### 5.2.1.4 4X PLL

The oscillator module contains a 4X PLL that can be used with both external and internal clock sources to provide a system clock source. The input frequency for the 4X PLL must fall within specifications. See the PLL Clock Timing Specifications in **Section 30.0 "Electrical Specifications"**.

The 4X PLL may be enabled for use by one of two methods:

- 1. Program the PLLEN bit in Configuration Word 2 to a '1'.

- Write the SPLLEN bit in the OSCCON register to a '1'. If the PLLEN bit in Configuration Word 2 is programmed to a '1', then the value of SPLLEN is ignored.

## 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Word 1

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<2:0> bits in the Configuration Word 1.

- When the SCS bits of the OSCCON register = 01, the system clock source is the Timer1 oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

| Note: | Any automatic clock switch, which may     |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | occur from Two-Speed Start-up or          |  |  |  |  |  |  |  |

|       | Fail-Safe Clock Monitor, does not update  |  |  |  |  |  |  |  |

|       | the SCS bits of the OSCCON register. The  |  |  |  |  |  |  |  |

|       | user can monitor the OSTS bit of the      |  |  |  |  |  |  |  |

|       | OSCSTAT register to determine the current |  |  |  |  |  |  |  |

|       | system clock source.                      |  |  |  |  |  |  |  |

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

#### 5.3.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the Timer1 Oscillator.

## 5.3.3 TIMER1 OSCILLATOR

The Timer1 Oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 21.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 5.3.4 TIMER1 OSCILLATOR READY (T1OSCR) BIT

The user must ensure that the Timer1 Oscillator is ready to be used before it is selected as a system clock source. The Timer1 Oscillator Ready (T1OSCR) bit of the OSCSTAT register indicates whether the Timer1 oscillator is ready to be used. After the T1OSCR bit is set, the SCS bits can be configured to select the Timer1 oscillator.

#### 10.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator.

#### 10.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Word 1. See Table 10-1.

10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Word 1 are set to '11', the WDT is always on.

WDT protection is active during Sleep.

10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Word 1 are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Word 1 are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

| WDTE<br>Config bits | SWDTEN | Device<br>Mode | WDT<br>Mode |

|---------------------|--------|----------------|-------------|

| WDT_ON (11)         | Х      | Х              | Active      |

| WDT_NSLEEP (10)     | Х      | Awake          | Active      |

| WDT_NSLEEP (10)     | Х      | Sleep          | Disabled    |

| WDT_SWDTEN (01)     | 1      | Х              | Active      |

| WDT_SWDTEN (01)     | 0      | Х              | Disabled    |

| WDT_OFF (00)        | Х      | Х              | Disabled    |

TABLE 10-1: WDT OPERATING MODES

#### 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds. After a Reset, the default time-out period is two seconds.

## 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail event

- WDT is disabled

- OST is running

See Table 10-2 for more information.

## 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 5.0** "Oscillator **Module (With Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See **Section 3.0 "Memory Organization"** and The STATUS register (Register 3-1) for more information.

#### TABLE 10-2: WDT CLEARING CONDITIONS

| Conditions                                               | WDT                          |  |  |  |

|----------------------------------------------------------|------------------------------|--|--|--|

| DTE<1:0> = 00                                            |                              |  |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |  |  |  |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |  |  |  |

| CLRWDT Command                                           | Cleared                      |  |  |  |

| Oscillator Fail Detected                                 |                              |  |  |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |  |  |  |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |  |  |  |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |  |  |  |

## 11.2 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. Refer to **Section 30.0 "Electrical Specifications"**. If this is the case, then a refresh of the array must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

#### 11.2.1 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADRL register, clear the EEPGD and CFGS control bits of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDATL register; therefore, it can be read in the next instruction. EEDATL will hold this value until another read or until it is written to by the user (during a write operation).

EXAMPLE 11-1: DATA EEPROM READ

| BANKSEL | EEADRL  |       | i                      |

|---------|---------|-------|------------------------|

| MOVLW   | DATA_EE | _ADDR | ;                      |

| MOVWF   | EEADRL  |       | ;Data Memory           |

|         |         |       | ;Address to read       |

| BCF     | EECON1, | CFGS  | ;Deselect Config space |

| BCF     | EECON1, | EEPGI | );Point to DATA memory |

| BSF     | EECON1, | RD    | ;EE Read               |

| MOVF    | EEDATL, | W     | ;W = EEDATL            |

|         |         |       |                        |

Note: Data EEPROM can be read regardless of the setting of the CPD bit.

#### 11.2.2 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADRL register and the data to the EEDATL register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the above sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

#### 11.2.3 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, WREN is cleared. Also, the Power-up Timer (64 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during:

- Brown-out

- Power Glitch

- Software Malfunction

#### 11.2.4 DATA EEPROM OPERATION DURING CODE-PROTECT

Data memory can be code-protected by programming the CPD bit in the Configuration Word 1 (Register 5-1) to '0'.

When the data memory is code-protected, only the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code-protecting data memory. This prevents anyone from replacing your program with a program that will access the contents of the data EEPROM.

## 13.0 INTERRUPT-ON-CHANGE

The PORTA pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTA pin, or combination of PORTA pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

### 13.1 Enabling the Module

To allow individual PORTA pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

#### 13.2 Individual Pin Configuration

For each PORTA pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCAPx bit of the IOCAP register is set. To enable a pin to detect a falling edge, the associated IOCANx bit of the IOCAN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCAPx bit and the IOCANx bit of the IOCAP and IOCAN registers, respectively.

#### 13.3 Interrupt Flags

The IOCAFx bits located in the IOCAF register are status flags that correspond to the Interrupt-on-change pins of PORTA. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx bits.

## 13.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCAF register will be updated prior to the first instruction executed out of Sleep.

#### REGISTER 13-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0

bit 5-0

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

## REGISTER 13-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

- IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

- 0 = No change was detected, or the user cleared the detected change.

## 21.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 21.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

| Note: | The oscillator requires a start-up and   |

|-------|------------------------------------------|

|       | stabilization time before use. Thus,     |

|       | T1OSCEN should be set and a suitable     |

|       | delay observed prior to enabling Timer1. |

## 21.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 21.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 21.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 Gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 Gate can also be driven by multiple selectable sources.

#### 21.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 21-3 for timing details.

#### TABLE 21-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 21.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 Gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 21-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                        |

|-------|---------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                           |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                   |

| 10    | Comparator 1 Output sync_C1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output sync_C2OUT<br>(optionally Timer1 synchronized output) |

<sup>© 2010-2015</sup> Microchip Technology Inc.

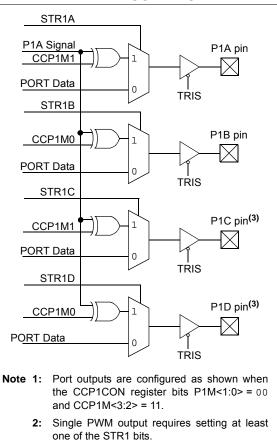

#### 24.4.6 PWM STEERING MODE

In Single Output mode, PWM steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR1 bits of the PSTR1CON register, as shown in Table 24-9.

| Note: | The associated TRIS bits must be set to      |

|-------|----------------------------------------------|

|       | output ('0') to enable the pin output driver |

|       | in order to see the PWM signal on the pin.   |

While the PWM Steering mode is active, the CCP1M<1:0> bits of the CCP1CON register determine the polarity of the output pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 24.4.3 "Enhanced PWM Auto-shutdown mode"**. An autoshutdown event will only affect pins that have PWM outputs enabled.

#### FIGURE 24-18: SIMPLIFIED STEERING BLOCK DIAGRAM

3: PIC16(L)F1823 only.

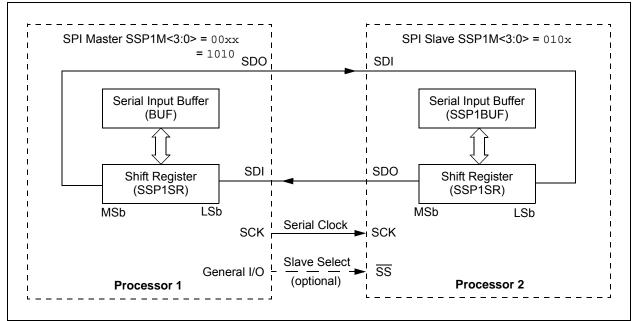

The MSSP1 consists of a transmit/receive shift register (SSP1SR) and a buffer register (SSP1BUF). The SSP1SR shifts the data in and out of the device. MSb first. The SSP1BUF holds the data that was written to the SSP1SR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSP1BUF register. Then, the Buffer Full Detect bit, BF of the SSP1STAT register, and the interrupt flag bit, SSP1IF, are set. This double-buffering of the received data (SSP1BUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSP1BUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL, of the SSP1CON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSP1BUF register to complete successfully.

When the application software is expecting to receive valid data, the SSP1BUF should be read before the next byte of data to transfer is written to the SSP1BUF. The Buffer Full bit, BF of the SSP1STAT register, indicates when SSP1BUF has been loaded with the received data (transmission is complete). When the SSP1BUF is read, the BF bit is cleared. This data may be irrelevant if the SP1 is only a transmitter. Generally, the MSSP1 interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSP1SR is not directly readable or writable and can only be accessed by addressing the SSP1BUF register. Additionally, the SSP1STAT register indicates the various Status conditions.

#### FIGURE 25-5: SPI MASTER/SLAVE CONNECTION

|                                           |                                                 |                   |                                            |                                           |                  |                       |                  | - 0)                      |                |            |                       |

|-------------------------------------------|-------------------------------------------------|-------------------|--------------------------------------------|-------------------------------------------|------------------|-----------------------|------------------|---------------------------|----------------|------------|-----------------------|

| <br>Ses<br>Opaionai                       |                                                 |                   |                                            |                                           |                  |                       |                  |                           |                |            |                       |

|                                           | ,<br>,<br>,<br>,,                               |                   |                                            |                                           |                  |                       |                  |                           |                |            | к<br>С<br>С<br>С      |

| 9782 999)<br>8086<br>6088 993<br>688 993) | *<br>;<br>;<br>;                                | ·<br>·            | ·<br>·                                     |                                           |                  | :<br>;<br>;           | ><br>            |                           |                |            | с<br>с<br>            |

| 088 + 6)<br>Wate to<br>SSP (885           | ,<br>,<br>,<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | \$<br>5<br>5<br>6 | 3<br>6.<br>5.<br>5.                        | 3                                         |                  | 5<br>6<br>6<br>5      | 3<br>c<br>c<br>c | 3                         | 33<br><br><br> |            |                       |

| V.884<br>8920                             |                                                 | i<br>K 58.7       |                                            | X 68 S                                    | N 1533-4         | X 385 ž               | X 32.2           | ,<br>X 68                 | X              |            |                       |

| SC:                                       | 3<br>3<br>3<br>4                                |                   | ,<br>                                      | ,<br>dlf///////////////////////////////// |                  |                       |                  | ;<br>;<br>;<br>;<br>;     |                |            | ,<br>,<br>,<br>,<br>, |

| ingné<br>Sampia                           | 4<br>4<br>3                                     |                   | ;<br>;<br>;<br>;<br>;                      |                                           |                  | :<br>; //j.<br>; //j. |                  |                           |                |            |                       |

| Staff and<br>Intercupa<br>Pagg            | 2<br>2<br>4<br>3                                | <<br><<br>5<br>5  | 2<br>2<br>2<br>2<br>2                      | ,<br>,<br>,<br>,                          | ·<br>:<br>:<br>: | <<br><<br>5<br>5      | 2<br>2<br>2<br>2 | 5<br>5<br>7               |                |            |                       |

| 239<br>SSP158 55<br>SSP1602               | 1<br>1<br>2                                     | -<br>2<br>2<br>2  | ·<br>·<br>·                                | ·<br>·<br>·<br>·                          |                  | -<br>5<br>5<br>5      | -<br>5<br>5<br>9 | 2<br>2<br>2<br>4<br>4<br> |                | <i>ģ</i> . |                       |

| Strike Configure                          | ·                                               | -                 | •<br>• • • • • • • • • • • • • • • • • • • |                                           |                  |                       |                  |                           | · .<br>        |            |                       |

| deteción scave -                          |                                                 |                   |                                            |                                           |                  |                       |                  |                           |                |            |                       |

## FIGURE 25-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| SS   SCK   (CKP = 0   CKE = 1)   SCK   (CKP = 1   CKE = 1) |                     |                       |                       |                       |                     |                            |                     |                     |       |    |

|------------------------------------------------------------|---------------------|-----------------------|-----------------------|-----------------------|---------------------|----------------------------|---------------------|---------------------|-------|----|

| Write to<br>SSP1BUF                                        | <br> <br>           | ,<br>,<br>,<br>,      | 1<br>1<br>1<br>1<br>1 | 1                     | 1<br>1<br>1<br>1    | 1<br>1<br>1<br>1           | <br> <br> <br> <br> | 1<br>1<br>1<br>1    | 1     |    |

| SDO ———                                                    | ` <u> </u>          | bit 7                 | bit 6                 | bit 5                 | bit 4               | bit 3                      | bit 2               | bit 1               | bit 0 |    |

| SDI ———                                                    | ,<br>1<br>1         | bit 7                 | $\frac{1}{2}$         | $\frac{1}{2}$         | $\sim$              | $\sim$                     |                     | $\frac{1}{2}$       | bit 0 |    |

| Input<br>Sample                                            | 1<br>1<br>1<br>1    | 1                     | 1                     | 1                     | 1                   | 1                          | 1                   | <u>↑</u>            | 1     |    |

| SSP1IF<br>Interrupt<br>Flag                                | <br> <br> <br> <br> | 1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1 | <br> <br> <br> <br> | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1    | <br> <br> <br> <br> |       |    |

| SSP1SR to<br>SSP1BUF                                       | 1                   | r                     | 1<br>1<br>1           | 1<br>1<br>1<br>1      | 1<br>1<br>1<br>1    | 1<br>1<br>1<br>1           | 1<br>1<br>1         | 1<br>1<br>1<br>1    |       | é. |

| Volte Collision<br>dataction solive                        | 1<br>1<br>1<br>1    |                       | •                     |                       |                     |                            |                     |                     |       |    |

#### 25.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSP1STAT register is cleared. The received address is loaded into the SSP1BUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSP1STAT register is set, or bit SSP1OV of the SSP1CON1 register is set. The BOEN bit of the SSP1CON3 register modifies this operation. For more information see Register 25-4.

An MSSP1 interrupt is generated for each transferred data byte. Flag bit, SSP1IF, must be cleared by software.

When the SEN bit of the SSP1CON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSP1CON1 register, except sometimes in 10-bit mode. See **Section 25.2.3 "SPI Master Mode"** for more detail.

#### 25.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP1 module configured as an  $I^2C$  Slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 25-14 and Figure 25-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSP1IF bit.

- 5. Software clears the SSP1IF bit.

- 6. Software reads received address from SSP1BUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDA low sending an ACK to the master, and sets SSP1IF bit.

- 10. Software clears SSP1IF.

- 11. Software reads the received byte from SSP1BUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the Master.

- 13. Master sends Stop condition, setting P bit of SSP1STAT, and the bus goes Idle.

## 25.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 25-16 displays a module using both address and data holding. Figure 25-17 includes the operation with the SEN bit of the SSP1CON2 register set.

- 1. S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSP1IF is set and CKP cleared after the 8th falling edge of SCL.

- 3. Slave clears the SSP1IF.

- Slave can look at the ACKTIM bit of the SSP1CON3 register to <u>determine</u> if the SSP1IF was after or before the ACK.

- 5. Slave reads the address value from SSP1BUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSP1IF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSP1IF.

Note: SSP1IF is still set after the 9th falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to Master is SSP1IF not set

- 11. SSP1IF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSP1CON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSP1BUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                           |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                    |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                              |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |  |  |  |  |  |

| SUBLW            | Subtract W from literal                                                                                                               |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                              |  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                   |  |  |  |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                             |  |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                              |  |  |  |  |  |  |  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the 8-bit literal<br>'k'. The result is placed in the W regis-<br>ter. |  |  |  |  |  |  |  |

|                  | C = 0 W > k                                                                                                                           |  |  |  |  |  |  |  |

|                  | <b>C</b> = 1 W ≤ k                                                                                                                    |  |  |  |  |  |  |  |

DC = 0 DC = 1 W<3:0> > k<3:0>

$W<3:0> \le k<3:0>$

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{W}DT \text{ prescaler}, \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                              |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down Status bit, $\overline{PD}$ is<br>cleared. Time-out Status bit, $\overline{TO}$ is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into Sleep mode<br>with the oscillator stopped. |

| SUBWF            | Subtract V                                                        | V from f                                                                                                                                                                                   |  |  |  |  |

|------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] S                                                         | UBWF f,d                                                                                                                                                                                   |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$ |                                                                                                                                                                                            |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (                                         | destination)                                                                                                                                                                               |  |  |  |  |

| Status Affected: | C, DC, Z                                                          |                                                                                                                                                                                            |  |  |  |  |

| Description:     | register from<br>result is stor<br>register. If 'd                | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f. |  |  |  |  |

|                  | <b>C =</b> 0                                                      | W > f                                                                                                                                                                                      |  |  |  |  |

|                  | $C = 1$ $W \le f$                                                 |                                                                                                                                                                                            |  |  |  |  |

|                  | DC = 0 W<3:0> > f<3:0>                                            |                                                                                                                                                                                            |  |  |  |  |

|                  | DC = 1 W<3:0> ≤ f<3:0>                                            |                                                                                                                                                                                            |  |  |  |  |

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                         |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

## TABLE 30-10: COMPARATOR SPECIFICATIONS

| Operating VDD = 3.0V, |          | s (unless otherwise stated)                |      |      |      |       |                                  |

|-----------------------|----------|--------------------------------------------|------|------|------|-------|----------------------------------|

| Param<br>No.          | Sym.     | Characteristics                            | Min. | Тур. | Max. | Units | Comments                         |

| CM01                  | VIOFF    | Input Offset Voltage                       |      | ±7.5 | ±60  | mV    | VICM = VDD/2,<br>High-Power mode |

| CM02                  | VICM     | Input Common Mode Voltage                  | 0    | —    | Vdd  | V     |                                  |

| CM03                  | CMRR     | Common Mode Rejection Ratio                | _    | 50   | —    | dB    |                                  |

| CM04A                 |          | Response Time Rising Edge                  | _    | 400  | 800  | ns    | High-Power mode                  |

| CM04B                 | TRESP(1) | Response Time Falling Edge                 | _    | 200  | 400  | ns    | High-Power mode                  |

| CM04C                 | TRESPY / | Response Time Rising Edge                  | _    | 1200 | —    | ns    | Low-Power mode                   |

| CM04D                 |          | Response Time Falling Edge                 | _    | 550  | _    | ns    | Low-Power mode                   |

| CM05                  | Тмс2о∨   | Comparator Mode Change to<br>Output Valid* | —    | —    | 10   | μS    |                                  |

| CM06                  | CHYSTER  | Comparator Hysteresis <sup>(2)</sup>       | —    | 45   | —    | mV    | Hysteresis on                    |

\* These parameters are characterized but not tested.

**Note 1:** Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

2: Comparator Hysteresis is available when the CxHYS bit of the CMxCON0 register is enabled.

#### TABLE 30-11: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

| <b>Operating Conditions (unless otherwise stated)</b><br>VDD = $3.0V$ , TA = $25^{\circ}C$ |      |                              |      |        |       |       |          |

|--------------------------------------------------------------------------------------------|------|------------------------------|------|--------|-------|-------|----------|

| Param<br>No.                                                                               | Sym. | Characteristics              | Min. | Тур.   | Max.  | Units | Comments |

| DAC01*                                                                                     | Clsb | Step Size                    | —    | VDD/32 | _     | V     |          |

| DAC02*                                                                                     | CACC | Absolute Accuracy            | —    | —      | ± 1/2 | LSb   |          |

| DAC03*                                                                                     | CR   | Unit Resistor Value (R)      | —    | 5K     | _     | Ω     |          |

| DAC04*                                                                                     | CST  | Settling Time <sup>(1)</sup> |      | —      | 10    | μS    |          |

\* These parameters are characterized but not tested.

Note 1: Settling time measured while DACR<4:0> transitions from '0000' to '1111'.

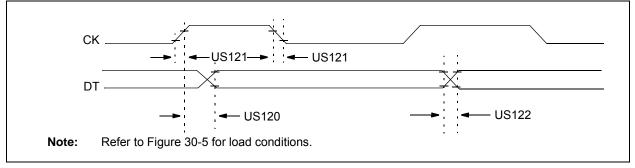

## FIGURE 30-14: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

| Param.<br>No. | Symbol | Characteristic |        | Min. | Тур† | Max. | Units | Conditions |

|---------------|--------|----------------|--------|------|------|------|-------|------------|

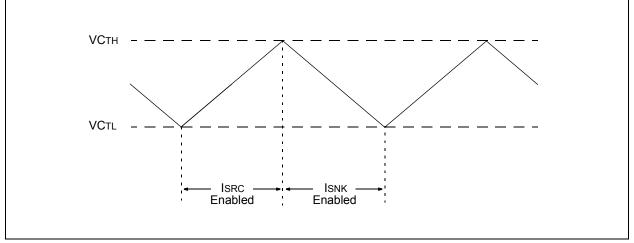

| CS01          | ISRC   | Current Source | High   | —    | -8   | —    | μA    |            |

|               |        |                | Medium |      | -1.5 |      | μA    |            |

|               |        |                | Low    | _    | -0.3 |      | μΑ    |            |

| CS02          | Isnk   | Current Sink   | High   | —    | 7.5  | _    | μA    |            |

|               |        |                | Medium | _    | 1.5  |      | μΑ    |            |

|               |        |                | Low    | —    | 0.25 |      | μA    |            |

| CS03          | VСтн   | Cap Threshold  |        | —    | 0.8  | —    | mV    |            |

| CS04          | VCTL   | Cap Threshold  |        | —    | 0.4  | —    | mV    |            |

| CS05          | VCHYST | CAP HYSTERESIS | High   | _    | 525  | —    | mV    |            |

|               |        | (VCTH - VCTL)  | Medium | —    | 375  |      | mV    |            |

|               |        |                | Low    | _    | 300  | _    | mV    |            |

## TABLE 30-17: CAP SENSE OSCILLATOR SPECIFICATIONS

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |                |          |      |  |

|--------------------------|-------------|----------------|----------|------|--|

| Dimension                | Limits      | MIN            | NOM      | MAX  |  |

| Number of Pins           | N           |                | 14       |      |  |

| Pitch                    | е           |                | 0.65 BSC |      |  |

| Overall Height           | Α           | -              | -        | 1.20 |  |

| Molded Package Thickness | A2          | 0.80           | 1.00     | 1.05 |  |

| Standoff                 | A1          | 0.05           | -        | 0.15 |  |

| Overall Width            | E           | 6.40 BSC       |          |      |  |

| Molded Package Width     | E1          | 4.30 4.40 4.50 |          |      |  |

| Molded Package Length    | D           | 4.90           | 5.00     | 5.10 |  |

| Foot Length              | L           | 0.45           | 0.60     | 0.75 |  |

| Footprint                | (L1)        | 1.00 REF       |          |      |  |

| Foot Angle               | φ           | 0°             | -        | 8°   |  |

| Lead Thickness           | С           | 0.09           | -        | 0.20 |  |

| Lead Width               | b           | 0.19 - 0.30    |          |      |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or

- protrusions shall not exceed 0.15mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-087C Sheet 2 of 2

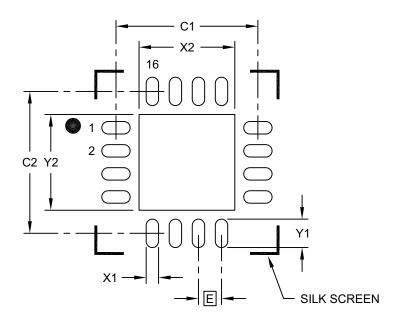

## 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                            | Units       |          |      |      |

|----------------------------|-------------|----------|------|------|

|                            | MILLIMETERS |          |      |      |

| Dimension Limits           |             | MIN      | NOM  | MAX  |

| Contact Pitch              | E           | 0.65 BSC |      |      |

| Optional Center Pad Width  | X2          | 2.70     |      |      |

| Optional Center Pad Length | Y2          | 2.70     |      |      |

| Contact Pad Spacing        | C1          |          | 4.00 |      |

| Contact Pad Spacing        | C2          |          | 4.00 |      |

| Contact Pad Width (X16)    | X1          |          |      | 0.35 |

| Contact Pad Length (X16)   | Y1          | 0.80     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2257A