Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

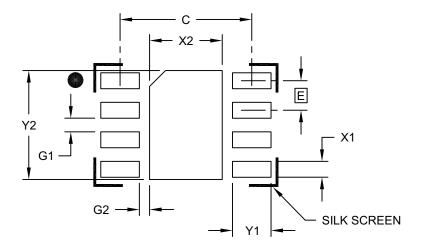

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 8-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1822-i-sn |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-3: PIC16(L)F1823 PINOUT DESCRIPTION

| Name                                                  | Function | Input<br>Type | Output<br>Type | Description                                   |

|-------------------------------------------------------|----------|---------------|----------------|-----------------------------------------------|

| RA0/AN0/CPS0/C1IN+/                                   | RA0      | TTL           | CMOS           | General purpose I/O.                          |

| DACOUT/TX <sup>(1)</sup> /CK <sup>(1)</sup> /ICSPDAT/ | AN0      | AN            | _              | A/D Channel 0 input.                          |

| ICDDAT                                                | CPS0     | AN            |                | Capacitive sensing input 0.                   |

|                                                       | C1IN+    | AN            |                | Comparator C1 positive input.                 |

|                                                       | DACOUT   | _             | AN             | Digital-to-Analog Converter output.           |

|                                                       | ТΧ       |               | CMOS           | USART asynchronous transmit.                  |

|                                                       | СК       | ST            | CMOS           | USART synchronous clock.                      |

|                                                       | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                               |

| RA1/AN1/CPS1/C12IN0-/VREF+/                           | RA1      | TTL           | CMOS           | General purpose I/O.                          |

| SRI/RX <sup>(1)</sup> /DT <sup>(1)</sup> /ICSPCLK/    | AN1      | AN            | _              | A/D Channel 1 input.                          |

| ICDCLK                                                | CPS1     | AN            | _              | Capacitive sensing input 1.                   |

|                                                       | C12IN0-  | AN            | _              | Comparator C1 or C2 negative input.           |

|                                                       | VREF+    | AN            | _              | A/D and DAC Positive Voltage Reference input. |

|                                                       | SRI      | ST            | _              | SR latch input.                               |

|                                                       | RX       | ST            | _              | USART asynchronous input.                     |

|                                                       | DT       | ST            | CMOS           | USART synchronous data.                       |

|                                                       | ICSPCLK  | ST            |                | Serial Programming Clock.                     |

| RA2/AN2/CPS2/T0CKI/INT/                               | RA2      | ST            | CMOS           | General purpose I/O.                          |

| C1OUT/SRQ/FLT0                                        | AN2      | AN            |                | A/D Channel 2 input.                          |

|                                                       | CPS2     | AN            | _              | Capacitive sensing input 2.                   |

|                                                       | TOCKI    | ST            | _              | Timer0 clock input.                           |

|                                                       | INT      | ST            | _              | External interrupt.                           |

|                                                       | C10UT    | _             | CMOS           | Comparator C1 output.                         |

|                                                       | SRQ      | _             | CMOS           | SR latch non-inverting output.                |

|                                                       | FLT0     | ST            |                | ECCP Auto-Shutdown Fault input.               |

| RA3/SS <sup>(1)</sup> /T1G <sup>(1)</sup> /VPP/MCLR   | RA3      | TTL           |                | General purpose input.                        |

|                                                       | SS       | ST            |                | Slave Select input.                           |

|                                                       | T1G      | ST            |                | Timer1 Gate input.                            |

|                                                       | VPP      | HV            |                | Programming voltage.                          |

|                                                       | MCLR     | ST            |                | Master Clear with internal pull-up.           |

| RA4/AN3/CPS3/OSC2/                                    | RA4      | TTL           | CMOS           | General purpose I/O.                          |

| CLKOUT/T1OSO/CLKR/SDO <sup>(1)</sup> /                | AN3      | AN            | _              | A/D Channel 3 input.                          |

| T1G <sup>(1)</sup>                                    | CPS3     | AN            | _              | Capacitive sensing input 3.                   |

|                                                       | OSC2     | XTAL          | XTAL           | Crystal/Resonator (LP, XT, HS modes).         |

|                                                       | CLKOUT   |               | CMOS           | Fosc/4 output.                                |

|                                                       | T10S0    | XTAL          | XTAL           | Timer1 oscillator connection.                 |

|                                                       | CLKR     |               | CMOS           | Clock Reference output.                       |

|                                                       | SDO      | —             | CMOS           | SPI data output.                              |

|                                                       | T1G      | ST            | _              | Timer1 Gate input.                            |

TTL = TTL compatible input of output  $TTL = TTL compatible input of ST = Schmitt Trigger input with CMOS levels <math>I^2C^{TM}$  = Schmitt Trigger input with I<sup>2</sup>C HV = High Voltage XTAL = Crystal levels

**Note 1:** Pin functions can be assigned to one of two pin locations via software. See APFCON register (Register 12-1).

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The High directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants  |            |      |         |      |  |

|------------|------------|------|---------|------|--|

| RETLW      | DATA0      |      | ;Index0 | data |  |

| RETLW      | DATA1      |      | ;Index1 | data |  |

| RETLW      | DATA2      |      |         |      |  |

| RETLW      | DATA3      |      |         |      |  |

| my_functi  | on         |      |         |      |  |

| ; LO       | IS OF CODE | S    |         |      |  |

| MOVLW      | LOW con    | stan | ts      |      |  |

| MOVWF      | FSR1L      |      |         |      |  |

| MOVLW      | HIGH CO    | nsta | nts     |      |  |

| MOVWF      | FSR1H      |      |         |      |  |

| MOVIW      | 0[FSR1]    |      |         |      |  |

| ; THE PROG | RAM MEMOR  | Y IS | IN W    |      |  |

|            |            |      |         |      |  |

### 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "Indirect Addressing" for more information.

#### 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation of the PIC12(L)F1822/16(L)F1823. These registers are listed below:

- INDF0

- INDF1

- PCL

- STATUS

- FSR0 Low

- FSR0 High

- FSR1 Low

- FSR1 High

- BSR

- WREG

- PCLATH

- INTCON

Note: The core registers are the first 12 addresses of every data memory bank.

# TABLE 3-7: PIC12(L)F1822/16(L)F1823 MEMORY MAP, BANK 31

|         | Bank 31                                             |  |  |  |  |  |

|---------|-----------------------------------------------------|--|--|--|--|--|

| FA0h    |                                                     |  |  |  |  |  |

|         | Unimplemented<br>Read as '0'                        |  |  |  |  |  |

| FE3h    |                                                     |  |  |  |  |  |

| FE4h    | STATUS_SHAD                                         |  |  |  |  |  |

| FE5h    | WREG_SHAD                                           |  |  |  |  |  |

| FE6h    | BSR_SHAD                                            |  |  |  |  |  |

| FE7h    | PCLATH_SHAD                                         |  |  |  |  |  |

| FE8h    | FSR0L_SHAD                                          |  |  |  |  |  |

| FE9h    | FSR0H_SHAD                                          |  |  |  |  |  |

| FEAh    | FSR1L_SHAD                                          |  |  |  |  |  |

| FEBh    | FSR1H_SHAD                                          |  |  |  |  |  |

| FECh    | —                                                   |  |  |  |  |  |

| FEDh    | STKPTR                                              |  |  |  |  |  |

| FEEh    | TOSL                                                |  |  |  |  |  |

| FEFh    | TOSH                                                |  |  |  |  |  |

| Legend: | = Unimplemented data memory locations, read as '0'. |  |  |  |  |  |

# 3.2.6 SPECIAL FUNCTION REGISTERS SUMMARY

The Special Function Register Summary for the device family are as follows:

| Device                         | Bank(s) | Page No. |

|--------------------------------|---------|----------|

|                                | 0       | 27       |

|                                | 1       | 28       |

|                                | 2       | 29       |

|                                | 3       | 30       |

|                                | 4       | 31       |

| PIC12(L)F1822<br>PIC16(L)F1823 | 5       | 32       |

|                                | 6       | 33       |

|                                | 7       | 34       |

|                                | 8       | 35       |

|                                | 9-30    | 36       |

|                                | 31      | 37       |

## 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

Internal clock sources are contained internally within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Locked Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Word 1 to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Timer1 Oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 5.3 "Clock Switching**" for more information.

#### 5.2.1.1 EC Mode

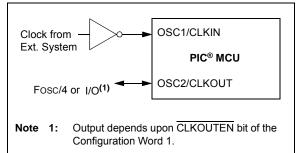

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Word 1:

- High power, 4-32 MHz (FOSC = 111)

- Medium power, 0.5-4 MHz (FOSC = 110)

- Low power, 0-0.5 MHz (FOSC = 101)

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

### 5.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 5-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 5-3 and Figure 5-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### 5.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4X PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Word 1 must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Word 1 (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4xPLL, or the PLLEN bit of the Configuration Word 2 must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Word 2, the 4xPLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4xPLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4xPLL with the internal oscillator.

### 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables of **Section 30.0** "**Electrical Specifications**".

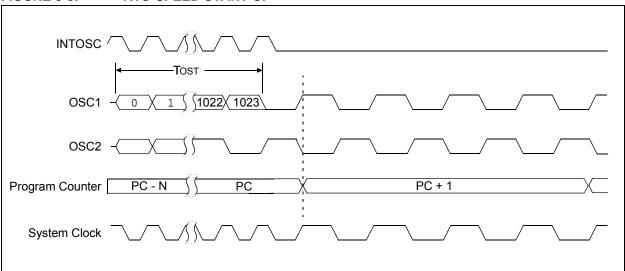

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or the internal oscillator.

#### FIGURE 5-8: TWO-SPEED START-UP

#### 8.5.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 8-2.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 8-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|--|

| TMR1GIE     | ADIE    | RCIE    | TXIE    | SSP1IE  | CCP1IE  | TMR2IE  | TMR1IE  |  |  |

| bit 7 bit 0 |         |         |         |         |         |         |         |  |  |

| Legend:          |               |                                                           |                                                       |  |  |  |

|------------------|---------------|-----------------------------------------------------------|-------------------------------------------------------|--|--|--|

| R = Readable     | bit           | W = Writable bit                                          | U = Unimplemented bit, read as '0'                    |  |  |  |

| u = Bit is unch  | anged         | x = Bit is unknown                                        | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |

| '1' = Bit is set |               | '0' = Bit is cleared                                      |                                                       |  |  |  |

|                  |               |                                                           |                                                       |  |  |  |

| bit 7            |               | mer1 Gate Interrupt Enable                                |                                                       |  |  |  |

|                  |               | he Timer1 Gate Acquisition<br>the Timer1 Gate Acquisitior |                                                       |  |  |  |

| bit 6            | ADIE: A/D Co  | onverter (ADC) Interrupt En                               | able bit                                              |  |  |  |

|                  | 1 = Enables t | he ADC interrupt                                          |                                                       |  |  |  |

|                  | 0 = Disables  | the ADC interrupt                                         |                                                       |  |  |  |

| bit 5            | RCIE: USAR    | T Receive Interrupt Enable                                | bit                                                   |  |  |  |

|                  |               | he USART receive interrupt                                |                                                       |  |  |  |

|                  |               | the USART receive interrup                                |                                                       |  |  |  |

| bit 4            |               | Transmit Interrupt Enable                                 |                                                       |  |  |  |

|                  |               | he USART transmit interrup                                |                                                       |  |  |  |

| <b>h</b> it 0    |               | the USART transmit interru                                |                                                       |  |  |  |

| bit 3            |               | chronous Serial Port (MSSF                                |                                                       |  |  |  |

|                  |               | he MSSP interrupt<br>the MSSP interrupt                   |                                                       |  |  |  |

| bit 2            |               | P1 Interrupt Enable bit                                   |                                                       |  |  |  |

| 2                |               | the CCP1 interrupt                                        |                                                       |  |  |  |

|                  |               | the CCP1 interrupt                                        |                                                       |  |  |  |

| bit 1            | TMR2IE: TM    | R2 to PR2 Match Interrupt E                               | Enable bit                                            |  |  |  |

|                  | 1 = Enables t | he Timer2 to PR2 match int                                | errupt                                                |  |  |  |

|                  | 0 = Disables  | the Timer2 to PR2 match in                                | terrupt                                               |  |  |  |

| bit 0            | TMR1IE: Tim   | er1 Overflow Interrupt Enat                               | le bit                                                |  |  |  |

|                  |               | he Timer1 overflow interrup                               |                                                       |  |  |  |

|                  | 0 = Disables  | the Timer1 overflow interrup                              | ot                                                    |  |  |  |

|                  |               |                                                           |                                                       |  |  |  |

### 11.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

#### EXAMPLE 11-6: EEPROM WRITE VERIFY

| BANKSEI | L EEDATL  | ;                    |

|---------|-----------|----------------------|

| MOVF    | EEDATL, W | ;EEDATL not changed  |

|         |           | ;from previous write |

| BSF     | EECON1, R | D ;YES, Read the     |

|         |           | ;value written       |

| XORWF   | EEDATL, W | ;                    |

| BTFSS   | STATUS, Z | ;Is data the same    |

| GOTO    | WRITE_ERR | ;No, handle error    |

| :       |           | ;Yes, continue       |

|         |           |                      |

### 12.2 PORTA Registers

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize PORTA.

Reading the PORTA register (Register 12-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The TRISA register (Register 12-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.2.1 ANSELA REGISTER

The ANSELA register (Register 12-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELA register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

#### EXAMPLE 12-1: INITIALIZING PORTA

| BANKSEL | PORTA       | i                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

| R/W-0/0          | R-q/q                 | R/W-0/0                                                                                                                                                                                                      | R/W-0/0          | R/W-0/0                   | R/W-0/0                    | R/W-0/0          | R/W-0/0      |  |  |  |

|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|----------------------------|------------------|--------------|--|--|--|

| FVREN            | FVRRDY <sup>(1)</sup> | TSEN                                                                                                                                                                                                         | TSRNG            | CDAF                      | /R<1:0>                    | ADFVI            | R<1:0>       |  |  |  |

| bit 7            |                       |                                                                                                                                                                                                              |                  |                           |                            |                  | bit (        |  |  |  |

|                  |                       |                                                                                                                                                                                                              |                  |                           |                            |                  |              |  |  |  |

| Legend:          |                       |                                                                                                                                                                                                              |                  |                           |                            |                  |              |  |  |  |

| R = Readable     | e bit                 | W = Writable                                                                                                                                                                                                 | bit              | U = Unimpler              | nented bit, read           | l as '0'         |              |  |  |  |

| u = Bit is uncl  | nanged                | x = Bit is unki                                                                                                                                                                                              | nown             | -n/n = Value a            | at POR and BO              | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set |                       | '0' = Bit is cle                                                                                                                                                                                             | ared             | q = Value dep             | pends on condit            | ion              |              |  |  |  |

| bit 7            | FVREN: Fixe           | d Voltage Refe                                                                                                                                                                                               | rence Enable     | bit                       |                            |                  |              |  |  |  |

|                  | 0 = Fixed Vo          | Itage Referenc                                                                                                                                                                                               | e is disabled    | 2.1                       |                            |                  |              |  |  |  |

| bit 6            | FVRRDY: Fix           | ed Voltage Re                                                                                                                                                                                                | ference Ready    | y Flag bit <sup>(1)</sup> |                            |                  |              |  |  |  |

|                  |                       | 0                                                                                                                                                                                                            |                  | t ready or not e          | enabled                    |                  |              |  |  |  |

|                  |                       | Itage Referenc                                                                                                                                                                                               | ·                | ady for use               |                            |                  |              |  |  |  |

| bit 5            |                       | erature Indicato                                                                                                                                                                                             |                  |                           |                            |                  |              |  |  |  |

|                  |                       | rature Indicator is disabled<br>rature Indicator is enabled                                                                                                                                                  |                  |                           |                            |                  |              |  |  |  |

| bit 4            |                       | perature Indica                                                                                                                                                                                              |                  | election bit              |                            |                  |              |  |  |  |

|                  |                       | /DD - 2VT (Low                                                                                                                                                                                               |                  |                           |                            |                  |              |  |  |  |

|                  | 1 = VOUT = V          | /DD - 4VT (High                                                                                                                                                                                              | Range)           |                           |                            |                  |              |  |  |  |

| bit 3-2          | CDAFVR<1:0            | <b>0&gt;:</b> Comparato                                                                                                                                                                                      | r and DAC Fix    | ked Voltage Re            | ference Selection          | on bits          |              |  |  |  |

|                  |                       | 00 = Comparator, DAC and CPS module Fixed Voltage Reference Peripheral output is off                                                                                                                         |                  |                           |                            |                  |              |  |  |  |

|                  |                       | 01 = Comparator, DAC and CPS module Fixed Voltage Reference Peripheral output is $1x (1.024V)$                                                                                                               |                  |                           |                            |                  |              |  |  |  |

|                  |                       | 10 = Comparator, DAC and CPS module Fixed Voltage Reference Peripheral output is $2x (2.048V)^{(2)}$<br>11 = Comparator, DAC and CPS module Fixed Voltage Reference Peripheral output is $4x (4.096V)^{(2)}$ |                  |                           |                            |                  |              |  |  |  |

| bit 1-0          | •                     |                                                                                                                                                                                                              |                  | nce Selection t           |                            |                  |              |  |  |  |

|                  |                       |                                                                                                                                                                                                              | •                | heral output is           |                            |                  |              |  |  |  |

|                  |                       | •                                                                                                                                                                                                            |                  | heral output is           |                            |                  |              |  |  |  |

|                  |                       |                                                                                                                                                                                                              |                  | heral output is           |                            |                  |              |  |  |  |

|                  | 11 = ADC Fix          | ked Voltage Re                                                                                                                                                                                               | ference Perip    | heral output is           | 4x (4.096V) <sup>(2)</sup> |                  |              |  |  |  |

| Note 1: FV       | RRDY is always        | s '1' on PIC12F                                                                                                                                                                                              | -<br>1822/16F182 | 23 only.                  |                            |                  |              |  |  |  |

|                  |                       |                                                                                                                                                                                                              |                  |                           |                            |                  |              |  |  |  |

#### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

#### TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|---------|---------|--------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR1 | CDAFVR0 | ADFVR1 | ADFVR0 | 128                 |

Legend: Shaded cells are unused by the Fixed Voltage Reference module.

<sup>2:</sup> Fixed Voltage Reference output cannot exceed VDD.

| Name                  | Bit 7        | Bit 6         | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|--------------|---------------|--------|--------|---------|---------|---------|---------|---------------------|

| ADCON0                | _            | CHS4          | CHS3   | CHS2   | CHS1    | CHS0    | GO/DONE | ADON    | 136                 |

| ADCON1                | ADFM         | ADCS2         | ADCS1  | ADCS0  | —       | —       | ADPREF1 | ADPREF0 | 137                 |

| ADRESH                | A/D Result I | Register High |        |        |         |         |         |         | 130*                |

| ADRESL                | A/D Result I | Register Low  |        |        |         |         |         |         | 130*                |

| ANSELA                | —            | —             | _      | ANSA4  | —       | ANSA2   | ANSA1   | ANSA0   | 118                 |

| ANSELC <sup>(1)</sup> | —            | _             | _      | _      | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 122                 |

| CCP1CON               | P1M1         | P1M0          | DC1B1  | DC1B0  | CCP1M3  | CCP1M2  | CCP1M1  | CCP1M0  | 213                 |

| DACCON0               | DACEN        | DACLPS        | DACOE  | _      | DACPSS1 | DACPSS0 | _       | _       | 146                 |

| DACCON1               | —            | _             | _      | DACR4  | DACR3   | DACR2   | DACR1   | DACR0   | 146                 |

| FVRCON                | FVREN        | FVRRDY        | TSEN   | TSRNG  | CDAFVR1 | CDAFVR0 | ADFVR1  | ADFVR0  | 128                 |

| INTCON                | GIE          | PEIE          | TMR0IE | INTE   | IOCE    | TMR0IF  | INTF    | IOCF    | 86                  |

| PIE1                  | TMR1GIE      | ADIE          | RCIE   | TXIE   | SSP1IE  | CCP1IE  | TMR2IE  | TMR1IE  | 87                  |

| PIR1                  | TMR1GIF      | ADIF          | RCIF   | TXIF   | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  | 89                  |

| TRISA                 | —            |               | TRISA5 | TRISA4 | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 117                 |

| TRISC <sup>(1)</sup>  | —            | _             | TRISC5 | TRISC4 | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 121                 |

#### TABLE 16-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: — = unimplemented read as '0'. Shaded cells are not used for ADC module.

\* Page provides register information.

Note 1: PIC16(L)F1823 only.

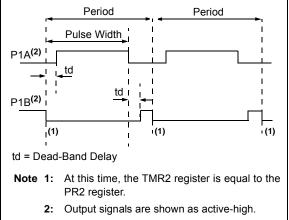

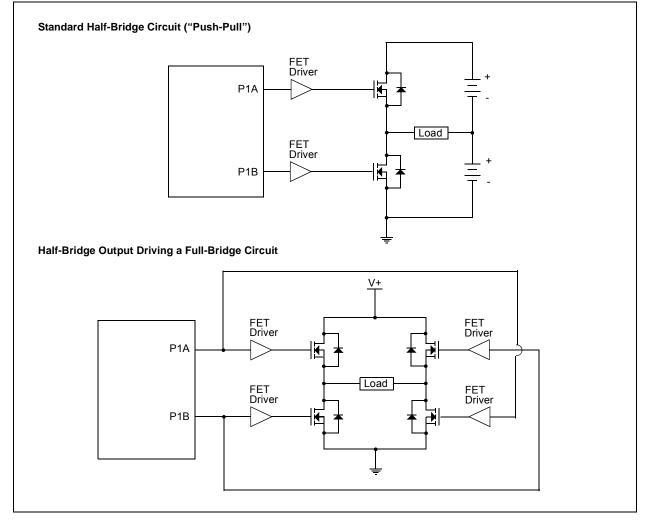

### 24.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCP1/P1A pin, while the complementary PWM output signal is output on the P1B pin (see Figure 24-9). This mode can be used for Half-Bridge applications, as shown in Figure 24-9, or for Full-Bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in Half-Bridge power devices. The value of the PDC<6:0> bits of the PWM1CON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 24.4.5 "Programmable Dead-Band Delay Mode"** for more details of the dead-band delay operations. Since the P1A and P1B outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure P1A and P1B as outputs.

### FIGURE 24-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

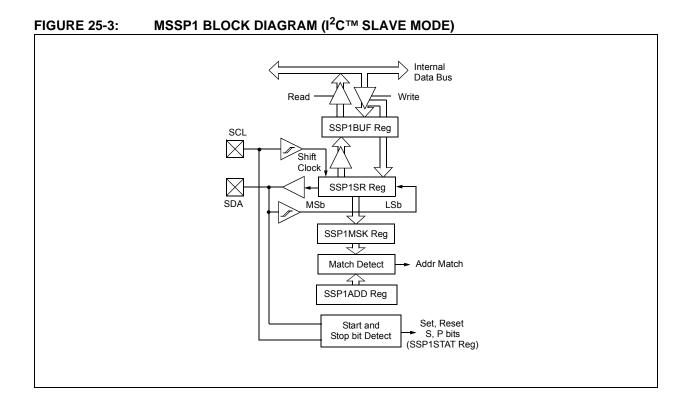

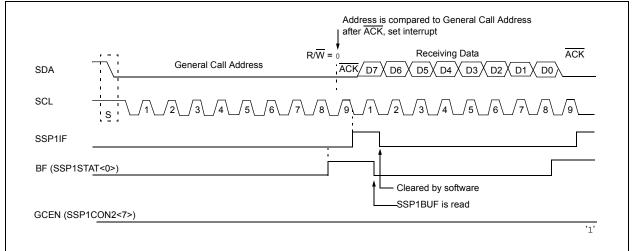

#### 25.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the I<sup>2</sup>C protocol, defined as address 0x00. When the GCEN bit of the SSP1CON2 register is set, the slave module will automatically  $\overline{ACK}$  the reception of this address regardless of the value stored in SSP1ADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave

software can read SSP1BUF and respond. Figure 25-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSP1CON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the 8th falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

#### FIGURE 25-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

#### 25.5.9 SSP1 MASK REGISTER

An SSP1 Mask (SSP1MSK) register (Register 25-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSP1SR register during an address comparison operation. A zero ('0') bit in the SSP1MSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP1 operation until written with a mask value.

The SSP1 Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP1 mask has no effect during the reception of the first (high) byte of the address.

### 26.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 26-3 contains the formulas for determining the baud rate. Example 26-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 26-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is Idle before changing the system clock.

#### EXAMPLE 26-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: Fosc Desired Baud Rate =  $\frac{1000}{64([SPBRGH:SPBRGL] + 1)}$ Solving for SPBRGH:SPBRGL: Fosc  $X = \frac{Desired Baud Rate}{-1}$ 64 16000000  $=\frac{\frac{9600}{9600}}{64}-1$ = [25.042] = 25 Calculated Baud Rate =  $\frac{16000000}{64(25+1)}$ = 9615Error = Calc. Baud Rate – Desired Baud Rate Desired Baud Rate  $=\frac{(9615-9600)}{9600} = 0.16\%$

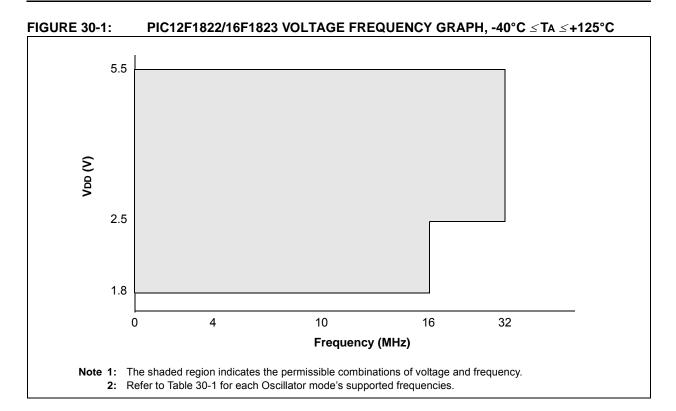

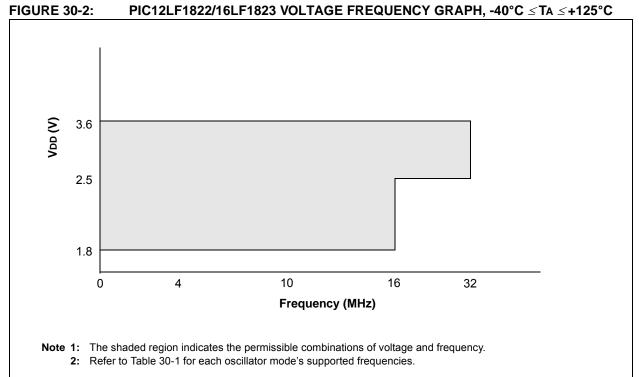

# 30.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40°C to +125°C                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Storage temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65°C to +150°C                          |

| Voltage on VDD with respect to Vss, PIC12F1822/16F1823                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.3V to +6.5V                           |

| Voltage on VDD with respect to Vss, PIC12LF1822/16LF1823                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -0.3V to +4.0V                          |

| Voltage on MCLR with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.3V to +9.0V                           |

| Voltage on all other pins with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.3V to (VDD + 0.3V)                    |

| Total power dissipation <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 800 mW                                  |

| Maximum current out of Vss pin, -40°C $\leq$ TA $\leq$ +85°C for industrial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 210 mA                                  |

| Maximum current out of Vss pin, -40°C $\leq$ TA $\leq$ +125°C for extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 95 mA                                   |