Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1823-e-sl |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-6: PIC12(L)F1822/16(L)F1823 MEMORY MAP, BANKS 24-31

|      | BANK 24                      |      | BANK 25                      |      | BANK 26                      |      | BANK 27                      |      | BANK 28                      |      | BANK 29                      |      | BANK 30                      |      | BANK 31                     |

|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|-----------------------------|

| C00h | INDF0                        | C80h | INDF0                        | D00h | INDF0                        | D80h | INDF0                        | E00h | INDF0                        | E80h | INDF0                        | F00h | INDF0                        | F80h | INDF0                       |

| C01h | INDF1                        | C81h | INDF1                        | D01h | INDF1                        | D81h | INDF1                        | E01h | INDF1                        | E81h | INDF1                        | F01h | INDF1                        | F81h | INDF1                       |

| C02h | PCL                          | C82h | PCL                          | D02h | PCL                          | D82h | PCL                          | E02h | PCL                          | E82h | PCL                          | F02h | PCL                          | F82h | PCL                         |

| C03h | STATUS                       | C83h | STATUS                       | D03h | STATUS                       | D83h | STATUS                       | E03h | STATUS                       | E83h | STATUS                       | F03h | STATUS                       | F83h | STATUS                      |

| C04h | FSR0L                        | C84h | FSR0L                        | D04h | FSR0L                        | D84h | FSR0L                        | E04h | FSR0L                        | E84h | FSR0L                        | F04h | FSR0L                        | F84h | FSR0L                       |

| C05h | FSR0H                        | C85h | FSR0H                        | D05h | FSR0H                        | D85h | FSR0H                        | E05h | FSR0H                        | E85h | FSR0H                        | F05h | FSR0H                        | F85h | FSR0H                       |

| C06h | FSR1L                        | C86h | FSR1L                        | D06h | FSR1L                        | D86h | FSR1L                        | E06h | FSR1L                        | E86h | FSR1L                        | F06h | FSR1L                        | F86h | FSR1L                       |

| C07h | FSR1H                        | C87h | FSR1H                        | D07h | FSR1H                        | D87h | FSR1H                        | E07h | FSR1H                        | E87h | FSR1H                        | F07h | FSR1H                        | F87h | FSR1H                       |

| C08h | BSR                          | C88h | BSR                          | D08h | BSR                          | D88h | BSR                          | E08h | BSR                          | E88h | BSR                          | F08h | BSR                          | F88h | BSR                         |

| C09h | WREG                         | C89h | WREG                         | D09h | WREG                         | D89h | WREG                         | E09h | WREG                         | E89h | WREG                         | F09h | WREG                         | F89h | WREG                        |

| C0Ah | PCLATH                       | C8Ah | PCLATH                       | D0Ah | PCLATH                       | D8Ah | PCLATH                       | E0Ah | PCLATH                       | E8Ah | PCLATH                       | F0Ah | PCLATH                       | F8Ah | PCLATH                      |

| C0Bh | INTCON                       | C8Bh | INTCON                       | D0Bh | INTCON                       | D8Bh | INTCON                       | E0Bh | INTCON                       | E8Bh | INTCON                       | F0Bh | INTCON                       | F8Bh | INTCON                      |

| C0Ch | _                            | C8Ch | _                            | D0Ch | _                            | D8Ch | _                            | E0Ch | _                            | E8Ch | _                            | F0Ch | _                            | F8Ch |                             |

| C0Dh | _                            | C8Dh | _                            | D0Dh | _                            | D8Dh | _                            | E0Dh | _                            | E8Dh | _                            | F0Dh | _                            | F8Dh |                             |

| C0Eh | _                            | C8Eh | _                            | D0Eh | _                            | D8Eh | _                            | E0Eh | _                            | E8Eh | _                            | F0Eh | _                            | F8Eh |                             |

| C0Fh | _                            | C8Fh | _                            | D0Fh | _                            | D8Fh | _                            | E0Fh | _                            | E8Fh | _                            | F0Fh | _                            | F8Fh |                             |

| C10h | _                            | C90h | _                            | D10h | _                            | D90h | _                            | E10h | _                            | E90h | _                            | F10h | _                            | F90h |                             |

| C11h | _                            | C91h | _                            | D11h | _                            | D91h | _                            | E11h | _                            | E91h | _                            | F11h | _                            | F91h |                             |

| C12h | _                            | C92h | _                            | D12h | _                            | D92h | _                            | E12h | _                            | E92h | _                            | F12h | _                            | F92h |                             |

| C13h | _                            | C93h | _                            | D13h | _                            | D93h | _                            | E13h | _                            | E93h | _                            | F13h | _                            | F93h |                             |

| C14h | _                            | C94h | _                            | D14h | _                            | D94h | _                            | E14h | _                            | E94h | _                            | F14h | _                            | F94h |                             |

| C15h | _                            | C95h | _                            | D15h | _                            | D95h | _                            | E15h | _                            | E95h | _                            | F15h | _                            | F95h |                             |

| C16h | _                            | C96h | _                            | D16h | _                            | D96h | _                            | E16h | _                            | E96h | _                            | F16h | _                            | F96h |                             |

| C17h | _                            | C97h | _                            | D17h | _                            | D97h | _                            | E17h | _                            | E97h | _                            | F17h | _                            | F97h |                             |

| C18h | _                            | C98h | _                            | D18h | _                            | D98h | _                            | E18h | _                            | E98h | _                            | F18h | _                            | F98h | See Table 3-7 for           |

| C19h | _                            | C99h | _                            | D19h | _                            | D99h | _                            | E19h | _                            | E99h | _                            | F19h | _                            | F99h | register mapping<br>details |

| C1Ah | _                            | C9Ah | _                            | D1Ah | _                            | D9Ah | _                            | E1Ah | _                            | E9Ah | _                            | F1Ah | _                            | F9Ah | dotano                      |

| C1Bh | _                            | C9Bh | _                            | D1Bh | _                            | D9Bh | _                            | E1Bh | _                            | E9Bh | _                            | F1Bh | _                            | F9Bh |                             |

| C1Ch | _                            | C9Ch | _                            | D1Ch | _                            | D9Ch | _                            | E1Ch | _                            | E9Ch | _                            | F1Ch | _                            | F9Ch |                             |

| C1Dh | _                            | C9Dh | _                            | D1Dh | _                            | D9Dh | _                            | E1Dh | _                            | E9Dh | _                            | F1Dh | _                            | F9Dh |                             |

| C1Eh | _                            | C9Eh | _                            | D1Eh | _                            | D9Eh | _                            | E1Eh | _                            | E9Eh | _                            | F1Eh | _                            | F9Eh |                             |

| C1Fh | _                            | C9Fh | _                            | D1Fh | _                            | D9Fh | _                            | E1Fh | _                            | E9Fh | _                            | F1Fh | _                            | F9Fh |                             |

| C20h |                              | CA0h |                              | D20h |                              | DA0h | -                            | E20h | -                            | EA0h |                              | F20h |                              | FA0h |                             |

|      | Unimplemented<br>Read as '0' |      |                             |

| C6Fh |                              | CEFh |                              | D6Fh |                              | DEFh |                              | E6Fh |                              | EEFh |                              | F6Fh |                              | FEFh |                             |

| C70h |                              | CF0h |                              | D70h |                              | DF0h |                              | E70h |                              | EF0h |                              | F70h |                              | FF0h |                             |

|      | Accesses                     |      | Accesses                    |

|      | 70h – 7Fh                    |      | 70h – 7Fh                   |

| CFFh |                              | CFFh |                              | D7Fh |                              | DFFh |                              | E7Fh |                              | EFFh |                              | F7Fh |                              | FFFh |                             |

**Legend:** = Unimplemented data memory locations, read as '0'.

| IABLE               | <u>ა-ი: ა</u>                                                                                                   |                                                                                                           | UNCTION        | REGIST                |                 |              |           | <u>(</u>              |                |                      |                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------|-----------------------|-----------------|--------------|-----------|-----------------------|----------------|----------------------|---------------------------------|

| Address             | Name                                                                                                            | Bit 7                                                                                                     | Bit 6          | Bit 5                 | Bit 4           | Bit 3        | Bit 2     | Bit 1                 | Bit 0          | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 2              | Bank 2                                                                                                          |                                                                                                           |                |                       |                 |              |           |                       |                |                      |                                 |

| 100h <sup>(1)</sup> | INDF0 Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                                                                                                           |                |                       |                 |              |           |                       | XXXX XXXX      | XXXX XXXX            |                                 |

| 101h <sup>(1)</sup> | INDF1                                                                                                           | Addressing this location uses contents of FSR1H/FSR1L to address data memory<br>(not a physical register) |                |                       |                 |              |           |                       |                | XXXX XXXX            | XXXX XXXX                       |

| 102h <sup>(1)</sup> | PCL                                                                                                             | Program Cou                                                                                               | inter (PC) Lea | st Significant E      | lyte            |              |           |                       |                | 0000 0000            | 0000 0000                       |

| 103h <sup>(1)</sup> | STATUS                                                                                                          | _                                                                                                         | _              | _                     | TO              | PD           | Z         | DC                    | С              | 1 1000               | q quuu                          |

| 104h <sup>(1)</sup> | FSR0L                                                                                                           | Indirect Data                                                                                             | Memory Addr    | ess 0 Low Poir        | nter            | •            |           | •                     | •              | 0000 0000            | uuuu uuuu                       |

| 105h <sup>(1)</sup> | FSR0H                                                                                                           | Indirect Data                                                                                             | Memory Addr    | ess 0 High Poi        | nter            |              |           |                       |                | 0000 0000            | 0000 0000                       |

| 106h <sup>(1)</sup> | FSR1L                                                                                                           | Indirect Data                                                                                             | Memory Addr    | ess 1 Low Poir        | nter            |              |           |                       |                | 0000 0000            | uuuu uuuu                       |

| 107h <sup>(1)</sup> | FSR1H                                                                                                           | Indirect Data                                                                                             | Memory Addr    | ess 1 High Poi        | nter            |              |           |                       |                | 0000 0000            | 0000 0000                       |

| 108h <sup>(1)</sup> | BSR                                                                                                             | _                                                                                                         | _              | _                     |                 |              | BSR<4:0>  |                       |                | 0 0000               | 0 0000                          |

| 109h <sup>(1)</sup> | WREG                                                                                                            | Working Reg                                                                                               | ister          |                       |                 |              |           |                       |                | 0000 0000            | uuuu uuuu                       |

| 10Ah <sup>(1)</sup> | PCLATH                                                                                                          | _                                                                                                         | Write Buffer f | or the upper 7        | bits of the Pro | ogram Counte | er        |                       |                | -000 0000            | -000 0000                       |

| 10Bh <sup>(1)</sup> | INTCON                                                                                                          | GIE                                                                                                       | PEIE           | TMR0IE                | INTE            | IOCIE        | TMR0IF    | INTF                  | IOCIF          | 0000 000x            | 0000 000u                       |

| 10Ch                | LATA                                                                                                            | _                                                                                                         | _              | LATA5                 | LATA4           |              | LATA2     | LATA1                 | LATA0          | xx -xxx              | uu -uuu                         |

| 10Dh                | —                                                                                                               | Unimplement                                                                                               | ed             |                       |                 |              |           |                       |                | _                    | _                               |

| 10Eh                | LATC <sup>(2)</sup>                                                                                             | _                                                                                                         | _              | LATC5                 | LATC4           | LATC3        | LATC2     | LATC1                 | LATC0          | xx xxxx              | uu uuuu                         |

| 10Fh                | _                                                                                                               | Unimplement                                                                                               | ed             |                       |                 |              |           | •                     |                | _                    | _                               |

| 110h                | _                                                                                                               | Unimplement                                                                                               | ed             |                       |                 |              |           |                       |                | _                    | _                               |

| 111h                | CM1CON0                                                                                                         | C10N                                                                                                      | C1OUT          | C10E                  | C1POL           |              | C1SP      | C1HYS                 | C1SYNC         | 0000 -100            | 0000 -100                       |

| 112h                | CM1CON1                                                                                                         | C1INTP                                                                                                    | C1INTN         | C1PCH                 | 1<1:0>          |              | _         | C1NCH1 <sup>(2)</sup> | C1NCH0         | 00000                | 00000                           |

| 113h                | CM2CON0 <sup>(2)</sup>                                                                                          | C2ON                                                                                                      | C2OUT          | C2OE                  | C2POL           |              | C2SP      | C2HYS                 | C2SYNC         | 0000 -100            | 0000 -100                       |

| 114h                | CM2CON1(2)                                                                                                      | C2INTP                                                                                                    | C2INTN         | C2PCH                 | 1<1:0>          |              | _         | C2NC                  | H<1:0>         | 000000               | 000000                          |

| 115h                | CMOUT                                                                                                           | _                                                                                                         | _              | _                     | _               |              | _         | MC2OUT <sup>(2)</sup> | MC10UT         | 00                   | 00                              |

| 116h                | BORCON                                                                                                          | SBOREN                                                                                                    | _              | _                     | _               | _            | _         | _                     | BORRDY         | 1 q                  | uu                              |

| 117h                | FVRCON                                                                                                          | FVREN                                                                                                     | FVRRDY         | TSEN                  | TSRNG           | CDAFV        | /R<1:0>   | ADFV                  | /R<1:0>        | 0q00 0000            | 0q00 0000                       |

| 118h                | DACCON0                                                                                                         | DACEN                                                                                                     | DACLPS         | DACOE                 | _               | DACPS        | SS<1:0>   | _                     | _              | 000- 00              | 000- 00                         |

| 119h                | DACCON1                                                                                                         | _                                                                                                         | _              | _                     |                 |              | DACR<4:0> |                       |                | 0 0000               | 0 0000                          |

| 11Ah                | SRCON0                                                                                                          | SRLEN                                                                                                     |                | SRCLK<2:0>            |                 | SRQEN        | SRNQEN    | SRPS                  | SRPR           | 0000 0000            | 0000 0000                       |

| 11Bh                | SRCON1                                                                                                          | SRSPE                                                                                                     | SRSCKE         | SRSC2E <sup>(2)</sup> | SRSC1E          | SRRPE        | SRRCKE    | SRRC2E                | SRRC1E         | 0000 0000            | 0000 0000                       |

| 11Ch                | —                                                                                                               | Unimplement                                                                                               | ed             |                       |                 |              |           |                       |                | _                    | —                               |

| 11Dh                | APFCON                                                                                                          | RXDTSEL                                                                                                   | SDOSEL         | SSSEL                 |                 | T1GSEL       | TXCKSEL   | P1BSEL <sup>(4)</sup> | CCP1SEL<br>(4) | 000- 0000            | 000- 0000                       |

| 11Eh                | —                                                                                                               | Unimplement                                                                                               | ed             |                       |                 |              |           |                       |                | _                    | —                               |

| 11Fh                | —                                                                                                               | Unimplement                                                                                               | ed             |                       |                 |              |           |                       |                | _                    | —                               |

| Logondu             |                                                                                                                 |                                                                                                           |                |                       |                 |              |           |                       |                |                      |                                 |

### TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: PIC16(L)F1823 only.

**3:** Unimplemented. Read as '1'.

4: PIC12(L)F1822 only.

© 2010-2015 Microchip Technology Inc.

#### **REGISTER 4-2: CONFIGURATION WORD 2**

|                                                                                                                                                                                                    |                                       | R/P-1/1            | R/P-1/1                      | U-1                | R/P-1/1            | R/P-1/1           | R/P-1/1    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------|--------------------|--------------------|-------------------|------------|

|                                                                                                                                                                                                    |                                       | LVP <sup>(1)</sup> | DEBUG <sup>(2)</sup>         | _                  | BORV               | STVREN            | PLLEN      |

|                                                                                                                                                                                                    |                                       | bit 13             |                              |                    |                    |                   | bit        |

| U-1                                                                                                                                                                                                | U-1                                   | U-1                | R-1                          | U-1                | U-1                | R/P-1/1           | R/P-1/1    |

| 0-1                                                                                                                                                                                                | 0-1                                   | 0-1                | Reserved                     | 0-1                | 0-1                |                   | <1:0>      |

| <br>bit 7                                                                                                                                                                                          |                                       |                    | Reserved                     |                    |                    | VIXI              | bit        |

|                                                                                                                                                                                                    |                                       |                    |                              |                    |                    |                   | Dit        |

| Legend:                                                                                                                                                                                            |                                       |                    |                              |                    |                    |                   |            |

| R = Readable bit                                                                                                                                                                                   |                                       | P = Programm       | able bit                     | U = Unimplem       | nented bit, read a | as '1'            |            |

| '0' = Bit is cleared                                                                                                                                                                               |                                       | '1' = Bit is set   |                              | -n = Value wh      | en blank or after  | Bulk Erase        |            |

|                                                                                                                                                                                                    |                                       |                    |                              |                    |                    |                   |            |

| bit 13                                                                                                                                                                                             | LVP: Low-Voltage                      |                    |                              |                    |                    |                   |            |

|                                                                                                                                                                                                    | 1 = Low-voltage p                     |                    |                              |                    |                    |                   |            |

|                                                                                                                                                                                                    | 0 = High-voltage                      |                    |                              | gramming           |                    |                   |            |

| bit 12                                                                                                                                                                                             | <b>DEBUG</b> : In-Circuit             |                    |                              |                    | eneral nurnose l   | /O nins           |            |

| <ul> <li>1 = In-Circuit Debugger disabled, ICSPCLK and ICSPDAT are general purpose I/O pins</li> <li>0 = In-Circuit Debugger enabled, ICSPCLK and ICSPDAT are dedicated to the debugger</li> </ul> |                                       |                    |                              |                    |                    | •                 |            |

| bit 11                                                                                                                                                                                             | Unimplemented:                        | Read as '1'        |                              |                    |                    |                   |            |

| bit 10                                                                                                                                                                                             | BORV: Brown-out                       | t Reset Voltage    | Selection bit <sup>(3)</sup> |                    |                    |                   |            |

|                                                                                                                                                                                                    | 1 = Brown-out Re<br>0 = Brown-out Re  | - ·                |                              |                    |                    |                   |            |

| bit 9                                                                                                                                                                                              | STVREN: Stack (<br>1 = Stack Overflow |                    |                              |                    |                    |                   |            |

|                                                                                                                                                                                                    | 0 = Stack Overflow                    |                    |                              |                    |                    |                   |            |

| bit 8                                                                                                                                                                                              | PLLEN: PLL Enal                       | ble bit            |                              |                    |                    |                   |            |

|                                                                                                                                                                                                    | 1 = 4xPLL enable                      |                    |                              |                    |                    |                   |            |

|                                                                                                                                                                                                    | 0 = 4xPLL disable                     |                    |                              |                    |                    |                   |            |

| bit 7-5                                                                                                                                                                                            | Unimplemented:                        |                    |                              |                    |                    |                   |            |

| bit 4                                                                                                                                                                                              | Reserved: This lo                     |                    | e programmed                 | to a '1'.          |                    |                   |            |

| bit 3-2                                                                                                                                                                                            | Unimplemented:                        |                    |                              | 1-14-              |                    |                   |            |

| bit 1-0                                                                                                                                                                                            | WRT<1:0>: Flash<br>11 = Write protect |                    | vrite Protection             | DItS               |                    |                   |            |

|                                                                                                                                                                                                    | 10 = 000h to 1FFI                     |                    | d, 200h to 7FFh              | n may be modifie   | d by EECON co      | ontrol            |            |

|                                                                                                                                                                                                    | 01 = 000h to 3FFI                     |                    |                              | •                  | •                  |                   |            |

|                                                                                                                                                                                                    | 00 = 000h to 7FF                      | h write-protected  | d, no addresses              | s may be modifie   | ed by EECON co     | ontrol            |            |

| Note 1: The L                                                                                                                                                                                      | VP bit cannot be p                    | rogrammed to '0    | )' when Program              | nming mode is e    | entered via LVP.   |                   |            |

| 2: The D                                                                                                                                                                                           | EBUG bit in Config                    | uration Word is I  | managed autom                | atically by device | e development to   | ols including deb | uggers and |

programmers. For normal device operation, this bit should be maintained as a '1'.3: See Vbor parameter for specific trip point voltages.

# 8.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 or PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 8.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

# 8.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 8-3 and Figure 8.3 for more details.

| REGISTER 10-1: | WDTCON: WATCHDOG TIMER CONTROL REGISTER |

|----------------|-----------------------------------------|

|                |                                         |

| U-0             | U-0              | R/W-0/0                                                            | R/W-1/1               | R/W-0/0         | R/W-1/1          | R/W-1/1         | R/W-0/0      |

|-----------------|------------------|--------------------------------------------------------------------|-----------------------|-----------------|------------------|-----------------|--------------|

| _               | _                |                                                                    |                       | WDTPS<4:0       | >                |                 | SWDTEN       |

| bit 7           |                  |                                                                    |                       |                 |                  |                 | bit          |

|                 |                  |                                                                    |                       |                 |                  |                 |              |

| Legend:         |                  |                                                                    |                       |                 |                  |                 |              |

| R = Readabl     |                  | W = Writable                                                       |                       | •               | mented bit, read |                 |              |

| u = Bit is unc  | 0                | x = Bit is unkr                                                    | nown                  | -m/n = Value    | at POR and BO    | OR/Value at all | other Resets |

| '1' = Bit is se | t                | '0' = Bit is cle                                                   | ared                  |                 |                  |                 |              |

| bit 7-6         | Unimplem         | ented: Read as '                                                   | 0'                    |                 |                  |                 |              |

| bit 5-1         | -                | :0>: Watchdog Ti                                                   |                       | elect bits      |                  |                 |              |

|                 |                  | Prescale Rate                                                      |                       |                 |                  |                 |              |

|                 |                  | 1:32 (Interval 1 m                                                 | s tvp)                |                 |                  |                 |              |

|                 |                  | 1:64 (Interval 2 m                                                 |                       |                 |                  |                 |              |

|                 | 00010 = 1        | 1:128 (Interval 4 r                                                | ns typ)               |                 |                  |                 |              |

|                 |                  | 1:256 (Interval 8 r                                                |                       |                 |                  |                 |              |

|                 |                  | 1:512 (Interval 16                                                 |                       |                 |                  |                 |              |

|                 |                  | 1:1024 (Interval 3<br>1:2048 (Interval 6                           | <b>2</b> • • <i>i</i> |                 |                  |                 |              |

|                 |                  | 1:4096 (Interval 0                                                 |                       |                 |                  |                 |              |

|                 |                  | 1:8192 (Interval 2                                                 |                       |                 |                  |                 |              |

|                 | 01001 = 1        | 1:16384 (Interval                                                  | 512 ms typ)           |                 |                  |                 |              |

|                 |                  | :32768 (Interval                                                   |                       |                 |                  |                 |              |

|                 | 01011 = 1        | 1:65536 (Interval                                                  | 2s typ) (Rese         | et value)       |                  |                 |              |

|                 | 01100 = 1        | l:131072 (2 <sup>17</sup> ) (Ir<br>l:262144 (2 <sup>18</sup> ) (Ir | iterval 4s typ)       |                 |                  |                 |              |

|                 |                  | 1:524288 (2 <sup>19</sup> ) (Ir                                    |                       |                 |                  |                 |              |

|                 | 01111 = 1        | 1:1048576 (2 <sup>20</sup> ) (                                     | Interval 32s ty       | (q)             |                  |                 |              |

|                 | 10000 = 1        | 1:2097152 (2 <sup>21</sup> ) (                                     | Interval 64s ty       | /p)             |                  |                 |              |

|                 | 10001 = 1        | I:4194304 (2 <sup>22</sup> ) (                                     | Interval 128s         | typ)            |                  |                 |              |

|                 | 10010 = 1        | 1:8388608 (2 <sup>23</sup> ) (                                     | Interval 256s         | typ)            |                  |                 |              |

|                 | 10011 <b>= F</b> | Reserved. Result                                                   | s in minimum          | interval (1:32) |                  |                 |              |

|                 | •                |                                                                    |                       |                 |                  |                 |              |

|                 | •                |                                                                    |                       |                 |                  |                 |              |

|                 | 11111 = F        | Reserved. Result                                                   | s in minimum          | interval (1:32) |                  |                 |              |

| bit 0           |                  | Software Enable/                                                   |                       |                 | bit              |                 |              |

|                 | If WDTE<1        |                                                                    |                       | 5               |                  |                 |              |

|                 | This bit is ig   | gnored.                                                            |                       |                 |                  |                 |              |

|                 | If WDTE<1        |                                                                    |                       |                 |                  |                 |              |

|                 | 1 = WDT is       |                                                                    |                       |                 |                  |                 |              |

|                 | $\cap = WDTie$   |                                                                    |                       |                 |                  |                 |              |

|                 | If WDTE<1        | s turned off                                                       |                       |                 |                  |                 |              |

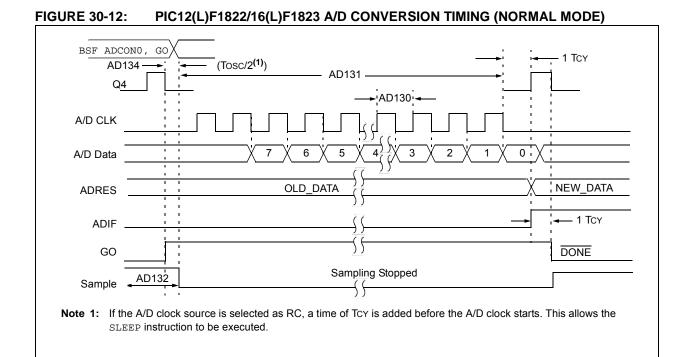

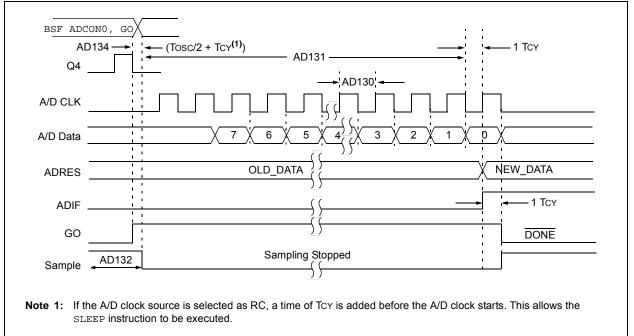

# 16.2 ADC Operation

### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 16.2.6 "A/D Conver-     |

|       | sion Procedure".                         |

### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- · Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device                   | CCP1/ECCP1 |

|--------------------------|------------|

| PIC12(L)F1822/16(L)F1823 | CCP1       |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 24.0 "Capture/Compare/PWM Modules" for more information.

| Name                  | Bit 7        | Bit 6         | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|--------------|---------------|--------|--------|---------|---------|---------|---------|---------------------|

| ADCON0                | _            | CHS4          | CHS3   | CHS2   | CHS1    | CHS0    | GO/DONE | ADON    | 136                 |

| ADCON1                | ADFM         | ADCS2         | ADCS1  | ADCS0  | —       | —       | ADPREF1 | ADPREF0 | 137                 |

| ADRESH                | A/D Result I | Register High |        |        |         |         |         |         | 130*                |

| ADRESL                | A/D Result I | Register Low  |        |        |         |         |         |         | 130*                |

| ANSELA                | —            | —             | _      | ANSA4  | —       | ANSA2   | ANSA1   | ANSA0   | 118                 |

| ANSELC <sup>(1)</sup> | —            | _             | _      | _      | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 122                 |

| CCP1CON               | P1M1         | P1M0          | DC1B1  | DC1B0  | CCP1M3  | CCP1M2  | CCP1M1  | CCP1M0  | 213                 |

| DACCON0               | DACEN        | DACLPS        | DACOE  | _      | DACPSS1 | DACPSS0 | _       | _       | 146                 |

| DACCON1               | —            | _             | _      | DACR4  | DACR3   | DACR2   | DACR1   | DACR0   | 146                 |

| FVRCON                | FVREN        | FVRRDY        | TSEN   | TSRNG  | CDAFVR1 | CDAFVR0 | ADFVR1  | ADFVR0  | 128                 |

| INTCON                | GIE          | PEIE          | TMR0IE | INTE   | IOCE    | TMR0IF  | INTF    | IOCF    | 86                  |

| PIE1                  | TMR1GIE      | ADIE          | RCIE   | TXIE   | SSP1IE  | CCP1IE  | TMR2IE  | TMR1IE  | 87                  |

| PIR1                  | TMR1GIF      | ADIF          | RCIF   | TXIF   | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  | 89                  |

| TRISA                 | —            |               | TRISA5 | TRISA4 | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 117                 |

| TRISC <sup>(1)</sup>  | —            | _             | TRISC5 | TRISC4 | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 121                 |

#### TABLE 16-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: — = unimplemented read as '0'. Shaded cells are not used for ADC module.

\* Page provides register information.

Note 1: PIC16(L)F1823 only.

# 21.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 21-1 displays the Timer1 enable selections.

| TABLE 21-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

# 21.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 21-2 displays the clock source selections.

#### 21.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 Gate

- C1 or C2 comparator input to Timer1 Gate

#### 21.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T1OSCEN | Clock Source                    |

|---------|---------|---------|---------------------------------|

| 0       | 1       | x       | System Clock (Fosc)             |

| 0       | 0       | x       | Instruction Clock (Fosc/4)      |

| 1       | 1       | x       | Capacitive Sensing Oscillator   |

| 1       | 0       | 0       | External Clocking on T1CKI Pin  |

| 1       | 0       | 1       | Osc.Circuit On T1OSI/T1OSO Pins |

### TABLE 21-2: CLOCK SOURCE SELECTIONS

### 24.4.8 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name                 | Bit 7                  | Bit 6              | Bit 5  | Bit 4    | Bit 3                | Bit 2                | Bit 1                 | Bit 0                  | Register<br>on Page |

|----------------------|------------------------|--------------------|--------|----------|----------------------|----------------------|-----------------------|------------------------|---------------------|

| APFCON               | RXDTSEL                | SDOSEL             | SSSEL  | _        | T1GSEL               | TXCKSEL              | P1BSEL <sup>(2)</sup> | CCP1SEL <sup>(2)</sup> | 114                 |

| CCP1CON              | P1M•                   | P1M<1:0> DC1B<1:0> |        |          | CCP1M<3:0>           |                      |                       |                        | 213                 |

| CCP1AS               | CCP1ASE                | CCP1AS<2:0>        |        |          | PSS1AC<1:0>          |                      | PSS1BD<1:0>           |                        | 214                 |

| INTCON               | GIE                    | PEIE               | TMR0IE | INTE     | IOCIE                | TMR0IF               | INTF                  | IOCIF                  | 86                  |

| PIE1                 | TMR1GIE                | ADIE               | RCIE   | TXIE     | SSP1IE               | CCP1IE               | TMR2IE                | TMR1IE                 | 87                  |

| PIR1                 | TMR1GIF                | ADIF               | RCIF   | TXIF     | SSP1IF               | CCP1IF               | TMR2IF                | TMR1IF                 | 89                  |

| PR2                  | Timer2 Period Register |                    |        |          |                      |                      |                       |                        | 176*                |

| PSTR1CON             | —                      | _                  | _      | STR1SYNC | STR1D <sup>(1)</sup> | STR1C <sup>(1)</sup> | STR1B                 | STR1A                  | 216                 |

| PWM1CON              | P1RSEN P1DC<6:0>       |                    |        |          |                      |                      |                       |                        | 215                 |

| T2CON                | —                      |                    | T2OUTI | PS<3:0>  |                      | TMR2ON               | T2CKPS<:0>1           |                        | 178                 |

| TMR2                 | Timer2 Module Register |                    |        |          |                      |                      |                       | 176*                   |                     |

| TRISA                | —                      | —                  | TRISA5 | TRISA4   | TRISA3               | TRISA2               | TRISA1                | TRISA0                 | 117                 |

| TRISC <sup>(1)</sup> | —                      | _                  | TRISC5 | TRISC4   | TRISC3               | TRISC2               | TRISC1                | TRISC0                 | 121                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the PWM.

\* Page provides register information.

Note 1: PIC16(L)F1823 only.

2: PIC12(L)F1822 only.

# FIGURE 29-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 13 8 7 6 0<br>OPCODE d f (FILE #)                                                     |  |  |  |  |  |  |  |  |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |  |  |  |  |  |  |  |  |

| Bit-oriented file register operations<br>13 10 9 7 6 0                                |  |  |  |  |  |  |  |  |

| OPCODE b (BIT #) f (FILE #)                                                           |  |  |  |  |  |  |  |  |

| b = 3-bit bit address<br>f = 7-bit file register address                              |  |  |  |  |  |  |  |  |

| Literal and control operations                                                        |  |  |  |  |  |  |  |  |

| General                                                                               |  |  |  |  |  |  |  |  |

|                                                                                       |  |  |  |  |  |  |  |  |

| OPCODE k (literal)                                                                    |  |  |  |  |  |  |  |  |

| k = 8-bit immediate value                                                             |  |  |  |  |  |  |  |  |

| CALL and GOTO instructions only                                                       |  |  |  |  |  |  |  |  |

| 13 11 10 0                                                                            |  |  |  |  |  |  |  |  |

| OPCODE k (literal)                                                                    |  |  |  |  |  |  |  |  |

| k = 11-bit immediate value                                                            |  |  |  |  |  |  |  |  |

| MOVLP instruction only<br>13 7 6 0                                                    |  |  |  |  |  |  |  |  |

| OPCODE k (literal)                                                                    |  |  |  |  |  |  |  |  |

| k = 7-bit immediate value                                                             |  |  |  |  |  |  |  |  |

|                                                                                       |  |  |  |  |  |  |  |  |

| MOVLB instruction only                                                                |  |  |  |  |  |  |  |  |

| 13 5 4 0<br>OPCODE k (literal)                                                        |  |  |  |  |  |  |  |  |

| k = 5-bit immediate value                                                             |  |  |  |  |  |  |  |  |

| BRA instruction only                                                                  |  |  |  |  |  |  |  |  |

|                                                                                       |  |  |  |  |  |  |  |  |

| OPCODE k (literal)                                                                    |  |  |  |  |  |  |  |  |

| k = 9-bit immediate value                                                             |  |  |  |  |  |  |  |  |

| FSR Offset instructions<br>13 7 6 5 0                                                 |  |  |  |  |  |  |  |  |

| OPCODE n k (literal)                                                                  |  |  |  |  |  |  |  |  |

| n = appropriate FSR<br>k = 6-bit immediate value                                      |  |  |  |  |  |  |  |  |

| FSR Increment instructions<br>13                                                      |  |  |  |  |  |  |  |  |

| OPCODE n m (mode)                                                                     |  |  |  |  |  |  |  |  |

| n = appropriate FSR<br>m = 2-bit mode value                                           |  |  |  |  |  |  |  |  |

| OPCODE only<br>13 0                                                                   |  |  |  |  |  |  |  |  |

| OPCODE                                                                                |  |  |  |  |  |  |  |  |

|                                                                                       |  |  |  |  |  |  |  |  |

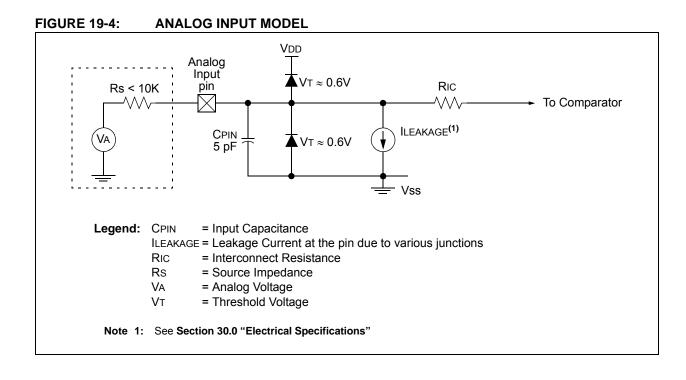

#### Standard Operating Conditions (unless otherwise stated) **DC CHARACTERISTICS** Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended Param Sym. Characteristic Min. Typ† Max. Units Conditions No. VIL Input Low Voltage I/O PORT: D030 with TTL buffer 0.8 V $4.5V \le VDD \le 5.5V$ D030A 0.15 VDD $1.8V \le VDD \le 4.5V$ V D031 with Schmitt Trigger buffer 0.2 VDD V $2.0V \le V\text{DD} \le 5.5V$ with I<sup>2</sup>C<sup>™</sup> levels 0.3 VDD V \_\_\_\_ \_ with SMBus levels 0.8 V $2.7V \leq V\text{DD} \leq 5.5V$ \_\_\_\_\_ \_ MCLR, OSC1 (RC mode)(1) D032 0.2 VDD V D033 OSC1 (HS mode) 0.3 VDD V \_ \_\_\_\_ Vін Input High Voltage I/O ports: D040 with TTL buffer 2.0 V $4.5V \le VDD \le 5.5V$ D040A 0.25 VDD + V $1.8V \le V\text{DD} \le 4.5V$ 0.8 D041 with Schmitt Trigger buffer 0.8 VDD V $2.0V \leq V\text{DD} \leq 5.5V$ with I<sup>2</sup>C<sup>™</sup> levels 0.7 VDD V with SMBus levels $2.7V \le VDD \le 5.5V$ 2.1 V D042 MCLR 0.8 VDD V \_ \_ D043A OSC1 (HS mode) 0.7 VDD V D043B OSC1 (RC mode) 0.9 VDD VDD > 2.0V, (Note 1) V Input Leakage Current<sup>(2)</sup> ١L D060 I/O ports ± 5 ± 125 nA $Vss \leq VPIN \leq VDD$ . Pin at high-impedance at 85°C ± 5 ± 1000 nA 125°C MCLR<sup>(3)</sup> D061 ± 200 $Vss \le VPIN \le VDD$ at $85^{\circ}C$ ± 50 nA Weak Pull-up Current IPUR D070\* 200 VDD = 3.3V, VPIN = VSS 25 100 25 140 300 uΑ VDD = 5.0V, VPIN = VSS Voi Output Low Voltage<sup>(4)</sup> D080 I/O ports IOL = 8mA, VDD = 5V0.6 V IOL = 6mA, VDD = 3.3VIOL = 1.8mA, VDD = 1.8V Vон Output High Voltage<sup>(4)</sup> D090 I/O ports ІОН = 3.5mA, VDD = 5V ІОН = 3mA. VDD = 3.3V VDD - 0.7 V ІОН = 1mA, VDD = 1.8V Capacitive Loading Specs on Output Pins In XT. HS and LP modes when D101\* COSC2 OSC2 pin 15 рF external clock is used to drive OSC1 D101A\* pF CIO All I/O pins 50

### 30.4 DC Characteristics: PIC12(L)F1822/16(L)F1823-I/E

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

### FIGURE 30-13: PIC12(L)F1822/16(L)F1823 A/D CONVERSION TIMING (SLEEP MODE)

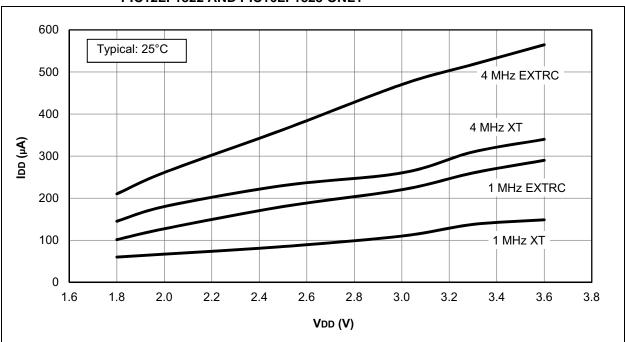

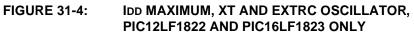

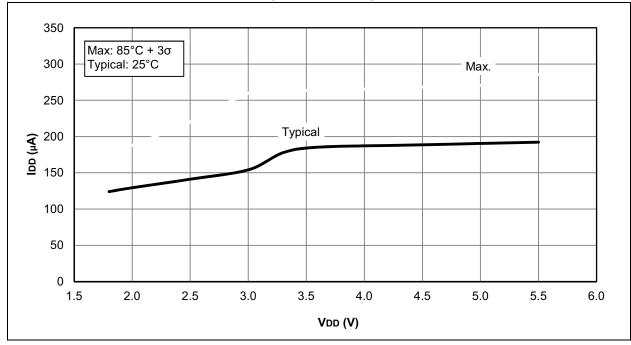

FIGURE 31-3: IDD TYPICAL, XT AND EXTRC OSCILLATOR, PIC12LF1822 AND PIC16LF1823 ONLY

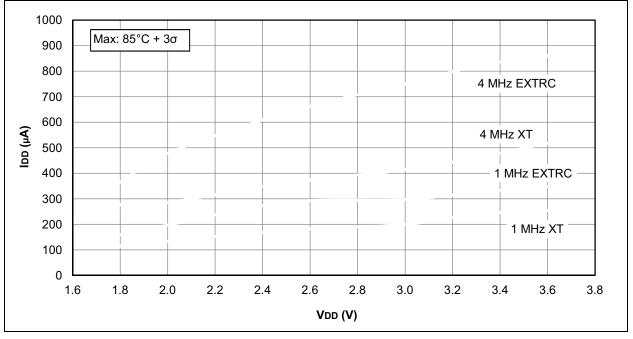

#### FIGURE 31-22: IDD, MFINTOSC MODE (Fosc = 500 kHz), PIC12F1822 AND PIC16F1823 ONLY

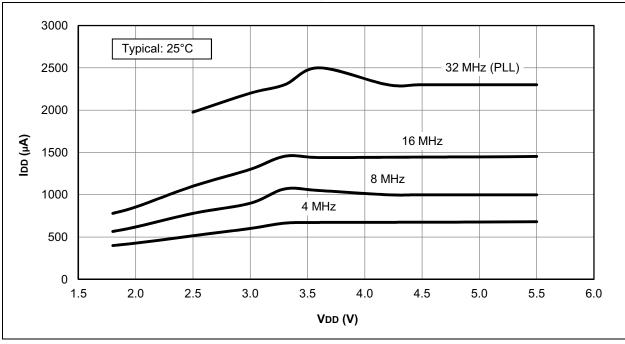

### FIGURE 31-25: IDD TYPICAL, HFINTOSC MODE, PIC12F1822 AND PIC16F1823 ONLY

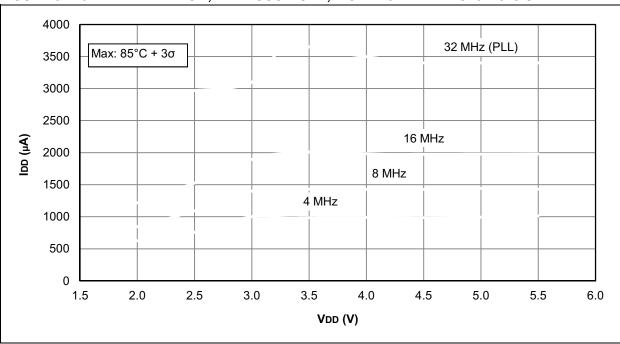

FIGURE 31-26: IDD MAXIMUM, HFINTOSC MODE, PIC12F1822 AND PIC16F1823 ONLY

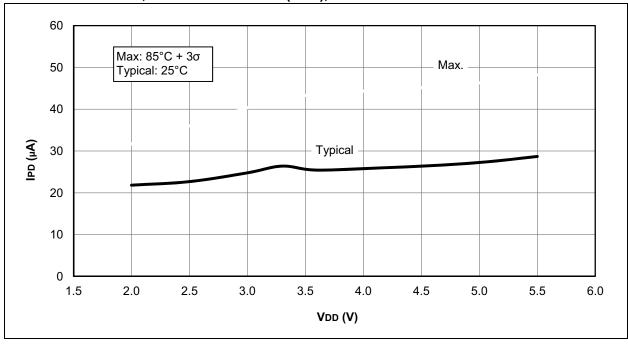

### FIGURE 31-37: IPD, BROWN-OUT RESET (BOR), PIC12F1822 AND PIC16F1823 ONLY

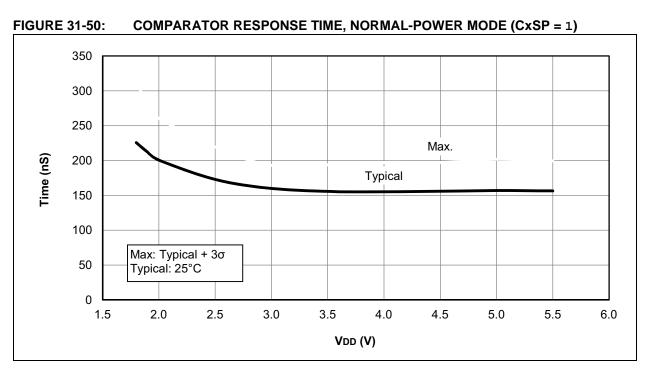

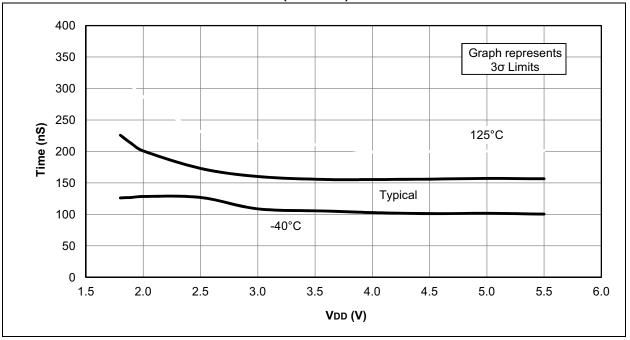

FIGURE 31-51: COMPARATOR RESPONSE TIME OVER TEMPERATURE, NORMAL-POWER MODE (CxSP = 1)

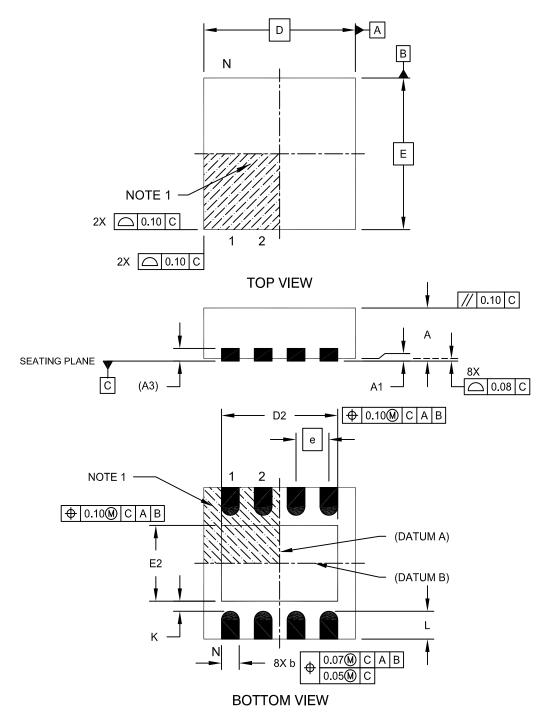

# 8-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-062C Sheet 1 of 2