Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-UQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1823-i-jq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-2:** PIC12(L)F1822 PINOUT DESCRIPTION

| Name                                                            | Function | Input<br>Type     | Output<br>Type | Description                                   |

|-----------------------------------------------------------------|----------|-------------------|----------------|-----------------------------------------------|

| RA0/AN0/CPS0/C1IN+/                                             | RA0      | TTL               | CMOS           | General purpose I/O.                          |

|                                                                 | AN0      | AN                | _              | A/D Channel 0 input.                          |

| SS <sup>(1)</sup> /P1B <sup>(1)</sup> /MDOUT/ICSPDAT/<br>ICDDAT | CPS0     | AN                |                | Capacitive sensing input 0.                   |

|                                                                 | C1IN+    | AN                | _              | Comparator C1 positive input.                 |

|                                                                 | DACOUT   |                   | AN             | Digital-to-Analog Converter output.           |

|                                                                 | ТΧ       |                   | CMOS           | USART asynchronous transmit.                  |

|                                                                 | СК       | ST                | CMOS           | USART synchronous clock.                      |

|                                                                 | SDO      |                   | CMOS           | SPI data output.                              |

|                                                                 | SS       | ST                |                | Slave Select input.                           |

|                                                                 | P1B      |                   | CMOS           | PWM output.                                   |

|                                                                 | MDOUT    |                   | CMOS           | Modulator output.                             |

|                                                                 | ICSPDAT  | ST                | CMOS           | ICSP™ Data I/O.                               |

| RA1/AN1/CPS1/VREF+/C1IN0-/                                      | RA1      | TTL               | CMOS           | General purpose I/O.                          |

| SRI/RX <sup>(1)</sup> /DT <sup>(1)</sup> /SCL/SCK/              | AN1      | AN                |                | A/D Channel 1 input.                          |

| MDMIN/ICSPCLK/ICDCLK                                            | CPS1     | AN                |                | Capacitive sensing input 1.                   |

|                                                                 | VREF+    | AN                |                | A/D and DAC Positive Voltage Reference input. |

|                                                                 | C1IN0-   | AN                | _              | Comparator C1 or C2 negative input.           |

|                                                                 | SRI      | ST                | _              | SR latch input.                               |

|                                                                 | RX       | ST                | _              | USART asynchronous input.                     |

|                                                                 | DT       | ST                | CMOS           | USART synchronous data.                       |

|                                                                 | SCL      | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C <sup>™</sup> clock.          |

|                                                                 | SCK      | ST                | CMOS           | SPI clock.                                    |

|                                                                 | MDMIN    | ST                | —              | Modulator source input.                       |

|                                                                 | ICSPCLK  | ST                | _              | Serial Programming Clock.                     |

| RA2/AN2/CPS2/C1OUT/SRQ/                                         | RA2      | ST                | CMOS           | General purpose I/O.                          |

| TOCKI/CCP1 <sup>(1)</sup> /P1A <sup>(1)</sup> /FLT0/            | AN2      | AN                | —              | A/D Channel 2 input.                          |

| SDA/SDI/INT/MDCIN1                                              | CPS2     | AN                | —              | Capacitive sensing input 2.                   |

|                                                                 | C10UT    | _                 | CMOS           | Comparator C1 output.                         |

|                                                                 | SRQ      | _                 | CMOS           | SR latch non-inverting output.                |

|                                                                 | TOCKI    | ST                | —              | Timer0 clock input.                           |

|                                                                 | CCP1     | ST                | CMOS           | Capture/Compare/PWM 1.                        |

|                                                                 | P1A      | _                 | CMOS           | PWM output.                                   |

|                                                                 | FLT0     | ST                | _              | ECCP Auto-Shutdown Fault input.               |

|                                                                 | SDA      | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C™ data input/output.          |

|                                                                 | SDI      | CMOS              | _              | SPI data input.                               |

|                                                                 | INT      | ST                | —              | External interrupt.                           |

|                                                                 | MDCIN1   | ST                | —              | Modulator Carrier Input 1.                    |

| RA3/SS <sup>(1)</sup> /T1G <sup>(1)</sup> /VPP/MCLR             | RA3      | TTL               |                | General purpose input.                        |

|                                                                 | SS       | ST                |                | Slave Select input.                           |

|                                                                 | T1G      | ST                | _              | Timer1 Gate input.                            |

|                                                                 | VPP      | HV                | _              | Programming voltage.                          |

|                                                                 | MCLR     | ST                |                | Master Clear with internal pull-up.           |

ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ TTL = TTL compatible input HV = High Voltage XTAL = Crystal levels

Note 1: Pin functions can be assigned to one of two pin locations via software. See APFCON register (Register 12-1).

### 4.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2, Code Protection and Device ID.

### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 register at 8008h.

| Note: | The DEBUG bit in Configuration Word 2 is    |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

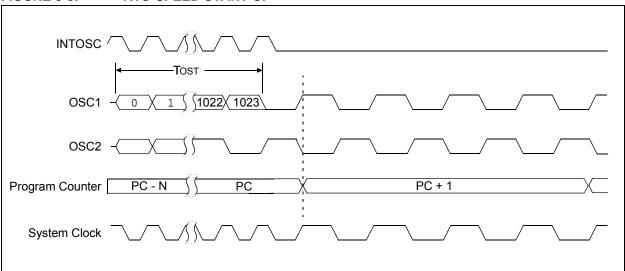

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or the internal oscillator.

### FIGURE 5-8: TWO-SPEED START-UP

| Name       | Bit 7   | Bit 6               | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|------------|---------|---------------------|--------|--------|--------|--------|--------|--------|---------------------|

| INTCON     | GIE     | PEIE                | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 86                  |

| OPTION_REG | WPUEN   | INTEDG              | TMR0CS | TMR0SE | PSA    | PS2    | PS1    | PS0    | 164                 |

| PIE1       | TMR1GIE | ADIE                | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 87                  |

| PIE2       | OSFIE   | C2IE <sup>(1)</sup> | C1IE   | EEIE   | BCL1IE | _      | _      | _      | 88                  |

| PIR1       | TMR1GIF | ADIF                | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 89                  |

| PIR2       | OSFIF   | C2IF <sup>(1)</sup> | C1IF   | EEIF   | BCL1IF | _      | _      | _      | 90                  |

#### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

Legend: — = unimplemented locations read as '0'. Shaded cells are not used by Interrupts.

Note 1: PIC16(L)F1823 only.

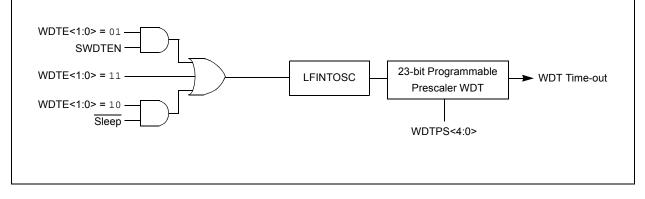

### **10.0 WATCHDOG TIMER**

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (typical)

- Multiple Reset conditions

- Operation during Sleep

### FIGURE 10-1: WATCHDOG TIMER BLOCK DIAGRAM

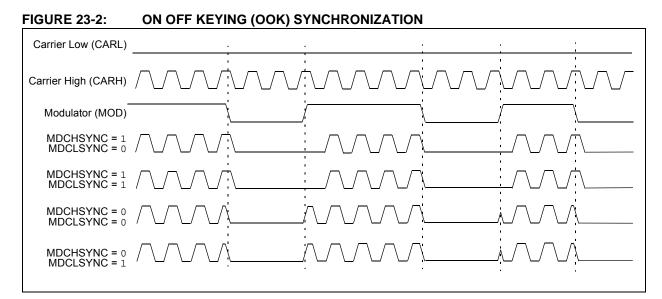

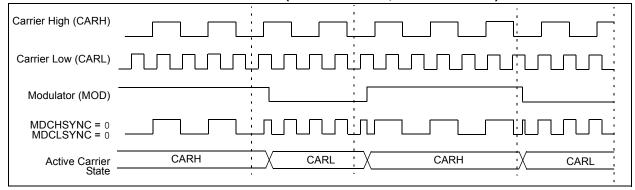

### EXAMPLE 23-1: NO SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 0)

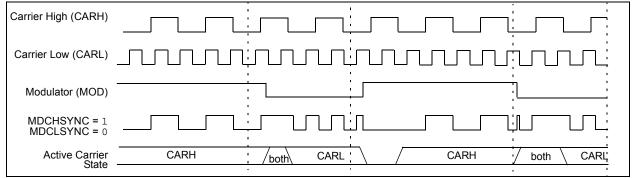

### FIGURE 23-3: CARRIER HIGH SYNCHRONIZATION (MDSHSYNC = 1, MDCLSYNC = 0)

### 24.3.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 24.3.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 24.3.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

### 24.3.9 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function**" for more information.

| Name                 | Bit 7                  | Bit 6                                         | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1                 | Bit 0                  | Register<br>on Page |

|----------------------|------------------------|-----------------------------------------------|--------|--------|--------|---------|-----------------------|------------------------|---------------------|

| APFCON               | RXDTSEL                | SDOSEL                                        | SSSEL  | —      | T1GSEL | TXCKSEL | P1BSEL <sup>(2)</sup> | CCP1SEL <sup>(2)</sup> | 114                 |

| CCP1CON              | P1M·                   | <1:0>                                         | DC1B   | <1:0>  |        | CCP1I   | V<3:0>                |                        | 213                 |

| CCPR1L               | Capture/Com            | Capture/Compare/PWM Register x Low Byte (LSB) |        |        |        |         |                       | 191                    |                     |

| INTCON               | GIE                    | PEIE                                          | TMR0IE | INTE   | IOCIE  | TMR0IF  | INTF                  | IOCIF                  | 86                  |

| PIE1                 | TMR1GIE                | ADIE                                          | RCIE   | TXIE   | SSP1IE | CCP1IE  | TMR2IE                | TMR1IE                 | 87                  |

| PIR1                 | TMR1GIF                | ADIF                                          | RCIF   | TXIF   | SSP1IF | CCP1IF  | TMR2IF                | TMR1IF                 | 89                  |

| PR2                  | Timer2 Period          | d Register                                    |        |        |        |         |                       |                        | 176*                |

| T2CON                | -                      | - T2OUTPS<3:0> TMR2ON T2CKPS<:0>1             |        |        |        |         |                       | 178                    |                     |

| TMR2                 | Timer2 Module Register |                                               |        |        |        |         |                       | 176*                   |                     |

| TRISA                | _                      | —                                             | TRISA5 | TRISA4 | TRISA3 | TRISA2  | TRISA1                | TRISA0                 | 117                 |

| TRISC <sup>(1)</sup> | _                      | _                                             | TRISC5 | TRISC4 | TRISC3 | TRISC2  | TRISC1                | TRISC0                 | 121                 |

### TABLE 24-8: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the PWM.

\* Page provides register information.

**Note 1:** PIC16(L)F1823 only.

2: PIC12(L)F1822 only.

| U-0            | U-0                  | U-0              | R/W-0/0            | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-1/1      |

|----------------|----------------------|------------------|--------------------|-----------------|-------------------|------------------|--------------|

|                |                      |                  | STR1SYNC           | STR1D           | STR1C             | STR1B            | STR1A        |

| bit 7          |                      | ·                |                    |                 |                   |                  | bit 0        |

|                |                      |                  |                    |                 |                   |                  |              |

| Legend:        |                      |                  |                    |                 |                   |                  |              |

| R = Readab     | ole bit              | W = Writable     | bit                | U = Unimpler    | mented bit, read  | l as '0'         |              |

| u = Bit is ur  | nchanged             | x = Bit is unk   | nown               | -n/n = Value a  | at POR and BO     | R/Value at all o | other Resets |

| '1' = Bit is s | et                   | '0' = Bit is cle | ared               |                 |                   |                  |              |

|                |                      |                  |                    |                 |                   |                  |              |

| bit 7-5        | Unimplemer           | nted: Read as    | 0'                 |                 |                   |                  |              |

| bit 4          | STR1SYNC:            | Steering Sync    | bit                |                 |                   |                  |              |

|                |                      | • •              | occurs on next     | •               |                   |                  |              |

|                | •                    | • .              |                    | eginning of the | e instruction cyc | le boundary      |              |

| bit 3          |                      | ering Enable bit |                    |                 |                   |                  |              |

|                |                      |                  |                    | olarity control | from CCP1M<       | 1:0>             |              |

|                | •                    | is assigned to p |                    |                 |                   |                  |              |

| bit 2          | STR1C: Stee          | ering Enable bit | : C <sup>(2)</sup> |                 |                   |                  |              |

|                | 1 = P1C pin          | has the PWM v    | vaveform with p    | olarity control | from CCP1M<       | 1:0>             |              |

|                | 0 = P1C pin i        | is assigned to p | oort pin           |                 |                   |                  |              |

| bit 1          | STR1B: Stee          | ering Enable bit | В                  |                 |                   |                  |              |

|                | 1 = P1B pin l        | has the PWM v    | vaveform with p    | olarity control | from CCP1M<       | 1:0>             |              |

|                | 0 = P1B pin i        | s assigned to p  | oort pin           |                 |                   |                  |              |

| bit 0          | STR1A: Stee          | ering Enable bit | A                  |                 |                   |                  |              |

|                | 1 = P1A pin l        | has the PWM v    | vaveform with p    | olarity control | from CCP1M<       | 1:0>             |              |

|                | 0 <b>= P1A pin i</b> | is assigned to p | port pin           |                 |                   |                  |              |

| Note 1:        | The PWM Steerin      | ia mode is avai  | lable only when    | the CCP1CO      | N register hits ( | CCP1M<3·2> =     | = 11 and     |

### **REGISTER 24-4: PSTR1CON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>**

Note 1: The PWM Steering mode is available only when the CCP1CON register bits CCP1M<3:2> = 11 and P1M<1:0> = 00.

**2:** PIC16(L)F1823 only.

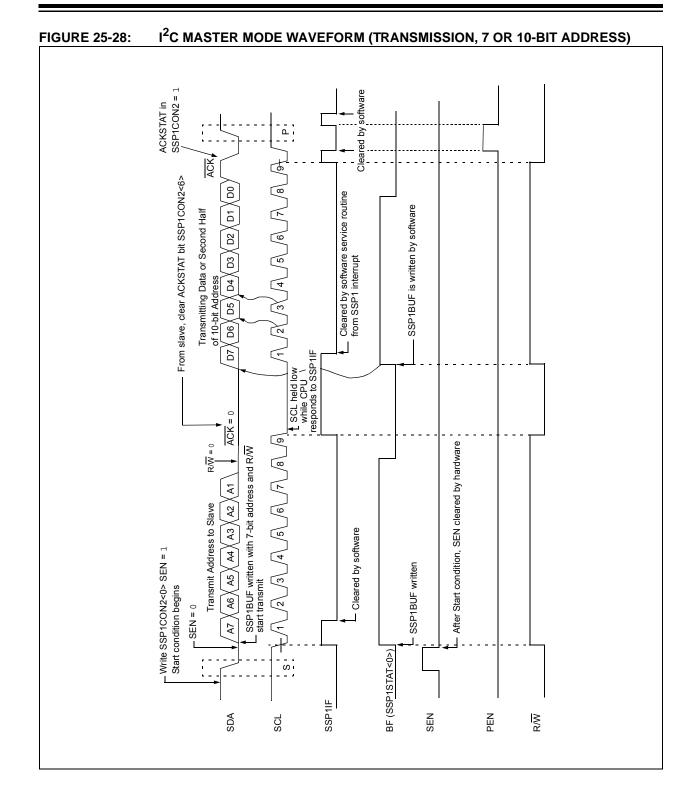

### 25.3 I<sup>2</sup>C MODE OVERVIEW

The Inter-Integrated Circuit Bus ( $I^2C$ ) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- Serial Data (SDA)

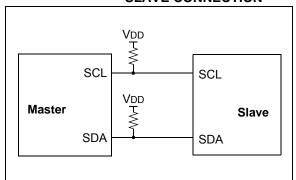

Figure 25-11 shows the block diagram of the MSSP1 module when operating in I<sup>2</sup>C mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 25-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode

(slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

### FIGURE 25-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overrightarrow{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

### REGISTER 25-1: SSP1STAT: SSP1 STATUS REGISTER

| R/W-0/0          | R/W-0/0                                                    | R-0/0                                                                                          | R-0/0              | R-0/0                | R-0/0                  | R-0/0               | R-0/0         |  |  |

|------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------|----------------------|------------------------|---------------------|---------------|--|--|

| SMP              | CKE                                                        | D/A                                                                                            | Р                  | S                    | R/W                    | UA                  | BF            |  |  |

| bit 7            |                                                            |                                                                                                |                    | 1                    | L                      | •                   | bit (         |  |  |

|                  |                                                            |                                                                                                |                    |                      |                        |                     |               |  |  |

| Legend:          |                                                            |                                                                                                |                    |                      |                        |                     |               |  |  |

| R = Readable b   | bit                                                        | W = Writable b                                                                                 | it                 | U = Unimplem         | ented bit, read as     | '0'                 |               |  |  |

| u = Bit is uncha | nged                                                       | x = Bit is unkno                                                                               | own                | -n/n = Value at      | POR and BOR/V          | alue at all other l | Resets        |  |  |

| '1' = Bit is set |                                                            | '0' = Bit is clear                                                                             | red                |                      |                        |                     |               |  |  |

|                  |                                                            |                                                                                                |                    |                      |                        |                     |               |  |  |

| bit 7            |                                                            | Input Sample bi                                                                                | t                  |                      |                        |                     |               |  |  |

|                  | <u>SPI Master mo</u>                                       | <u>de:</u><br>sampled at end c                                                                 | of data output tir | ne                   |                        |                     |               |  |  |

|                  |                                                            | sampled at middl                                                                               |                    |                      |                        |                     |               |  |  |

|                  | <u>SPI Slave mod</u>                                       |                                                                                                |                    |                      |                        |                     |               |  |  |

|                  | -                                                          | leared when SP                                                                                 | I is used in Slav  | e mode               |                        |                     |               |  |  |

|                  | $\frac{\ln I^2 C \text{ Master o}}{1 = \text{Slew rate }}$ | <u>er Slave mode:</u><br>control disabled t                                                    | for standard sne   | ed mode (100 k       | Hz and 1 MHz)          |                     |               |  |  |

|                  |                                                            | control enabled f                                                                              | •                  | •                    |                        |                     |               |  |  |

| bit 6            |                                                            | k Edge Select bi                                                                               | <b>o</b> .         | · · · ·              |                        |                     |               |  |  |

|                  | In SPI Master of                                           | or Slave mode:                                                                                 |                    |                      |                        |                     |               |  |  |

|                  |                                                            | ccurs on transitio                                                                             |                    |                      |                        |                     |               |  |  |

|                  | -                                                          | Transmit occurs on transition from Idle to active clock state                                  |                    |                      |                        |                     |               |  |  |

|                  |                                                            | <u>mode only:</u><br>ble input logic so that thresholds are compliant with SMBus specification |                    |                      |                        |                     |               |  |  |

|                  |                                                            | Bus specific inp                                                                               |                    |                      |                        |                     |               |  |  |

| bit 5            | D/A: Data/Add                                              | ress bit (I <sup>2</sup> C mod                                                                 | e only)            |                      |                        |                     |               |  |  |

|                  |                                                            | hat the last byte r                                                                            |                    |                      |                        |                     |               |  |  |

|                  |                                                            | hat the last byte r                                                                            | eceived or trans   | smitted was add      | ress                   |                     |               |  |  |

| bit 4            | <b>P:</b> Stop bit                                         | This bit is also                                                                               |                    |                      |                        |                     |               |  |  |

|                  |                                                            | at a Stop bit has                                                                              |                    |                      | disabled, SSP1EN       | is cleared.)        |               |  |  |

|                  |                                                            | s not detected la                                                                              |                    |                      | on resety              |                     |               |  |  |

| bit 3            | S: Start bit                                               |                                                                                                |                    |                      |                        |                     |               |  |  |

|                  | (I <sup>2</sup> C mode only                                | . This bit is clear                                                                            | ed when the MS     | SP1 module is        | disabled, SSP1EN       | l is cleared.)      |               |  |  |

|                  |                                                            | hat a Start bit has                                                                            |                    | last (this bit is '0 | o' on Reset)           |                     |               |  |  |

|                  | _                                                          | s not detected la                                                                              |                    |                      |                        |                     |               |  |  |

| bit 2            |                                                            | te bit information                                                                             |                    |                      | natch. This bit is o   | ally valid from the | addraga matak |  |  |

|                  |                                                            | t bit, Stop bit, or                                                                            |                    | ne last audress i    |                        | any valid from the  | address match |  |  |

|                  | In I <sup>2</sup> C Slave me                               | ode:                                                                                           |                    |                      |                        |                     |               |  |  |

|                  | 1 = Read<br>0 = Write                                      |                                                                                                |                    |                      |                        |                     |               |  |  |

|                  | In I <sup>2</sup> C Master n                               | node:                                                                                          |                    |                      |                        |                     |               |  |  |

|                  | 1 = Transmit i                                             | s in progress                                                                                  |                    |                      |                        |                     |               |  |  |

|                  |                                                            | s not in progress                                                                              |                    |                      | vill indianta if tha l | MCCD1 is in Idla    | mada          |  |  |

| 1-14 A           |                                                            |                                                                                                |                    |                      | will indicate if the I | MSSPT is in Idle    | mode.         |  |  |

| bit 1            |                                                            | ldress bit (10-bit                                                                             |                    |                      | SP1ADD register        |                     |               |  |  |

|                  |                                                            | es not need to b                                                                               | •                  |                      | INDD Tegister          |                     |               |  |  |

| bit 0            | BF: Buffer Full                                            | Status bit                                                                                     |                    |                      |                        |                     |               |  |  |

|                  | Receive (SPI a                                             |                                                                                                |                    |                      |                        |                     |               |  |  |

|                  | 1 = Receive co                                             | mplete, SSP1BL                                                                                 |                    |                      |                        |                     |               |  |  |

|                  |                                                            | t complete, SSP                                                                                | 1BUF is empty      |                      |                        |                     |               |  |  |

|                  | <u>Transmit (I<sup>2</sup>C n</u><br>1 = Data transr       |                                                                                                | loes not include   | the ACK and St       | op bits), SSP1BU       | F is full           |               |  |  |

|                  |                                                            | nit complete (doe                                                                              |                    |                      |                        |                     |               |  |  |

### 30.2 DC Characteristics: PIC12(L)F1822/16(L)F1823-I/E (Industrial, Extended)

| PIC12LF1           | 1822/16LF1823                       | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |                                         |      |       |     |                                                                               |

|--------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------|-------|-----|-------------------------------------------------------------------------------|

| PIC12F1822/16F1823 |                                     |                                                                                                                                                                                                                                                            |                                         |      |       |     | less otherwise stated)<br>A ≤ +85°C for industrial<br>A ≤ +125°C for extended |

| Param              | Device                              | Min.                                                                                                                                                                                                                                                       | Тур†                                    | Max. | Units |     | Conditions                                                                    |

| No.                | Characteristics                     |                                                                                                                                                                                                                                                            | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Шал  | onno  | Vdd | Note                                                                          |

|                    | Supply Current (IDD) <sup>(1,</sup> | 2)                                                                                                                                                                                                                                                         |                                         |      |       |     |                                                                               |

| D010               |                                     |                                                                                                                                                                                                                                                            | 5.0                                     | 15   | μA    | 1.8 | Fosc = 32 kHz, -40°C to +85°C                                                 |

|                    |                                     | _                                                                                                                                                                                                                                                          | 8.0                                     | 19   | μA    | 3.0 | LP Oscillator mode                                                            |

| D010               |                                     |                                                                                                                                                                                                                                                            | 24                                      | 36   | μΑ    | 1.8 | Fosc = 32 kHz, -40°C to +85°C                                                 |

|                    |                                     |                                                                                                                                                                                                                                                            | 30                                      | 48   | μΑ    | 3.0 | LP Oscillator mode                                                            |

|                    |                                     |                                                                                                                                                                                                                                                            | 32                                      | 66   | μA    | 5.0 |                                                                               |

| D010A              |                                     | —                                                                                                                                                                                                                                                          | 5.0                                     | 21   | μA    | 1.8 | Fosc = 32 kHz, -40°C to +125°C                                                |

|                    |                                     | _                                                                                                                                                                                                                                                          | 7.5                                     | 25   | μΑ    | 3.0 | LP Oscillator mode                                                            |

| D010A              |                                     | _                                                                                                                                                                                                                                                          | 24                                      | 60   | μΑ    | 1.8 | Fosc = 32 kHz, -40°C to +125°C                                                |

|                    |                                     | —                                                                                                                                                                                                                                                          | 30                                      | 70   | μΑ    | 3.0 | LP Oscillator mode                                                            |

|                    |                                     |                                                                                                                                                                                                                                                            | 32                                      | 80   | μA    | 5.0 |                                                                               |

| D011               |                                     | _                                                                                                                                                                                                                                                          | 60                                      | 115  | μA    | 1.8 | Fosc = 1 MHz                                                                  |

|                    |                                     | —                                                                                                                                                                                                                                                          | 111                                     | 200  | μA    | 3.0 | XT Oscillator mode                                                            |

| D011               |                                     |                                                                                                                                                                                                                                                            | 82                                      | 135  | μA    | 1.8 | Fosc = 1 MHz                                                                  |

|                    |                                     |                                                                                                                                                                                                                                                            | 141                                     | 225  | μA    | 3.0 | XT Oscillator mode                                                            |

|                    |                                     |                                                                                                                                                                                                                                                            | 200                                     | 320  | μA    | 5.0 |                                                                               |

| D012               |                                     | _                                                                                                                                                                                                                                                          | 145                                     | 280  | μA    | 1.8 | Fosc = 4 MHz                                                                  |

|                    |                                     |                                                                                                                                                                                                                                                            | 260                                     | 460  | μA    | 3.0 | XT Oscillator mode                                                            |

| D012               |                                     |                                                                                                                                                                                                                                                            | 165                                     | 300  | μA    | 1.8 | Fosc = 4 MHz                                                                  |

|                    |                                     |                                                                                                                                                                                                                                                            | 290                                     | 500  | μA    | 3.0 | XT Oscillator mode                                                            |

|                    |                                     | _                                                                                                                                                                                                                                                          | 368                                     | 700  | μA    | 5.0 |                                                                               |

| D013               |                                     |                                                                                                                                                                                                                                                            | 34                                      | 170  | μA    | 1.8 | Fosc = 1 MHz                                                                  |

|                    |                                     |                                                                                                                                                                                                                                                            | 59                                      | 250  | μA    | 3.0 | EC Oscillator mode, Medium-power mode                                         |

| D013               |                                     |                                                                                                                                                                                                                                                            | 60                                      | 200  | μA    | 1.8 | Fosc = 1 MHz                                                                  |

|                    |                                     |                                                                                                                                                                                                                                                            | 92                                      | 260  | μA    | 3.0 | EC Oscillator mode<br>Medium-power mode                                       |

|                    |                                     | —                                                                                                                                                                                                                                                          | 126                                     | 350  | μA    | 5.0 |                                                                               |

| D014               |                                     |                                                                                                                                                                                                                                                            | 118                                     | 250  | μA    | 1.8 | Fosc = 4 MHz                                                                  |

|                    |                                     | —                                                                                                                                                                                                                                                          | 210                                     | 420  | μA    | 3.0 | EC Oscillator mode,<br>Medium-power mode                                      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- **3:** 8 MHz internal RC oscillator with 4x PLL enabled.

- 4: 8 MHz crystal oscillator with 4x PLL enabled.

- 5: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

### 30.9 High Temperature Operation

This section outlines the specifications for the following devices operating in the high temperature range between  $-40^{\circ}$ C and  $150^{\circ}$ C.<sup>(2)</sup>

- PIC12F1822<sup>(4)</sup>

- PIC16F1823<sup>(4)</sup>

When the value of any parameter is identical for both the 125°C Extended and the 150°C High Temp. temperature ranges, then that value will be found in the standard specification tables shown earlier in this chapter, under the fields listed for the 125°C Extended temperature range. If the value of any parameter is unique to the 150°C High Temp. temperature range, then it will be listed here, in this section of the data sheet.

If a Silicon Errata exists for the product and it lists a modification to the 125°C Extended temperature range value, one that is also shared at the 150°C High Temp. temperature range, then that modified value will apply to both temperature ranges.

- Note 1: Writes are <u>not allowed</u> for Flash program memory above 125°C.

- 2: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- **3:** The temperature range indicator in the catalog part number and device marking is "H" for -40°C to 150°C.

Example: PIC12F1822T-H/SN indicates the device is shipped in a Tape and Reel configuration, in the SOIC package, and is rated for operation from -40°C to 150°C.

- 4: The low voltage versions of these devices, PIC12LF1822 and PIC16LF1823, is not released for operation above +125°C.

- Errata Sheet DS80502 lists various mask revisions. 150°C operation applies only to revisions A9 and later.

- 6: The Capacitive Sensing module (CPS) should not be used in High Temperature devices. Function and its parametrics are not warranted.

- Only SOIC (SN or SL), TSSOP (ST), and DFN/QFN (MF or ML) packages will be offered, not PDIP or UQFN.

| Parameter                      | Condition | Value           |

|--------------------------------|-----------|-----------------|

| Max. Current: VDD              | Source    | 15 mA           |

| Max. Current: Vss              | Sink      | 15 mA           |

| Max. Current: Pin              | Source    | 5 mA            |

| Max. Current: Pin              | Sink      | 5 mA            |

| Max. Storage Temperature       | —         | -65°C to 155°C  |

| Max. Junction Temperature      | —         | +155°C          |

| Ambient Temperature under Bias | —         | -40°C to +150°C |

### TABLE 30-18: ABSOLUTE MAXIMUM RATINGS

**Note:** Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

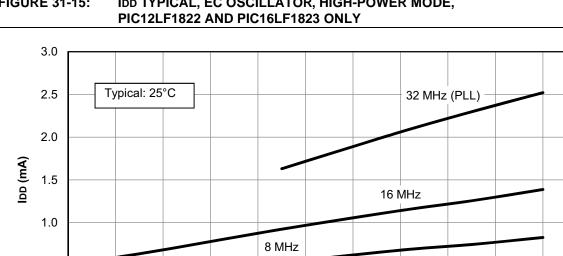

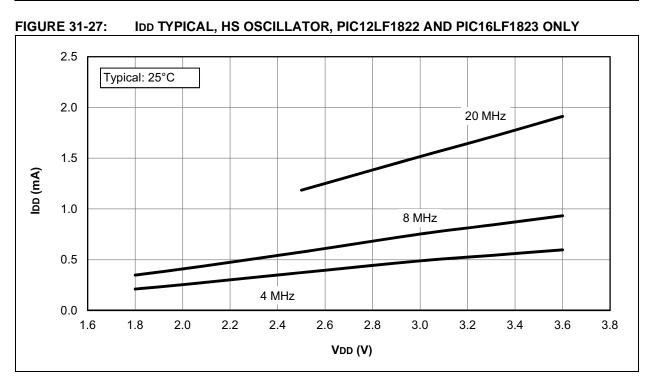

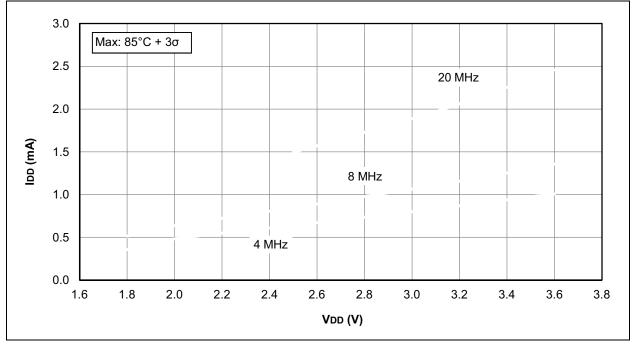

FIGURE 31-15: IDD TYPICAL, EC OSCILLATOR, HIGH-POWER MODE,

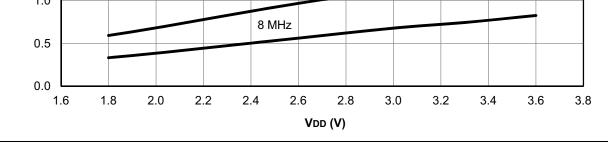

**FIGURE 31-16:** IDD MAXIMUM, EC OSCILLATOR, HIGH-POWER MODE, PIC12LF1822 AND PIC16LF1823 ONLY

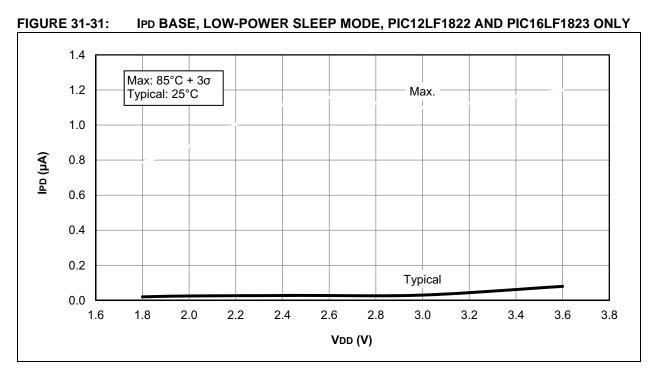

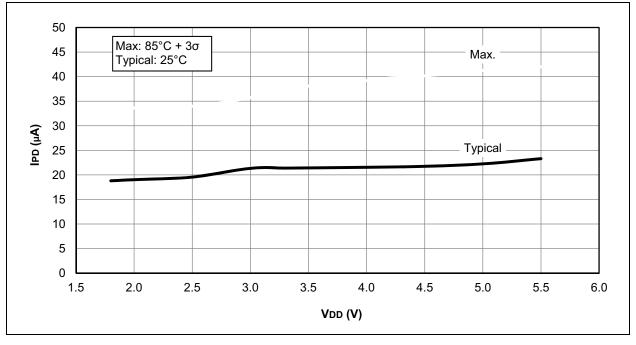

FIGURE 31-32: IPD BASE, LOW-POWER SLEEP MODE, PIC12F1822 AND PIC16F1823 ONLY

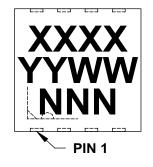

### 33.1 Package Marking Information (Continuation)

8-Lead DFN (3x3x0.9 mm) 8-Lead UDFN (3x3x0.5 mm)

Example

### TABLE 33-1: 8-LEAD 3x3x0.9 DFN (MF) TOP MARKING

| Part Number       | Marking |

|-------------------|---------|

| PIC12F1822T-E/MF  | MFLO    |

| PIC12F1822T-I/MF  | MFMO    |

| PIC12LF1822T-E/MF | MFPO    |

| PIC12LF1822T-I/MF | MFNO    |

### TABLE 33-2: 8-LEAD 3x3x0.5 UDFN (RF) TOP MARKING

| Part Number       | Marking |

|-------------------|---------|

| PIC12F1822T-E/RF  | DABO    |

| PIC12F1822T-I/RF  | DAAO    |

| PIC12LF1822T-E/RF | DAHO    |

| PIC12LF1822T-I/RF | DAGO    |

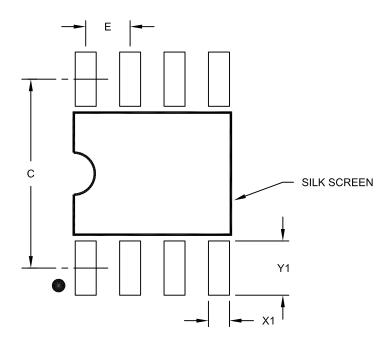

### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | MILLIMETERS |     |          |      |

|-------------------------|-------------|-----|----------|------|

| Dimension               | MIN         | NOM | MAX      |      |

| Contact Pitch           | E           |     | 1.27 BSC |      |

| Contact Pad Spacing     | С           |     | 5.40     |      |

| Contact Pad Width (X8)  | X1          |     |          | 0.60 |

| Contact Pad Length (X8) | Y1          |     |          | 1.55 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

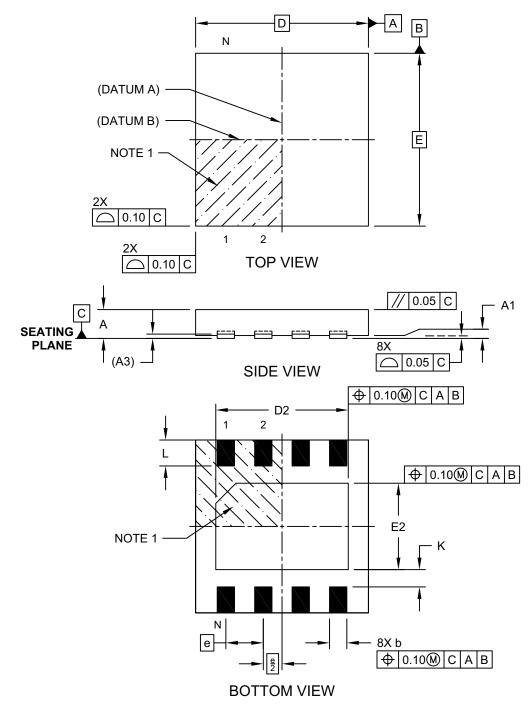

### 8-Lead Ultra Thin Plastic Dual Flat, No Lead Package (RF) - 3x3x0.50 mm Body [UDFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-254A Sheet 1 of 2