## Microchip Technology - PIC16F1823-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1823-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                               | FunctionInput<br>TypeOutput<br>Type |                   | Output<br>Type | Description                                      |  |  |

|----------------------------------------------------|-------------------------------------|-------------------|----------------|--------------------------------------------------|--|--|

| A5/CLKIN/OSC1/T1OSI/T1CKI                          | RA5                                 | TTL               | CMOS           | General purpose I/O.                             |  |  |

|                                                    | CLKIN                               | CMOS              | _              | External clock input (EC mode).                  |  |  |

|                                                    | OSC1                                | XTAL              | _              | Crystal/Resonator (LP, XT, HS modes).            |  |  |

|                                                    | T1OSI                               | XTAL              | XTAL           | Timer1 oscillator connection.                    |  |  |

|                                                    | T1CKI                               | ST                | _              | Timer1 clock input.                              |  |  |

| C0/AN4/CPS4/C2IN+/SCL/                             | RC0                                 | TTL               | CMOS           | General purpose I/O.                             |  |  |

| CK                                                 | AN4                                 | AN                | _              | A/D Channel 4 input.                             |  |  |

|                                                    | CPS4                                | AN                | _              | Capacitive sensing input 4.                      |  |  |

|                                                    | C2IN+                               | AN                |                | Comparator C2 positive input.                    |  |  |

|                                                    | SCL                                 | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C <sup>™</sup> clock.             |  |  |

|                                                    | SCK                                 | ST                | CMOS           | SPI clock.                                       |  |  |

| C1/AN5/CPS5/C12IN1-/SDA/                           | RC1                                 | TTL               | CMOS           | General purpose I/O.                             |  |  |

| DI                                                 | AN5                                 | AN                | _              | A/D Channel 5 input.                             |  |  |

|                                                    | CPS5                                | AN                | _              | Capacitive sensing input 5.                      |  |  |

|                                                    | C12IN1-                             | AN                |                | Comparator C1 or C2 negative input.              |  |  |

|                                                    | SDA                                 | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C <sup>™</sup> data input/output. |  |  |

|                                                    | SDI                                 | CMOS              |                | SPI data input.                                  |  |  |

| C2/AN6/CPS6/C12IN2-/P1D/                           | RC2                                 | TTL               | CMOS           | General purpose I/O.                             |  |  |

| DO <sup>(1)</sup> /MDCIN1                          | AN6                                 | AN                |                | A/D Channel 6 input.                             |  |  |

|                                                    | CPS6                                | AN                | _              | Capacitive sensing input 6.                      |  |  |

|                                                    | C12IN2-                             | AN                |                | Comparator C1 or C2 negative input.              |  |  |

|                                                    | P1D                                 |                   | CMOS           | PWM output.                                      |  |  |

|                                                    | SDO                                 | _                 | CMOS           | SPI data output.                                 |  |  |

|                                                    | MDCIN1                              | ST                |                | Modulator Carrier Input 1.                       |  |  |

| C3/AN7/CPS7/C12IN3-/P1C/                           | RC6                                 | TTL               | CMOS           | General purpose I/O.                             |  |  |

| S <sup>(1)</sup> /MDMIN                            | AN7                                 | AN                |                | A/D Channel 6 input.                             |  |  |

|                                                    | CPS7                                | AN                | _              | Capacitive sensing input 6.                      |  |  |

|                                                    | C12IN3-                             | AN                | _              | Comparator C1 or C2 negative input.              |  |  |

|                                                    | P1C                                 |                   | CMOS           | PWM output.                                      |  |  |

|                                                    | SS                                  | ST                |                | Slave Select input.                              |  |  |

|                                                    | MDMIN                               | ST                |                | Modulator source input.                          |  |  |

| C4/C2OUT/SRNQ/P1B/CK(1)/                           | RC4                                 | TTL               | CMOS           | General purpose I/O.                             |  |  |

| X <sup>(1)</sup> /MDOUT                            | C2OUT                               | _                 | CMOS           | Comparator C2 output.                            |  |  |

|                                                    | SRNQ                                |                   | CMOS           | SR latch inverting output.                       |  |  |

|                                                    | P1B                                 |                   | CMOS           | PWM output.                                      |  |  |

|                                                    | СК                                  | ST                | CMOS           | USART synchronous clock.                         |  |  |

|                                                    | TX                                  |                   | CMOS           | USART asynchronous transmit.                     |  |  |

|                                                    | MDOUT                               |                   | CMOS           | Modulator output.                                |  |  |

| C5/P1A/CCP1/DT <sup>(1)</sup> /RX <sup>(1)</sup> / | RC5                                 | TTL               | CMOS           | General purpose I/O.                             |  |  |

| IDCIN2                                             | P1A                                 |                   | CMOS           | PWM output.                                      |  |  |

|                                                    | CCP1                                | ST                | CMOS           | Capture/Compare/PWM 1.                           |  |  |

|                                                    | DT                                  | ST                | CMOS           | USART synchronous data.                          |  |  |

|                                                    | RX                                  | ST                | —              | USART asynchronous input.                        |  |  |

|                                                    | MDCIN2                              | ST                | _              | Modulator Carrier Input 2.                       |  |  |

## TABLE 1-3: PIC16(L)F1823 PINOUT DESCRIPTION (CONTINUED)

Note 1: Pin functions can be assigned to one of two pin locations via software. See APFCON register (Register 12-1).

## FIGURE 3-1: PROGRAM MEMORY MAP AND STACK FOR PIC12(L)F1822/16(L)F1823

|                              |                     | _              |

|------------------------------|---------------------|----------------|

|                              | PC<14:0>            |                |

| CALL<br>RETURN<br>Interrup   | · 13 .              |                |

|                              |                     |                |

|                              | •<br>Stack Level 15 |                |

|                              | Reset Vector        | 0000h          |

|                              | •                   |                |

|                              | Interrupt Vector    | 0004h          |

| On-chip<br>Program<br>Memory | Page 0              | 0005h<br>07FFh |

|                              | Rollover to Page 0  | 0800h          |

|                              | :                   |                |

|                              | Rollover to Page 0  | 7FFFh          |

## 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

## 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_IN     | DEX                 |

| CALL constants    |                     |

| ; THE CONSTANT IS | IN W                |

|                   |                     |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

Г

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### **REGISTER 3-1:** STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 29.0 "Instruction Set Summary").

| Note 1: | The C and DC bits operate as Borrow         |

|---------|---------------------------------------------|

|         | and Digit Borrow out bits, respectively, in |

|         | subtraction.                                |

| U-0              | U-0                                                                                          | U-0               | R-1/q | R-1/q                          | R/W-0/u | R/W-0/u           | R/W-0/u          |  |

|------------------|----------------------------------------------------------------------------------------------|-------------------|-------|--------------------------------|---------|-------------------|------------------|--|

| _                | _                                                                                            | —                 | TO    | PD                             | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |

| bit 7            |                                                                                              |                   |       |                                |         |                   | bit 0            |  |

|                  |                                                                                              |                   |       |                                |         |                   |                  |  |

| Legend:          | Legend:                                                                                      |                   |       |                                |         |                   |                  |  |

| R = Readable b   | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                         |                   |       |                                |         |                   |                  |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset |                   |       |                                |         | ther Resets       |                  |  |

| '1' = Bit is set |                                                                                              | '0' = Bit is clea | ared  | q = Value depends on condition |         |                   |                  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-down bit                                                                                                                                                      |

|         | 1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                            |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit <sup>(1)</sup>                                                                                                                         |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup>                                                                                                                                      |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1. | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                                   |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

| Address             | Name                | Bit 7                          | Bit 6          | Bit 5            | Bit 4           | Bit 3        | Bit 2       | Bit 1   | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------------------|---------------------|--------------------------------|----------------|------------------|-----------------|--------------|-------------|---------|-------|----------------------|---------------------------------|

| Bank 4              | Bank 4              |                                |                |                  |                 |              |             |         |       |                      |                                 |

| 200h <sup>(1)</sup> | INDF0               | Addressing th<br>(not a physic |                | es contents of   | FSR0H/FSR0      | L to address | data memory | ,       |       | XXXX XXXX            | XXXX XXXX                       |

| 201h <sup>(1)</sup> | INDF1               | Addressing th<br>(not a physic |                | es contents of   | FSR1H/FSR1      | L to address | data memory | ,       |       | XXXX XXXX            | XXXX XXXX                       |

| 202h <sup>(1)</sup> | PCL                 | Program Cou                    | inter (PC) Lea | st Significant E | Byte            |              |             |         |       | 0000 0000            | 0000 0000                       |

| 203h <sup>(1)</sup> | STATUS              | _                              | _              | _                | TO              | PD           | Z           | DC      | С     | 1 1000               | q quuu                          |

| 204h <sup>(1)</sup> | FSR0L               | Indirect Data                  | Memory Addr    | ess 0 Low Poir   | nter            |              |             |         |       | 0000 0000            | uuuu uuuu                       |

| 205h <sup>(1)</sup> | FSR0H               | Indirect Data                  | Memory Addr    | ess 0 High Poi   | nter            |              |             |         |       | 0000 0000            | 0000 0000                       |

| 206h <sup>(1)</sup> | FSR1L               | Indirect Data                  | Memory Addr    | ess 1 Low Poir   | nter            |              |             |         |       | 0000 0000            | uuuu uuuu                       |

| 207h <sup>(1)</sup> | FSR1H               | Indirect Data                  | Memory Addr    | ess 1 High Poi   | nter            |              |             |         |       | 0000 0000            | 0000 0000                       |

| 208h <sup>(1)</sup> | BSR                 | _                              | _              | _                |                 |              | BSR<4:0>    |         |       | 0 0000               | 0 0000                          |

| 209h <sup>(1)</sup> | WREG                | Working Reg                    | ister          | •                | •               |              |             |         |       | 0000 0000            | uuuu uuuu                       |

| 20Ah <sup>(1)</sup> | PCLATH              | _                              | Write Buffer f | or the upper 7   | bits of the Pro | ogram Counte | er          |         |       | -000 0000            | -000 0000                       |

| 20Bh <sup>(1)</sup> | INTCON              | GIE                            | PEIE           | TMR0IE           | INTE            | IOCIE        | TMR0IF      | INTF    | IOCIF | 0000 000x            | 0000 000u                       |

| 20Ch                | WPUA                | _                              | —              | WPUA5            | WPUA4           | WPUA3        | WPUA2       | WPUA1   | WPUA0 | 11 1111              | 11 1111                         |

| 20Dh                | —                   | Unimplement                    | ted            | •                | •               | •            | •           |         | •     | _                    | _                               |

| 20Eh                | WPUC <sup>(2)</sup> | _                              | _              | WPUC5            | WPUC4           | WPUC3        | WPUC2       | WPUC1   | WPUC0 | 11 1111              | 11 1111                         |

| 20Fh                | —                   | Unimplement                    | ted            | •                |                 |              |             |         | •     | _                    | _                               |

| 210h                | _                   | Unimplement                    | ted            |                  |                 |              |             |         |       | _                    | _                               |

| 211h                | SSP1BUF             | Synchronous                    | Serial Port Re | eceive Buffer/T  | ransmit Regis   | ster         |             |         |       | xxxx xxxx            | uuuu uuuu                       |

| 212h                | SSP1ADD             |                                |                |                  | ADD<            | 7:0>         |             |         |       | 0000 0000            | 0000 0000                       |

| 213h                | SSP1MSK             |                                |                |                  | MSK<            | 7:0>         |             |         |       | 1111 1111            | 1111 1111                       |

| 214h                | SSP1STAT            | SMP                            | CKE            | D/A              | Р               | S            | R/W         | UA      | BF    | 0000 0000            | 0000 0000                       |

| 215h                | SSP1CON1            | WCOL                           | SSPOV          | SSPEN            | CKP             |              | SSPN        | //<3:0> |       | 0000 0000            | 0000 0000                       |

| 216h                | SSP1CON2            | GCEN                           | ACKSTAT        | ACKDT            | ACKEN           | RCEN         | PEN         | RSEN    | SEN   | 0000 0000            | 0000 0000                       |

| 217h                | SSP1CON3            | ACKTIM                         | PCIE           | SCIE             | BOEN            | SDAHT        | SBCDE       | AHEN    | DHEN  | 0000 0000            | 0000 0000                       |

| 218h                | _                   | Unimplement                    | ted            |                  |                 |              |             |         |       | _                    | _                               |

| 219h                | _                   | Unimplemented                  |                |                  |                 |              |             |         | _     | _                    |                                 |

| 21Ah                | _                   | Unimplemented                  |                |                  |                 |              |             |         | _     | _                    |                                 |

| 21Bh                | _                   | Unimplemented                  |                |                  |                 |              |             |         | _     | _                    |                                 |

| 21Ch                | _                   | Unimplement                    | Unimplemented  |                  |                 |              |             |         |       |                      | _                               |

| 21Dh                | _                   | Unimplement                    | Jnimplemented  |                  |                 |              |             |         |       |                      | _                               |

| 21Eh                | _                   | Unimplement                    | ted            |                  |                 |              |             |         |       | _                    | _                               |

| 21Fh                | _                   | Unimplement                    | ted            |                  |                 |              |             |         |       | _                    | —                               |

## TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: PIC16(L)F1823 only.

**3:** Unimplemented. Read as '1'.

4: PIC12(L)F1822 only.

© 2010-2015 Microchip Technology Inc.

| R-1/q            | R-0/q                                                                                                                                      | R-q/q                                                     | R-0/q            | R-0/q            | R-q/q            | R-0/0            | R-0/q        |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------|------------------|------------------|------------------|--------------|--|

| T1OSCR           | PLLR                                                                                                                                       | OSTS                                                      | HFIOFR           | HFIOFL           | MFIOFR           | LFIOFR           | HFIOFS       |  |

| bit 7            |                                                                                                                                            |                                                           |                  |                  |                  |                  | bit 0        |  |

|                  |                                                                                                                                            |                                                           |                  |                  |                  |                  |              |  |

| Legend:          |                                                                                                                                            |                                                           |                  |                  |                  |                  |              |  |

| R = Readable     |                                                                                                                                            | W = Writable                                              |                  | •                | mented bit, read |                  |              |  |

| u = Bit is uncl  | hanged                                                                                                                                     | x = Bit is unk                                            | nown             | -n/n = Value a   | at POR and BO    | R/Value at all o | other Resets |  |

| '1' = Bit is set |                                                                                                                                            | '0' = Bit is cle                                          | ared             | q = Condition    | al               |                  |              |  |

| bit 7            | <u>If T1OSCEN</u><br>1 = Timer1<br>0 = Timer1<br><u>If T1OSCEN</u>                                                                         | oscillator is rea                                         | dy<br>ready      |                  |                  |                  |              |  |

| bit 6            | <b>PLLR</b> 4x PL<br>1 = 4x PLL<br>0 = 4x PLL                                                                                              | L Ready bit<br>is ready                                   | ulways ready     |                  |                  |                  |              |  |

| bit 5            | 1 = Runnin                                                                                                                                 | llator Start-up T<br>g from the clocl<br>g from an interr | k defined by the | e FOSC<2:0> ł    |                  | guration Word    | 1            |  |

| bit 4            | <ul> <li>HFIOFR: High Frequency Internal Oscillator Ready bit</li> <li>1 = HFINTOSC is ready</li> <li>0 = HFINTOSC is not ready</li> </ul> |                                                           |                  |                  |                  |                  |              |  |

| bit 3            | 1 = HFINTC                                                                                                                                 | gh Frequency Ir<br>DSC is at least 2<br>DSC is not 2% a   | 2% accurate      | or Locked bit    |                  |                  |              |  |

| bit 2            | 1 = MFINTC                                                                                                                                 | edium Frequend<br>DSC is ready<br>DSC is not read         | -                | illator Ready bi | it               |                  |              |  |

| bit 1            | 1 = LFINTO                                                                                                                                 | w Frequency In<br>SC is ready<br>SC is not ready          |                  | r Ready bit      |                  |                  |              |  |

| bit 0            | 1 = HFINTC                                                                                                                                 | gh Frequency Ir<br>DSC is at least (<br>DSC is not 0.5%   | ).5% accurate    | or Stable bit    |                  |                  |              |  |

## REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

## EXAMPLE 11-2: DATA EEPROM WRITE

|                      | MOVWF<br>MOVLW<br>MOVWF             | DATA_EE_ADDR<br>EEADRL<br>DATA_EE_DATA<br>EEDATL<br>EECON1, CFGS | ;Data Memory Address to write<br>;<br>;Data Memory Value to write<br>;Deselect Configuration space<br>;Point to DATA memory |

|----------------------|-------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Required<br>Sequence | MOVLW<br>MOVWF<br>BSF<br>BSF<br>BCF | EECON2<br>OAAh<br>EECON2<br>EECON1, WR<br>INTCON, GIE            | ;<br>;Write 55h<br>;<br>;Write AAh<br>;Set WR bit to begin write<br>;Enable Interrupts<br>;Disable writes                   |

|                              | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4              | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    |

|------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------|--------------------------------|--------------------------------|

| Flash ADDR                   | <br>{                          | PC + 1                         | EEADRH,EEADRL                  | PC + 3                   | PC + 4                         | PC + 5                         |

| Flash Data                   |                                | STR (PC) INST                  | R (PC + 1) EEDA                |                          | R (PC + 3) INST                | R (PC + 4)                     |

|                              | INSTR(PC - 1)<br>executed here | BSF EECON1,RD<br>executed here | INSTR(PC + 1)<br>executed here | Forced NOP executed here | INSTR(PC + 3)<br>executed here | INSTR(PC + 4)<br>executed here |

| RD bit                       | <br>                           | <br>                           | /                              |                          | <br>                           |                                |

| EEDATH<br>EEDATL<br>Register | <br>                           |                                |                                | Χ                        |                                |                                |

| EERHLT                       | <br> <br>                      | <br> <br>                      |                                |                          | <br>  <br>                     |                                |

### REGISTER 11-1: EEDATL: EEPROM DATA REGISTER

| R/W-x/u              | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u           | R/W-x/u              | R/W-x/u              | R/W-x/u |

|----------------------|---------|----------------------|---------|-------------------|----------------------|----------------------|---------|

|                      |         |                      | EEDA    | T<7:0>            |                      |                      |         |

| bit 7                |         |                      |         |                   |                      |                      | bit (   |

|                      |         |                      |         |                   |                      |                      |         |

| Legend:              |         |                      |         |                   |                      |                      |         |

| R = Readable bit     |         | W = Writable bit     |         | U = Unimpleme     | nted bit, read as '0 | ,                    |         |

| u = Bit is unchanged |         | x = Bit is unknown   |         | -n/n = Value at F | OR and BOR/Valu      | ue at all other Rese | ts      |

| '1' = Bit is set     |         | '0' = Bit is cleared |         |                   |                      |                      |         |

bit 7-0

'1' = Bit is set

EEDAT<7:0>: Read/write value for EEPROM data byte or Least Significant bits of program memory

### REGISTER 11-2: EEDATH: EEPROM DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | EEDA    | T<13:8> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

| DIL 7-0 | Unimplementeu. Reau as 0   |

bit 5-0 EEDAT<13:8>: Read/write value for Most Significant bits of program memory

## REGISTER 11-3: EEADRL: EEPROM ADDRESS REGISTER

'0' = Bit is cleared

| R/W-0/0             | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0           | R/W-0/0              | R/W-0/0              | R/W-0/0 |

|---------------------|---------|-------------------|---------|-------------------|----------------------|----------------------|---------|

|                     |         |                   | EEAD    | R<7:0>            |                      |                      |         |

| bit 7               |         |                   |         |                   |                      |                      | bit 0   |

|                     |         |                   |         |                   |                      |                      |         |

| Legend:             |         |                   |         |                   |                      |                      |         |

| R = Readable bit    |         | W = Writable bit  |         | U = Unimpleme     | nted bit, read as '0 | 3                    |         |

| u = Bit is unchange | ed      | x = Bit is unknow | 'n      | -n/n = Value at F | POR and BOR/Valu     | ue at all other Rese | ets     |

bit 7-0 EEADR<7:0>: Specifies the Least Significant bits for program memory address or EEPROM address

### **REGISTER 11-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER**

| U-1                 | R/W-0/0 | R/W-0/0              | R/W-0/0 | R/W-0/0           | R/W-0/0              | R/W-0/0             | R/W-0/0 |

|---------------------|---------|----------------------|---------|-------------------|----------------------|---------------------|---------|

| (1)                 |         |                      |         | EEADR<14:8>       |                      |                     |         |

| bit 7               |         |                      |         |                   |                      |                     | bit 0   |

|                     |         |                      |         |                   |                      |                     |         |

| Legend:             |         |                      |         |                   |                      |                     |         |

| R = Readable bit    |         | W = Writable bit     |         | U = Unimplemer    | nted bit, read as '0 | 3                   |         |

| u = Bit is unchange | ed      | x = Bit is unknowr   | ı       | -n/n = Value at F | OR and BOR/Valu      | ue at all other Res | ets     |

| '1' = Bit is set    |         | '0' = Bit is cleared |         |                   |                      |                     |         |

bit 7 Unimplemented: Read as '1'

bit 6-0 **EEADR<14:8**>: Specifies the Most Significant bits for program memory address or EEPROM address

Note 1: Unimplemented, read as '1'.

## 19.7 Comparator Negative Input Selection

The CxNCH<1:0> bits of the CMxCON0 register direct one of four analog pins to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog<br>input, the appropriate bits must be set in<br>the ANSEL register and the correspond- |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

|       | ing TRIS bits must also be set to disable the output drivers.                                                                  |

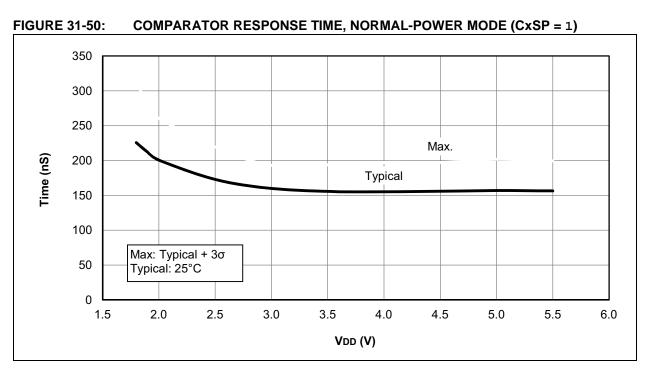

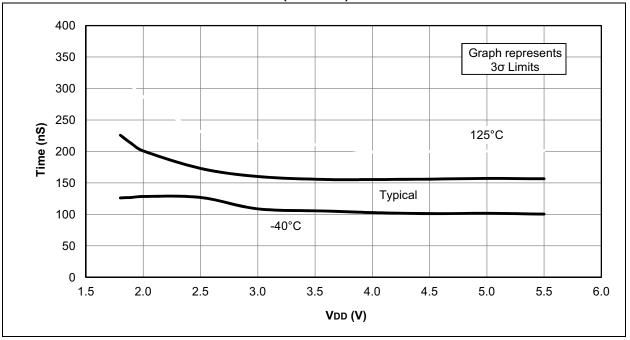

## 19.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 30.0 "Electrical Specifications"** for more details.

## **19.9** Interaction with ECCP Logic

The C1 and C2 comparators can be used as general purpose comparators. Their outputs can be brought out to the C1OUT and C2OUT pins. When the ECCP Auto-Shutdown is active it can use one or both comparator signals. If auto-restart is also enabled, the comparators can be configured as a closed loop analog feedback to the ECCP, thereby, creating an analog controlled PWM.

Note: When the Comparator module is first initialized the output state is unknown. Upon initialization, the user should verify the output state of the comparator prior to relying on the result, primarily when using the result in connection with other peripheral features, such as the ECCP Auto-Shutdown mode.

## 19.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 19-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### 21.7 **Timer1 Interrupt**

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- · PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

The TMR1H:TMR1L register pair and the Note: TMR1IF bit should be cleared before enabling interrupts.

#### 21.8 **Timer1 Operation During Sleep**

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- T1OSCEN bit of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the  $\overline{\text{T1SYNC}}$  bit setting.

#### 21.9 ECCP/CCP Capture/Compare Time Base

The CCP1 module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 24.0 "Capture/Compare/PWM Modules".

## 21.10 ECCP/CCP Special Event Trigger

When any of the CCP's are configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized and Fosc/4 should be selected as the clock source in order to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see Section 16.2.5 "Special Event Trigger".

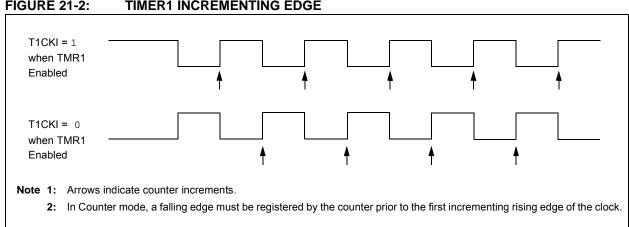

#### **FIGURE 21-2:** TIMER1 INCREMENTING EDGE

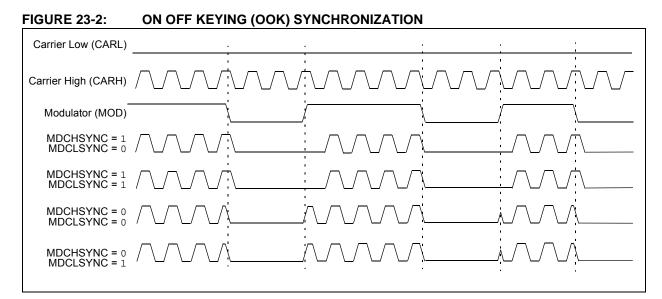

## EXAMPLE 23-1: NO SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 0)

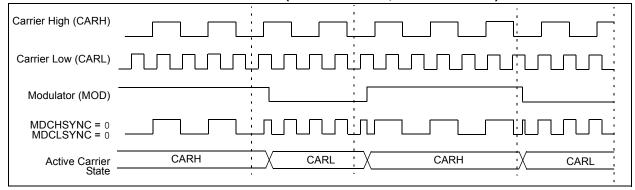

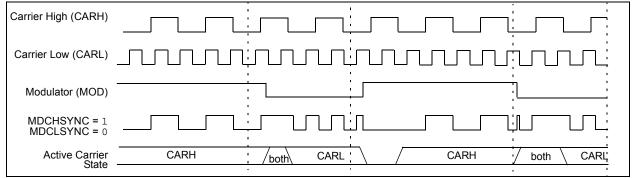

## FIGURE 23-3: CARRIER HIGH SYNCHRONIZATION (MDSHSYNC = 1, MDCLSYNC = 0)

## 25.0 MASTER SYNCHRONOUS SERIAL PORT MODULE

## 25.1 Master SSP (MSSP1) Module Overview

The Master Synchronous Serial Port (MSSP1) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP1 module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

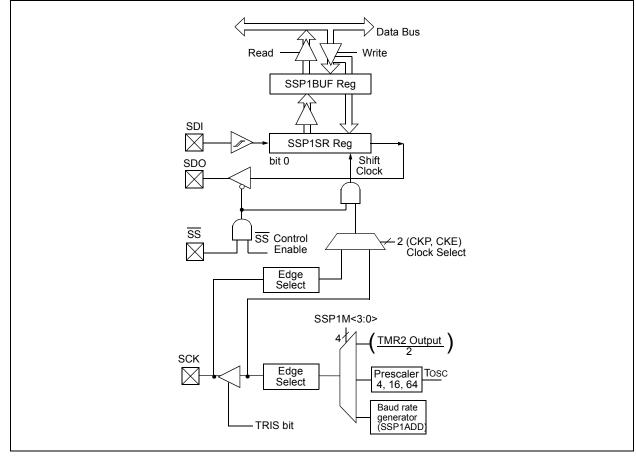

Figure 25-1 is a block diagram of the SPI interface module.

## 25.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP1 interrupt is enabled).

## 25.6.11 EFFECTS OF A RESET

A Reset disables the MSSP1 module and terminates the current transfer.

## 25.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP1 module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSP1STAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCL1IF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- · A Start Condition

- · A Repeated Start Condition

- An Acknowledge Condition

## 25.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

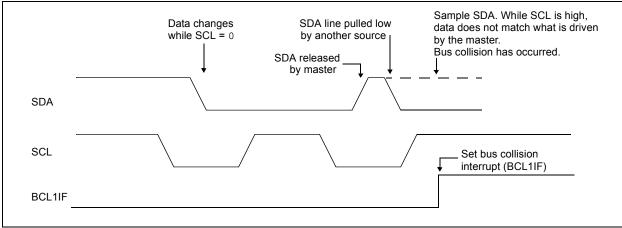

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCL1IF, and reset the I<sup>2</sup>C port to its Idle state (Figure 25-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSP1BUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $l^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSP1CON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSP1IF bit will be set.

A write to the SSP1BUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSP1STAT register, or the bus is Idle and the S and P bits are cleared.

## FIGURE 25-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

## REGISTER 25-2: SSP1CON1: SSP1 CONTROL REGISTER 1

| R/C/HS-0             | )/0 R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0/0                                                                                                                                            | R/W-0/0                                                                                                                                                                        | R/W-0/0                                                                                                                      | R/W-0/0                                                | R/W-0/0                             | R/W-0/0                              |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------|--------------------------------------|

| WCOL                 | SSP10V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SSP1EN                                                                                                                                             | СКР                                                                                                                                                                            |                                                                                                                              | SSP1I                                                  | VI<3:0>                             |                                      |

| bit 7                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                                                                                                                                  | •                                                                                                                                                                              | •                                                                                                                            |                                                        |                                     | bit                                  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                    |                                                                                                                                                                                |                                                                                                                              |                                                        |                                     |                                      |

| Legend:              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                    |                                                                                                                                                                                |                                                                                                                              |                                                        |                                     |                                      |

| R = Readab           | le bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | W = Writable bi                                                                                                                                    | t                                                                                                                                                                              | U = Unimplemer                                                                                                               | nted bit, read as '0                                   | ,                                   |                                      |

| u = Bit is un        | changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | x = Bit is unkno                                                                                                                                   | wn                                                                                                                                                                             | -n/n = Value at F                                                                                                            | OR and BOR/Valu                                        | ue at all other Rese                | ets                                  |

| '1' = Bit is se      | et                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | '0' = Bit is clear                                                                                                                                 | ed                                                                                                                                                                             | HS = Bit is set b                                                                                                            | y hardware                                             | C = User cleared                    | l                                    |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                    |                                                                                                                                                                                |                                                                                                                              | ,                                                      |                                     |                                      |

| bit 7                | Master mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ollision Detect bit                                                                                                                                | intor was attampt                                                                                                                                                              | ed while the I <sup>2</sup> C co                                                                                             | nditions were not a                                    | colid for a transmiss               | aion to bo start                     |

|                      | 0 = No collisio<br><u>Slave mode:</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | n<br>BUF register is writt                                                                                                                         |                                                                                                                                                                                | ansmitting the previo                                                                                                        |                                                        |                                     |                                      |

| bit 6                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ive Overflow Indic                                                                                                                                 | ator hit(1)                                                                                                                                                                    |                                                                                                                              |                                                        |                                     |                                      |

|                      | is lost. Óve<br>data, to av<br>initiated by<br>0 = No overflo<br><u>In I<sup>2</sup>C mode:</u><br>1 = A byte is r                                                                                                                                                                                                                                                                                                                                                                                                      | erflow can only occ<br>oid setting overflow<br>writing to the SSP<br>w<br>eceived while the<br>st be cleared in so                                 | ur in Slave mode.<br>v. In Master mode<br>1BUF register (m<br>SSP1BUF regist                                                                                                   | ster is still holding th<br>In Slave mode, the<br>, the overflow bit is i<br>ust be cleared in so<br>er is still holding the | user must read the<br>not set since each r<br>ftware). | SSP1BUF, even if new reception (and | only transmittin<br>transmission) is |

| bit 5                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nronous Serial Po<br>when enabled, the                                                                                                             |                                                                                                                                                                                | properly configure                                                                                                           | d as input or outpu                                    | ıt                                  |                                      |

|                      | 1 = Enables set<br>0 = Disables s<br>$\frac{\ln l^2 C \mod e}{1}$<br>1 = Enables th                                                                                                                                                                                                                                                                                                                                                                                                                                     | erial port and con                                                                                                                                 | figures these pin<br>onfigures the SDA                                                                                                                                         | and SCL pins as the                                                                                                          |                                                        |                                     |                                      |

| bit 4                | <ul> <li>0 = Disables serial port and configures these pins as I/O port pins</li> <li>CKP: Clock Polarity Select bit <ul> <li>In SPI mode:</li> <li>1 = Idle state for clock is a high level</li> <li>0 = Idle state for clock is a low level</li> <li>In I<sup>2</sup>C Slave mode:</li> <li>SCL release control</li> <li>1 = Enable clock</li> <li>0 = Holds clock low (clock stretch). (Used to ensure data setup time.)</li> <li>In I<sup>2</sup>C Master mode:</li> <li>Unused in this mode</li> </ul> </li> </ul> |                                                                                                                                                    |                                                                                                                                                                                |                                                                                                                              |                                                        |                                     |                                      |

| bit 3-0              | 0000 = SPI Ma;<br>0001 = SPI Ma;<br>0010 = SPI Ma;<br>0100 = SPI Ma;<br>0100 = SPI Sla<br>0101 = SPI Sla<br>$0101 = I^2C Slav$<br>$1000 = I^2C Ma;$<br>1001 = Reserve<br>1010 = SPI Ma;<br>$1011 = I^2C firm$<br>1100 = Reserve<br>1101 = Reserve<br>$1101 = I^2C Slav$                                                                                                                                                                                                                                                 | ve mode, 7-bit ado<br>ve mode, 10-bit ado<br>ster mode, clock =<br>ed<br>ster mode, clock =<br>ware controlled M<br>ed<br>ed<br>ve mode, 7-bit ado | Fosc/4<br>Fosc/16<br>Fosc/64<br>TMR2 output/2<br>SCK pin, <u>SS</u> pin<br>SCK pin, <u>SS</u> pin<br>tress<br>Idress<br>Fosc / (4 * (SSF<br>Fosc/(4 * (SSP<br>aster mode (Slav | control enabled _<br>control disabled, S<br>P1ADD+1)) <sup>(4)</sup><br>1ADD+1))( <sup>5)</sup>                              | ts enabled                                             | I/O pin                             |                                      |

| Note 1:              | In Master mode, the c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                    |                                                                                                                                                                                | -                                                                                                                            | -                                                      | iated by writing to                 | the SSP1BUF                          |

| 2:<br>3:<br>4:<br>5: | register.<br>When enabled, these<br>When enabled, the SI<br>SSP1ADD values of 0<br>SSP1ADD value of '0'                                                                                                                                                                                                                                                                                                                                                                                                                 | pins must be prop<br>DA and SCL pins i<br>), 1 or 2 are not su                                                                                     | perly configured a<br>must be configure<br>Ipported for I <sup>2</sup> C N                                                                                                     | as input or output.<br>ed as inputs.<br>Aode.                                                                                | .,                                                     | ,, <u>.</u>                         |                                      |

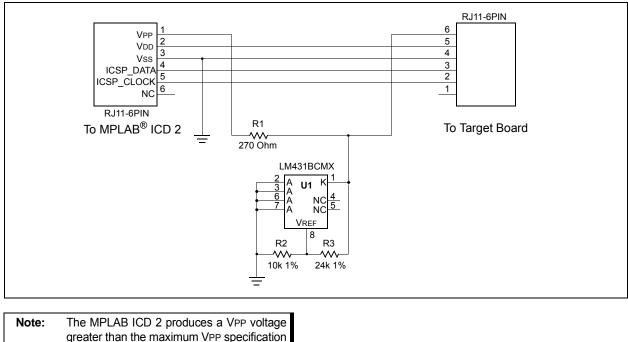

## 28.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "*PIC16F/LF182X/PIC12F/LF1822 Memory Programming Specification*" (DS41403).

## 28.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

Some programmers produce VPP greater than VIHH (9.0V), an external circuit is required to limit the VPP voltage. See Figure 28-1 for example circuit.

FIGURE 28-1: VPP LIMITER EXAMPLE CIRCUIT

© 2010-2015 Microchip Technology Inc.

of the PIC12(L)F1822/16(L)F1823.

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                  |  |  |  |

| Operands:        | None                                                                                                                                                                                                            |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                         |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |  |  |  |

| Words:           | 1                                                                                                                                                                                                               |  |  |  |