#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

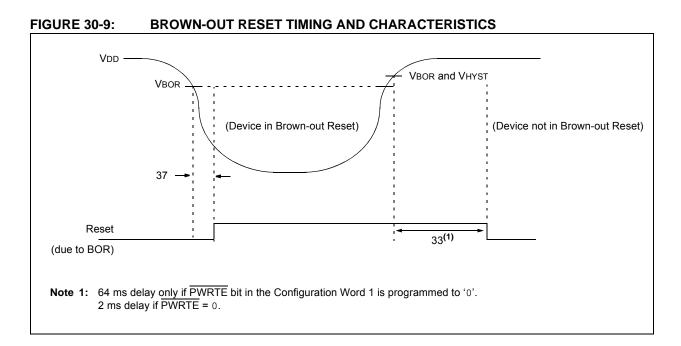

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1823t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

Г

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### **REGISTER 3-1:** STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 29.0 "Instruction Set Summary").

| Note 1: | The C and DC bits operate as Borrow         |

|---------|---------------------------------------------|

|         | and Digit Borrow out bits, respectively, in |

|         | subtraction.                                |

| U-0              | U-0                                 | U-0                  | R-1/q                                                 | R-1/q                          | R/W-0/u          | R/W-0/u           | R/W-0/u          |

|------------------|-------------------------------------|----------------------|-------------------------------------------------------|--------------------------------|------------------|-------------------|------------------|

| _                | _                                   | —                    | TO                                                    | PD                             | Z                | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7            |                                     |                      |                                                       |                                |                  |                   | bit 0            |

|                  |                                     |                      |                                                       |                                |                  |                   |                  |

| Legend:          |                                     |                      |                                                       |                                |                  |                   |                  |

| R = Readable b   | oit                                 | W = Writable I       | bit                                                   | U = Unimpler                   | mented bit, read | as '0'            |                  |

| u = Bit is uncha | Bit is unchanged x = Bit is unknown |                      | -n/n = Value at POR and BOR/Value at all other Resets |                                |                  |                   |                  |

| '1' = Bit is set |                                     | '0' = Bit is cleared |                                                       | q = Value depends on condition |                  |                   |                  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-down bit                                                                                                                                                      |

|         | 1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                            |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit <sup>(1)</sup>                                                                                                                         |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup>                                                                                                                                      |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1. | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                                   |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

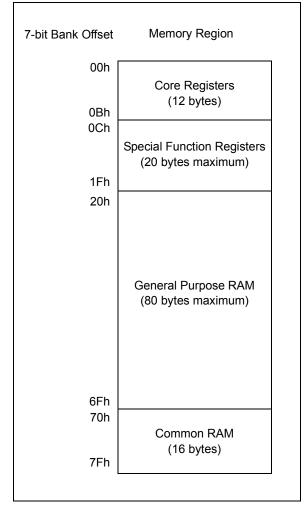

### 3.2.2 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.2.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank.

#### 3.2.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.5.2** "**Linear Data Memory**" for more information.

#### 3.2.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-2: BANKED MEMORY PARTITIONING

#### 3.2.5 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-2.

#### TABLE 3-2: MEMORY MAP TABLES

| Device                   | Banks | Table No. |

|--------------------------|-------|-----------|

|                          | 0-7   | Table 3-3 |

|                          | 8-15  | Table 3-4 |

| PIC12(L)F1822/16(L)F1823 | 16-23 | Table 3-5 |

|                          | 24-31 | Table 3-6 |

|                          | 31    | Table 3-7 |

### 8.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the Section 9.0 "Power-Down Mode (Sleep)" for more details.

### 8.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

### 8.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

#### REGISTER 13-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0

bit 5-0

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 13-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

- IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

- 0 = No change was detected, or the user cleared the detected change.

### 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 Gate Control. It can be used to supply an external source to the Timer1 Gate circuitry.

#### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 Gate circuitry.

#### 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 Gate Control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization"**.

#### 21.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 Gate Control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization"**.

#### 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 Gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |  |  |  |  |

|       | indeterminate operation.                    |  |  |  |  |  |  |  |

#### 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 Gate source to be measured. See Figure 21-6 for timing details.

#### 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 Gate is not enabled (TMR1GE bit is cleared).

#### 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 Gate is not enabled (TMR1GE bit is cleared).

#### 21.7 **Timer1 Interrupt**

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- · PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

The TMR1H:TMR1L register pair and the Note: TMR1IF bit should be cleared before enabling interrupts.

#### 21.8 **Timer1 Operation During Sleep**

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- T1OSCEN bit of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the  $\overline{\text{T1SYNC}}$  bit setting.

#### 21.9 ECCP/CCP Capture/Compare Time Base

The CCP1 module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 24.0 "Capture/Compare/PWM Modules".

### 21.10 ECCP/CCP Special Event Trigger

When any of the CCP's are configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized and Fosc/4 should be selected as the clock source in order to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see Section 16.2.5 "Special Event Trigger".

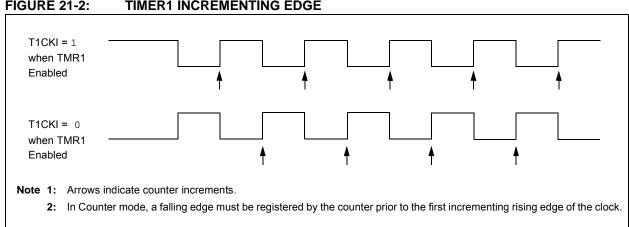

#### **FIGURE 21-2:** TIMER1 INCREMENTING EDGE

| R/W-x/u          | R/W-x/u                                                                                                                                                                                                                 | R/W-x/u             | U-0         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|----------------|------------------|------------------|--------------|--|--|--|

| MDCHODIS         | MDCHPOL                                                                                                                                                                                                                 | MDCHSYNC            | _           |                | MDCH             | 1<3:0>           |              |  |  |  |

| bit 7            |                                                                                                                                                                                                                         |                     |             | ·              |                  |                  | bit          |  |  |  |

|                  |                                                                                                                                                                                                                         |                     |             |                |                  |                  |              |  |  |  |

| Legend:          |                                                                                                                                                                                                                         |                     |             |                |                  |                  |              |  |  |  |

| R = Readable     | bit                                                                                                                                                                                                                     | W = Writable bit    | t           | U = Unimplen   | nented bit, read | l as '0'         |              |  |  |  |

| u = Bit is unch  | anged                                                                                                                                                                                                                   | x = Bit is unknow   | wn          | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                                                         | '0' = Bit is cleare | ed          |                |                  |                  |              |  |  |  |

|                  |                                                                                                                                                                                                                         |                     |             |                |                  |                  |              |  |  |  |

| bit 7            |                                                                                                                                                                                                                         | Modulator High (    |             | •              |                  |                  |              |  |  |  |

|                  | <ul> <li>1 = Output signal driving the peripheral output pin (selected by MDCH&lt;3:0&gt;) is disabled</li> <li>0 = Output signal driving the peripheral output pin (selected by MDCH&lt;3:0&gt;) is enabled</li> </ul> |                     |             |                |                  |                  |              |  |  |  |

|                  |                                                                                                                                                                                                                         | • • •               | •           |                | ted by MDCH<     | 3:0>) is enable  | bd           |  |  |  |

| bit 6            | MDCHPOL: Modulator High Carrier Polarity Select bit                                                                                                                                                                     |                     |             |                |                  |                  |              |  |  |  |

|                  | <ol> <li>Selected high carrier signal is inverted</li> <li>Selected high carrier signal is not inverted</li> </ol>                                                                                                      |                     |             |                |                  |                  |              |  |  |  |

|                  |                                                                                                                                                                                                                         |                     |             |                |                  |                  |              |  |  |  |

| bit 5            | MDCHSYNC: Modulator High Carrier Synchronization Enable bit                                                                                                                                                             |                     |             |                |                  |                  |              |  |  |  |

|                  | 1 = Modulator waits for a falling edge on the high time carrier signal before allowing a switch to the<br>low time carrier                                                                                              |                     |             |                |                  |                  |              |  |  |  |

|                  | 0 = Modulator Output is not synchronized to the high time carrier signal <sup>(1)</sup>                                                                                                                                 |                     |             |                |                  |                  |              |  |  |  |

| bit 4            |                                                                                                                                                                                                                         | nted: Read as '0'   |             | <b>J</b>       |                  |                  |              |  |  |  |

| bit 3-0          | MDCH<3:0> Modulator Data High Carrier Selection bits <sup>(1)</sup>                                                                                                                                                     |                     |             |                |                  |                  |              |  |  |  |

|                  | 1111 = Reserved. No channel connected.                                                                                                                                                                                  |                     |             |                |                  |                  |              |  |  |  |

|                  | •                                                                                                                                                                                                                       |                     |             |                |                  |                  |              |  |  |  |

|                  | •                                                                                                                                                                                                                       |                     |             |                |                  |                  |              |  |  |  |

|                  | •                                                                                                                                                                                                                       |                     |             |                |                  |                  |              |  |  |  |

|                  | 0101 = Reserved. No channel connected.<br>0100 = CCP1 output (PWM Output mode only)                                                                                                                                     |                     |             |                |                  |                  |              |  |  |  |

|                  |                                                                                                                                                                                                                         | erence Clock mod    |             |                |                  |                  |              |  |  |  |

|                  |                                                                                                                                                                                                                         | CIN2 port pin       | iuie signai |                |                  |                  |              |  |  |  |

|                  |                                                                                                                                                                                                                         | CIN1 port pin       |             |                |                  |                  |              |  |  |  |

|                  | 0000 = Vss                                                                                                                                                                                                              |                     |             |                |                  |                  |              |  |  |  |

|                  |                                                                                                                                                                                                                         |                     |             |                |                  |                  |              |  |  |  |

### REGISTER 23-3: MDCARH: MODULATION HIGH CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

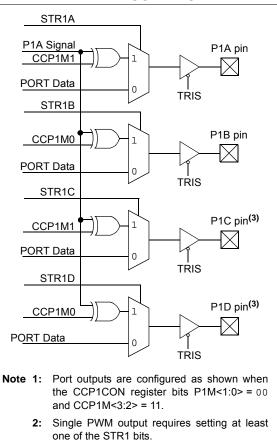

#### 24.4.6 PWM STEERING MODE

In Single Output mode, PWM steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR1 bits of the PSTR1CON register, as shown in Table 24-9.

| Note: | The associated TRIS bits must be set to      |

|-------|----------------------------------------------|

|       | output ('0') to enable the pin output driver |

|       | in order to see the PWM signal on the pin.   |

While the PWM Steering mode is active, the CCP1M<1:0> bits of the CCP1CON register determine the polarity of the output pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 24.4.3 "Enhanced PWM Auto-shutdown mode"**. An autoshutdown event will only affect pins that have PWM outputs enabled.

#### FIGURE 24-18: SIMPLIFIED STEERING BLOCK DIAGRAM

3: PIC16(L)F1823 only.

#### 25.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSP1CON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSP1IF interrupt is set.

Figure 25-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSP1STAT is set; SSP1IF is set if interrupt-on-Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCL line the CKP bit is cleared and SSP1IF interrupt is generated.

- 4. Slave software clears SSP1IF.

- 5. Slave software reads ACKTIM bit of SSP1CON3 register, and  $R/\overline{W}$  and  $D/\overline{A}$  of the SSP1STAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSP1BUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets ACKDT bit of the SSP1CON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSP1IF after the ACK if the R/W bit is set.

- 11. Slave software clears SSP1IF.

- 12. Slave loads value to transmit to the master into SSP1BUF setting the BF bit.

Note: <u>SSP1BUF</u> cannot be loaded until after the <u>ACK</u>.

13. Slave sets CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the 9th SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSP1CON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus, allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

#### REGISTER 25-2: SSP1CON1: SSP1 CONTROL REGISTER 1

| R/C/HS-0             | )/0 R/C/HS-0/0                                                                                                                                                                                                                                                          | R/W-0/0                                                                                                                                            | R/W-0/0                                                                                                                                                              | R/W-0/0                                                                                                                      | R/W-0/0                                                | R/W-0/0                             | R/W-0/0                              |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------|--------------------------------------|

| WCOL                 | SSP10V                                                                                                                                                                                                                                                                  | SSP1EN                                                                                                                                             | СКР                                                                                                                                                                  |                                                                                                                              | SSP1I                                                  | VI<3:0>                             |                                      |

| bit 7                |                                                                                                                                                                                                                                                                         | •                                                                                                                                                  | •                                                                                                                                                                    | •                                                                                                                            |                                                        |                                     | bit                                  |

|                      |                                                                                                                                                                                                                                                                         |                                                                                                                                                    |                                                                                                                                                                      |                                                                                                                              |                                                        |                                     |                                      |

| Legend:              |                                                                                                                                                                                                                                                                         |                                                                                                                                                    |                                                                                                                                                                      |                                                                                                                              |                                                        |                                     |                                      |

| R = Readab           | le bit                                                                                                                                                                                                                                                                  | W = Writable bi                                                                                                                                    | t                                                                                                                                                                    | U = Unimplemer                                                                                                               | nted bit, read as '0                                   | ,                                   |                                      |

| u = Bit is un        | changed                                                                                                                                                                                                                                                                 | x = Bit is unkno                                                                                                                                   | wn                                                                                                                                                                   | -n/n = Value at F                                                                                                            | OR and BOR/Valu                                        | ue at all other Rese                | ets                                  |

| '1' = Bit is se      | et                                                                                                                                                                                                                                                                      | '0' = Bit is clear                                                                                                                                 | ed                                                                                                                                                                   | HS = Bit is set b                                                                                                            | y hardware                                             | C = User cleared                    | l                                    |

|                      |                                                                                                                                                                                                                                                                         |                                                                                                                                                    |                                                                                                                                                                      |                                                                                                                              | ,                                                      |                                     |                                      |

| bit 7                | Master mode:                                                                                                                                                                                                                                                            | ollision Detect bit                                                                                                                                | intor was attampt                                                                                                                                                    | ed while the I <sup>2</sup> C co                                                                                             | nditions were not a                                    | colid for a transmiss               | aion to bo start                     |

|                      | 0 = No collisio<br><u>Slave mode:</u>                                                                                                                                                                                                                                   | n<br>BUF register is writt                                                                                                                         |                                                                                                                                                                      | ansmitting the previo                                                                                                        |                                                        |                                     |                                      |

| bit 6                |                                                                                                                                                                                                                                                                         | ive Overflow Indic                                                                                                                                 | ator hit(1)                                                                                                                                                          |                                                                                                                              |                                                        |                                     |                                      |

|                      | is lost. Óve<br>data, to av<br>initiated by<br>0 = No overflo<br><u>In I<sup>2</sup>C mode:</u><br>1 = A byte is r                                                                                                                                                      | erflow can only occ<br>oid setting overflow<br>writing to the SSP<br>w<br>eceived while the<br>st be cleared in so                                 | ur in Slave mode.<br>v. In Master mode<br>1BUF register (m<br>SSP1BUF regist                                                                                         | ster is still holding th<br>In Slave mode, the<br>, the overflow bit is i<br>ust be cleared in so<br>er is still holding the | user must read the<br>not set since each r<br>ftware). | SSP1BUF, even if new reception (and | only transmittin<br>transmission) is |

| bit 5                |                                                                                                                                                                                                                                                                         | nronous Serial Po<br>when enabled, the                                                                                                             |                                                                                                                                                                      | properly configure                                                                                                           | d as input or outpu                                    | ıt                                  |                                      |

|                      | 1 = Enables set<br>0 = Disables s<br>$\frac{\ln l^2 C \mod e}{1}$<br>1 = Enables th                                                                                                                                                                                     | erial port and con                                                                                                                                 | figures these pin<br>onfigures the SDA                                                                                                                               | and SCL pins as the                                                                                                          |                                                        |                                     |                                      |

| bit 4                | 0 = Idle state fo<br>In I <sup>2</sup> C Slave mo<br>SCL release co<br>1 = Enable cloc                                                                                                                                                                                  | r clock is a high le<br>r clock is a low lev<br>d <u>e:</u><br>ntrol<br>k<br>low (clock stretch<br><u>ode:</u>                                     |                                                                                                                                                                      |                                                                                                                              |                                                        |                                     |                                      |

| bit 3-0              | 0000 = SPI Ma;<br>0001 = SPI Ma;<br>0010 = SPI Ma;<br>0100 = SPI Ma;<br>0100 = SPI Sla<br>0101 = SPI Sla<br>$0101 = I^2C Slav$<br>$1000 = I^2C Ma;$<br>1001 = Reserve<br>1010 = SPI Ma;<br>$1011 = I^2C firm$<br>1100 = Reserve<br>1101 = Reserve<br>$1101 = I^2C Slav$ | ve mode, 7-bit ado<br>ve mode, 10-bit ado<br>ster mode, clock =<br>ed<br>ster mode, clock =<br>ware controlled M<br>ed<br>ed<br>ve mode, 7-bit ado | Fosc/4<br>Fosc/16<br>Fosc/64<br>TMR2 output/2<br>SCK pin, <u>SS</u> pin<br>SCK pin, <u>SS</u> pin<br>dress<br>Fosc / (4 * (SSF<br>Fosc/(4 * (SSP<br>aster mode (Slav | control enabled<br>control disabled, S<br>P1ADD+1)) <sup>(4)</sup><br>1ADD+1))( <sup>5)</sup>                                | ts enabled                                             | I/O pin                             |                                      |

| Note 1:              | In Master mode, the c                                                                                                                                                                                                                                                   |                                                                                                                                                    |                                                                                                                                                                      | -                                                                                                                            | -                                                      | iated by writing to                 | the SSP1BUF                          |

| 2:<br>3:<br>4:<br>5: | register.<br>When enabled, these<br>When enabled, the SI<br>SSP1ADD values of 0<br>SSP1ADD value of '0'                                                                                                                                                                 | pins must be prop<br>DA and SCL pins i<br>), 1 or 2 are not su                                                                                     | perly configured a<br>must be configure<br>Ipported for I <sup>2</sup> C N                                                                                           | as input or output.<br>ed as inputs.<br>Aode.                                                                                | .,                                                     | ,, <u>.</u>                         |                                      |

### 26.3.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 26-9 for the timing of the Break character sequence.

#### 26.3.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### Write to TXREG Dummy Write **BRG** Output (Shift Clock) TX (pin) Start bit bit 0 bit 1 Stop bit Break TXIF bit (Transmit Interrupt Flag) TRMT bit (Transmit Shift Empty Flag) SENDB Sampled Here Auto Cleared SENDB (send Break control bit)

#### 26.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the Received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 26.3.3** "**Auto-Wake-up on Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

### FIGURE 26-9: SEND BREAK CHARACTER SEQUENCE

#### REGISTER 27-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1

| U-0              | U-0                   | U-0               | U-0                | R/W-0/0        | R/W-0/0 <sup>(1)</sup> | R/W-0/0          | R/W-0/0   |

|------------------|-----------------------|-------------------|--------------------|----------------|------------------------|------------------|-----------|

| _                | _                     | _                 | _                  |                | CPSCH                  | 1<3:0>           |           |

| bit 7            |                       |                   |                    |                |                        |                  | bit 0     |

|                  |                       |                   |                    |                |                        |                  |           |

| Legend:          |                       |                   |                    |                |                        |                  |           |

| R = Readable b   | bit                   | W = Writable b    | bit                | U = Unimplem   | nented bit, read a     | s '0'            |           |

| u = Bit is uncha | inged                 | x = Bit is unkn   | own                | -n/n = Value a | t POR and BOR/         | Value at all oth | er Resets |

| '1' = Bit is set |                       | '0' = Bit is clea | red                |                |                        |                  |           |

|                  |                       |                   |                    |                |                        |                  |           |

| bit 7-4          | Unimplement           | ted: Read as '0'  |                    |                |                        |                  |           |

| bit 3-0          | CPSCH<3:0>            | : Capacitive Ser  | nsing Channel      | Select bits    |                        |                  |           |

|                  | <u>If CPSON = 0</u> : |                   | -                  |                |                        |                  |           |

|                  | These bit             | s are ignored. N  | lo channel is s    | elected.       |                        |                  |           |

|                  | <u>If CPSON = 1</u> : |                   |                    |                |                        |                  |           |

|                  |                       | channel 0, (CP    | ,                  |                |                        |                  |           |

|                  |                       | channel 1, (CP    |                    |                |                        |                  |           |

|                  |                       | channel 2, (CP    |                    |                |                        |                  |           |

|                  |                       | channel 3, (CP    |                    |                |                        |                  |           |

|                  |                       | channel 4, (CP    |                    |                |                        |                  |           |

|                  | 0101 =                | channel 5, (CP    | S5) <sup>(1)</sup> |                |                        |                  |           |

|                  | 0110 =                | channel 6, (CP    | S6) <sup>(1)</sup> |                |                        |                  |           |

|                  |                       | channel 7, (CP    | ,                  |                |                        |                  |           |

|                  | 1000 =                | Reserved. Do r    | not use.           |                |                        |                  |           |

|                  | •                     |                   |                    |                |                        |                  |           |

|                  | •                     |                   |                    |                |                        |                  |           |

|                  | •                     | _                 |                    |                |                        |                  |           |

|                  | 1111 =                | Reserved. Do r    | not use.           |                |                        |                  |           |

Note 1: These channels are only implemented on the PIC16(L)F1823.

| TABLE 27-3:         SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSING |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

| Name                  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3                 | Bit 2                 | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|---------|---------|---------|---------|-----------------------|-----------------------|--------|--------|---------------------|

| ANSELA                | —       | —       | _       | ANSA4   | —                     | ANSA2                 | ANSA1  | ANSA0  | 118                 |

| ANSELC <sup>(1)</sup> | _       | —       | _       | _       | ANSC3                 | ANSC2                 | ANSC1  | ANSC0  | 122                 |

| CPSCON0               | CPSON   | CPSRM   | -       | -       | CPSRNG1               | CPSRNG0               | CPSOUT | TOXCS  | 302                 |

| CPSCON1               | _       | —       | _       | —       | CPSCH3 <sup>(1)</sup> | CPSCH2 <sup>(1)</sup> | CPSCH1 | CPSCH0 | 303                 |

| INTCON                | GIE     | PEIE    | TMR0IE  | INTE    | IOCIE                 | TMR0IF                | INTF   | IOCIF  | 86                  |

| OPTION_REG            | WPUEN   | INTEDG  | TMR0CS  | TMR0SE  | PSA                   | PS2                   | PS1    | PS0    | 164                 |

| T1CON                 | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN               | T1SYNC                | —      | TMR10N | 173                 |

| TRISA                 | _       | —       | TRISA5  | TRISA4  | TRISA3                | TRISA2                | TRISA1 | TRISA0 | 117                 |

| TRISC <sup>(1)</sup>  |         | _       | TRISC5  | TRISC4  | TRISC3                | TRISC2                | TRISC1 | TRISC0 | 121                 |

Legend: — = Unimplemented locations, read as '0'. Shaded cells are not used by the CPS module.

Note 1: PIC16(L)F1823 only.

#### TABLE 30-6: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym.      |                                   | Characteristi                                            | c              | Min.                                      | Тур†   | Max.   | Units | Conditions                         |

|--------------|-----------|-----------------------------------|----------------------------------------------------------|----------------|-------------------------------------------|--------|--------|-------|------------------------------------|

| 40*          | Тт0Н      | T0CKI High F                      | Pulse Width                                              | No Prescaler   | 0.5 Tcy + 20                              | _      | _      | ns    |                                    |

|              |           |                                   |                                                          | With Prescaler | 10                                        | —      | _      | ns    |                                    |

| 41*          | TT0L      | T0CKI Low P                       | ulse Width                                               | No Prescaler   | 0.5 Tcy + 20                              | —      | _      | ns    |                                    |

|              |           |                                   |                                                          | With Prescaler | 10                                        | —      | _      | ns    |                                    |

| 42*          | Тт0Р      | T0CKI Period                      | l                                                        |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | _      | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Тт1Н      | T1H T1CKI High<br>Time            | Synchronous, No Prescaler                                |                | 0.5 Tcy + 20                              | —      | _      | ns    |                                    |

|              |           |                                   | Synchronous,<br>with Prescaler                           |                | 15                                        | —      | —      | ns    |                                    |

|              |           |                                   | Asynchronous                                             |                | 30                                        | _      |        | ns    |                                    |

| 46*          | T⊤1L      | T1CKI Low                         | Synchronous, No Prescaler<br>Synchronous, with Prescaler |                | 0.5 Tcy + 20                              | —      |        | ns    |                                    |

|              |           | Time                              |                                                          |                | 15                                        | —      | _      | ns    |                                    |

|              |           |                                   | Asynchronous                                             |                | 30                                        | —      |        | ns    |                                    |

| 47*          | TT1P      | T1CKI Input Synchronous<br>Period |                                                          |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —      | _      | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                   | Asynchronous                                             |                | 60                                        | —      | _      | ns    |                                    |

| 48           | F⊤1       |                                   | ator Input Freque abled by setting                       | , 0            | 32.4                                      | 32.768 | 33.1   | kHz   |                                    |

| 49*          | TCKEZTMR1 | Delay from E<br>Increment         | elay from External Clock Edge to Timer                   |                |                                           | —      | 7 Tosc | —     | Timers in Sync<br>mode             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

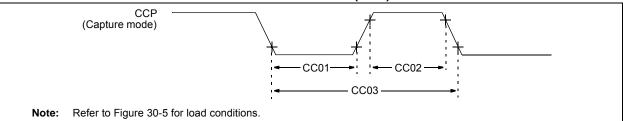

#### FIGURE 30-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

#### TABLE 30-7: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                     |                |                       |      |       |            |                                 |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|------|---------------------|----------------|-----------------------|------|-------|------------|---------------------------------|--|--|--|

| Param<br>No.                                                                                                         | Sym. | Characteri          | Min.           | Тур†                  | Max. | Units | Conditions |                                 |  |  |  |

| CC01*                                                                                                                | TccL | CCP Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —    | —     | ns         |                                 |  |  |  |

|                                                                                                                      |      |                     | With Prescaler | 20                    | _    | _     | ns         |                                 |  |  |  |

| CC02*                                                                                                                | TccH | CCP Input High Time | No Prescaler   | 0.5Tcy + 20           | _    | _     | ns         |                                 |  |  |  |

|                                                                                                                      |      |                     | With Prescaler | 20                    |      |       | ns         |                                 |  |  |  |

| CC03*                                                                                                                | TccP | CCP Input Period    |                | <u>3Tcy + 40</u><br>N | —    | —     | ns         | N = prescale value (1, 4 or 16) |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

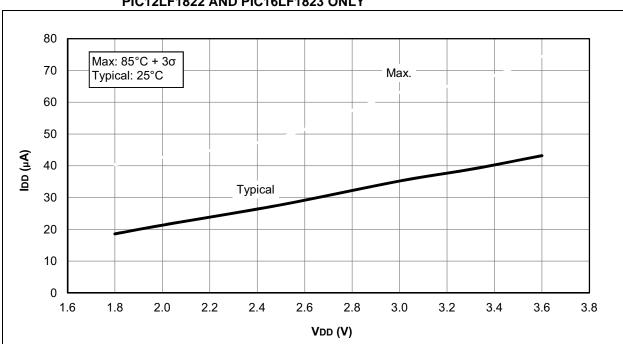

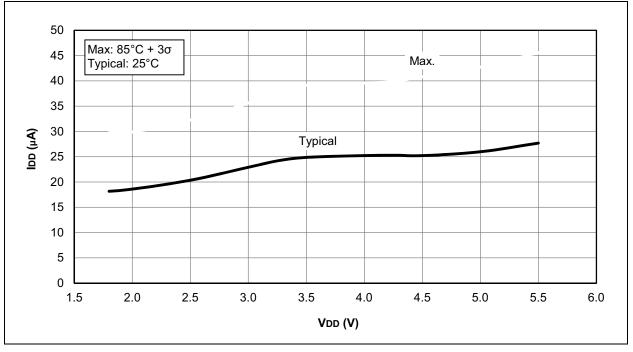

FIGURE 31-9: IDD, EC OSCILLATOR, LOW-POWER MODE (Fosc = 500 kHz), PIC12LF1822 AND PIC16LF1823 ONLY

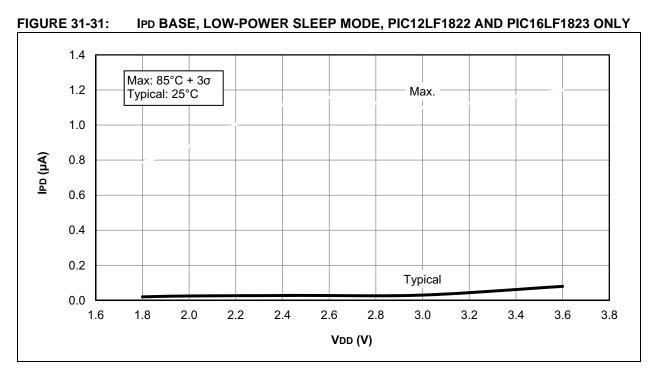

FIGURE 31-32: IPD BASE, LOW-POWER SLEEP MODE, PIC12F1822 AND PIC16F1823 ONLY

## 33.0 PACKAGING INFORMATION

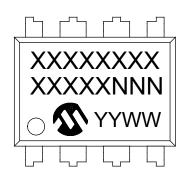

## 33.1 Package Marking Information

8-Lead PDIP (300 mil)

8-Lead SOIC (3.90 mm)

| Le | egend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>*                                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |  |  |  |  |

|----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| No | b      | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

© 2010-2015 Microchip Technology Inc.

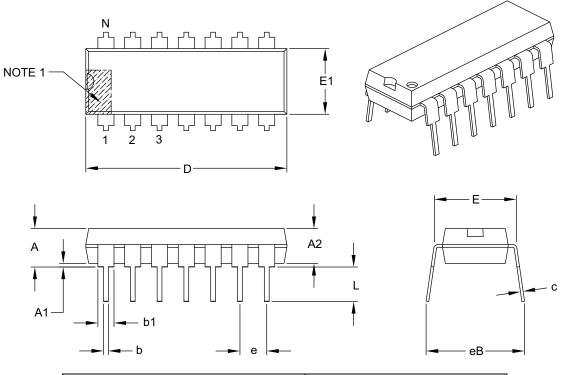

### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    | INCHES |          |      |  |

|----------------------------|----------|--------|----------|------|--|

| Dimension                  | n Limits | MIN    | NOM      | MAX  |  |

| Number of Pins             | Ν        |        | 14       |      |  |

| Pitch                      | е        |        | .100 BSC |      |  |

| Top to Seating Plane       | Α        | -      | -        | .210 |  |

| Molded Package Thickness   | A2       | .115   | .130     | .195 |  |

| Base to Seating Plane      | A1       | .015   | -        | —    |  |

| Shoulder to Shoulder Width | Е        | .290   | .310     | .325 |  |

| Molded Package Width       | E1       | .240   | .250     | .280 |  |

| Overall Length             | D        | .735   | .750     | .775 |  |

| Tip to Seating Plane       | L        | .115   | .130     | .150 |  |

| Lead Thickness             | С        | .008   | .010     | .015 |  |

| Upper Lead Width           | b1       | .045   | .060     | .070 |  |

| Lower Lead Width           | b        | .014   | .018     | .022 |  |

| Overall Row Spacing §      | eB       | -      | -        | .430 |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.