Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

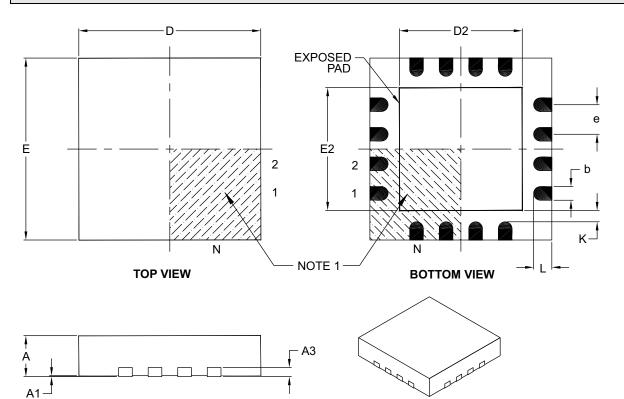

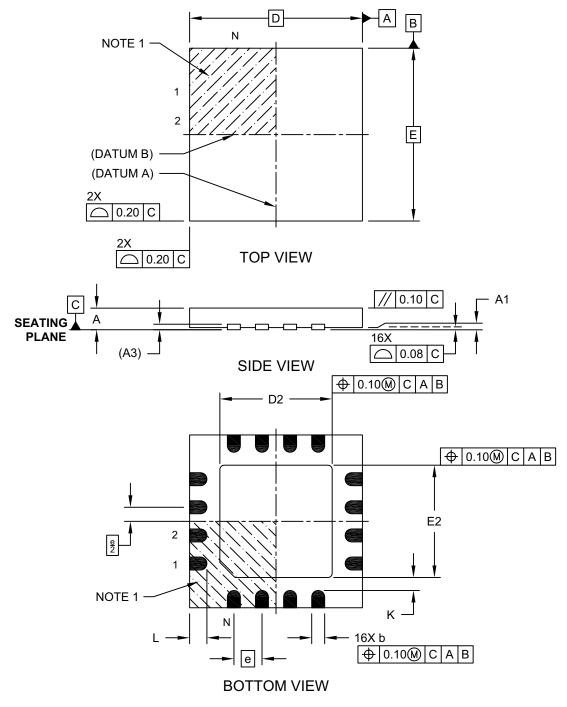

| Mounting Type              | Surface Mount                                                              |

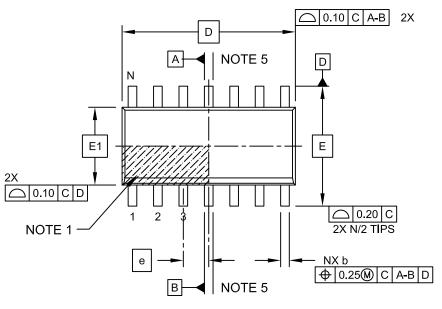

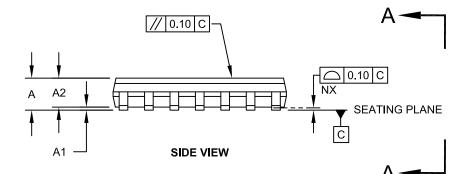

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1823t-i-st |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

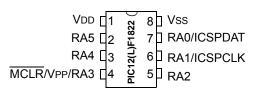

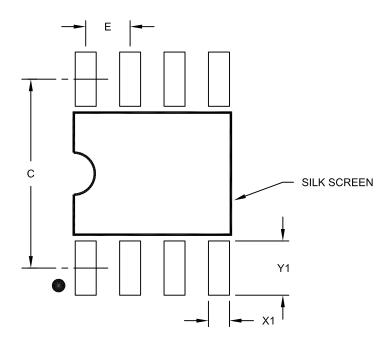

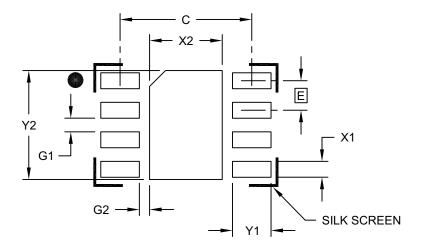

#### FIGURE 1: 8-PIN DIAGRAM FOR PIC12(L)F1822

PDIP, SOIC, DFN, UDFN

#### TABLE 2:8-PIN ALLOCATION TABLE (PIC12(L)F1822)

|     |                          |     |           |           | -          | •        | - ()                        | - /                                               |                                        |                                         |             |           |         |                        |

|-----|--------------------------|-----|-----------|-----------|------------|----------|-----------------------------|---------------------------------------------------|----------------------------------------|-----------------------------------------|-------------|-----------|---------|------------------------|

| 0/1 | 8-Pin PDIP/SOIC/DFN/UDFN | A/D | Reference | Cap Sense | Comparator | SR Latch | Timers                      | ECCP                                              | EUSART                                 | dSSM                                    | Interrupt   | Modulator | Pull-up | Basic                  |

| RA0 | 7                        | AN0 | DACOUT    | CPS0      | C1IN+      |          |                             | P1B <sup>(1)</sup>                                | TX <sup>(1)</sup><br>CK <sup>(1)</sup> | SDO <sup>(1)</sup><br>SS <sup>(1)</sup> | IOC         | MDOUT     | Y       | ICSPDAT<br>ICDDAT      |

| RA1 | 6                        | AN1 | VREF+     | CPS1      | C1IN0-     | SRI      | _                           | _                                                 | RX <sup>(1)</sup><br>DT <sup>(1)</sup> | SCL<br>SCK                              | IOC         | MDMIN     | Y       | ICSPCLK<br>ICPCLK      |

| RA2 | 5                        | AN2 | —         | CPS2      | C1OUT      | SRQ      | TOCKI                       | CCP1 <sup>(1)</sup><br>P1A <sup>(1)</sup><br>FLT0 | —                                      | SDA<br>SDI                              | INT/<br>IOC | MDCIN1    | Y       | _                      |

| RA3 | 4                        | _   | —         | _         | _          | —        | T1G <sup>(1)</sup>          | _                                                 | —                                      | SS <sup>(1)</sup>                       | IOC         | —         | Y       | MCLR<br>Vpp            |

| RA4 | 3                        | AN3 | —         | CPS3      | C1IN1-     | —        | T1G <sup>(1)</sup><br>T1OSO | P1B <sup>(1)</sup>                                | TX <sup>(1)</sup><br>CK <sup>(1)</sup> | SDO <sup>(1)</sup>                      | IOC         | MDCIN2    | Y       | OSC2<br>CLKOUT<br>CLKR |

| RA5 | 2                        |     | —         |           |            | SRNQ     | T1CKI<br>T1OSI              | CCP1 <sup>(1)</sup><br>P1A <sup>(1)</sup>         | RX <sup>(1)</sup><br>DT <sup>(1)</sup> |                                         | IOC         | —         | Y       | OSC1<br>CLKIN          |

| Vdd | 1                        | —   | _         | —         | —          | —        | —                           | _                                                 | _                                      | —                                       | —           | —         | _       | Vdd                    |

| Vss | 8                        |     | —         |           | _          |          | _                           | _                                                 | —                                      | _                                       | _           | —         | _       | Vss                    |

Note 1: Pin function is selectable via the APFCON register.

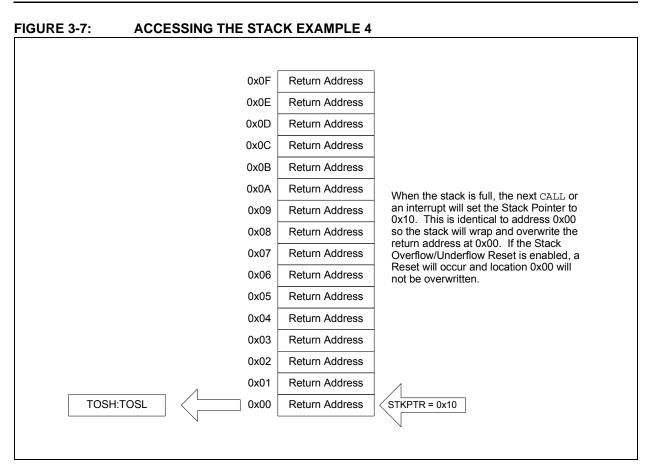

## 3.4.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Word 2 is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

#### 3.5 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- · Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

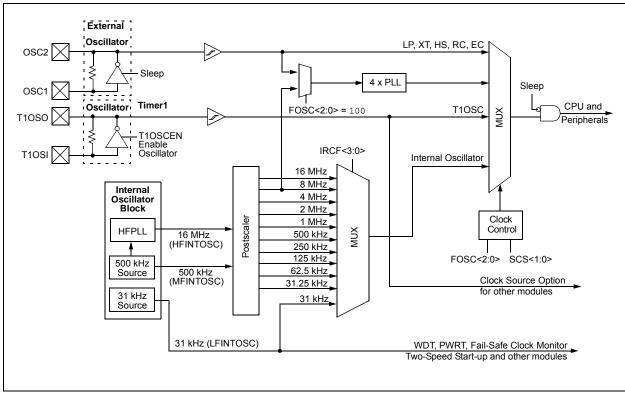

#### FIGURE 5-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

| R/W-0/0                                                                              | R/W-0/0                                                                   | R/W-1/1            | R/W-1/1         | R/W-0/0              | R/W-0/0          | R/W-0/0         | R/W-0/0      |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|-----------------|----------------------|------------------|-----------------|--------------|--|

| CLKREN                                                                               | CLKROE                                                                    | CLKRSLR            | CLKRI           | DC<1:0>              | (                | CLKRDIV<2:0>    | >            |  |

| bit 7                                                                                |                                                                           |                    |                 |                      |                  |                 | bit 0        |  |

|                                                                                      |                                                                           |                    |                 |                      |                  |                 |              |  |

| Legend:                                                                              |                                                                           |                    |                 |                      |                  |                 |              |  |

| R = Readable                                                                         | e bit                                                                     | W = Writable       | bit             | •                    | nented bit, read |                 |              |  |

| u = Bit is uncl                                                                      | nanged                                                                    | x = Bit is unkr    | nown            | -n/n = Value a       | at POR and BC    | OR/Value at all | other Resets |  |

| '1' = Bit is set                                                                     |                                                                           | '0' = Bit is clea  | ared            |                      |                  |                 |              |  |

| bit 7                                                                                | CI KREN: Re                                                               | eference Clock     | Module Enabl    | e bit                |                  |                 |              |  |

|                                                                                      |                                                                           | ce clock module    |                 | o bit                |                  |                 |              |  |

|                                                                                      | 0 = Reference                                                             | ce clock module    | e is disabled   |                      |                  |                 |              |  |

| bit 6                                                                                | CLKROE: Re                                                                | eference Clock     | Output Enable   | e bit <sup>(3)</sup> |                  |                 |              |  |

|                                                                                      |                                                                           | ce clock output    |                 | •                    |                  |                 |              |  |

|                                                                                      | 0 = Reference                                                             | ce clock output    | disabled on C   | LKR pin              |                  |                 |              |  |

| bit 5                                                                                | CLKRSLR: F                                                                | Reference Clock    | < Slew Rate C   | ontrol limiting e    | nable bit        |                 |              |  |

|                                                                                      |                                                                           | e limiting is ena  |                 |                      |                  |                 |              |  |

| bit 4-3                                                                              |                                                                           | e limiting is disa |                 | ala hita             |                  |                 |              |  |

| DIL 4-3                                                                              |                                                                           | 0>: Reference      |                 | cie dits             |                  |                 |              |  |

|                                                                                      |                                                                           | outputs duty cyc   |                 |                      |                  |                 |              |  |

|                                                                                      |                                                                           | outputs duty cyc   |                 |                      |                  |                 |              |  |

|                                                                                      | 00 = Clock o                                                              | outputs duty cyc   | le of 0%        |                      |                  |                 |              |  |

| bit 2-0                                                                              | CLKRDIV<2:                                                                | :0> Reference (    | Clock Divider I | bits                 |                  |                 |              |  |

|                                                                                      |                                                                           | clock value divi   | •               |                      |                  |                 |              |  |

|                                                                                      | 110 = Base clock value divided by 64 101 = Base clock value divided by 32 |                    |                 |                      |                  |                 |              |  |

|                                                                                      | 100 = Base clock value divided by 32                                      |                    |                 |                      |                  |                 |              |  |

|                                                                                      |                                                                           | clock value divi   | •               |                      |                  |                 |              |  |

| 010 = Base clock value divided by 4                                                  |                                                                           |                    |                 |                      |                  |                 |              |  |

| 001 = Base clock value divided by $2^{(1)}$<br>000 = Base clock value <sup>(2)</sup> |                                                                           |                    |                 |                      |                  |                 |              |  |

|                                                                                      | 000 = Base                                                                | CIOCK VAIUE        |                 |                      |                  |                 |              |  |

| Note 1: In                                                                           | this mode, the                                                            | 25% and 75% (      | duty cycle acc  | uracy will be de     | ependent on the  | e source clock  | duty cycle.  |  |

#### REGISTER 6-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

- 2: In this mode, the duty cycle will always be equal to the source clock duty cycle, unless a duty cycle of 0% is selected.

- **3:** To route CLKR to pin, CLKOUTEN of Configuration Word 1 = 1 is required. CLKOUTEN of Configuration Word 1 = 0 will result in Fosc/4. See **Section 6.3 "Conflicts with the CLKR pin"** for details.

### 7.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 7.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word 1.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

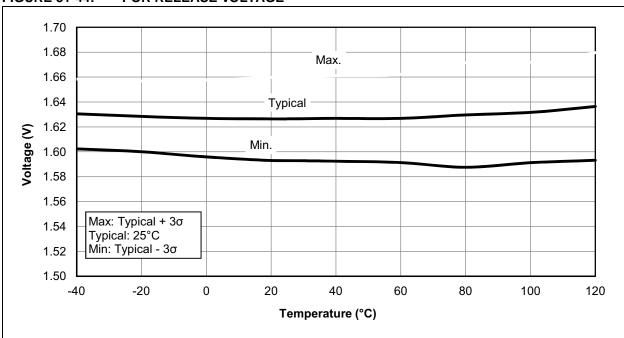

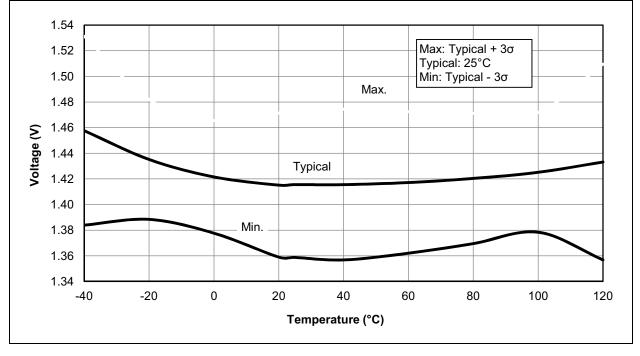

## 7.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word 1. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 7-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Word 2.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 7-3 for more information.

| BOREN<br>Config bits | SBOREN | Device Mode | BOR Mode | Device<br>Operation upon<br>release of POR | Device<br>Operation upon<br>wake- up from<br>Sleep |

|----------------------|--------|-------------|----------|--------------------------------------------|----------------------------------------------------|

| BOR_ON (11)          | х      | Х           | Active   | Waits for B                                | OR ready <sup>(1)</sup>                            |

| BOR_NSLEEP (10)      | х      | Awake       | Active   | Waite for I                                |                                                    |

| BOR_NSLEEP (10)      | х      | Sleep       | Disabled |                                            | BOR ready                                          |

| BOR_SBOREN (01)      | 1      | х           | Active   | Begins im                                  | nmediately                                         |

| BOR_SBOREN (01)      | 0      | х           | Disabled | Begins im                                  | nmediately                                         |

| BOR_OFF (00)         | х      | х           | Disabled | Begins im                                  | nmediately                                         |

#### TABLE 7-1:BOR OPERATING MODES

**Note 1:** In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 7.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word 1 are set to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 7.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word 1 are set to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

| U-0              | U-0   | U-0               | U-0  | R/W-1/1        | R/W-1/1          | R/W-1/1        | R/W-1/1      |

|------------------|-------|-------------------|------|----------------|------------------|----------------|--------------|

| —                | —     | —                 | _    | ANSC3          | ANSC2            | ANSC1          | ANSC0        |

| bit 7            |       |                   |      |                |                  |                | bit 0        |

|                  |       |                   |      |                |                  |                |              |

| Legend:          |       |                   |      |                |                  |                |              |

| R = Readable I   | bit   | W = Writable      | bit  | U = Unimplen   | nented bit, read | l as '0'       |              |

| u = Bit is uncha | anged | x = Bit is unkr   | nown | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared |                |                  |                |              |

#### REGISTER 12-10: ANSELC: PORTC ANALOG SELECT REGISTER

bit 7-4 Unimplemented: Read as '0'

bit 3-0

ANSC<3:0>: Analog Select between Analog or Digital Function on pins RC<3:0>, respectively

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 12-11: WPUC: WEAK PULL-UP PORTC REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 WPUC<5:0>: Weak Pull-up Register bits<sup>(1, 2)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

## TABLE 12-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC<sup>(1)</sup>

| Name       | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|-------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| ANSELC     | -     | -      | —      | -      | ANSC3  | ANSC2  | ANSC1   | ANSC0  | 122                 |

| LATC       | _     | _      | LATC5  | LATC4  | LATC3  | LATC2  | LATC1   | LATC0  | 121                 |

| OPTION_REG | WPUEN | INTEDG | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |        | 164                 |

| PORTC      | _     | _      | RC5    | RC4    | RC3    | RC2    | RC1     | RC0    | 121                 |

| TRISC      | _     | _      | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1  | TRISC0 | 121                 |

| WPUC       | _     | _      | WPUC5  | WPUC4  | WPUC3  | WPUC2  | WPUC1   | WPUC0  | 122                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

Note 1: PIC16(L)F1823 only.

| SRSPE SRSCKE SRSC2E <sup>(1)</sup> SRSC1E SRRPE SRRCKE SRRC2E <sup>(1)</sup> SRRC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |              |                       |                |                    |                 |                       |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|-----------------------|----------------|--------------------|-----------------|-----------------------|-------------|

| bit 7       Image: Comparator output is high         Image: Comparator output has no effect on the reset input of the SR latch         bit 3       SRSPE: SR Latch 2 Reset Clock Enable bit         1 = SR latch is set when the SRI pin is high       0 = SRI pin has no effect on the set input of the SR latch         bit 5       SRSCXE: SR Latch 2 Stenable bit         1 = SR latch is set when the SRI pin is high       0 = SRI pin has no effect on the set input of the SR latch         bit 5       SRSCXE: SR Latch Set Clock Enable bit         1 = SR latch is set when the SRI pin is high       0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSCZE: SR Latch C2 Set Enable bit         1 = SR latch is set when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSCIE: SR Latch C1 Set Enable bit       1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch       1 = SR latch is reset when the SRI pin is high         0 = SRCLK has no effect on the reset input of the SR latch       1 = SR latch is reset when the C2 Comparator output is high         0 = SRC in pin has no effect on the reset input of the SR latch       1 = SR latch is reset when the SRI pin is high         0 = SRCLK has no effect on the reset input of the SR latch       1 = SR latch is reset when the C2 Comparator output is high                                                                                                                                                                      | R/W-0/0          | R/W-0/0      | R/W-0/0               | R/W-0/0        | R/W-0/0            | R/W-0/0         | R/W-0/0               | R/W-0/0     |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reservers         '1' = Bit is set       '0' = Bit is cleared         bit 7       SRSPE: SR Latch Peripheral Set Enable bit         1 = SR latch is set when the SRI pin is high       0 = SRI pin has no effect on the set input of the SR latch         bit 6       SRSCKE: SR Latch Set Clock Enable bit         1 = Set input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSCZE: SR Latch C2 Set Enable bit         1 = SR latch is set when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSC1E: SR Latch C1 Set Enable bit       1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch       bit 3         SRRPE: SR Latch Peripheral Reset Enable bit       1 = SR latch is reset when the SRI pin is high         0 = SRI pin has no effect on the reset input of the SR latch       bit 2         SRRPE: SR Latch C2 Reset Clock Enable bit       1 = SR latch is reset when the SRI pin is high         0 = SRI pin has no effect on the reset input of the SR latch       bit 3         SRRPE: SR Latch C2 Resest E                                                                                                                                                                                                                            | SRSPE            | SRSCKE       | SRSC2E <sup>(1)</sup> | SRSC1E         | SRRPE              | SRRCKE          | SRRC2E <sup>(1)</sup> | SRRC1E      |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reset         '1' = Bit is set       '0' = Bit is cleared         bit 7       SRSPE: SR Latch Peripheral Set Enable bit         1 = SR latch is set when the SRI pin is high       0 = SRI pin has no effect on the set input of the SR latch         bit 6       SRSCKE: SR Latch Set Clock Enable bit         1 = Set input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSCZE: SR Latch C2 Set Enable bit'         1 = SR latch is set when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSC1E: SR Latch C1 Set Enable bit       1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch       1 = SR latch is reset when the SRI pin is high         0 = C1 Comparator output has no effect on the set input of the SR latch       1 = SR latch is reset when the SRI pin is high         0 = SRI pin has no effect on the reset input of the SR latch       1 = SR latch is reset when the SRI pin is high         0 = C1 Comparator output has no effect on the reset input of the SR latch       1 = SR latch is reset when the C2 Comparator output is high         0 = SRC KE: SR Latch C2 Reset Ena                                                                                                                                                               | bit 7            |              |                       |                |                    |                 |                       | bit 0       |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reset         '1' = Bit is set       '0' = Bit is cleared       -n/n = Value at POR and BOR/Value at all other Reset         bit 7       SRSPE: SR Latch Peripheral Set Enable bit       1 = SR lip in has no effect on the set input of the SR latch         bit 6       SRSCKE: SR Latch Set Clock Enable bit       1 = Set input of SR latch is pulsed with SRCLK         0 = SRCLK has no effect on the set input of the SR latch       5 SRSC2E: SR Latch C2 Set Enable bit <sup>(1)</sup> 1 = SR latch is set when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the set input of the SR latch         bit 3       SRRPF: SR Latch Peripheral Reset Enable bit       1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch       5 SRCEK         bit 3       SRRPF: SR Latch Peripheral Reset Enable bit       1 = SR latch is reset when the SRI pin is high         0 = C1 Comparator output has no effect on the reset input of the SR latch       5 SRCEK         bit 2       SRRCKE: SR Latch Reset Clock Enable bit       1 = Reset input of SR latch is pulsed with SRCLK         0 = SRCLK has no effect on the reset input of the SR latch       5 SRCEK       5 SRCEK         bit 3       SRR                                                                                                                                                                                         |                  |              |                       |                |                    |                 |                       |             |

| u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reset         '1' = Bit is set       '0' = Bit is cleared         bit 7       SRSPE: SR Latch Peripheral Set Enable bit         1 = SR latch is set when the SRI pin is high       0 = SRI pin has no effect on the set input of the SR latch         bit 6       SRSCKE: SR Latch Set Clock Enable bit         1 = Set input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSCZE: SR Latch C2 Set Enable bit         1 = SR latch is set when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSCTE: SR Latch C1 Set Enable bit       1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch       SR RPE: SR Latch Peripheral Reset Enable bit         1 = SR latch is set when the SRI pin is high       0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit       1 = Reset input of SR latch is pulsed with SRCLK         0 = SRI pin has no effect on the reset input of the SR latch       0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit       1 = Reset input of SR latch is pulsed with SRCLK         0 = SRI pin has no effect on the                                                                                                                                                                         | Legend:          |              |                       |                |                    |                 |                       |             |

| '1' = Bit is set       '0' = Bit is cleared         bit 7       SRSPE: SR Latch Peripheral Set Enable bit         1 = SR latch is set when the SRI pin is high       0 = SRI pin has no effect on the set input of the SR latch         bit 6       SRSCKE: SR Latch Set Clock Enable bit         1 = Set input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSCZE: SR Latch C2 Set Enable bit <sup>(1)</sup> 1 = SR latch is set when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSC1E: SR Latch C1 Set Enable bit       1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch       0 = SR latch is reset when the SR latch         bit 3       SRRPE: SR Latch Peripheral Reset Enable bit       1 = SR latch is reset when the SR lpin is high         0 = SRI pin has no effect on the reset input of the SR latch       0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit       1 = Reset input of SR latch is pulsed with SRCLK         0 = SRCLK has no effect on the reset input of the SR latch       0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRCE: SR Latch C2 Reset Enable bit       1 = Reset input of SR latch is pulsed with SRCLK         0 = SRCLK has no effe                                                                                                                                                                      | R = Readable     | bit          | W = Writable I        | oit            | U = Unimpler       | mented bit, rea | d as '0'              |             |

| bit 7       SRSPE: SR Latch Peripheral Set Enable bit         1 = SR latch is set when the SRI pin is high         0 = SRI pin has no effect on the set input of the SR latch         bit 6       SRSCKE: SR Latch Set Clock Enable bit         1 = Set input of SR latch is pulsed with SRCLK         0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSC2E: SR Latch C2 Set Enable bit <sup>(1)</sup> 1 = SR latch is set when the C2 Comparator output is high         0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSC1E: SR Latch C1 Set Enable bit         1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch         bit 3       SRRPE: SR Latch Peripheral Reset Enable bit         1 = SR latch is reset when the SRI pin is high       0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit         1 = SR latch is reset when the SRI pin is high       0 = SRI pin has no effect on the reset input of the SR latch         bit 1       SRRCKE: SR Latch C2 Reset Enable bit         1 = Reset input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRCZE: SR Latch C2 Reset Enable bit         1 = Reset input of SR latch is pulsed with SRCLK <td>u = Bit is unch</td> <td>nanged</td> <td>x = Bit is unkn</td> <td>own</td> <td>-n/n = Value a</td> <td>at POR and BC</td> <td>R/Value at all c</td> <td>ther Resets</td>                                                               | u = Bit is unch  | nanged       | x = Bit is unkn       | own            | -n/n = Value a     | at POR and BC   | R/Value at all c      | ther Resets |

| 1 = SR latch is set when the SRI pin is high         0 = SRI pin has no effect on the set input of the SR latch         bit 6       SRSCKE: SR Latch Set Clock Enable bit         1 = Set input of SR latch is pulsed with SRCLK         0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSCZE: SR Latch C2 Set Enable bit <sup>(1)</sup> 1 = SR latch is set when the C2 Comparator output is high         0 = C2 comparator output has no effect on the set input of the SR latch         bit 4       SRSCTE: SR Latch C1 Set Enable bit         1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch         bit 3       SRRPE: SR Latch Peripheral Reset Enable bit         1 = SR latch is reset when the SRI pin is high         0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit         1 = Reset input of SR latch is pulsed with SRCLK         0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRCZE: SR Latch C2 Reset Enable bit         1 = Reset input of SR latch is pulsed with SRCLK         0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRCZE: SR Latch C2 Reset Enable bit         1 = Reset input of SR latch is pulsed with SRCLK         0 = C2 C                                                                                                                                                                                                                                                                                   | '1' = Bit is set |              | '0' = Bit is clea     | ared           |                    |                 |                       |             |

| 1 = SR latch is set when the SRI pin is high         0 = SRI pin has no effect on the set input of the SR latch         bit 6       SRSCKE: SR Latch Set Clock Enable bit         1 = Set input of SR latch is pulsed with SRCLK         0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSC2E: SR Latch C2 Set Enable bit <sup>(1)</sup> 1 = SR latch is set when the C2 Comparator output is high         0 = C2 comparator output has no effect on the set input of the SR latch         bit 4       SRSC1E: SR Latch C1 Set Enable bit         1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch         bit 3       SRRPE: SR Latch Peripheral Reset Enable bit         1 = SR latch is reset when the SRI pin is high         0 = C1 Comparator output has no effect on the set input of the SR latch         bit 3       SRRPE: SR Latch Reset Clock Enable bit         1 = SR latch is reset when the SRI pin is high         0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit         1 = Reset input of SR latch is pulsed with SRCLK         0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRCZE: SR Latch C2 Reset Enable bit         1 = Reset input of SR latch is pulsed with SRCLK                                                                                                                                                                                                                                                                                       |                  |              |                       |                |                    |                 |                       |             |

| 0 = SRI pin has no effect on the set input of the SR latch         bit 6       SRSCKE: SR Latch Set Clock Enable bit         1 = Set input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSC2E: SR Latch C2 Set Enable bit <sup>(1)</sup> 1 = SR latch is set when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSC1E: SR Latch C1 Set Enable bit       1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch       0 = C1 Comparator output has no effect on the set input of the SR latch         bit 3       SRRPE: SR Latch Peripheral Reset Enable bit       1 = SR latch is reset when the SRI pin is high         0 = SRI pin has no effect on the reset input of the SR latch       0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit       1 = Reset input of SR latch is pulsed with SRCLK         0 = SRI pin has no effect on the reset input of the SR latch       0 = SRI pin has no effect on the reset input of the SR latch         bit 1       = Reset input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch C2 Reset Enable bit       1 = Reset input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the reset input of the SR latch <td>bit 7</td> <td>SRSPE: SR</td> <td>Latch Periphera</td> <td>I Set Enable I</td> <td>bit</td> <td></td> <td></td> <td></td> | bit 7            | SRSPE: SR    | Latch Periphera       | I Set Enable I | bit                |                 |                       |             |

| bit 6       SRSCKE: SR Latch Set Clock Enable bit         1 = Set input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSC2E: SR Latch C2 Set Enable bit <sup>(1)</sup> 1 = SR latch is set when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSC1E: SR Latch C1 Set Enable bit       1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch       0 = C1 Comparator output has no effect on the set input of the SR latch         bit 3       SRRPE: SR Latch Peripheral Reset Enable bit       1 = SR latch is reset when the SRI pin is high         0 = SRI pin has no effect on the reset input of the SR latch       0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit       1 = Reset input of SR latch is pulsed with SRCLK         0 = SRI pin has no effect on the reset input of the SR latch       0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRC2E: SR Latch C2 Reset Enable bit <sup>(1)</sup> 1 = Reset input of SR latch is pulsed with SRCLK         0 = SRI pin has no effect on the reset input of the SR latch       0 = C2 Comparator output has no effect on the reset input of the SR latch         bit 1       SRRC2E: SR Latch C2 Reset Enable bit       1 = SR latch is reset when the C2 Comparator output is high </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                           |                  |              |                       |                |                    |                 |                       |             |

| 1 = Set input of SR latch is pulsed with SRCLK         0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSC2E: SR Latch C2 Set Enable bit <sup>(1)</sup> 1 = SR latch is set when the C2 Comparator output is high         0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSC1E: SR Latch C1 Set Enable bit         1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch         bit 3       SRRPE: SR Latch Peripheral Reset Enable bit         1 = SR latch is reset when the SRI pin is high       0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit         1 = Reset input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRCZE: SR Latch C2 Reset Enable bit         1 = Reset input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRCZE: SR Latch C2 Reset Enable bit <sup>(1)</sup> 1 = SR latch is reset when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the reset input of the SR latch         bit 1       SRRCZE: SR Latch C1 Reset Enable bit       1 = SR latch is reset when the C1 Comparator output is high         0 = C2 Comparator output has no effect on the reset input                                                                                                                                                                                             | 1.1.0            | •            |                       | •              | of the SR latch    |                 |                       |             |

| 0 = SRCLK has no effect on the set input of the SR latch         bit 5       SRSC2E: SR Latch C2 Set Enable bit <sup>(1)</sup> 1 = SR latch is set when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSC1E: SR Latch C1 Set Enable bit       1 = SR latch is set when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the set input of the SR latch       SRRPE: SR Latch Peripheral Reset Enable bit         1 = SR latch is reset when the SRI pin is high       0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit         1 = Reset input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRC2E: SR Latch C2 Reset Enable bit <sup>(1)</sup> 1 = Reset input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRC2E: SR Latch C2 Reset Enable bit <sup>(1)</sup> 1 = SR latch is reset when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the reset input of the SR latch         bit 0       SRRC1E: SR Latch C1 Reset Enable bit       1 = SR latch is reset when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the reset input of the SR latch       1 = SR latch is reset when the C1 Comparator output is high         0 = C1 Comparator output has                                                                                                                                        | DIT 6            |              |                       |                |                    |                 |                       |             |

| bit 5SRSC2E: SR Latch C2 Set Enable bit<br>1 = SR latch is set when the C2 Comparator output is high<br>0 = C2 Comparator output has no effect on the set input of the SR latchbit 4SRSC1E: SR Latch C1 Set Enable bit<br>1 = SR latch is set when the C1 Comparator output is high<br>0 = C1 Comparator output has no effect on the set input of the SR latchbit 3SRRPE: SR Latch Peripheral Reset Enable bit<br>1 = SR latch is reset when the SRI pin is high<br>0 = SRI pin has no effect on the reset input of the SR latchbit 2SRRCKE: SR Latch Reset Clock Enable bit<br>1 = Reset input of SR latch is pulsed with SRCLK<br>0 = SRCLK has no effect on the reset input of the SR latchbit 1SRRC2E: SR Latch C2 Reset Enable bit<br>1 = SR latch is reset when the C2 Comparator output is high<br>0 = C2 Comparator output has no effect on the reset input of the SR latchbit 1SRRC2E: SR Latch C2 Reset Enable bit<br>1 = SR latch is reset when the C2 Comparator output is high<br>0 = C2 Comparator output has no effect on the reset input of the SR latchbit 0SRRC1E: SR Latch C1 Reset Enable bit<br>1 = SR latch is reset when the C1 Comparator output is high<br>0 = C1 Comparator output has no effect on the reset input of the SR latchbit 0SRRC1E: SR Latch C1 Reset Enable bit<br>1 = SR latch is reset when the C1 Comparator output is high<br>0 = C1 Comparator output has no effect on the reset input of the SR latch                                                                                                                                                                                                                                                                       |                  |              |                       |                |                    | 1               |                       |             |

| 0 = C2 Comparator output has no effect on the set input of the SR latch         bit 4       SRSC1E: SR Latch C1 Set Enable bit         1 = SR latch is set when the C1 Comparator output is high       0 = C1 Comparator output has no effect on the set input of the SR latch         bit 3       SRRPE: SR Latch Peripheral Reset Enable bit         1 = SR latch is reset when the SRI pin is high       0 = SRI pin has no effect on the reset input of the SR latch         bit 2       SRRCKE: SR Latch Reset Clock Enable bit         1 = Reset input of SR latch is pulsed with SRCLK       0 = SRCLK has no effect on the reset input of the SR latch         bit 1       SRRC2E: SR Latch C2 Reset Enable bit <sup>(1)</sup> 1 = SR latch is reset when the C2 Comparator output is high       0 = C2 Comparator output has no effect on the reset input of the SR latch         bit 1       SRRC2E: SR Latch C1 Reset Enable bit <sup>(1)</sup> 1 = SR latch is reset when the C2 Comparator output is high         0 = C2 Comparator output has no effect on the reset input of the SR latch       SR latch is reset when the C1 Comparator output is high         0 = C1 Comparator output has no effect on the reset input of the SR latch       SR latch is reset when the C1 Comparator output is high                                                                                                                                                                                                                                                                                                                                                                                                   | bit 5            |              |                       |                |                    |                 |                       |             |

| bit 4SRSC1E: SR Latch C1 Set Enable bit<br>1 = SR latch is set when the C1 Comparator output is high<br>0 = C1 Comparator output has no effect on the set input of the SR latchbit 3SRRPE: SR Latch Peripheral Reset Enable bit<br>1 = SR latch is reset when the SRI pin is high<br>0 = SRI pin has no effect on the reset input of the SR latchbit 2SRRCKE: SR Latch Reset Clock Enable bit<br>1 = Reset input of SR latch is pulsed with SRCLK<br>0 = SRCLK has no effect on the reset input of the SR latchbit 1SRRC2E: SR Latch C2 Reset Enable bit<br>1 = SR latch is reset when the C2 Comparator output is high<br>0 = C2 Comparator output has no effect on the reset input of the SR latchbit 0SRRC1E: SR Latch C1 Reset Enable bit<br>1 = SR latch is reset when the C1 Comparator output is high<br>0 = C1 Comparator output has no effect on the reset input of the SR latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  | 1 = SR latch | is set when the       | C2 Compara     | tor output is high | gh              |                       |             |

| 1 = SR latch is set when the C1 Comparator output is high<br>0 = C1 Comparator output has no effect on the set input of the SR latchbit 3SRRPE: SR Latch Peripheral Reset Enable bit<br>1 = SR latch is reset when the SRI pin is high<br>0 = SRI pin has no effect on the reset input of the SR latchbit 2SRRCKE: SR Latch Reset Clock Enable bit<br>1 = Reset input of SR latch is pulsed with SRCLK<br>0 = SRCLK has no effect on the reset input of the SR latchbit 1SRRC2E: SR Latch C2 Reset Enable bit<br>1 = SR latch is reset when the C2 Comparator output is high<br>0 = C2 Comparator output has no effect on the reset input of the SR latchbit 0SRRC1E: SR Latch C1 Reset Enable bit<br>1 = SR latch is reset when the C1 Comparator output is high<br>0 = C1 Comparator output has no effect on the reset input of the SR latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  | 0 = C2 Com   | parator output h      | as no effect o | on the set input   | of the SR latch | 1                     |             |

| <ul> <li>0 = C1 Comparator output has no effect on the set input of the SR latch</li> <li>bit 3 SRRPE: SR Latch Peripheral Reset Enable bit         <ol> <li>1 = SR latch is reset when the SRI pin is high                 0 = SRI pin has no effect on the reset input of the SR latch</li> </ol> </li> <li>bit 2 SRRCKE: SR Latch Reset Clock Enable bit         <ol> <li>1 = Reset input of SR latch is pulsed with SRCLK                 0 = SRCLK has no effect on the reset input of the SR latch</li> </ol> </li> <li>bit 1 SRRC2E: SR Latch C2 Reset Enable bit<sup>(1)</sup> <ol> <li>1 = SR latch is reset when the C2 Comparator output is high                 0 = C2 Comparator output has no effect on the reset input of the SR latch</li> </ol> </li> <li>bit 0 SRRC1E: SR Latch C1 Reset Enable bit         <ol> <li>1 = SR latch is reset when the C1 Comparator output is high                 0 = C1 Comparator output has no effect on the reset input of the SR latch</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 4            | SRSC1E: SF   | R Latch C1 Set I      | Enable bit     |                    |                 |                       |             |

| bit 3SRRPE: SR Latch Peripheral Reset Enable bit1 = SR latch is reset when the SRI pin is high0 = SRI pin has no effect on the reset input of the SR latchbit 2SRRCKE: SR Latch Reset Clock Enable bit1 = Reset input of SR latch is pulsed with SRCLK0 = SRCLK has no effect on the reset input of the SR latchbit 1SRRC2E: SR Latch C2 Reset Enable bit1 = SR latch is reset when the C2 Comparator output is high0 = C2 Comparator output has no effect on the reset input of the SR latchbit 0SRRC1E: SR Latch C1 Reset Enable bit1 = SR latch is reset when the C1 Comparator output is high0 = C1 Comparator output has no effect on the reset input of the SR latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |              |                       |                |                    |                 |                       |             |

| <ul> <li>1 = SR latch is reset when the SRI pin is high</li> <li>0 = SRI pin has no effect on the reset input of the SR latch</li> <li>bit 2 SRRCKE: SR Latch Reset Clock Enable bit</li> <li>1 = Reset input of SR latch is pulsed with SRCLK</li> <li>0 = SRCLK has no effect on the reset input of the SR latch</li> <li>bit 1 SRRC2E: SR Latch C2 Reset Enable bit<sup>(1)</sup></li> <li>1 = SR latch is reset when the C2 Comparator output is high</li> <li>0 = C2 Comparator output has no effect on the reset input of the SR latch</li> <li>bit 0 SRRC1E: SR Latch C1 Reset Enable bit</li> <li>1 = SR latch is reset when the C1 Comparator output is high</li> <li>0 = C1 Comparator output has no effect on the reset input of the SR latch</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>h</b> it 0    |              |                       |                | •                  | of the SR later | 1                     |             |

| <ul> <li>0 = SRI pin has no effect on the reset input of the SR latch</li> <li>bit 2</li> <li>SRRCKE: SR Latch Reset Clock Enable bit         <ol> <li>1 = Reset input of SR latch is pulsed with SRCLK</li> <li>0 = SRCLK has no effect on the reset input of the SR latch</li> </ol> </li> <li>bit 1</li> <li>SRRC2E: SR Latch C2 Reset Enable bit<sup>(1)</sup> <ol> <li>1 = SR latch is reset when the C2 Comparator output is high</li> <li>0 = C2 Comparator output has no effect on the reset input of the SR latch</li> </ol> </li> <li>bit 0</li> <li>SRRC1E: SR Latch C1 Reset Enable bit         <ol> <li>1 = SR latch is reset when the C1 Comparator output is high</li> <li>0 = C1 Comparator output has no effect on the reset input of the SR latch</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DIL 3            |              |                       |                |                    |                 |                       |             |

| bit 2SRRCKE: SR Latch Reset Clock Enable bit<br>1 = Reset input of SR latch is pulsed with SRCLK<br>0 = SRCLK has no effect on the reset input of the SR latchbit 1SRRC2E: SR Latch C2 Reset Enable bit(1)<br>1 = SR latch is reset when the C2 Comparator output is high<br>0 = C2 Comparator output has no effect on the reset input of the SR latchbit 0SRRC1E: SR Latch C1 Reset Enable bit<br>1 = SR latch is reset when the C1 Comparator output is high<br>0 = C1 Comparator output has no effect on the reset input of the SR latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |              |                       | •              | •                  | ch              |                       |             |

| <ul> <li>0 = SRCLK has no effect on the reset input of the SR latch</li> <li>bit 1</li> <li>SRRC2E: SR Latch C2 Reset Enable bit<sup>(1)</sup></li> <li>1 = SR latch is reset when the C2 Comparator output is high</li> <li>0 = C2 Comparator output has no effect on the reset input of the SR latch</li> <li>bit 0</li> <li>SRRC1E: SR Latch C1 Reset Enable bit</li> <li>1 = SR latch is reset when the C1 Comparator output is high</li> <li>0 = C1 Comparator output has no effect on the reset input of the SR latch</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 2            |              |                       |                |                    |                 |                       |             |

| bit 1SRRC2E: SR Latch C2 Reset Enable bit(1)1 = SR latch is reset when the C2 Comparator output is high<br>0 = C2 Comparator output has no effect on the reset input of the SR latchbit 0SRRC1E: SR Latch C1 Reset Enable bit<br>1 = SR latch is reset when the C1 Comparator output is high<br>0 = C1 Comparator output has no effect on the reset input of the SR latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  | 1 = Reset in | put of SR latch       | is pulsed with | SRCLK              |                 |                       |             |

| <ul> <li>1 = SR latch is reset when the C2 Comparator output is high</li> <li>0 = C2 Comparator output has no effect on the reset input of the SR latch</li> <li>bit 0</li> <li>SRRC1E: SR Latch C1 Reset Enable bit</li> <li>1 = SR latch is reset when the C1 Comparator output is high</li> <li>0 = C1 Comparator output has no effect on the reset input of the SR latch</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  | ·            |                       |                |                    |                 |                       |             |

| <ul> <li>0 = C2 Comparator output has no effect on the reset input of the SR latch</li> <li>bit 0</li> <li>SRRC1E: SR Latch C1 Reset Enable bit</li> <li>1 = SR latch is reset when the C1 Comparator output is high</li> <li>0 = C1 Comparator output has no effect on the reset input of the SR latch</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 1            |              |                       |                |                    |                 |                       |             |

| bit 0 SRRC1E: SR Latch C1 Reset Enable bit<br>1 = SR latch is reset when the C1 Comparator output is high<br>0 = C1 Comparator output has no effect on the reset input of the SR latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |              |                       |                |                    |                 |                       |             |