Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1823-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Peripheral Features (Continued)**

- Data Signal Modulator module

- Selectable modulator and carrier sources

- SR Latch:

- Multiple Set/Reset input options

- Emulates 555 Timer applications

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data EEPROM<br>(bytes) | Data SRAM<br>(bytes) | I/O'S <sup>(2)</sup> | 10-bit ADC (ch) | CapSense (ch) | Comparators | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> C <sup>TM</sup> /SPI) | ECCP (Full-Bridge)<br>ECCP (Half-Bridge)<br>CCP | SR Latch | Debug <sup>(1)</sup> | XLP |

|---------------|------------------|---------------------------------|------------------------|----------------------|----------------------|-----------------|---------------|-------------|----------------------|--------|--------------------------------------------|-------------------------------------------------|----------|----------------------|-----|

| PIC12(L)F1822 | (1)              | 2K                              | 256                    | 128                  | 6                    | 4               | 4             | 1           | 2/1                  | 1      | 1                                          | 0/1/0                                           | Y        | I/H                  | Y   |

| PIC12(L)F1840 | (2)              | 4K                              | 256                    | 256                  | 6                    | 4               | 4             | 1           | 2/1                  | 1      | 1                                          | 0/1/0                                           | Y        | I/H                  | Y   |

| PIC16(L)F1823 | (1)              | 2K                              | 256                    | 128                  | 12                   | 8               | 8             | 2           | 2/1                  | 1      | 1                                          | 1/0/0                                           | Y        | I/H                  | Y   |

| PIC16(L)F1824 | (3)              | 4K                              | 256                    | 256                  | 12                   | 8               | 8             | 2           | 4/1                  | 1      | 1                                          | 1/1/2                                           | Y        | I/H                  | Y   |

| PIC16(L)F1825 | (4)              | 8K                              | 256                    | 1024                 | 12                   | 8               | 8             | 2           | 4/1                  | 1      | 1                                          | 1/1/2                                           | Y        | I/H                  | Y   |

| PIC16(L)F1826 | (5)              | 2K                              | 256                    | 256                  | 16                   | 12              | 12            | 2           | 2/1                  | 1      | 1                                          | 1/0/0                                           | Y        | I/H                  | Y   |

| PIC16(L)F1827 | (5)              | 4K                              | 256                    | 384                  | 16                   | 12              | 12            | 2           | 4/1                  | 1      | 2                                          | 1/1/2                                           | Y        | I/H                  | Y   |

| PIC16(L)F1828 | (3)              | 4K                              | 256                    | 256                  | 18                   | 12              | 12            | 2           | 4/1                  | 1      | 1                                          | 1/1/2                                           | Y        | I/H                  | Y   |

| PIC16(L)F1829 | (4)              | 8K                              | 256                    | 1024                 | 18                   | 12              | 12            | 2           | 4/1                  | 1      | 2                                          | 1/1/2                                           | Y        | I/H                  | Y   |

| PIC16(L)F1847 | (6)              | 8K                              | 256                    | 1024                 | 16                   | 12              | 12            | 2           | 4/1                  | 1      | 2                                          | 1/1/2                                           | Y        | I/H                  | Y   |

#### TABLE 1: PIC12(L)F1822/1840/PIC16(L)F182X/1847 FAMILY TYPES

Note 1: I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS41413 PIC12(L)F1822/PIC16(L)F1823 Data Sheet, 8/14-Pin Flash Microcontrollers.

2: DS41441 PIC12(L)F1840 Data Sheet, 8-Pin Flash Microcontrollers.

**3:** DS41419 PIC16(L)F1824/1828 Data Sheet, 28/40/44-Pin Flash Microcontrollers.

4: DS41440 PIC16(L)F1825/1829 Data Sheet, 14/20-Pin Flash Microcontrollers.

5: DS41391 PIC16(L)F1826/1827 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

6: DS41453 PIC16(L)F1847 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

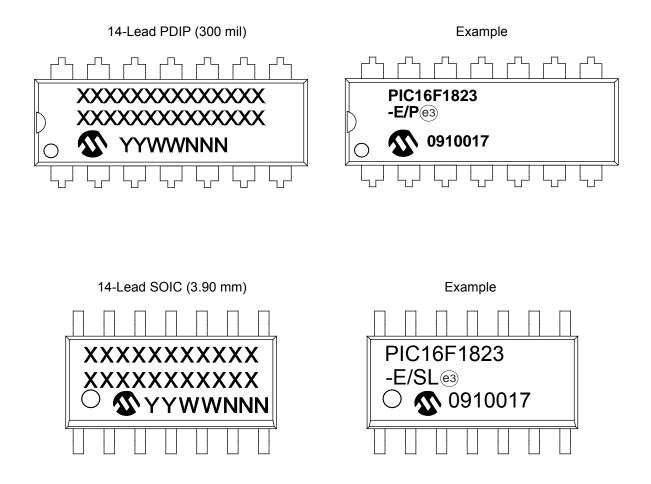

**Note:** For other small form-factor package availability and marking information, please visit www.microchip.com/packaging or contact your local sales office.

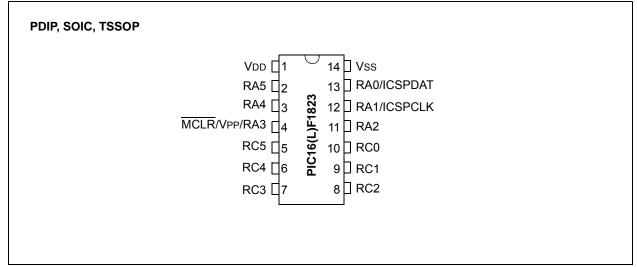

#### FIGURE 2: 14-PIN DIAGRAM FOR PIC16(L)F1823

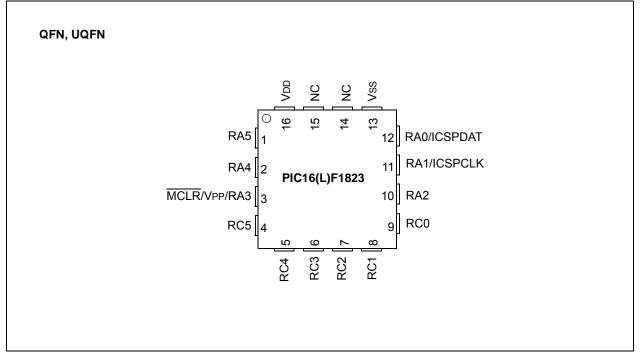

#### FIGURE 3: 16-PIN DIAGRAM FOR PIC16(L)F1823

#### **REGISTER 4-1: CONFIGURATION WORD 1**

|                      |                                                                                                                                                                             | FCMEN                                                       | IESO                       | CLKOUTEN                       | BORE             | N<1.0>             |               |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------|--------------------------------|------------------|--------------------|---------------|

|                      |                                                                                                                                                                             |                                                             |                            | OLIGOTEIN                      | BORL             | N~1.0/             | CPD           |

|                      |                                                                                                                                                                             | bit 13                                                      |                            |                                |                  |                    | bit 8         |

|                      |                                                                                                                                                                             |                                                             |                            |                                |                  |                    |               |

| R/P-1/1              | R/P-1/1                                                                                                                                                                     | R/P-1/1                                                     | R/P-1/1                    | R/P-1/1                        | R/P-1/1          | R/P-1/1            | R/P-1/1       |

| CP                   | MCLRE                                                                                                                                                                       | PWRTE                                                       | WD                         | ΓE<1:0>                        |                  | FOSC<2:0>          |               |

| bit 7                |                                                                                                                                                                             | •                                                           |                            |                                |                  |                    | bit           |

|                      |                                                                                                                                                                             |                                                             |                            |                                |                  |                    |               |

| Legend:              |                                                                                                                                                                             |                                                             |                            |                                |                  |                    |               |

| R = Readable bit     |                                                                                                                                                                             | P = Programm                                                | able bit                   | U = Unimpleme                  | nted bit, read a | ıs '1'             |               |

| '0' = Bit is cleared |                                                                                                                                                                             | '1' = Bit is set                                            |                            | -n = Value wher                | n blank or after | Bulk Erase         |               |

| bit 13               | FCMEN: Fail-Sa                                                                                                                                                              | fe Clock Monitor                                            | Enable bit                 |                                |                  |                    |               |

|                      |                                                                                                                                                                             | ock Monitor is ena<br>ock Monitor is disa                   |                            |                                |                  |                    |               |

|                      | 1 = Internal/Exte                                                                                                                                                           | xternal Switchove<br>rnal Switchover n<br>rnal Switchover n | node is enable             |                                |                  |                    |               |

| bit 11               | CLKOUTEN: Clo                                                                                                                                                               | ock Out Enable bi                                           | it                         |                                |                  |                    |               |

|                      | If FOSC configuration bits are set to LP. XT. HS modes:<br>This bit is ignored, CLKOUT function is disabled. Oscillator function on the CLKOUT pin<br>All other FOSC modes: |                                                             |                            |                                |                  |                    |               |

|                      |                                                                                                                                                                             | JT function is disa<br>JT function is ena                   |                            | tion on the CLKOL<br>_KOUT pin | JT pin           |                    |               |

|                      |                                                                                                                                                                             | Brown-out Reset E                                           | Enable bits <sup>(1)</sup> |                                |                  |                    |               |

|                      | 11 = BOR enable                                                                                                                                                             |                                                             | on and disable             | d in Sleen                     |                  |                    |               |

|                      | <ul> <li>10 = BOR enabled during operation and disabled in Sleep</li> <li>01 = BOR controlled by SBOREN bit of the BORCON register</li> <li>00 = BOR disabled</li> </ul>    |                                                             |                            |                                |                  |                    |               |

|                      | CPD: Data Code                                                                                                                                                              |                                                             | is disabled                |                                |                  |                    |               |

|                      |                                                                                                                                                                             | y code protection<br>y code protection                      |                            |                                |                  |                    |               |

|                      | CP: Code Protec                                                                                                                                                             |                                                             |                            |                                |                  |                    |               |

|                      | 1 = Program memory code protection is disabled<br>0 = Program memory code protection is enabled                                                                             |                                                             |                            |                                |                  |                    |               |

|                      | •                                                                                                                                                                           | VPP Pin Function                                            |                            | 1                              |                  |                    |               |

|                      | If LVP bit = $1$ :                                                                                                                                                          |                                                             |                            |                                |                  |                    |               |

|                      | This bit is ig                                                                                                                                                              | nored.                                                      |                            |                                |                  |                    |               |

|                      | <u>lf LVP bit = 0</u> :<br>1 = MCLR/V                                                                                                                                       | PP pin function is                                          | MCLR; Weak p               | ull-up enabled.                |                  |                    |               |

|                      |                                                                                                                                                                             |                                                             |                            | ICLR internally disa           | abled; Weak pu   | II-up under contro | ol of the WPU |

| bit 5                |                                                                                                                                                                             | up Timer Enable                                             | bit <sup>(1)</sup>         |                                |                  |                    |               |

|                      | 1 = PWRT disa                                                                                                                                                               |                                                             |                            |                                |                  |                    |               |

|                      | 0 = PWRT enat<br>WDTE<1:0>: Wa                                                                                                                                              | oled<br>atchdog Timer En                                    | able bit                   |                                |                  |                    |               |

|                      | 11 = WDT enab                                                                                                                                                               | -                                                           |                            |                                |                  |                    |               |

|                      |                                                                                                                                                                             | led while running                                           |                            | •                              |                  |                    |               |

|                      | 01 = WDT contr<br>00 = WDT disab                                                                                                                                            |                                                             | IEN bit in the             | WDTCON registe                 | r                |                    |               |

3: The entire program memory will be erased when the code protection is turned off.

| REGISTER 10-1: | WDTCON: WATCHDOG TIMER CONTROL REGISTER |

|----------------|-----------------------------------------|

|                |                                         |

| U-0             | U-0              | R/W-0/0                                                            | R/W-1/1               | R/W-0/0         | R/W-1/1          | R/W-1/1         | R/W-0/0      |

|-----------------|------------------|--------------------------------------------------------------------|-----------------------|-----------------|------------------|-----------------|--------------|

| _               | _                |                                                                    |                       | WDTPS<4:0       | >                |                 | SWDTEN       |

| bit 7           |                  |                                                                    |                       |                 |                  |                 | bit          |

|                 |                  |                                                                    |                       |                 |                  |                 |              |

| Legend:         |                  |                                                                    |                       |                 |                  |                 |              |

| R = Readabl     |                  | W = Writable                                                       |                       | •               | mented bit, read |                 |              |

| u = Bit is unc  | 0                | x = Bit is unkr                                                    | nown                  | -m/n = Value    | at POR and BO    | OR/Value at all | other Resets |

| '1' = Bit is se | t                | '0' = Bit is cle                                                   | ared                  |                 |                  |                 |              |

| bit 7-6         | Unimplem         | ented: Read as '                                                   | 0'                    |                 |                  |                 |              |

| bit 5-1         | -                | :0>: Watchdog Ti                                                   |                       | elect bits      |                  |                 |              |

|                 |                  | Prescale Rate                                                      |                       |                 |                  |                 |              |

|                 |                  | 1:32 (Interval 1 m                                                 | s tvp)                |                 |                  |                 |              |

|                 |                  | 1:64 (Interval 2 m                                                 |                       |                 |                  |                 |              |

|                 | 00010 = 1        | 1:128 (Interval 4 r                                                | ns typ)               |                 |                  |                 |              |

|                 |                  | 1:256 (Interval 8 r                                                |                       |                 |                  |                 |              |

|                 |                  | 1:512 (Interval 16                                                 |                       |                 |                  |                 |              |

|                 |                  | 1:1024 (Interval 3<br>1:2048 (Interval 6                           | <b>2</b> • • <i>i</i> |                 |                  |                 |              |

|                 |                  | 1:4096 (Interval 0                                                 |                       |                 |                  |                 |              |

|                 |                  | 1:8192 (Interval 2                                                 |                       |                 |                  |                 |              |

|                 | 01001 = 1        | 1:16384 (Interval                                                  | 512 ms typ)           |                 |                  |                 |              |

|                 |                  | :32768 (Interval                                                   |                       |                 |                  |                 |              |

|                 | 01011 = 1        | 1:65536 (Interval                                                  | 2s typ) (Rese         | et value)       |                  |                 |              |

|                 | 01100 = 1        | l:131072 (2 <sup>17</sup> ) (Ir<br>l:262144 (2 <sup>18</sup> ) (Ir | iterval 4s typ)       |                 |                  |                 |              |

|                 |                  | 1:524288 (2 <sup>19</sup> ) (Ir                                    |                       |                 |                  |                 |              |

|                 | 01111 = 1        | 1:1048576 (2 <sup>20</sup> ) (                                     | Interval 32s ty       | (q)             |                  |                 |              |

|                 | 10000 = 1        | 1:2097152 (2 <sup>21</sup> ) (                                     | Interval 64s ty       | /p)             |                  |                 |              |

|                 | 10001 = 1        | I:4194304 (2 <sup>22</sup> ) (                                     | Interval 128s         | typ)            |                  |                 |              |

|                 | 10010 = 1        | 1:8388608 (2 <sup>23</sup> ) (                                     | Interval 256s         | typ)            |                  |                 |              |

|                 | 10011 <b>= F</b> | Reserved. Result                                                   | s in minimum          | interval (1:32) |                  |                 |              |

|                 | •                |                                                                    |                       |                 |                  |                 |              |

|                 | •                |                                                                    |                       |                 |                  |                 |              |

|                 | 11111 = F        | Reserved. Result                                                   | s in minimum          | interval (1:32) |                  |                 |              |

| bit 0           |                  | Software Enable/                                                   |                       |                 | bit              |                 |              |

|                 | If WDTE<1        |                                                                    |                       | 5               |                  |                 |              |

|                 | This bit is ig   | gnored.                                                            |                       |                 |                  |                 |              |

|                 | If WDTE<1        |                                                                    |                       |                 |                  |                 |              |

|                 | 1 = WDT is       |                                                                    |                       |                 |                  |                 |              |

|                 | $\cap = WDTie$   |                                                                    |                       |                 |                  |                 |              |

|                 | If WDTE<1        | s turned off $= 1$                                                 |                       |                 |                  |                 |              |

#### 16.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |

|---------|------------------------------------------|

|         | every conversion, regardless of whether  |

|         | or not the ADC interrupt is enabled.     |

|         |                                          |

2: The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

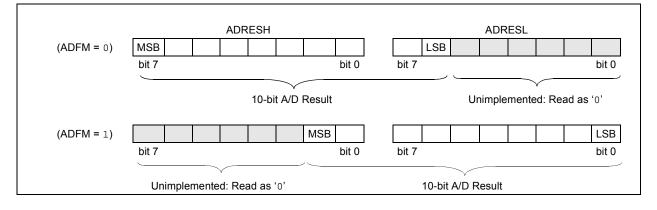

#### 16.1.6 RESULT FORMATTING

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 16-3 shows the two output formats.

#### FIGURE 16-3: 10-BIT A/D CONVERSION RESULT FORMAT

#### 16.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 16-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 16-4. **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 16-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 16-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - I}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} (1 - \frac{1}{(2^{n+1}) - I}) ; combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$Tc = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

$$= -12.5pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$$

$$= 1.72\mu s$$

Therefore:

$$TACQ = 2\mu s + 1.72\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.97\mu s

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

| R/W-0/0                                                              | R/W-0/0                                                                                                          | R/W-1/1                                                                                        | R/W-0/0         | R-0/0          | U-0                | U-0            | R/W-0/0      |  |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------|----------------|--------------------|----------------|--------------|--|

| MDEN                                                                 | MDOE                                                                                                             | MDSLR                                                                                          | MDOPOL          | MDOUT          | —                  | —              | MDBIT        |  |

| bit 7                                                                |                                                                                                                  |                                                                                                |                 |                |                    |                | bit 0        |  |

|                                                                      |                                                                                                                  |                                                                                                |                 |                |                    |                |              |  |

| Legend:                                                              |                                                                                                                  |                                                                                                |                 |                |                    |                |              |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                                                  |                                                                                                |                 |                |                    |                |              |  |

| u = Bit is und                                                       | changed                                                                                                          | x = Bit is unk                                                                                 | nown            | -n/n = Value   | at POR and BOP     | R/Value at all | other Resets |  |

| '1' = Bit is se                                                      | et                                                                                                               | '0' = Bit is cle                                                                               | eared           |                |                    |                |              |  |

|                                                                      |                                                                                                                  |                                                                                                |                 |                |                    |                |              |  |

| bit 7                                                                | MDEN: Mod                                                                                                        | ulator Module E                                                                                | Enable bit      |                |                    |                |              |  |

|                                                                      |                                                                                                                  | or module is er                                                                                |                 | • • •          | als                |                |              |  |

|                                                                      |                                                                                                                  | or module is di                                                                                |                 | •              |                    |                |              |  |

| bit 6                                                                | MDOE: Mod                                                                                                        | MDOE: Modulator Module Pin Output Enable bit                                                   |                 |                |                    |                |              |  |

|                                                                      |                                                                                                                  | or pin output ei                                                                               |                 |                |                    |                |              |  |

|                                                                      |                                                                                                                  | 0 = Modulator pin output disabled                                                              |                 |                |                    |                |              |  |

| bit 5                                                                |                                                                                                                  | OUT Pin Slew                                                                                   | 0               |                |                    |                |              |  |

|                                                                      |                                                                                                                  | pin slew rate l                                                                                |                 |                |                    |                |              |  |

| bit 4                                                                |                                                                                                                  | Iodulator Outpu                                                                                | 0               |                |                    |                |              |  |

|                                                                      |                                                                                                                  |                                                                                                |                 |                |                    |                |              |  |

|                                                                      | <ul> <li>1 = Modulator output signal is inverted</li> <li>0 = Modulator output signal is not inverted</li> </ul> |                                                                                                |                 |                |                    |                |              |  |

| bit 3                                                                | MDOUT: Modulator Output bit                                                                                      |                                                                                                |                 |                |                    |                |              |  |

|                                                                      | Displays the                                                                                                     | Displays the current output value of the Modulator module. <sup>(1)</sup>                      |                 |                |                    |                |              |  |

| bit 2-1                                                              | Unimpleme                                                                                                        | Unimplemented: Read as '0'                                                                     |                 |                |                    |                |              |  |

| bit 0                                                                | MDBIT: Allow                                                                                                     | <b>MDBIT:</b> Allows software to manually set modulation source input to module <sup>(2)</sup> |                 |                |                    |                |              |  |

|                                                                      |                                                                                                                  | or uses High C                                                                                 |                 |                |                    |                |              |  |

|                                                                      | 0 = Modulat                                                                                                      | or uses Low Ca                                                                                 | arrier source   |                |                    |                |              |  |

| Note 1: ⊤                                                            | he modulated ou                                                                                                  | utput frequency                                                                                | can be greate   | r and asynchro | onous from the c   | lock that upd  | ates this    |  |

| re                                                                   | egister bit, the bi                                                                                              | t value may not                                                                                | be valid for hi | gher speed mo  | odulator or carrie | er signals.    |              |  |

|                                                                      |                                                                                                                  |                                                                                                |                 |                |                    |                |              |  |

#### REGISTER 23-1: MDCON: MODULATION CONTROL REGISTER

2: MDBIT must be selected as the modulation source in the MDSRC register for this operation.

#### 24.3.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 24.3.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 24.3.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 24.3.9 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function**" for more information.

| Name                 | Bit 7         | Bit 6                                           | Bit 5          | Bit 4      | Bit 3  | Bit 2   | Bit 1                 | Bit 0                  | Register<br>on Page |

|----------------------|---------------|-------------------------------------------------|----------------|------------|--------|---------|-----------------------|------------------------|---------------------|

| APFCON               | RXDTSEL       | SDOSEL                                          | SSSEL          | —          | T1GSEL | TXCKSEL | P1BSEL <sup>(2)</sup> | CCP1SEL <sup>(2)</sup> | 114                 |

| CCP1CON              | P1M·          | <1:0>                                           | DC1B           | <1:0>      |        | CCP1I   | V<3:0>                |                        | 213                 |

| CCPR1L               | Capture/Com   | pare/PWM Re                                     | gister x Low B | syte (LSB) |        |         |                       |                        | 191                 |

| INTCON               | GIE           | PEIE                                            | TMR0IE         | INTE       | IOCIE  | TMR0IF  | INTF                  | IOCIF                  | 86                  |

| PIE1                 | TMR1GIE       | ADIE                                            | RCIE           | TXIE       | SSP1IE | CCP1IE  | TMR2IE                | TMR1IE                 | 87                  |

| PIR1                 | TMR1GIF       | ADIF                                            | RCIF           | TXIF       | SSP1IF | CCP1IF  | TMR2IF                | TMR1IF                 | 89                  |

| PR2                  | Timer2 Period | d Register                                      |                |            |        |         |                       |                        | 176*                |

| T2CON                | -             | T2OUTPS<3:0>         TMR2ON         T2CKPS<:0>1 |                |            |        |         |                       | 178                    |                     |

| TMR2                 | Timer2 Modu   | Timer2 Module Register                          |                |            |        |         |                       | 176*                   |                     |

| TRISA                | _             | —                                               | TRISA5         | TRISA4     | TRISA3 | TRISA2  | TRISA1                | TRISA0                 | 117                 |

| TRISC <sup>(1)</sup> | _             | _                                               | TRISC5         | TRISC4     | TRISC3 | TRISC2  | TRISC1                | TRISC0                 | 121                 |

#### TABLE 24-8: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the PWM.

\* Page provides register information.

**Note 1:** PIC16(L)F1823 only.

2: PIC12(L)F1822 only.

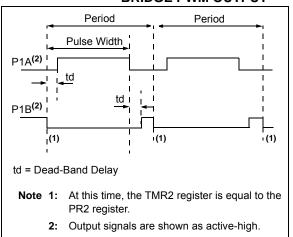

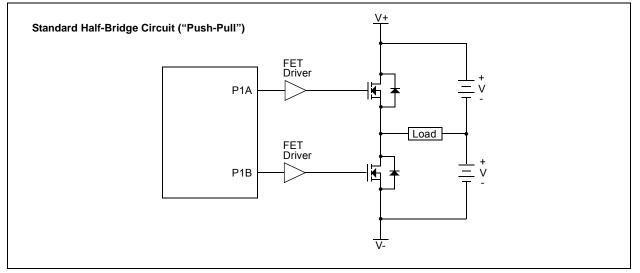

#### 24.4.5 PROGRAMMABLE DEAD-BAND DELAY MODE

In Half-Bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable deadband delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 24-16 for illustration. The lower seven bits of the associated PWM1CON register (Register 24-3) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### FIGURE 24-16: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

#### FIGURE 24-17: EXAMPLE OF HALF-BRIDGE APPLICATIONS

| R/W-0/0        | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0            | R/W-0/0      | R/W-0/0       | R/W-0/0          | R/W-0/0  | R/W-0/0      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|---------------|------------------|----------|--------------|

| CCP1AS         | Ξ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CCP1AS<2:0>        |              | PSS1A         | AC<1:0>          | PSS1B    | SD<1:0>      |

| bit 7          | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |              |               |                  |          | bit (        |

| Legend:        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |              |               |                  |          |              |

| R = Readat     | ole hit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable b     | nit          | II – Unimpler | nented bit, read | 1 ac '0' |              |

| u = Bit is ur  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | x = Bit is unknown |              | •             | at POR and BO    |          | other Resets |

| '1' = Bit is s | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | '0' = Bit is clea  |              |               |                  |          |              |

| 1 - Dit 13 3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | licu         |               |                  |          |              |

| bit 7          | CCP1ASE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | : CCP1 Auto-Shut   | down Event S | Status bit    |                  |          |              |

|                | 1 = A shutdown event has occurred; CCP1 outputs are in shutdown state<br>0 = CCP1 outputs are operating                                                                                                                                                                                                                                                                                                                                                                                                        |                    |              |               |                  |          |              |

| bit 6-4        | <b>CCP1AS&lt;2:0&gt;:</b> CCP1 Auto-Shutdown Source Select bits<br>000 = Auto-shutdown is disabled<br>001 = Comparator C1 output high <sup>(1)</sup><br>010 = Comparator C2 output high <sup>(1, 2)</sup><br>011 = Either Comparator C1 or C2 high <sup>(1, 2)</sup><br>100 = VIL on FLT0 pin<br>101 = VIL on FLT0 pin or Comparator C1 high <sup>(1)</sup><br>110 = VIL on FLT0 pin or Comparator C2 high <sup>(1, 2)</sup><br>111 = VIL on FLT0 pin or Comparator C1 or Comparator C2 high <sup>(1, 2)</sup> |                    |              |               |                  |          |              |

| bit 3-2        | <b>PSS1AC&lt;1:0&gt;:</b> Pins P1A and P1C Shutdown State Control bits <sup>(2)</sup> 00 = Drive pins P1A and P1C to '0' 01 = Drive pins P1A and P1C to '1' 1x = Pins P1A and P1C tri-state                                                                                                                                                                                                                                                                                                                    |                    |              |               |                  |          |              |

| bit 1-0        | <b>PSS1BD&lt;1:0&gt;:</b> Pins P1B and P1D Shutdown State Control bits <sup>(2)</sup><br>00 = Drive pins P1B and P1D to '0'<br>01 = Drive pins P1B and P1D to '1'<br>1x = Pins P1B and P1D tri-state                                                                                                                                                                                                                                                                                                           |                    |              |               |                  |          |              |

|                | f C1SYNC is enabled, the shutdown will be delayed by Timer1.<br>22, P1C and P1D available on PIC16(L)F1823 only.                                                                                                                                                                                                                                                                                                                                                                                               |                    |              |               |                  |          |              |

#### REGISTER 24-2: CCP1AS: CCP1 AUTO-SHUTDOWN CONTROL REGISTER

| TABLE 27-3:         SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSING |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

| Name                  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3                 | Bit 2                 | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|---------|---------|---------|---------|-----------------------|-----------------------|--------|--------|---------------------|

| ANSELA                | —       | —       | _       | ANSA4   | —                     | ANSA2                 | ANSA1  | ANSA0  | 118                 |

| ANSELC <sup>(1)</sup> | _       | —       | _       | _       | ANSC3                 | ANSC2                 | ANSC1  | ANSC0  | 122                 |

| CPSCON0               | CPSON   | CPSRM   | -       | -       | CPSRNG1               | CPSRNG0               | CPSOUT | TOXCS  | 302                 |

| CPSCON1               | _       | —       | _       | —       | CPSCH3 <sup>(1)</sup> | CPSCH2 <sup>(1)</sup> | CPSCH1 | CPSCH0 | 303                 |

| INTCON                | GIE     | PEIE    | TMR0IE  | INTE    | IOCIE                 | TMR0IF                | INTF   | IOCIF  | 86                  |

| OPTION_REG            | WPUEN   | INTEDG  | TMR0CS  | TMR0SE  | PSA                   | PS2                   | PS1    | PS0    | 164                 |

| T1CON                 | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN               | T1SYNC                | —      | TMR10N | 173                 |

| TRISA                 | _       | _       | TRISA5  | TRISA4  | TRISA3                | TRISA2                | TRISA1 | TRISA0 | 117                 |

| TRISC <sup>(1)</sup>  |         | _       | TRISC5  | TRISC4  | TRISC3                | TRISC2                | TRISC1 | TRISC0 | 121                 |

Legend: — = Unimplemented locations, read as '0'. Shaded cells are not used by the CPS module.

Note 1: PIC16(L)F1823 only.

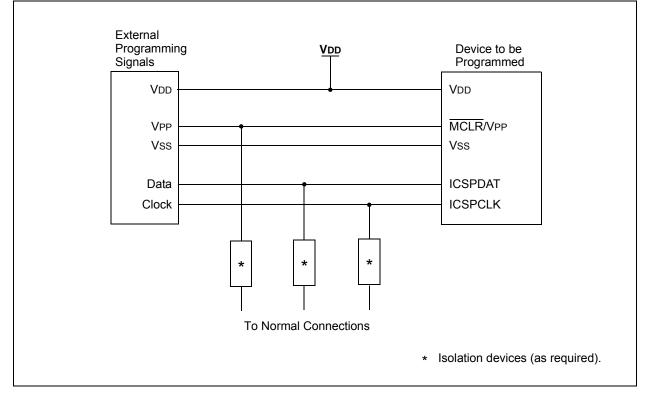

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 28-4 for more information.

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<4:3>) \rightarrow PC<12:11> \end{array}$                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The eleven-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle instruc-<br>tion. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                        |

| Operands:        | None                                                                                                                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow \underline{WDT} \text{ prescaler,} \\ 1 \rightarrow \underline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{TO}$ and $\overline{PD}$<br>are set.            |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Operation:       | (PC) +1 → TOS,<br>(W) → PC<7:0>,<br>(PCLATH<6:0>) → PC<14:8>                                                                                                                                                          |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |  |  |  |  |  |  |

| COMF             | Complement f                                                                                                                                                  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                     |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                               |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                             |  |  |  |  |

| Description:     | The contents of register 'f' are com-<br>plemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

| CLRF             | Clear f                                                                      |  |  |  |

|------------------|------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] CLRF f                                                               |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                          |  |  |  |

| Operation:       | $\begin{array}{l} \text{OOh} \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |  |

| Status Affected: | Z                                                                            |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.               |  |  |  |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                                |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0', the<br>result is stored in the W register. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |

### 30.0 ELECTRICAL SPECIFICATIONS

### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40°C to +125°C                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|