Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            | Active                                                                     |

| Product Status             |                                                                            |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1823-i-ml |

TABLE 3-5: PIC12(L)F1822/16(L)F1823 MEMORY MAP, BANKS 16-23

|       | BANK 16                      | `      | BANK 17                      | •     | BANK 18                      |        | BANK 19                      |      | BANK 20                      |      | BANK 21                      |       | BANK 22                      |        | BANK 23                      |

|-------|------------------------------|--------|------------------------------|-------|------------------------------|--------|------------------------------|------|------------------------------|------|------------------------------|-------|------------------------------|--------|------------------------------|

| 800h  | INDF0                        | 880h   | INDF0                        | 900h  | INDF0                        | 980h   | INDF0                        | A00h | INDF0                        | A80h | INDF0                        | B00h  | INDF0                        | B80h   | INDF0                        |

| 801h  | INDF1                        | 881h   | INDF1                        | 901h  | INDF1                        | 981h   | INDF1                        | A01h | INDF1                        | A81h | INDF1                        | B01h  | INDF1                        | B81h   | INDF1                        |

| 802h  | PCL                          | 882h   | PCL                          | 902h  | PCL                          | 982h   | PCL                          | A02h | PCL                          | A82h | PCL                          | B02h  | PCL                          | B82h   | PCL                          |

| 803h  | STATUS                       | 883h   | STATUS                       | 903h  | STATUS                       | 983h   | STATUS                       | A03h | STATUS                       | A83h | STATUS                       | B03h  | STATUS                       | B83h   | STATUS                       |

| 804h  | FSR0L                        | 884h   | FSR0L                        | 904h  | FSR0L                        | 984h   | FSR0L                        | A04h | FSR0L                        | A84h | FSR0L                        | B04h  | FSR0L                        | B84h   | FSR0L                        |

| 805h  | FSR0H                        | 885h   | FSR0H                        | 905h  | FSR0H                        | 985h   | FSR0H                        | A05h | FSR0H                        | A85h | FSR0H                        | B05h  | FSR0H                        | B85h   | FSR0H                        |

| 806h  | FSR1L                        | 886h   | FSR1L                        | 906h  | FSR1L                        | 986h   | FSR1L                        | A06h | FSR1L                        | A86h | FSR1L                        | B06h  | FSR1L                        | B86h   | FSR1L                        |

| 807h  | FSR1H                        | 887h   | FSR1H                        | 907h  | FSR1H                        | 987h   | FSR1H                        | A07h | FSR1H                        | A87h | FSR1H                        | B07h  | FSR1H                        | B87h   | FSR1H                        |

| 808h  | BSR                          | 888h   | BSR                          | 908h  | BSR                          | 988h   | BSR                          | A08h | BSR                          | A88h | BSR                          | B08h  | BSR                          | B88h   | BSR                          |

| 809h  | WREG                         | 889h   | WREG                         | 909h  | WREG                         | 989h   | WREG                         | A09h | WREG                         | A89h | WREG                         | B09h  | WREG                         | B89h   | WREG                         |

| 80Ah  | PCLATH                       | 88Ah   | PCLATH                       | 90Ah  | PCLATH                       | 98Ah   | PCLATH                       | A0Ah | PCLATH                       | A8Ah | PCLATH                       | B0Ah  | PCLATH                       | B8Ah   | PCLATH                       |

| 80Bh  | INTCON                       | 88Bh   | INTCON                       | 90Bh  | INTCON                       | 98Bh   | INTCON                       | A0Bh | INTCON                       | A8Bh | INTCON                       | B0Bh  | INTCON                       | B8Bh   | INTCON                       |

| 80Ch  | _                            | 88Ch   | _                            | 90Ch  | _                            | 98Ch   | _                            | A0Ch |                              | A8Ch |                              | B0Ch  | _                            | B8Ch   | _                            |

| 80Dh  | _                            | 88Dh   | _                            | 90Dh  | _                            | 98Dh   | _                            | A0Dh |                              | A8Dh |                              | B0Dh  | _                            | B8Dh   | _                            |

| 80Eh  | _                            | 88Eh   | _                            | 90Eh  | _                            | 98Eh   | _                            | A0Eh |                              | A8Eh |                              | B0Eh  | _                            | B8Eh   | _                            |

| 80Fh  | _                            | 88Fh   | _                            | 90Fh  | _                            | 98Fh   | _                            | A0Fh |                              | A8Fh | 1                            | B0Fh  | _                            | B8Fh   | _                            |

| 810h  | _                            | 890h   | _                            | 910h  | _                            | 990h   | _                            | A10h | 1                            | A90h |                              | B10h  | _                            | B90h   | _                            |

| 811h  | _                            | 891h   | _                            | 911h  | _                            | 991h   | _                            | A11h | _                            | A91h | _                            | B11h  | _                            | B91h   | _                            |

| 812h  | _                            | 892h   | _                            | 912h  | _                            | 992h   | _                            | A12h |                              | A92h |                              | B12h  | _                            | B92h   | _                            |

| 813h  | _                            | 893h   | _                            | 913h  | _                            | 993h   | _                            | A13h |                              | A93h |                              | B13h  | _                            | B93h   | _                            |

| 814h  | _                            | 894h   | _                            | 914h  | _                            | 994h   | _                            | A14h | I                            | A94h |                              | B14h  |                              | B94h   | _                            |

| 815h  | _                            | 895h   | _                            | 915h  | _                            | 995h   | _                            | A15h |                              | A95h | _                            | B15h  | _                            | B95h   | _                            |

| 816h  | _                            | 896h   | _                            | 916h  | _                            | 996h   | _                            | A16h |                              | A96h |                              | B16h  | _                            | B96h   | _                            |

| 817h  | _                            | 897h   | _                            | 917h  |                              | 997h   | _                            | A17h |                              | A97h |                              | B17h  |                              | B97h   | _                            |

| 818h  | _                            | 898h   | _                            | 918h  | _                            | 998h   | _                            | A18h | 1                            | A98h |                              | B18h  | _                            | B98h   | _                            |

| 819h  | _                            | 899h   | _                            | 919h  | _                            | 999h   | _                            | A19h |                              | A99h |                              | B19h  | _                            | B99h   | _                            |

| 81Ah  | _                            | 89Ah   | _                            | 91Ah  | _                            | 99Ah   | _                            | A1Ah | _                            | A9Ah | _                            | B1Ah  | _                            | B9Ah   | _                            |

| 81Bh  | _                            | 89Bh   | _                            | 91Bh  | _                            | 99Bh   | _                            | A1Bh |                              | A9Bh | 1                            | B1Bh  | _                            | B9Bh   | _                            |

| 81Ch  | _                            | 89Ch   | _                            | 91Ch  | _                            | 99Ch   | _                            | A1Ch | 1                            | A9Ch |                              | B1Ch  | _                            | B9Ch   | _                            |

| 81Dh  | _                            | 89Dh   | _                            | 91Dh  | _                            | 99Dh   | _                            | A1Dh |                              | A9Dh | _                            | B1Dh  | _                            | B9Dh   | _                            |

| 81Eh  | _                            | 89Eh   | _                            | 91Eh  | _                            | 99Eh   | _                            | A1Eh |                              | A9Eh | _                            | B1Eh  | _                            | B9Eh   | _                            |

| 81Fh  | _                            | 89Fh   | _                            | 91Fh  | _                            | 99Fh   | _                            | A1Fh | _                            | A9Fh | _                            | B1Fh  | _                            | B9Fh   | _                            |

| 820h  |                              | 8A0h   |                              | 920h  |                              | 9A0h   |                              | A20h |                              | AA0h |                              | B20h  |                              | BA0h   |                              |

|       | Unimplemented<br>Read as '0' |        | Unimplemented<br>Read as '0' |       | Unimplemented<br>Read as '0' |        | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |       | Unimplemented<br>Read as '0' |        | Unimplemented<br>Read as '0' |

| 86Fh  |                              | 8EFh   |                              | 96Fh  |                              | 9EFh   |                              | A6Fh |                              | AEFh |                              | B6Fh  |                              | BEFh   |                              |

| 870h  |                              | 8F0h   |                              | 970h  |                              | 9F0h   |                              | A70h |                              | AF0h |                              | B70h  |                              | BF0h   |                              |

| 0.011 | Accesses                     | 3. 011 | Accesses                     | 3.011 | Accesses                     | 3. 011 | Accesses                     | 011  | Accesses                     | 011  | Accesses                     | 2.011 | Accesses                     | 2. 011 | Accesses                     |

|       | 70h – 7Fh                    |        | 70h – 7Fh                    |       | 70h – 7Fh                    |        | 70h – 7Fh                    |      | 70h – 7Fh                    |      | 70h – 7Fh                    |       | 70h – 7Fh                    |        | 70h – 7Fh                    |

| 87Fh  |                              | 8FFh   |                              | 97Fh  |                              | 9FFh   |                              | A7Fh |                              | AFFh |                              | B7Fh  |                              | BFFh   |                              |

| L     |                              | ,      |                              |       |                              | 1      |                              | ļi   |                              | •    |                              |       |                              | ,      | I                            |

**Legend:** = Unimplemented data memory locations, read as '0'.

**TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)**

| IABLE               | 3 <del>-</del> 0. 3  | FECIAL F                       | ONC HON                                     | KEGIST         | EK SUMIN        | IAK I (CC    | ם טאוו ו אוכ | (ט:     |         |                      |                                 |

|---------------------|----------------------|--------------------------------|---------------------------------------------|----------------|-----------------|--------------|--------------|---------|---------|----------------------|---------------------------------|

| Address             | Name                 | Bit 7                          | Bit 6                                       | Bit 5          | Bit 4           | Bit 3        | Bit 2        | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 1              |                      |                                |                                             |                |                 |              |              |         |         |                      |                                 |

| 080h <sup>(1)</sup> | INDF0                | Addressing the (not a physical |                                             | es contents of | FSR0H/FSR0      | L to address | data memory  | 1       |         | xxxx xxxx            | xxxx xxxx                       |

| 081h <sup>(1)</sup> | INDF1                | Addressing the (not a physical |                                             | es contents of | FSR1H/FSR1      | L to address | data memory  | 1       |         | xxxx xxxx            | xxxx xxxx                       |

| 082h <sup>(1)</sup> | PCL                  | Program Cou                    | Program Counter (PC) Least Significant Byte |                |                 |              |              |         |         |                      |                                 |

| 083h <sup>(1)</sup> | STATUS               | _                              | _                                           | _              | TO              | PD           | Z            | DC      | С       | 1 1000               | q quuu                          |

| 084h <sup>(1)</sup> | FSR0L                | Indirect Data                  | Memory Addr                                 | ess 0 Low Poir | nter            |              |              |         |         | 0000 0000            | uuuu uuuu                       |

| 085h <sup>(1)</sup> | FSR0H                | Indirect Data                  | Memory Addr                                 | ess 0 High Poi | nter            |              |              |         |         | 0000 0000            | 0000 0000                       |

| 086h <sup>(1)</sup> | FSR1L                | Indirect Data                  | Memory Addr                                 | ess 1 Low Poir | nter            |              |              |         |         | 0000 0000            | uuuu uuuu                       |

| 087h <sup>(1)</sup> | FSR1H                | Indirect Data                  | Memory Addr                                 | ess 1 High Poi | nter            |              |              |         |         | 0000 0000            | 0000 0000                       |

| 088h <sup>(1)</sup> | BSR                  | _                              | _                                           | _              |                 |              | BSR<4:0>     |         |         | 0 0000               | 0 0000                          |

| 089h <sup>(1)</sup> | WREG                 | Working Reg                    | ister                                       |                |                 |              |              |         |         | 0000 0000            | uuuu uuuu                       |

| 08Ah <sup>(1)</sup> | PCLATH               | _                              | Write Buffer f                              | or the upper 7 | bits of the Pro | gram Counte  | r            |         |         | -000 0000            | -000 0000                       |

| 08Bh <sup>(1)</sup> | INTCON               | GIE                            | PEIE                                        | TMR0IE         | INTE            | IOCIE        | TMR0IF       | INTF    | IOCIF   | 0000 000x            | 0000 000u                       |

| 08Ch                | TRISA                | _                              | _                                           | TRISA5         | TRISA4          | TRISA3       | TRISA2       | TRISA1  | TRISA0  | 11 1111              | 11 1111                         |

| 08Dh                | _                    | Unimplement                    | ted                                         |                | ·               | I.           |              | ·       | I.      | _                    | _                               |

| 08Eh                | TRISC <sup>(2)</sup> | _                              | _                                           | TRISC5         | TRISC4          | TRISC3       | TRISC2       | TRISC1  | TRISC0  | 11 1111              | 11 1111                         |

| 08Fh                |                      | Unimplement                    | ted                                         | •              |                 |              |              |         |         | _                    | _                               |

| 090h                |                      | Unimplement                    | ted                                         |                |                 |              |              |         |         | _                    | _                               |

| 091h                | PIE1                 | TMR1GIE                        | ADIE                                        | RCIE           | TXIE            | SSP1IE       | CCP1IE       | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| 092h                | PIE2                 | OSFIE                          | C2IE <sup>(2)</sup>                         | C1IE           | EEIE            | BCL1IE       | _            | _       | _       | 0000 0               | 0000 0                          |

| 093h                | _                    | Unimplement                    | ted                                         | •              | •               | •            |              | •       | •       | _                    | _                               |

| 094h                | _                    | Unimplement                    | ted                                         |                |                 |              |              |         |         | _                    | _                               |

| 095h                | OPTION_REG           | WPUEN                          | INTEDG                                      | TMR0CS         | TMR0SE          | PSA          |              | PS<2:0> |         | 1111 1111            | 1111 1111                       |

| 096h                | PCON                 | STKOVF                         | STKUNF                                      | _              | _               | RMCLR        | RI           | POR     | BOR     | 00 11qq              | qq qquu                         |

| 097h                | WDTCON               | _                              | _                                           |                | V               | /DTPS<4:0>   |              |         | SWDTEN  | 01 0110              | 01 0110                         |

| 098h                | OSCTUNE              | _                              | _                                           |                |                 | TUN<         | 5:0>         |         |         | 00 0000              | 00 0000                         |

| 099h                | OSCCON               | SPLLEN                         |                                             | IRCF           | <3:0>           |              | _            | SCS     | S<1:0>  | 0011 1-00            | 0011 1-00                       |

| 09Ah                | OSCSTAT              | T10SCR                         | PLLR                                        | OSTS           | HFIOFR          | HFIOFL       | MFIOFR       | LFIOFR  | HFIOFS  | 10q0 0q00            | qqqq qq0q                       |

| 09Bh                | ADRESL               | A/D Result R                   | egister Low                                 | •              |                 | •            |              | •       |         | xxxx xxxx            | uuuu uuuu                       |

| 09Ch                | ADRESH               | A/D Result R                   | egister High                                |                |                 |              |              |         |         | xxxx xxxx            | uuuu uuuu                       |

| 09Dh                | ADCON0               | _                              |                                             |                | CHS<4:0>        |              |              | GO/DONE | ADON    | -000 0000            | -000 0000                       |

| 09Eh                | ADCON1               | ADFM                           |                                             | ADCS<2:0>      |                 | _            | _            | ADPR    | EF<1:0> | 000000               | 000000                          |

| 09Fh                | _                    | Unimplement                    | ted                                         |                |                 |              |              | •       |         | _                    | _                               |

|                     |                      |                                |                                             |                |                 | :I           |              |         |         |                      |                                 |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: PIC16(L)F1823 only.

3: Unimplemented. Read as '1'.

4: PIC12(L)F1822 only.

#### 4.2 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data EEPROM protection are controlled independently. Internal access to the program memory and data EEPROM are unaffected by any code protection setting.

#### 4.2.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Word 1. When  $\overline{CP}=0$ , external reads and writes of program memory are inhibited and a read will return all 'o's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See Section 4.3 "Write Protection" for more information.

#### 4.2.2 DATA EEPROM PROTECTION

The entire data EEPROM is protected from external reads and writes by the  $\overline{CPD}$  bit. When  $\overline{CPD}$  = 0, external reads and writes of data EEPROM are inhibited. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

#### 4.3 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Word 2 define the size of the program memory block that is protected.

#### 4.4 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 11.5 "User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC16F/LF1826/27/PIC12F/LF1822 Memory Programming Specification" (DS41390).

### 4.5 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See Section 11.5 "User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

### REGISTER 4-3: DEVICEID: DEVICE ID REGISTER<sup>(1)</sup>

| R      | R    | R    | R    | R    | R     |

|--------|------|------|------|------|-------|

| DEV8   | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 13 |      |      |      |      | bit 8 |

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:          |                      |                  |  |

|------------------|----------------------|------------------|--|

| R = Readable bit | '0' = Bit is cleared | '1' = Bit is set |  |

bit 13-5 **DEV<8:0>:** Device ID bits

100111000 = PIC12F1822 100111001 = PIC16F1823 101000000 = PIC12LF1822 101000001 = PIC16LF1823

bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision.

Note 1: This location cannot be written.

TABLE 7-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------------|

| BORCON | SBOREN | _      | _      |        | _      | _      | _      | BORRDY | 74               |

| PCON   | STKOVF | STKUNF | _      | _      | RMCLR  | RI     | POR    | BOR    | 78               |

| STATUS | _      | _      | _      | TO     | PD     | Z      | DC     | С      | 20               |

| WDTCON | _      | _      | WDTPS4 | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 | SWDTEN | 97               |

**Legend:** — = unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

#### 8.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, interrupt-on-change and external INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0 | R-0/0                |

|---------|---------|---------|---------|---------|---------|---------|----------------------|

| GIE     | PEIE    | TMR0IE  | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF <sup>(1)</sup> |

| bit 7   |         |         |         |         |         |         | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

| bit 7 | GIE: Global Interrupt Enable bit                                                                                                                                                              |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Enables all active interrupts</li><li>0 = Disables all interrupts</li></ul>                                                                                                       |

| bit 6 | PEIE: Peripheral Interrupt Enable bit  1 = Enables all active peripheral interrupts  0 = Disables all peripheral interrupts                                                                   |

| bit 5 | <b>TMR0IE:</b> Timer0 Overflow Interrupt Enable bit 1 = Enables the Timer0 interrupt 0 = Disables the Timer0 interrupt                                                                        |

| bit 4 | INTE: INT External Interrupt Enable bit  1 = Enables the INT external interrupt  0 = Disables the INT external interrupt                                                                      |

| bit 3 | IOCIE: Interrupt-on-Change Enable bit  1 = Enables the interrupt-on-change  0 = Disables the interrupt-on-change                                                                              |

| bit 2 | <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed<br>0 = TMR0 register did not overflow                                                                   |

| bit 1 | INTF: INT External Interrupt Flag bit  1 = The INT external interrupt occurred  0 = The INT external interrupt did not occur                                                                  |

| bit 0 | IOCIF: Interrupt-on-Change Interrupt Flag bit <sup>(1)</sup> 1 = When at least one of the interrupt-on-change pins changed state  0 = None of the interrupt-on-change pins have changed state |

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the Interrupt-on-Change flags in the IOCAF register have been cleared by software.

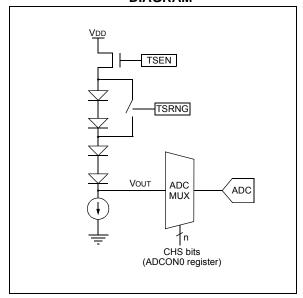

# 15.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between of -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, "Use and Calibration of the Internal Temperature Indicator" (DS01333) for more details regarding the calibration process.

### 15.1 Circuit Operation

Figure 15-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 15-1 describes the output characteristics of the temperature indicator.

### **EQUATION 15-1: VOUT RANGES**

High Range: Vout = VDD - 4VT

Low Range: Vout = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See Section 14.0 "Fixed Voltage Reference (FVR)" for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

FIGURE 15-1: TEMPERATURE CIRCUIT DIAGRAM

# 15.2 Minimum Operating VDD vs. Minimum Sensing Temperature

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 15-1 shows the recommended minimum VDD vs. range setting.

TABLE 15-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

### 15.3 Temperature Output

The output of the circuit is measured using the internal analog to digital converter. A channel is reserved for the temperature circuit output. Refer to Section 16.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

### 15.3.1 ADC ACQUISITION TIME

To ensure accurate temperature measurements, the user must wait at least 200 usec after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200 usec between sequential conversions of the temperature indicator output.

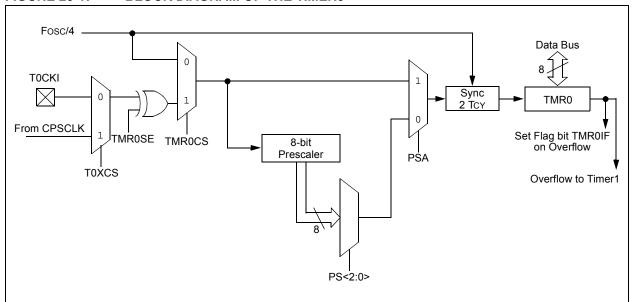

## 20.0 TIMERO MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- · 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- · Programmable external clock edge selection

- · Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 20-1 is a block diagram of the Timer0 module.

### 20.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 20.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note:

The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 20.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSCLK) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter mode using the Capacitive Sensing Oscillator (CPSCLK) signal is selected by setting the TMR0CS bit in the OPTION register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION register.

#### FIGURE 20-1: BLOCK DIAGRAM OF THE TIMER0

TABLE 21-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

| Name    | Bit 7      | Bit 6          | Bit 5      | Bit 4        | Bit 3          | Bit 2     | Bit 1  | Bit 0  | Register on Page |

|---------|------------|----------------|------------|--------------|----------------|-----------|--------|--------|------------------|

| ANSELA  | _          | _              | _          | ANSA4        | _              | ANSA2     | ANSA1  | ANSA0  | 118              |

| CCP1CON | P1M1       | P1M0           | DC1B1      | DC1B0        | CCP1M3         | CCP1M2    | CCP1M1 | CCP1M0 | 213              |

| INTCON  | GIE        | PEIE           | TMR0IE     | INTE         | IOCIE          | TMR0IF    | INTF   | IOCIF  | 86               |

| PIE1    | TMR1GIE    | ADIE           | RCIE       | TXIE         | SSP1IE         | CCP1IE    | TMR2IE | TMR1IE | 87               |

| PIR1    | TMR1GIF    | ADIF           | RCIF       | TXIF         | SSP1IF         | CCP1IF    | TMR2IF | TMR1IF | 89               |

| TMR1H   | Holding Re | gister for the | Most Signi | ficant Byte  | of the 16-bit  | TMR1 Regi | ster   |        | 169*             |

| TMR1L   | Holding Re | gister for the | Least Sign | ificant Byte | of the 16-bit  | TMR1 Reg  | ister  |        | 169*             |

| TRISA   | _          | _              | TRISA5     | TRISA4       | TRISA3         | TRISA2    | TRISA1 | TRISA0 | 117              |

| T1CON   | TMR1CS1    | TMR1CS0        | T1CKPS1    | T1CKPS0      | T10SCEN        | T1SYNC    | 1      | TMR10N | 173              |

| T1GCON  | TMR1GE     | T1GPOL         | T1GTM      | T1GSPM       | T1GGO/<br>DONE | T1GVAL    | T1GSS1 | T1GSS0 | 174              |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: PIC16(L)F1823 only.

<sup>\*</sup> Page provides register information.

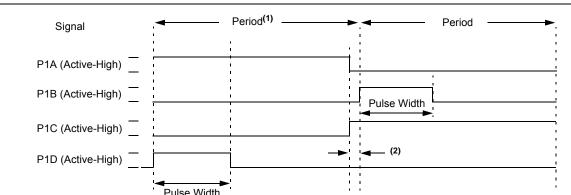

## 24.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the P1M1 bit in the CCP1CON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the P1M1 bit of the CCP1CON register. The following sequence occurs four Timer cycles prior to the end of the current PWM period:

- The modulated outputs (P1B and P1D) are placed in their inactive state.

- The associated unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction

- PWM modulation resumes at the beginning of the next period.

See Figure 24-12 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 24-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output P1A and P1D become inactive, while output P1C becomes active. Since the turn off time of the power devices is longer than the turn on time, a shoot-through current will flow through power devices QC and QD (see Figure 24-10) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

#### FIGURE 24-12: EXAMPLE OF PWM DIRECTION CHANGE

- Note 1: The direction bit P1M1 of the CCP1CON register is written any time during the PWM cycle.

- 2: When changing directions, the P1A and P1C signals switch before the end of the current PWM cycle. The modulated P1B and P1D signals are inactive at this time. The length of this time is four Timer counts.

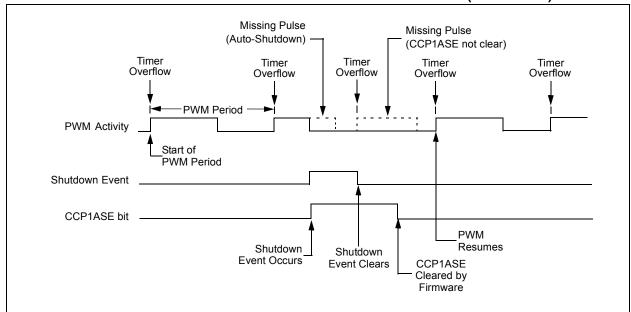

### 24.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCP1AS<2:0> bits of the CCP1AS register. A shutdown event may be generated by:

- A logic '0' on the FLT0 pin

- · A logic '1' on a Comparator (C1) output

A shutdown condition is indicated by the CCP1ASE (Auto-Shutdown Event Status) bit of the CCP1AS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCP1ASE bit is set to '1'. The CCP1ASE will remain set until cleared in firmware or an auto-restart occurs (see **Section 24.4.4 "Auto-Restart Mode"**).

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [P1A/P1C] and [P1B/P1D]. The state of each pin pair is determined by the PSS1AC and PSS1BD bits of the CCP1AS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- · Drive logic '0'

- Tri-state (high-impedance)

- Note 1: The auto-shutdown condition is a levelbased signal, not an edge-based signal. As long as the level is present, the autoshutdown will persist.

- 2: Writing to the CCP1ASE bit is disabled while an auto-shutdown condition persists.

- **3:** Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

- 4: Prior to an auto-shutdown event caused by a comparator output or FLT0 pin event, a software shutdown can be triggered in firmware by setting the CCP1ASE bit of the CCP1AS register to '1'. The autorestart feature tracks the active status of a shutdown caused by a comparator output or FLT0 pin event only. If it is enabled at this time, it will immediately clear this bit and restart the ECCP module at the beginning of the next PWM period.

FIGURE 24-14: PWM AUTO-SHUTDOWN WITH FIRMWARE RESTART (P1RSEN = 0)

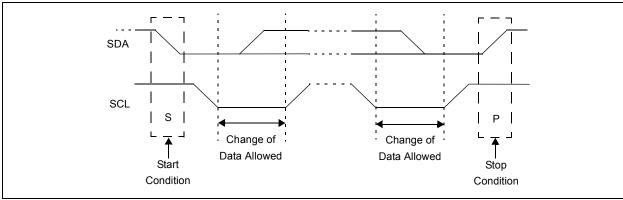

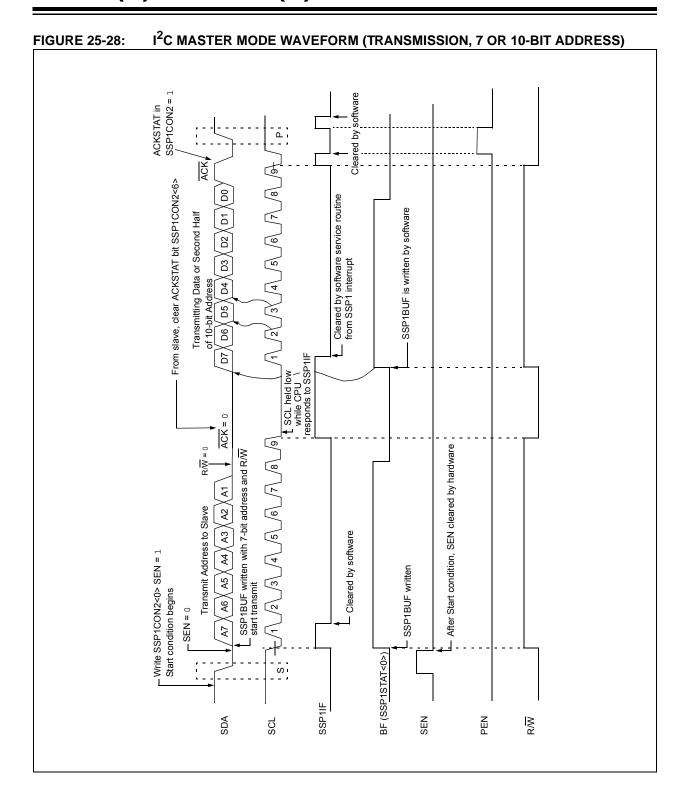

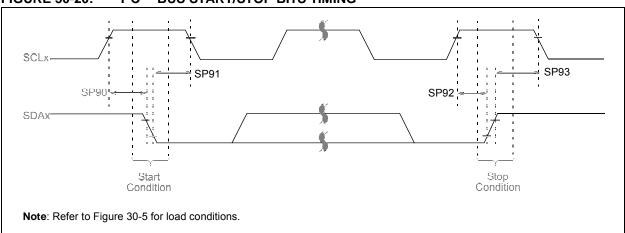

#### 25.4.5 START CONDITION

The I<sup>2</sup>C specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 25-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the I<sup>2</sup>C Specification that states no bus collision can occur on a Start.

#### 25.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

Note: At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low then high again while the SCL line stays high, only the Start condition is detected.

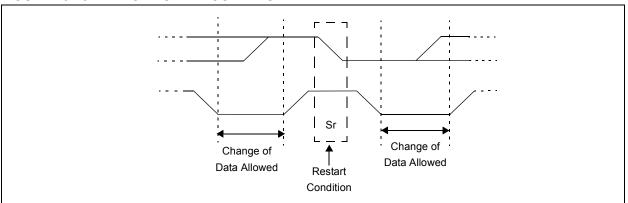

#### 25.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 25-13 shows wave forms for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained. Until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

# 25.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSP1CON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

FIGURE 25-12: I<sup>2</sup>C START AND STOP CONDITIONS

FIGURE 25-13: I<sup>2</sup>C RESTART CONDITION

#### 25.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSP1CON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

### 25.5.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSP1STAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSP1BUF with data to transfer to the master. If the SEN bit of SSP1CON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSP1BUF was read before the ninth falling edge of SCL.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSP1BUF was loaded before the ninth falling edge of SCL. It is now always cleared for read requests.

#### 25.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSP1ADD.

**Note:** Previous versions of the module did not stretch the clock if the second address byte did not match.

#### 25.5.6.3 Byte NACKing

When AHEN bit of SSP1CON3 is set; CKP is cleared by hardware after the eighth falling edge of SCL for a received matching address byte. When DHEN bit of SSP1CON3 is set; CKP is cleared after the eighth falling edge of SCL for received data.

Stretching after the eighth falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

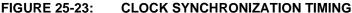

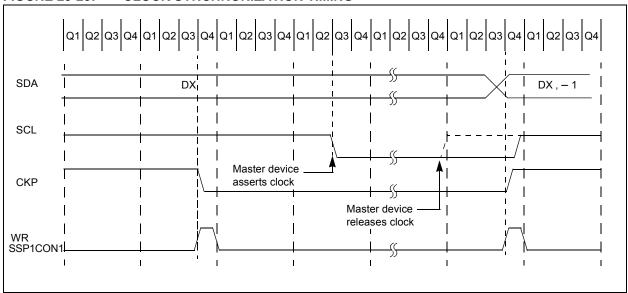

# 25.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external I<sup>2</sup>C master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the I<sup>2</sup>C bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 25-23).

### 25.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception (Figure 25-29) is enabled by programming the Receive Enable bit, RCEN bit of the SSP1CON2 register.

Note: The MSSP1 module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSP1SR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSP1SR are loaded into the SSP1BUF, the BF flag bit is set, the SSP1IF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP1 is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSP1CON2 register.

### 25.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSP1BUF from SSP1SR. It is cleared when the SSP1BUF register is read.

#### 25.6.7.2 SSP1OV Status Flag

In receive operation, the SSP1OV bit is set when eight bits are received into the SSP1SR and the BF flag bit is already set from a previous reception.

#### 25.6.7.3 WCOL Status Flag

If the user writes the SSP1BUF when a receive is already in progress (i.e., SSP1SR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### 25.6.7.4 Typical Receive Sequence:

- The user generates a Start condition by setting the SEN bit of the SSP1CON2 register.

- SSP1IF is set by hardware on completion of the Start.

- 3. SSP1IF is cleared by software.

- User writes SSP1BUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSP1BUF is written to.

- 6. The MSSP1 module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSP1CON2 register.

- The MSSP1 module generates an interrupt at the end of the ninth clock cycle by setting the SSP1IF bit.

- 8. User sets the RCEN bit of the SSP1CON2 register and the Master clocks in a byte from the slave.

- After the eighth falling edge of SCL, SSP1IF and BF are set.

- Master clears SSP1IF and reads the received byte from SSP1UF, clears BF.

- Master sets ACK value sent to slave in ACKDT bit of the SSP1CON2 register and initiates the ACK by setting the ACKEN bit.

- Masters ACK is clocked out to the Slave and SSP1IF is set.

- 13. User clears SSP1IF.

- Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

#### 25.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP1 interrupt is enabled).

#### 25.6.11 EFFECTS OF A RESET

A Reset disables the MSSP1 module and terminates the current transfer.

#### 25.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP1 module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSP1STAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

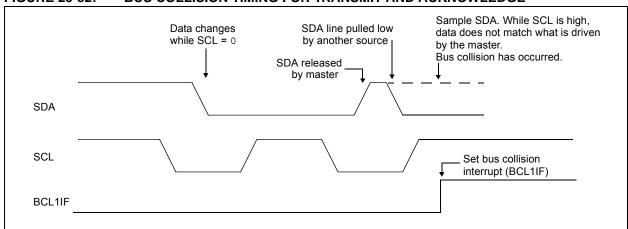

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCL1IF bit.

The states where arbitration can be lost are:

- · Address Transfer

- · Data Transfer

- · A Start Condition

- · A Repeated Start Condition

- An Acknowledge Condition

### 25.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCL1IF, and reset the I<sup>2</sup>C port to its Idle state (Figure 25-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSP1BUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $\rm I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSP1CON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSP1IF bit will be set.

A write to the SSP1BUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the I<sup>2</sup>C bus can be taken when the P bit is set in the SSP1STAT register, or the bus is Idle and the S and P bits are cleared.

**TABLE 26-3: BAUD RATE FORMULAS**

| Configuration Bits |       |      | DDC/FUCADT Mada     | Baud Rate Formula |  |  |

|--------------------|-------|------|---------------------|-------------------|--|--|

| SYNC               | BRG16 | BRGH | BRG/EUSART Mode     | Baud Rate Formula |  |  |

| 0                  | 0     | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |  |  |

| 0                  | 0     | 1    | 8-bit/Asynchronous  | F000//40 (n.14)]  |  |  |

| 0                  | 1     | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |  |  |

| 0                  | 1     | 1    | 16-bit/Asynchronous |                   |  |  |

| 1                  | 0     | х    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |  |  |

| 1                  | 1     | х    | 16-bit/Synchronous  |                   |  |  |

**Legend:** x = Don't care, n = value of SPBRGH, SPBRGL register pair.

TABLE 26-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register on Page |

|---------|-----------|-------|-------|-------|-------|-------|-------|-------|------------------|

| BAUDCON | ABDOVF    | RCIDL | _     | SCKP  | BRG16 | _     | WUE   | ABDEN | 279              |

| RCSTA   | SPEN      | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 278              |

| SPBRGL  | BRG<7:0>  |       |       |       |       |       |       |       | 280*             |

| SPBRGH  | BRG<15:8> |       |       |       |       |       |       | 280*  |                  |

| TXSTA   | CSRC      | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 277              |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

<sup>\*</sup> Page provides register information.

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                    |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                     |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |  |  |  |  |

| Status Affected: | None                                                                                                                                                                   |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |  |  |  |  |

| TRIS             | Load TRIS Register with W                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] TRIS f                                                                                                                         |

| Operands:        | $5 \leq f \leq 7$                                                                                                                        |

| Operation:       | $(W) \rightarrow TRIS$ register 'f'                                                                                                      |

| Status Affected: | None                                                                                                                                     |

| Description:     | Move data from W register to TRIS register. When 'f' = 5, TRISA is loaded. When 'f' = 6, TRISB is loaded. When 'f' = 7, TRISC is loaded. |

| XORLW            | Exclusive OR literal with W                                                                                   |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] XORLW k                                                                                             |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                 |  |  |  |  |  |

| Status Affected: | Z                                                                                                             |  |  |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] XORWF f,d                                                                                                                                                             |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

**TABLE 30-14: SPI MODE REQUIREMENTS**

| Param<br>No. | Symbol                | Characteristic                            | Min.        | Тур†     | Max. | Units | Conditions |  |

|--------------|-----------------------|-------------------------------------------|-------------|----------|------|-------|------------|--|

| SP70*        | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↓ or SCKx ↑ input           | 2.25 TcY    | _        | _    | ns    |            |  |

| SP71*        | TscH                  | SCKx input high time (Slave mod           | de)         | Tcy + 20 | _    | _     | ns         |  |

| SP72*        | TscL                  | SCKx input low time (Slave mod            | e)          | Tcy + 20 |      | _     | ns         |  |

| SP73*        | TDIV2scH,<br>TDIV2scL | Setup time of SDIx data input to          | 100         | _        | _    | ns    |            |  |

| SP74*        | TscH2DIL,<br>TscL2DIL | Hold time of SDIx data input to S         | 100         | _        | _    | ns    |            |  |

| SP75* TDOR   |                       | SDO data output rise time                 | 3.0-5.5V    | _        | 10   | 25    | ns         |  |

|              |                       |                                           | 1.8-5.5V    | _        | 25   | 50    | ns         |  |

| SP76*        | TDOF                  | SDOx data output fall time                |             | _        | 10   | 25    | ns         |  |

| SP77*        | TssH2DoZ              | SSx <sup>↑</sup> to SDOx output high-impe | 10          | _        | 50   | ns    |            |  |

| SP78* TscR   | SCKx output rise time | 3.0-5.5V                                  | _           | 10       | 25   | ns    |            |  |

|              |                       | (Master mode)                             | 1.8-5.5V    | _        | 25   | 50    | ns         |  |

| SP79*        | TscF                  | SCKx output fall time (Master mo          | ode)        | _        | 10   | 25    | ns         |  |

| SP80*        | TscH2DoV,             | cH2DOV, SDOx data output valid after      | 3.0-5.5V    | _        | _    | 50    | ns         |  |

|              | TscL2DoV              | SCKx edge                                 | 1.8-5.5V    | _        | _    | 145   | ns         |  |

| SP81*        | TDOV2scH,<br>TDOV2scL | SDOx data output setup to SCK             | Tcy         | _        | _    | ns    |            |  |

| SP82*        | TssL2DoV              | SDOx data output valid after SS           | _           | _        | 50   | ns    |            |  |

| SP83*        | TscH2ssH,<br>TscL2ssH | SSx ↑ after SCKx edge                     | 1.5Tcy + 40 | _        | _    | ns    |            |  |

<sup>\*</sup> These parameters are characterized but not tested.

FIGURE 30-20: I<sup>2</sup>C™ BUS START/STOP BITS TIMING

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

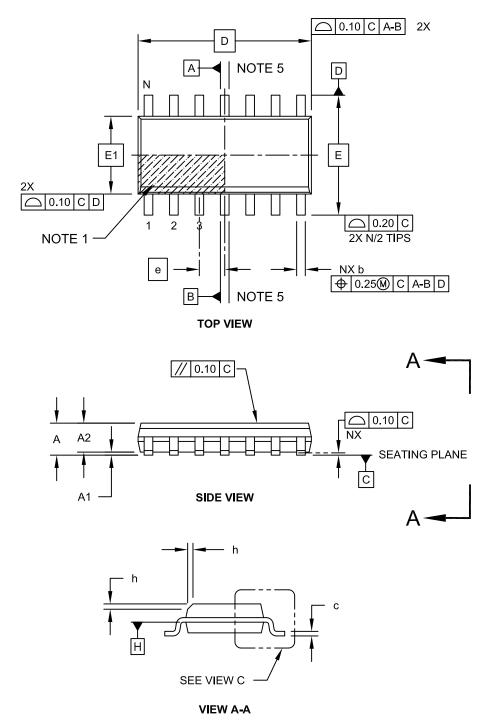

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-065C Sheet 1 of 2