### Microchip Technology - PIC16LF1823-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

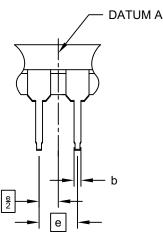

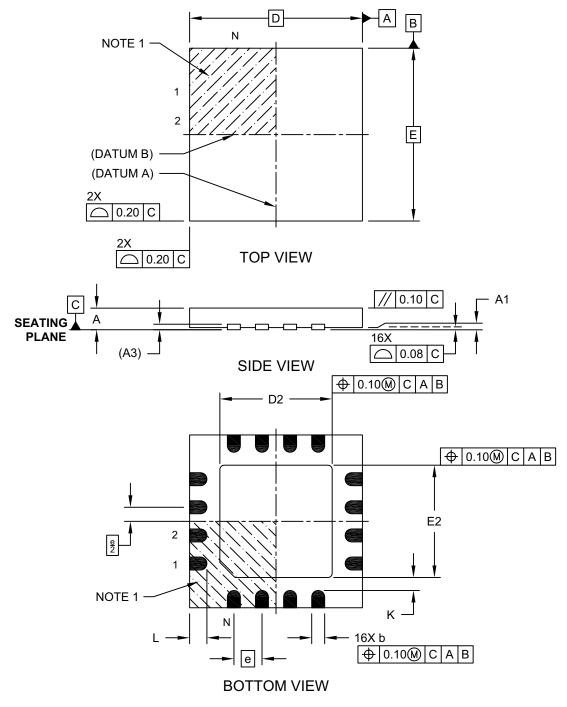

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1823-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

The PIC12(L)F1822/16(L)F1823 are described within this data sheet. They are available in 8/14 pin packages. Figure 1-1 shows a block diagram of the PIC12(L)F1822/16(L)F1823 devices. Tables 1-2 and 1-3 show the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral               |             | PIC12(L)F1822 | PIC16(L)F1823 |

|--------------------------|-------------|---------------|---------------|

| ADC                      |             | ٠             | •             |

| Capacitive Sensing (CP   | S) Module   | •             | •             |

| Data EEPROM              |             | ٠             | •             |

| Digital-to-Analog Conve  | rter (DAC)  | ٠             | •             |

| Digital Signal Modulator | · (DSM)     | ٠             | •             |

| EUSART                   | •           | •             |               |

| Fixed Voltage Reference  | e (FVR)     | ٠             | •             |

| SR Latch                 |             | •             | •             |

| Capture/Compare/PWM      | Modules     |               |               |

|                          | ECCP1       | •             | •             |

| Comparators              |             |               |               |

|                          | C1          | •             | •             |

|                          | C2          |               | •             |

| Master Synchronous Se    | erial Ports |               |               |

|                          | MSSP        | ٠             | •             |

| Timers                   |             |               |               |

|                          | Timer0      | •             | •             |

|                          | Timer1      | •             | •             |

|                          | Timer2      | ٠             | •             |

# TABLE 3-3:PIC12(L)F1822/16(L)F1823 MEMORY MAP, BANKS 0-7

| IADL         |                      | 012(         |                       | -)1 10       |                        |              |                       |              |                       |              |                       |       |                       |      |                       |

|--------------|----------------------|--------------|-----------------------|--------------|------------------------|--------------|-----------------------|--------------|-----------------------|--------------|-----------------------|-------|-----------------------|------|-----------------------|

|              | BANK 0               |              | BANK 1                |              | BANK 2                 |              | BANK 3                |              | BANK 4                |              | BANK 5                |       | BANK 6                |      | BANK 7                |

| 000h         | INDF0                | 080h         | INDF0                 | 100h         | INDF0                  | 180h         | INDF0                 | 200h         | INDF0                 | 280h         | INDF0                 | 300h  | INDF0                 | 380h | INDF0                 |

| 001h         | INDF1                | 081h         | INDF1                 | 101h         | INDF1                  | 181h         | INDF1                 | 201h         | INDF1                 | 281h         | INDF1                 | 301h  | INDF1                 | 381h | INDF1                 |

| 002h         | PCL                  | 082h         | PCL                   | 102h         | PCL                    | 182h         | PCL                   | 202h         | PCL                   | 282h         | PCL                   | 302h  | PCL                   | 382h | PCL                   |

| 003h         | STATUS               | 083h         | STATUS                | 103h         | STATUS                 | 183h         | STATUS                | 203h         | STATUS                | 283h         | STATUS                | 303h  | STATUS                | 383h | STATUS                |

| 004h         | FSR0L                | 084h         | FSR0L                 | 104h         | FSR0L                  | 184h         | FSR0L                 | 204h         | FSR0L                 | 284h         | FSR0L                 | 304h  | FSR0L                 | 384h | FSR0L                 |

| 005h         | FSR0H                | 085h         | FSR0H                 | 105h         | FSR0H                  | 185h         | FSR0H                 | 205h         | FSR0H                 | 285h         | FSR0H                 | 305h  | FSR0H                 | 385h | FSR0H                 |

| 006h         | FSR1L                | 086h         | FSR1L                 | 106h         | FSR1L                  | 186h         | FSR1L                 | 206h         | FSR1L                 | 286h         | FSR1L                 | 306h  | FSR1L                 | 386h | FSR1L                 |

| 007h         | FSR1H                | 087h         | FSR1H                 | 107h         | FSR1H                  | 187h         | FSR1H                 | 207h         | FSR1H                 | 287h         | FSR1H                 | 307h  | FSR1H                 | 387h | FSR1H                 |

| 008h         | BSR                  | 088h         | BSR                   | 108h         | BSR                    | 188h         | BSR                   | 208h         | BSR                   | 288h         | BSR                   | 308h  | BSR                   | 388h | BSR                   |

| 009h         | WREG                 | 089h         | WREG                  | 109h         | WREG                   | 189h         | WREG                  | 209h         | WREG                  | 289h         | WREG                  | 309h  | WREG                  | 389h | WREG                  |

| 00Ah         | PCLATH               | 08Ah         | PCLATH                | 10Ah         | PCLATH                 | 18Ah         | PCLATH                | 20Ah         | PCLATH                | 28Ah         | PCLATH                | 30Ah  | PCLATH                | 38Ah | PCLATH                |

| 00Bh         | INTCON               | 08Bh         | INTCON                | 10Bh         | INTCON                 | 18Bh         | INTCON                | 20Bh         | INTCON                | 28Bh         | INTCON                | 30Bh  | INTCON                | 38Bh | INTCON                |

| 00Ch         | PORTA                | 08Ch         | TRISA                 | 10Ch         | LATA                   | 18Ch         | ANSELA                | 20Ch         | WPUA                  | 28Ch         | —                     | 30Ch  | —                     | 38Ch | —                     |

| 00Dh         | —                    | 08Dh         | _                     | 10Dh         | _                      | 18Dh         |                       | 20Dh         | _                     | 28Dh         | —                     | 30Dh  | —                     | 38Dh | —                     |

| 00Eh         | PORTC <sup>(1)</sup> | 08Eh         | TRISC <sup>(1)</sup>  | 10Eh         | LATC <sup>(1)</sup>    | 18Eh         | ANSELC <sup>(1)</sup> | 20Eh         | WPUC <sup>(1)</sup>   | 28Eh         | —                     | 30Eh  | —                     | 38Eh | —                     |

| 00Fh         | —                    | 08Fh         | —                     | 10Fh         | —                      | 18Fh         | —                     | 20Fh         | —                     | 28Fh         | —                     | 30Fh  | —                     | 38Fh | —                     |

| 010h         | _                    | 090h         | —                     | 110h         | —                      | 190h         | —                     | 210h         | —                     | 290h         | —                     | 310h  | —                     | 390h | —                     |

| 011h         | PIR1                 | 091h         | PIE1                  | 111h         | CM1CON0                | 191h         | EEADRL                | 211h         | SSP1BUF               | 291h         | CCPR1L                | 311h  | —                     | 391h | IOCAP                 |

| 012h         | PIR2                 | 092h         | PIE2                  | 112h         | CM1CON1                | 192h         | EEADRH                | 212h         | SSP1ADD               | 292h         | CCPR1H                | 312h  | —                     | 392h | IOCAN                 |

| 013h         | —                    | 093h         | —                     | 113h         | CM2CON0 <sup>(1)</sup> | 193h         | EEDATL                | 213h         | SSP1MASK              | 293h         | CCP1CON               | 313h  | —                     | 393h | IOCAF                 |

| 014h         | —                    | 094h         | —                     | 114h         | CM2CON1 <sup>(1)</sup> | 194h         | EEDATH                | 214h         | SSP1STAT              | 294h         | PWM1CON               | 314h  | —                     | 394h | —                     |

| 015h         | TMR0                 | 095h         | OPTION                | 115h         | CMOUT                  | 195h         | EECON1                | 215h         | SSP1CON1              | 295h         | CCP1AS                | 315h  | —                     | 395h | _                     |

| 016h         | TMR1L                | 096h         | PCON                  | 116h         | BORCON                 | 196h         | EECON2                | 216h         | SSP1CON2              | 296h         | PSTR1CON              | 316h  | -                     | 396h | —                     |

| 017h         | TMR1H                | 097h         | WDTCON                | 117h         | FVRCON                 | 197h         |                       | 217h         | SSP1CON3              | 297h         | —                     | 317h  | —                     | 397h | —                     |

| 018h         | T1CON                | 098h         | OSCTUNE               | 118h         | DACCON0                | 198h         |                       | 218h         | _                     | 298h         | _                     | 318h  | —                     | 398h | —                     |

| 019h         | T1GCON               | 099h         | OSCCON                | 119h         | DACCON1                | 199h         | RCREG                 | 219h         | -                     | 299h         | —                     | 319h  | —                     | 399h | —                     |

| 01Ah         | TMR2                 | 09Ah         | OSCSTAT               | 11Ah         | SRCON0                 | 19Ah         | TXREG                 | 21Ah         | —                     | 29Ah         | —                     | 31Ah  | —                     | 39Ah | CLKRCON               |

| 01Bh         | PR2                  | 09Bh         | ADRESL                | 11Bh         | SRCON1                 | 19Bh         | SPBRGL                | 21Bh         | _                     | 29Bh         | —                     | 31Bh  | —                     | 39Bh | —                     |

| 01Ch         | T2CON                | 09Ch         | ADRESH                | 11Ch         | —                      | 19Ch         | SPBRGH                | 21Ch         | _                     | 29Ch         | _                     | 31Ch  | —                     | 39Ch | MDCON                 |

| 01Dh         | _                    | 09Dh         | ADCON0                | 11Dh         | APFCON                 | 19Dh         | RCSTA                 | 21Dh         | _                     | 29Dh         | _                     | 31Dh  | —                     | 39Dh | MDSRC                 |

| 01Eh         | CPSCON0              | 09Eh         | ADCON1                | 11Eh         | _                      | 19Eh         | TXSTA                 | 21Eh         | -                     | 29Eh         | —                     | 31Eh  | —                     | 39Eh | MDCARL                |

| 01Fh         | CPSCON1              | 09Fh         | —                     | 11Fh         | —                      | 19Fh         | BAUDCON               | 21Fh         | _                     | 29Fh         | —                     | 31Fh  | —                     | 39Fh | MDCARH                |

| 020h         |                      | 0A0h         | General               | 120h         |                        | 1A0h         |                       | 220h         |                       | 2A0h         |                       | 320h  |                       | 3A0h |                       |

|              | General              |              | Purpose               |              |                        |              |                       |              |                       |              |                       |       |                       |      |                       |

|              | Purpose              | 0BFh         | Register              |              | Unimplemented          |              | Unimplemented         |              | Unimplemented         |              | Unimplemented         |       | Unimplemented         |      | Unimplemented         |

|              | Register             | 0CFh         | 32 Bytes              |              | Read as '0'            |              | Read as '0'           |              | Read as '0'           |              | Read as '0'           |       | Read as '0'           |      | Read as '0'           |

|              | 80 Bytes             | UCFII        | Unimplemented         |              |                        |              |                       |              |                       |              |                       |       |                       |      |                       |

|              | -                    |              | Read as '0'           |              |                        |              |                       |              |                       |              |                       | 36Fh  |                       | 3EFh |                       |

| 06Fh<br>070h |                      | 0EFh<br>0F0h |                       | 16Fh<br>170h |                        | 1EFh<br>1F0h |                       | 26Fh<br>270h |                       | 2EFh<br>2F0h |                       | 370h  |                       | 3EFI |                       |

| 07011        |                      | UFUN         | A                     | 1700         | A                      | IFUN         | A                     | 2700         | A                     | 2500         | A                     | 3/0/1 | A                     | 3500 | A                     |

|              | Common RAM           |              | Accesses<br>70h – 7Fh |              | Accesses<br>70h – 7Fh  |              | Accesses<br>70h – 7Fh |              | Accesses<br>70h – 7Fh |              | Accesses<br>70h – 7Fh |       | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |

| 075          |                      |              | 7011 - 7111           | 4751         | 7011 - 7111            | 455          | 7011-7111             | 075          |                       | 055          |                       | 075   | 7011-7111             |      | 7011-7111             |

| 07Fh         |                      | 0FFh         |                       | 17Fh         |                        | 1FFh         |                       | 27Fh         |                       | 2FFh         |                       | 37Fh  |                       | 3FFh |                       |

**Legend:** = Unimplemented data memory locations, read as '0'.

Note 1: Available only on PIC16(L)F1823.

| Address             | Name                 | Bit 7                         | Bit 6               | Bit 5             | Bit 4           | Bit 3                   | Bit 2                | Bit 1  | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------------------|----------------------|-------------------------------|---------------------|-------------------|-----------------|-------------------------|----------------------|--------|---------|----------------------|---------------------------------|

| Bank 0              | Bank 0               |                               |                     |                   |                 |                         |                      |        |         |                      |                                 |

| 000h <sup>(1)</sup> | INDF0                | Addressing the (not a physic) |                     | es contents of    | FSR0H/FSR0      | L to address            | data memory          | /      |         | XXXX XXXX            | XXXX XXXX                       |

| 001h <sup>(1)</sup> | INDF1                | Addressing the (not a physic) |                     | es contents of    | FSR1H/FSR1      | L to address            | data memory          | /      |         | XXXX XXXX            | XXXX XXXX                       |

| 002h <sup>(1)</sup> | PCL                  | Program Cou                   | inter (PC) Lea      | st Significant E  | Byte            |                         |                      |        |         | 0000 0000            | 0000 0000                       |

| 003h <sup>(1)</sup> | STATUS               | _                             | —                   | —                 | TO              | PD                      | Z                    | DC     | С       | 1 1000               | q quuu                          |

| 004h <sup>(1)</sup> | FSR0L                | Indirect Data                 | Memory Addr         | ess 0 Low Poir    | nter            |                         |                      |        |         | 0000 0000            | uuuu uuuu                       |

| 005h <sup>(1)</sup> | FSR0H                | Indirect Data                 | Memory Addr         | ess 0 High Poi    | nter            |                         |                      |        |         | 0000 0000            | 0000 0000                       |

| 006h <sup>(1)</sup> | FSR1L                | Indirect Data                 | Memory Addr         | ess 1 Low Poir    | nter            |                         |                      |        |         | 0000 0000            | uuuu uuuu                       |

| 007h <sup>(1)</sup> | FSR1H                | Indirect Data                 | Memory Addr         | ess 1 High Poi    | nter            |                         |                      |        |         | 0000 0000            | 0000 0000                       |

| 008h <sup>(1)</sup> | BSR                  | _                             | —                   | —                 |                 |                         | BSR<4:0>             |        |         | 0 0000               | 0 0000                          |

| 009h <sup>(1)</sup> | WREG                 | Working Reg                   | ister               | •                 | •               |                         |                      |        |         | 0000 0000            | uuuu uuuu                       |

| 00Ah <sup>(1)</sup> | PCLATH               | _                             | Write Buffer f      | or the upper 7    | bits of the Pro | ogram Counte            | er                   |        |         | -000 0000            | -000 0000                       |

| 00Bh <sup>(1)</sup> | INTCON               | GIE                           | PEIE                | TMR0IE            | INTE            | IOCIE                   | TMR0IF               | INTF   | IOCIF   | 0000 000x            | 0000 000u                       |

| 00Ch                | PORTA                | _                             | _                   | RA5               | RA4             | RA3                     | RA2                  | RA1    | RA0     | xx xxxx              | xx xxxx                         |

| 00Dh                | —                    | Unimplement                   | ted                 | •                 | •               | •                       | •                    |        | •       | _                    | _                               |

| 00Eh                | PORTC <sup>(2)</sup> | _                             | _                   | RC5               | RC4             | RC3                     | RC2                  | RC1    | RC0     | xx xxxx              | xx xxxx                         |

| 00Fh                | —                    | Unimplement                   | ted                 | •                 | •               | •                       | •                    |        | •       | _                    | _                               |

| 010h                | _                    | Unimplement                   | ted                 |                   |                 |                         |                      |        |         | _                    | _                               |

| 011h                | PIR1                 | TMR1GIF                       | ADIF                | RCIF              | TXIF            | SSP1IF                  | CCP1IF               | TMR2IF | TMR1IF  | 0000 0000            | 0000 0000                       |

| 012h                | PIR2                 | OSFIF                         | C2IF <sup>(2)</sup> | C1IF              | EEIF            | BCL1IF                  | _                    | _      | _       | 0000 0               | 0000 0                          |

| 013h                | —                    | Unimplement                   | ted                 |                   |                 |                         |                      |        |         | _                    | _                               |

| 014h                | —                    | Unimplement                   | ted                 |                   |                 |                         |                      |        |         | _                    | _                               |

| 015h                | TMR0                 | Timer0 Modu                   | le Register         |                   |                 |                         |                      |        |         | xxxx xxxx            | uuuu uuuu                       |

| 016h                | TMR1L                | Holding Regi                  | ster for the Le     | ast Significant   | Byte of the 16  | 5-bit TMR1 Re           | egister              |        |         | xxxx xxxx            | uuuu uuuu                       |

| 017h                | TMR1H                | Holding Regi                  | ster for the Mo     | ost Significant I | Byte of the 16  | -bit TMR1 Re            | gister               |        |         | xxxx xxxx            | uuuu uuuu                       |

| 018h                | T1CON                | TMR1CS1                       | TMR1CS0             | T1CKP             | S<1:0>          | T1OSCEN                 | T1SYNC               | _      | TMR10N  | 0000 00-0            | uuuu uu-u                       |

| 019h                | T1GCON               | TMR1GE                        | T1GPOL              | T1GTM             | T1GSPM          | T <u>1GGO</u> /<br>DONE | T1GVAL               | T1GS   | S<1:0>  | 0000 0x00            | uuuu uxuu                       |

| 01Ah                | TMR2                 | Timer2 Modu                   | le Register         |                   |                 |                         |                      |        |         | 0000 0000            | 0000 0000                       |

| 01Bh                | PR2                  | Timer2 Perio                  | d Register          |                   |                 |                         |                      |        |         | 1111 1111            | 1111 1111                       |

| 01Ch                | T2CON                | _                             |                     | T2OUTF            | °S<3:0>         |                         | TMR2ON               | T2CK   | PS<1:0> | -000 0000            | -000 0000                       |

| 01Dh                | —                    | Unimplement                   | ted                 |                   |                 |                         |                      |        |         | —                    | _                               |

| 01Eh                | CPSCON0              | CPSON                         | CPSRM               | _                 | _               | CPSRN                   | G<1:0>               | CPSOUT | T0XCS   | 00 0000              | 00 0000                         |

| 01Fh                | CPSCON1              |                               | _                   | _                 | _               | CPSCH                   | <3:2> <sup>(2)</sup> | CPSC   | :H<1:0> | 0000                 | 0000                            |

#### TABLE 3-8: SPECIAL FUNCTION REGISTER SUMMARY

$\label{eq:legend: Legend: Legend: u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.$

1: These registers can be addressed from any bank.

2: PIC16(L)F1823 only.

Note

**3:** Unimplemented. Read as '1'.

4: PIC12(L)F1822 only.

# 5.6 Oscillator Control Registers

#### REGISTER 5-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0/              | /0 R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-1/1                                                                                                                                                                                     | R/W-1/1                               | R/W-1/1         | U-0               | R/W-0/0         | R/W-0/0      |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|-------------------|-----------------|--------------|--|

| SPLLE               | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IRCF                                                                                                                                                                                        | <3:0>                                 |                 | _                 | SCS             | <1:0>        |  |

| bit 7               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                             |                                       |                 |                   |                 | bit 0        |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                             |                                       |                 |                   |                 |              |  |

| Legend:<br>R = Read | abla bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | W = Writabla                                                                                                                                                                                | hit                                   | LI – Unimpion   | contod hit roa    |                 |              |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                |                                       | U = Unimplen    |                   |                 | athar Daaata |  |

|                     | unchanged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | x = Bit is unki                                                                                                                                                                             |                                       | -n/n = value a  | IT POR and B      | OR/Value at all | other Resets |  |

| '1' = Bit is        | set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is cle                                                                                                                                                                            | areo                                  |                 |                   |                 |              |  |

| bit 7               | <u>If PLLEN in (</u><br>SPLLEN bit<br><u>If PLLEN in (</u><br>1 = 4x PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Configuration W                                                                                                                                                                             | /ord 1 = <u>1:</u><br>/LL is always e | nabled (subject | : to oscillator r | requirements)   |              |  |

| bit 6-3             | $0 = 4x PLL \text{ is disabled}$ bit 6-3 $IRCF<3:0>: Internal Oscillator Frequency Select bits$ $000x = 31 \text{ kHz LF}$ $0010 = 31.25 \text{ kHz MF}$ $0011 = 31.25 \text{ kHz MF}$ $0101 = 62.5 \text{ kHz MF}$ $0101 = 125 \text{ kHz MF}$ $0110 = 250 \text{ kHz MF}$ $0111 = 500 \text{ kHz MF} (default upon Reset)$ $1000 = 125 \text{ kHz HF}^{(1)}$ $1001 = 250 \text{ kHz HF}^{(1)}$ $1001 = 250 \text{ kHz HF}^{(1)}$ $1010 = 500 \text{ kHz HF}^{(1)}$ $1011 = 1 \text{ MHz HF}$ $1100 = 2 \text{ MHz HF}$ $1101 = 4 \text{ MHz HF}$ $1100 = 8 \text{ MHz or 32 MHz HF}(see Section 5.2.2.1 "HFINTOSC")$ |                                                                                                                                                                                             |                                       |                 |                   |                 |              |  |

| bit 2<br>bit 1-0    | <b>SCS&lt;1:0&gt;:</b> \$<br>1x = Interna<br>01 = Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Unimplemented: Read as '0'<br>SCS<1:0>: System Clock Select bits<br>1x = Internal oscillator block<br>01 = Timer1 oscillator<br>00 = Clock determined by FOSC<2:0> in Configuration Word 1. |                                       |                 |                   |                 |              |  |

| Note 1:             | Duplicate frequency derived from HFINTOSC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                             |                                       |                 |                   |                 |              |  |

Note 1: Duplicate frequency derived from HFINTOSC.

#### EXAMPLE 11-2: DATA EEPROM WRITE

|                      | MOVWF<br>MOVLW<br>MOVWF             | DATA_EE_ADDR<br>EEADRL<br>DATA_EE_DATA<br>EEDATL<br>EECON1, CFGS | ;Data Memory Address to write<br>;<br>;Data Memory Value to write<br>;Deselect Configuration space<br>;Point to DATA memory |

|----------------------|-------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Required<br>Sequence | MOVLW<br>MOVWF<br>BSF<br>BSF<br>BCF | EECON2<br>OAAh<br>EECON2<br>EECON1, WR<br>INTCON, GIE            | ;<br>;Write 55h<br>;<br>;Write AAh<br>;Set WR bit to begin write<br>;Enable Interrupts<br>;Disable writes                   |

|                              | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4              | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    |

|------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------|--------------------------------|--------------------------------|

| Flash ADDR                   | <br>{                          | PC + 1                         | EEADRH,EEADRL                  | PC + 3                   | PC + 4                         | PC + 5                         |

| Flash Data                   |                                | STR (PC) INST                  | R (PC + 1) EEDA                |                          | R (PC + 3) INST                | R (PC + 4)                     |

|                              | INSTR(PC - 1)<br>executed here | BSF EECON1,RD<br>executed here | INSTR(PC + 1)<br>executed here | Forced NOP executed here | INSTR(PC + 3)<br>executed here | INSTR(PC + 4)<br>executed here |

| RD bit                       | <br>                           | <br>                           | /                              |                          | <br>                           |                                |

| EEDATH<br>EEDATL<br>Register | <br>                           |                                |                                | Χ                        |                                |                                |

| EERHLT                       | <br> <br>                      | <br> <br>                      |                                |                          | <br>  <br>                     |                                |

#### EXAMPLE 11-5: WRITING TO FLASH PROGRAM MEMORY

| ; This               | write rout  | ine assumes the f             | following:                                                 |

|----------------------|-------------|-------------------------------|------------------------------------------------------------|

| ; 1. Tł              | ne 16 bytes | of data are load              | led, starting at the address in DATA_ADDR                  |

|                      | _           |                               | ten is made up of two adjacent bytes in DATA_ADDR,         |

|                      |             | ttle endian forma             |                                                            |

|                      |             |                               | e least significant bits = 000) is loaded in ADDRH:ADDRL   |

|                      |             |                               | in shared data memory 0x70 - 0x7F                          |

| ;                    |             | Did die 100d00d               |                                                            |

|                      | BCF         | INTCON, GIE                   | ; Disable ints so required sequences will execute properly |

|                      | BANKSEL     | EEADRH                        | ; Bank 3                                                   |

|                      | MOVF        | ADDRH,W                       | ; Load initial address                                     |

|                      | MOVWF       | EEADRH                        | i                                                          |

|                      | MOVF        | ADDRL,W                       | ;                                                          |

|                      | MOVWF       | EEADRL                        | :                                                          |

|                      | MOVLW       |                               | ; Load initial data address                                |

|                      | MOVWF       | FSROL                         | :                                                          |

|                      | MOVLW       |                               | ,<br>; Load initial data address                           |

|                      | MOVEW       | FSR0H                         | :                                                          |

|                      | BSF         | EECON1,EEPGD                  | ; Point to program memory                                  |

|                      | BCF         | EECON1, EEFGD<br>EECON1, CFGS |                                                            |

|                      |             |                               | ; Enable writes                                            |

|                      | BSF         | EECON1, WREN                  |                                                            |

| T OOD                | BSF         | EECON1,LWLO                   | ; Only Load Write Latches                                  |

| LOOP                 | MONTRA      | ECDO                          | . Lood first data buta into locar                          |

|                      | MOVIW       | FSR0++                        | ; Load first data byte into lower                          |

|                      | MOVWF       | EEDATL                        | ;                                                          |

|                      | MOVIW       | FSR0++                        | ; Load second data byte into upper                         |

|                      | MOVWF       | EEDATH                        | ;                                                          |

|                      | MOUTE       |                               |                                                            |

|                      | MOVF        | EEADRL,W                      | ; Check if lower bits of address are '000'                 |

|                      | XORLW       | 0x07                          | ; Check if we're on the last of 8 addresses                |

|                      | ANDLW       | 0x07                          |                                                            |

|                      | BTFSC       | STATUS,Z                      | ; Exit if last of eight words,                             |

|                      | GOTO        | START_WRITE                   | ;                                                          |

|                      |             | 1                             |                                                            |

|                      | MOVLW       | 55h                           | ; Start of required write sequence:                        |

|                      | MOVWF       | EECON2                        | ; Write 55h                                                |

| Required<br>Sequence | MOVLW       | 0AAh                          | ;                                                          |

| uire<br>Jer          | MOVWF       | EECON2                        | ; Write AAh                                                |

| ed                   | BSF         | EECON1,WR                     | ; Set WR bit to begin write                                |

| шw                   | NOP         |                               | ; Any instructions here are ignored as processor           |

|                      | NOD         |                               | ; halts to begin write sequence                            |

|                      | NOP         |                               | ; Processor will stop here and wait for write to complete. |

|                      |             |                               | · Réten mite more sentimer with Jud instanction            |

|                      |             |                               | ; After write processor continues with 3rd instruction.    |

|                      |             |                               |                                                            |

|                      | INCF        | EEADRL,F                      | ; Still loading latches Increment address                  |

|                      | GOTO        | LOOP                          | ; Write next latches                                       |

|                      |             |                               |                                                            |

| START_V              |             | EECON1 THTO                   | · No more loading latabag . Naturally start Black war      |

|                      | BCF         | EECON1,LWLO                   | ; No more loading latches - Actually start Flash program   |

|                      |             |                               | ; memory write                                             |

|                      | MONTES      | <b>F F b</b>                  | · Otaut of nominal and to compare                          |

|                      | MOVLW       | 55h                           | ; Start of required write sequence:                        |

| (N                   | MOVWF       | EECON2                        | ; Write 55h                                                |

| nce                  | MOVLW       | 0AAh                          | ; . Their and                                              |

| Required<br>Sequence | MOVWF       | EECON2                        | ; Write AAh                                                |

| Rec                  | BSF         | EECON1,WR                     | ; Set WR bit to begin write                                |

| - 0                  | NOP         |                               | ; Any instructions here are ignored as processor           |

|                      | NOD         |                               | ; halts to begin write sequence                            |

|                      | NOP         |                               | ; Processor will stop here and wait for write complete.    |

|                      |             |                               |                                                            |

|                      | DCE         | 550011 ····                   | ; after write processor continues with 3rd instruction     |

|                      | BCF         | EECON1, WREN                  | ; Disable writes                                           |

|                      | BSF         | INTCON,GIE                    | ; Enable interrupts                                        |

|                      |             |                               |                                                            |

## 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 16.2.6 "A/D Conver-     |

|       | sion Procedure".                         |

#### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- · Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device                   | CCP1/ECCP1 |

|--------------------------|------------|

| PIC12(L)F1822/16(L)F1823 | CCP1       |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 24.0 "Capture/Compare/PWM Modules" for more information.

#### 24.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

### 24.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name                 | Bit 7                                                                       | Bit 6               | Bit 5          | Bit 4           | Bit 3            | Bit 2   | Bit 1                 | Bit 0                  | Register on<br>Page |

|----------------------|-----------------------------------------------------------------------------|---------------------|----------------|-----------------|------------------|---------|-----------------------|------------------------|---------------------|

| APFCON               | RXDTSEL                                                                     | SDOSEL              | SSSEL          | _               | T1GSEL           | TXCKSEL | P1BSEL <sup>(2)</sup> | CCP1SEL <sup>(2)</sup> | 114                 |

| CCP1CON              | P1M•                                                                        | <1:0>               | DC1B           | <1:0>           |                  | CCP1M<  | :3:0>                 |                        | 213                 |

| CCPR1L               | Capture/Con                                                                 | npare/PWM R         | egister x Low  | Byte (LSB)      |                  |         |                       |                        | 191                 |

| CCPR1H               | Capture/Con                                                                 | npare/PWM R         | egister x High | Byte (MSB)      |                  |         |                       |                        | 191                 |

| INTCON               | GIE                                                                         | PEIE                | TMR0IE         | INTE            | IOCIE            | TMR0IF  | INTF                  | IOCIF                  | 86                  |

| PIE1                 | TMR1GIE                                                                     | ADIE                | RCIE           | TXIE            | SSP1IE           | CCP1IE  | TMR2IE                | TMR1IE                 | 87                  |

| PIE2                 | OSFIE                                                                       | C2IE <sup>(1)</sup> | C1IE           | EEIE            | BCL1IE           | _       | _                     | —                      | 88                  |

| PIR1                 | TMR1GIF                                                                     | ADIF                | RCIF           | TXIF            | SSP1IF           | CCP1IF  | TMR2IF                | TMR1IF                 | 89                  |

| PIR2                 | OSFIF                                                                       | C2IF <sup>(1)</sup> | C1IF           | EEIF            | BCL1IF           | _       | _                     | _                      | 90                  |

| T1CON                | TMR1C                                                                       | :S<1:0>             | T1CKP          | S<1:0>          | T1OSCEN          | T1SYNC  | _                     | TMR10N                 | 173                 |

| T1GCON               | TMR1GE                                                                      | T1GPOL              | T1GTM          | T1GSPM          | T1GGO/DONE       | T1GVAL  | T1GS                  | S<1:0>                 | 174                 |

| TMR1H                | Holding Regi                                                                | ster for the M      | ost Significan | t Byte of the 1 | 6-bit TMR1 Regis | ter     |                       |                        | 169                 |

| TMR1L                | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                     |                |                 |                  |         |                       | 169                    |                     |

| TRISA                | —                                                                           | —                   | TRISA5         | TRISA4          | TRISA3           | TRISA2  | TRISA1                | TRISA0                 | 117                 |

| TRISC <sup>(1)</sup> |                                                                             | _                   | TRISC5         | TRISC4          | TRISC3           | TRISC2  | TRISC1                | TRISC0                 | 121                 |

#### TABLE 24-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Capture mode.

**Note 1:** PIC16(L)F1823 only.

2: PIC12(L)F1822 only.

#### 24.4.4 AUTO-RESTART MODE

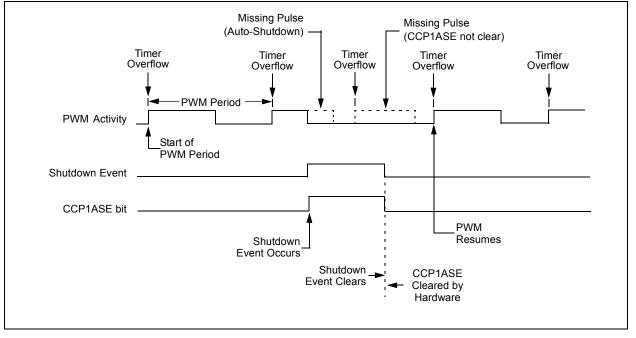

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the P1RSEN bit in the PWM1CON register.

If auto-restart is enabled, the CCP1ASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the CCP1ASE bit will be cleared via hardware and normal operation will resume.

#### FIGURE 24-15: PWM AUTO-SHUTDOWN WITH AUTO-RESTART (P1RSEN = 1)

#### 25.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSP1CON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

# TABLE 25-2: I<sup>2</sup>C BUS TERMS

| TABLE 25-2:         | I-C BUS IERMS                                                                                                                                                                                                   |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                                                     |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                                  |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                                   |

| Master              | The device that initiates a transfer,<br>generates clock signals and termi-<br>nates a transfer.                                                                                                                |

| Slave               | The device addressed by the mas-<br>ter.                                                                                                                                                                        |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                               |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                                             |

| Synchronization     | Procedure to synchronize the<br>clocks of two or more devices on<br>the bus.                                                                                                                                    |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                                    |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                                    |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                                    |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSP1ADD.                                                                                                                             |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                                            |

| Read Request        | Master sends an address byte with<br>the $R/\overline{W}$ bit set, indicating that it<br>wishes to clock data out of the<br>Slave. This data is the next and all<br>following bytes until a Restart or<br>Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                                                   |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                                      |

# 25.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception (Figure 25-29) is enabled by programming the Receive Enable bit, RCEN bit of the SSP1CON2 register.

| Note: | The MSSP1 module must be in an Idle     |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | state before the RCEN bit is set or the |  |  |  |  |  |  |

|       | RCEN bit will be disregarded.           |  |  |  |  |  |  |

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSP1SR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSP1SR are loaded into the SSP1BUF, the BF flag bit is set, the SSP1IF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP1 is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSP1CON2 register.

#### 25.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSP1BUF from SSP1SR. It is cleared when the SSP1BUF register is read.

#### 25.6.7.2 SSP1OV Status Flag

In receive operation, the SSP1OV bit is set when eight bits are received into the SSP1SR and the BF flag bit is already set from a previous reception.

#### 25.6.7.3 WCOL Status Flag

If the user writes the SSP1BUF when a receive is already in progress (i.e., SSP1SR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

25.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSP1CON2 register.

- 2. SSP1IF is set by hardware on completion of the Start.

- 3. SSP1IF is cleared by software.

- 4. User writes SSP1BUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSP1BUF is written to.

- 6. The MSSP1 module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSP1CON2 register.

- 7. The MSSP1 module generates an interrupt at the end of the ninth clock cycle by setting the SSP1IF bit.

- 8. User sets the RCEN bit of the SSP1CON2 register and the Master clocks in a byte from the slave.

- 9. After the eighth falling edge of SCL, SSP1IF and BF are set.

- 10. Master clears SSP1IF and reads the received byte from SSP1UF, clears BF.

- 11. Master sets ACK value sent to slave in ACKDT bit of the SSP1CON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Masters ACK is clocked out to the Slave and SSP1IF is set.

- 13. User clears SSP1IF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

# 26.4 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 26.4.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 26.4.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 26.4.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

# 26.4.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

#### TABLE 30-6: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym.      |                                                      | Characteristic                                             |              | Min.                                      | Тур†   | Max.   | Units | Conditions                         |

|--------------|-----------|------------------------------------------------------|------------------------------------------------------------|--------------|-------------------------------------------|--------|--------|-------|------------------------------------|

| 40*          | Тт0Н      | T0CKI High Pulse Width No Prescaler With Prescaler   |                                                            | No Prescaler | 0.5 Tcy + 20                              | _      | _      | ns    |                                    |

|              |           |                                                      |                                                            | 10           | —                                         | _      | ns     |       |                                    |

| 41*          | TT0L      | T0CKI Low Pulse Width No Prescaler With Prescaler    |                                                            | No Prescaler | 0.5 Tcy + 20                              | —      | _      | ns    |                                    |

|              |           |                                                      |                                                            | 10           | —                                         | _      | ns     |       |                                    |

| 42*          | Тт0Р      | T0CKI Period                                         | od                                                         |              | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | _      | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Тт1Н      | T1CKI High<br>Time                                   | Synchronous, No Prescaler                                  |              | 0.5 Tcy + 20                              | —      | _      | ns    |                                    |

|              |           |                                                      | Synchronous,<br>with Prescaler                             |              | 15                                        | —      | —      | ns    |                                    |

|              |           |                                                      | Asynchronous                                               |              | 30                                        | _      |        | ns    |                                    |

| 46*          | TT1L      | . T1CKI Low<br>Time                                  | Synchronous, N                                             | No Prescaler | 0.5 Tcy + 20                              | —      |        | ns    |                                    |

|              |           |                                                      | Synchronous, with Prescaler<br>Asynchronous                |              | 15                                        | —      | _      | ns    |                                    |

|              |           |                                                      |                                                            |              | 30                                        | —      |        | ns    |                                    |

| 47*          | TT1P      | T1CKI Input<br>Period                                | Synchronous                                                |              | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —      | _      | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                      | Asynchronous                                               |              | 60                                        | —      | _      | ns    |                                    |

| 48           | F⊤1       |                                                      | lator Input Frequency Range nabled by setting bit T1OSCEN) |              | 32.4                                      | 32.768 | 33.1   | kHz   |                                    |

| 49*          | TCKEZTMR1 | Delay from External Clock Edge to Timer<br>Increment |                                                            |              | 2 Tosc                                    | —      | 7 Tosc | —     | Timers in Sync<br>mode             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

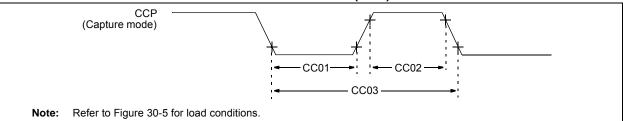

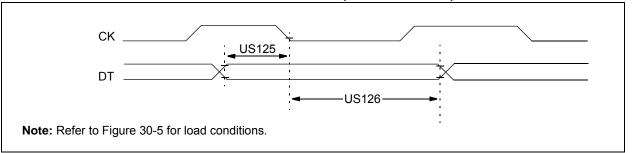

#### FIGURE 30-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

#### TABLE 30-7: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)