Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                       |

| Core Size                  | 16/32-Bit                                                                   |

| Speed                      | 55MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, SSC, UART/USART, USB                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 88                                                                          |

| Program Memory Size        | 512KB (512K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 32K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                               |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 128-LQFP                                                                    |

| Supplier Device Package    | 128-LQFP (20x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7se512b-au |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Provides Reset or Interrupt Signals to the System

- Counter May Be Stopped While the Processor is in Debug State or in Idle Mode

- Real-time Timer (RTT)

- 32-bit Free-running Counter with Alarm

- Runs Off the Internal RC Oscillator

- Three Parallel Input/Output Controllers (PIO)

- Eighty-eight Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os

- Input Change Interrupt Capability on Each I/O Line

- Individually Programmable Open-drain, Pull-up Resistor and Synchronous Output

- Schmitt Trigger on All inputs

- Eleven Peripheral DMA Controller (PDC) Channels

- One USB 2.0 Full Speed (12 Mbits per second) Device Port

- On-chip Transceiver, Eight Endpoints, 2688-byte Configurable Integrated FIFOs

- One Synchronous Serial Controller (SSC)

- Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

- I<sup>2</sup>S Analog Interface Support, Time Division Multiplex Support

- High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

- Two Universal Synchronous/Asynchronous Receiver Transmitters (USART)

- Individual Baud Rate Generator, IrDA<sup>®</sup> Infrared Modulation/Demodulation

- Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

- Full Modem Line Support on USART1

- One Master/Slave Serial Peripheral Interfaces (SPI)

- 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

- One Three-channel 16-bit Timer/Counter (TC)

- Three External Clock Inputs, Two Multi-purpose I/O Pins per Channel

- Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

- One Four-channel 16-bit PWM Controller (PWMC)

- One Two-wire Interface (TWI)

- Master, Multi-Master and Slave Mode Support, All Two-wire Atmel EEPROMs Supported

- General Call Supported in Slave Mode

- One 8-channel 10-bit Analog-to-Digital Converter, Four Channels Multiplexed with Digital I/Os

- SAM-BA®

- Default Boot program

- Interface with SAM-BA Graphic User Interface

- IEEE<sup>®</sup> 1149.1 JTAG Boundary Scan on All Digital Pins

- Four High-current Drive I/O lines, Up to 16 mA Each

- Power Supplies

- Embedded 1.8V Regulator, Drawing up to 100 mA for the Core and External Components

- 1.8V or 3,3V VDDIO I/O Lines Power Supply, Independent 3.3V VDDFLASH Flash Power Supply

- 1.8V VDDCORE Core Power Supply with Brownout Detector

- Fully Static Operation:

- Up to 55 MHz at 1.8V and 85° C Worst Case Conditions

- Up to 48 MHz at 1.65V and 85° C Worst Case Conditions

- Available in a 128-lead LQFP Green Package, or a 144-ball LFBGA RoHS-compliant Package

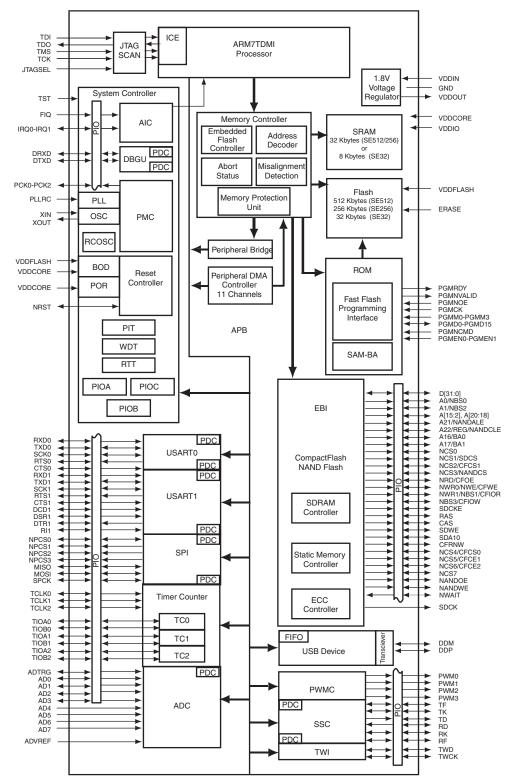

# 2. Block Diagram

| Signal Name | Function                          | Туре         | Active<br>Level | Comments             |

|-------------|-----------------------------------|--------------|-----------------|----------------------|

|             | EBI for NAND F                    | lash Support |                 |                      |

| NANDCS      | NAND Flash Chip Select Line       | Output       | Low             |                      |

| NANDOE      | NAND Flash Output Enable          | Output       | Low             |                      |

| NANDWE      | NAND Flash Write Enable           | Output       | Low             |                      |

| NANDCLE     | NAND Flash Command Line Enable    | Output       | Low             |                      |

| NANDALE     | NAND Flash Address Line Enable    | Output       | Low             |                      |

|             | SDRAM C                           | ontroller    |                 |                      |

| SDCK        | SDRAM Clock                       | Output       |                 | Tied low after reset |

| SDCKE       | SDRAM Clock Enable                | Output       | High            |                      |

| SDCS        | SDRAM Controller Chip Select Line | Output       | Low             |                      |

| BA[1:0]     | Bank Select                       | Output       |                 |                      |

| SDWE        | SDRAM Write Enable                | Output       | Low             |                      |

| RAS - CAS   | RAS - CAS Row and Column Signal   |              | Low             |                      |

| NBS[3:0]    | Byte Mask Signals                 | Output       | Low             |                      |

| SDA10       | SDRAM Address 10 Line             | Output       |                 |                      |

### Table 3-1. Signal Description List (Continued)

Note: 1. Refer to Section 6. "/O Lines Considerations" on page 15.

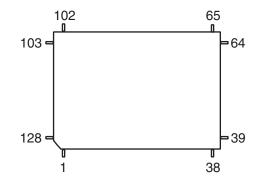

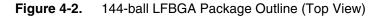

# 4. Package

The SAM7SE512/256/32 is available in:

- 20 x 14 mm 128-lead LQFP package with a 0.5 mm lead pitch.

- 10x 10 x 1.4 mm 144-ball LFBGA package with a 0.8 mm lead pitch

### 4.1 128-lead LQFP Package Outline

Figure 4-1 shows the orientation of the 128-lead LQFP package and a detailed mechanical description is given in the Mechanical Characteristics section of the full datasheet.

Figure 4-1. 128-lead LQFP Package Outline (Top View)

# 4.2 128-lead LQFP Pinout

# Table 4-1.Pinout in 128-lead LQFP Package

| 1  | ADVREF         |  |

|----|----------------|--|

| 2  | GND            |  |

| 3  | AD7            |  |

| 4  | AD6            |  |

| 5  | AD5            |  |

| 6  | AD4            |  |

| 7  | VDDOUT         |  |

| 8  | VDDIN          |  |

| 9  | PA20/PGMD8/AD3 |  |

| 10 | PA19/PGMD7/AD2 |  |

| 11 | PA18/PGMD6/AD1 |  |

| 12 | PA17/PGMD5/AD0 |  |

| 13 | PA16/PGMD4     |  |

| 14 | PA15/PGMD3     |  |

| 15 | PA14/PGMD2     |  |

| 16 | PA13/PGMD1     |  |

| 17 | PA12/PGMD0     |  |

| 18 | PA11/PGMM3     |  |

| 19 | PA10/PGMM2     |  |

| 20 | PA9/PGMM1      |  |

| 21 | VDDIO          |  |

| 22 | GND            |  |

| 23 | VDDCORE        |  |

| 24 | PA8/PGMM0      |  |

| 25 | PA7/PGMNVALID  |  |

| 26 | PA6/PGMNOE     |  |

| 27 | PA5/PGMRDY     |  |

| 28 | PA4/PGMNCMD    |  |

| 29 | PA3            |  |

| 30 | PA2/PGMEN2     |  |

| 31 | PA1/PGMEN1     |  |

| 32 | PA0/PGMEN0     |  |

|    |                |  |

|    | ППаскауе |  |  |  |

|----|----------|--|--|--|

| 33 | PB31     |  |  |  |

| 34 | PB30     |  |  |  |

| 35 | PB29     |  |  |  |

| 36 | PB28     |  |  |  |

| 37 | PB27     |  |  |  |

| 38 | PB26     |  |  |  |

| 39 | PB25     |  |  |  |

| 40 | PB24     |  |  |  |

| 41 | PB23     |  |  |  |

| 42 | PB22     |  |  |  |

| 43 | PB21     |  |  |  |

| 44 | PB20     |  |  |  |

| 45 | GND      |  |  |  |

| 46 | VDDIO    |  |  |  |

| 47 | VDDCORE  |  |  |  |

| 48 | PB19     |  |  |  |

| 49 | PB18     |  |  |  |

| 50 | PB17     |  |  |  |

| 51 | PB16     |  |  |  |

| 52 | PB15     |  |  |  |

| 53 | PB14     |  |  |  |

| 54 | PB13     |  |  |  |

| 55 | PB12     |  |  |  |

| 56 | PB11     |  |  |  |

| 57 | PB10     |  |  |  |

| 58 | PB9      |  |  |  |

| 59 | PB8      |  |  |  |

| 60 | PB7      |  |  |  |

| 61 | PB6      |  |  |  |

| 62 | PB5      |  |  |  |

| 63 | PB4      |  |  |  |

| 64 | PB3      |  |  |  |

|    |          |  |  |  |

| 65 | TDI     |  |  |  |

|----|---------|--|--|--|

| 66 | TDO     |  |  |  |

| 67 | PB2     |  |  |  |

| 68 | PB1     |  |  |  |

| 69 | PB0     |  |  |  |

| 70 | GND     |  |  |  |

| 71 | VDDIO   |  |  |  |

| 72 | VDDCORE |  |  |  |

| 73 | NRST    |  |  |  |

| 74 | TST     |  |  |  |

| 75 | ERASE   |  |  |  |

| 76 | ТСК     |  |  |  |

| 77 | TMS     |  |  |  |

| 78 | JTAGSEL |  |  |  |

| 79 | PC23    |  |  |  |

| 80 | PC22    |  |  |  |

| 81 | PC21    |  |  |  |

| 82 | PC20    |  |  |  |

| 83 | PC19    |  |  |  |

| 84 | PC18    |  |  |  |

| 85 | PC17    |  |  |  |

| 86 | PC16    |  |  |  |

| 87 | PC15    |  |  |  |

| 88 | PC14    |  |  |  |

| 89 | PC13    |  |  |  |

| 90 | PC12    |  |  |  |

| 91 | PC11    |  |  |  |

| 92 | PC10    |  |  |  |

| 93 | PC9     |  |  |  |

| 94 | GND     |  |  |  |

| 95 | VDDIO   |  |  |  |

| 96 | VDDCORE |  |  |  |

|    | -       |  |  |  |

| 97  | SDCK        |

|-----|-------------|

| 98  | PC8         |

| 99  | PC7         |

| 100 | PC6         |

| 101 | PC5         |

| 102 | PC4         |

| 103 | PC3         |

| 104 | PC2         |

| 105 | PC1         |

| 106 | PC0         |

| 107 | PA31        |

| 108 | PA30        |

| 109 | PA29        |

| 110 | PA28        |

| 111 | PA27/PGMD15 |

| 112 | PA26/PGMD14 |

| 113 | PA25/PGMD13 |

| 114 | PA24/PGMD12 |

| 115 | PA23/PGMD11 |

| 116 | PA22/PGMD10 |

| 117 | PA21/PGMD9  |

| 118 | VDDCORE     |

| 119 | GND         |

| 120 | VDDIO       |

| 121 | DM          |

| 122 | DP          |

| 123 | VDDFLASH    |

| 124 | GND         |

| 125 | XIN/PGMCK   |

| 126 | XOUT        |

| 127 | PLLRC       |

| 128 | VDDPLL      |

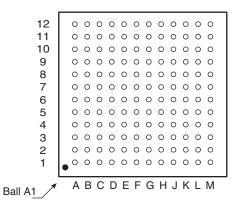

### 4.3 144-ball LFBGA Package Outline

Figure 4-2 shows the orientation of the 144-ball LFBGA package and a detailed mechanical description is given in the Mechanical Characteristics section.

# 4.4 144-ball LFBGA Pinout

| Pin | Signal Name | Pin | Signal Name   | Pin | Signal Name    | Pin | Signal Name    |

|-----|-------------|-----|---------------|-----|----------------|-----|----------------|

| A1  | PB7         | D1  | VDDCORE       | G1  | PC18           | K1  | PC11           |

| A2  | PB8         | D2  | VDDCORE       | G2  | PC16           | K2  | PC6            |

| A3  | PB9         | D3  | PB2           | G3  | PC17           | КЗ  | PC2            |

| A4  | PB12        | D4  | TDO           | G4  | PC9            | K4  | PC0            |

| A5  | PB13        | D5  | TDI           | G5  | VDDIO          | K5  | PA27/PGMD15    |

| A6  | PB16        | D6  | PB17          | G6  | GND            | K6  | PA26/PGMD14    |

| A7  | PB22        | D7  | PB26          | G7  | GND            | K7  | GND            |

| A8  | PB23        | D8  | PA14/PGMD2    | G8  | GND            | K8  | VDDCORE        |

| A9  | PB25        | D9  | PA12/PGMD0    | G9  | GND            | К9  | VDDFLASH       |

| A10 | PB29        | D10 | PA11/PGMM3    | G10 | AD4            | K10 | VDDIO          |

| A11 | PB30        | D11 | PA8/PGMM0     | G11 | VDDIN          | K11 | VDDIO          |

| A12 | PB31        | D12 | PA7/PGMNVALID | G12 | VDDOUT         | K12 | PA18/PGMD6/AD1 |

| B1  | PB6         | E1  | PC22          | H1  | PC15           | L1  | SDCK           |

| B2  | PB3         | E2  | PC23          | H2  | PC14           | L2  | PC7            |

| B3  | PB4         | E3  | NRST          | НЗ  | PC13           | L3  | PC4            |

| B4  | PB10        | E4  | ТСК           | H4  | VDDCORE        | L4  | PC1            |

| B5  | PB14        | E5  | ERASE         | H5  | VDDCORE        | L5  | PA29           |

| B6  | PB18        | E6  | TEST          | H6  | GND            | L6  | PA24/PGMD12    |

| B7  | PB20        | E7  | VDDCORE       | H7  | GND            | L7  | PA21/PGMD9     |

| B8  | PB24        | E8  | VDDCORE       | H8  | GND            | L8  | ADVREF         |

| B9  | PB28        | E9  | GND           | H9  | GND            | L9  | VDDFLASH       |

| B10 | PA4/PGMNCMD | E10 | PA9/PGMM1     | H10 | PA19/PGMD7/AD2 | L10 | VDDFLASH       |

| B11 | PA0/PGMEN0  | E11 | PA10/PGMM2    | H11 | PA20/PGMD8/AD3 | L11 | PA17/PGMD5/AD0 |

| B12 | PA1/PGMEN1  | E12 | PA13/PGMD1    | H12 | VDDIO          | L12 | GND            |

| C1  | PB0         | F1  | PC21          | J1  | PC12           | M1  | PC8            |

| C2  | PB1         | F2  | PC20          | J2  | PC10           | M2  | PC5            |

| C3  | PB5         | F3  | PC19          | JЗ  | PA30           | M3  | PC3            |

| C4  | PB11        | F4  | JTAGSEL       | J4  | PA28           | M4  | PA31           |

| C5  | PB15        | F5  | TMS           | J5  | PA23/PGMD11    | M5  | PA25/PGMD13    |

| C6  | PB19        | F6  | VDDIO         | J6  | PA22/PGMD10    | M6  | DM             |

| C7  | PB21        | F7  | GND           | J7  | AD6            | M7  | DP             |

| C8  | PB27        | F8  | GND           | J8  | AD7            | M8  | GND            |

| C9  | PA6/PGMNOE  | F9  | GND           | J9  | VDDCORE        | M9  | XIN/PGMCK      |

| C10 | PA5/PGMRDY  | F10 | AD5           | J10 | VDDCORE        | M10 | XOUT           |

| C11 | PA2/PGMEN2  | F11 | PA15/PGMD3    | J11 | VDDCORE        | M11 | PLLRC          |

| C12 | PA3         | F12 | PA16/PGMD4    | J12 | VDDIO          | M12 | VDDPLL         |

Table 4-2.SAM7SE512/256/32 Pinout for 144-ball LFBGA Package

# 12 SAM7SE512/256/32 Summary

# 5. Power Considerations

### 5.1 Power Supplies

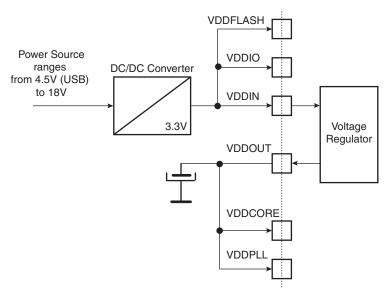

The SAM7SE512/256/32 has six types of power supply pins and integrates a voltage regulator, allowing the device to be supplied with only one voltage. The six power supply pin types are:

- VDDIN pin. It powers the voltage regulator and the ADC; voltage ranges from 3.0V to 3.6V, 3.3V nominal.

- VDDOUT pin. It is the output of the 1.8V voltage regulator.

- VDDIO pin. It powers the I/O lines; two voltage ranges are supported:

- from 3.0V to 3.6V, 3.3V nominal

- or from 1.65V to 1.95V, 1.8V nominal.

- VDDFLASH pin. It powers the USB transceivers and a part of the Flash. It is required for the Flash to operate correctly; voltage ranges from 3.0V to 3.6V, 3.3V nominal.

- VDDCORE pins. They power the logic of the device; voltage ranges from 1.65V to 1.95V, 1.8V typical. It can be connected to the VDDOUT pin with decoupling capacitor. VDDCORE is required for the device, including its embedded Flash, to operate correctly.

- VDDPLL pin. It powers the oscillator and the PLL. It can be connected directly to the VDDOUT pin.

In order to decrease current consumption, if the voltage regulator and the ADC are not used, VDDIN, ADVREF, AD4, AD5, AD6 and AD7 should be connected to GND. In this case VDDOUT should be left unconnected.

No separate ground pins are provided for the different power supplies. Only GND pins are provided and should be connected as shortly as possible to the system ground plane.

### 5.2 Power Consumption

The SAM7SE512/256/32 has a static current of less than 60  $\mu$ A on VDDCORE at 25°C, including the RC oscillator, the voltage regulator and the power-on reset when the brownout detector is deactivated. Activating the brownout detector adds 20  $\mu$ A static current.

The dynamic power consumption on VDDCORE is less than 80 mA at full speed when running out of the Flash. Under the same conditions, the power consumption on VDDFLASH does not exceed 10 mA.

### 5.3 Voltage Regulator

The SAM7SE512/256/32 embeds a voltage regulator that is managed by the System Controller.

In Normal Mode, the voltage regulator consumes less than 100  $\mu$ A static current and draws 100 mA of output current.

The voltage regulator also has a Low-power Mode. In this mode, it consumes less than 20  $\mu$ A static current and draws 1 mA of output current.

Adequate output supply decoupling is mandatory for VDDOUT to reduce ripple and avoid oscillations. The best way to achieve this is to use two capacitors in parallel:

• One external 470 pF (or 1 nF) NPO capacitor should be connected between VDDOUT and GND as close to the chip as possible.

- One external 2.2  $\mu F$  (or 3.3  $\mu F)$  X7R capacitor should be connected between VDDOUT and GND.

Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop. The input decoupling capacitor should be placed close to the chip. For example, two capacitors can be used in parallel: 100 nF NPO and 4.7  $\mu$ F X7R.

### 5.4 Typical Powering Schematics

The SAM7SE512/256/32 supports a 3.3V single supply mode. The internal regulator input connected to the 3.3V source and its output feeds VDDCORE and the VDDPLL. Figure 5-1 shows the power schematics to be used for USB bus-powered systems.

Figure 5-1. 3.3V System Single Power Supply Schematic

## 7.8 Peripheral DMA Controller

- Handles data transfer between peripherals and memories

- Eleven channels

- Two for each USART

- Two for the Debug Unit

- Two for the Serial Synchronous Controller

- Two for the Serial Peripheral Interface

- One for the Analog-to-digital Converter

- · Low bus arbitration overhead

- One Master Clock cycle needed for a transfer from memory to peripheral

- Two Master Clock cycles needed for a transfer from peripheral to memory

- Next Pointer management for reducing interrupt latency requirements

- Peripheral DMA Controller (PDC) priority is as follows (from the highest priority to the lowest):

| Receive  | DBGU   |

|----------|--------|

| Receive  | USART0 |

| Receive  | USART1 |

| Receive  | SSC    |

| Receive  | ADC    |

| Receive  | SPI    |

| Transmit | DBGU   |

| Transmit | USART0 |

| Transmit | USART1 |

| Transmit | SSC    |

| Transmit | SPI    |

|          |        |

# SAM7SE512/256/32 Summary

## 8. Memories

- 512 Kbytes of Flash Memory (SAM7SE512)

- dual plane

- two contiguous banks of 1024 pages of 256 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 32 lock bits, each protecting 32 lock regions of 64 pages

- Protection Mode to secure contents of the Flash

- 256 Kbytes of Flash Memory (SAM7SE256)

- single plane

- one bank of 1024 pages of 256 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 cycles, 10-year data retention capability

- 16 lock bits, each protecting 16 lock regions of 64 pages

- Protection Mode to secure contents of the Flash

- 32 Kbytes of Flash Memory (SAM7SE32)

- single plane

- one bank of 256 pages of 128 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 cycles, 10-year data retention capability

- 8 lock bits, each protecting 8 lock regions of 32 pages

- Protection Mode to secure contents of the Flash

- 32 Kbytes of Fast SRAM (SAM7SE512/256)

- Single-cycle access at full speed

- 8 Kbytes of Fast SRAM (SAM7SE32)

- Single-cycle access at full speed

|            | 0x0000 0000<br>0x000F FFFF<br>0x0010 0000 | <b>ROM</b> Before Remap<br>SRAM After Remap |  | 1 M Bytes   |

|------------|-------------------------------------------|---------------------------------------------|--|-------------|

|            | 0x001F FFFF<br>0x0020 0000                | Internal FLASH                              |  | 1 M Bytes   |

| 256M Bytes | 0x002F FFFF                               | Internal SRAM                               |  | 1 M Bytes   |

|            | 0x0030 0000<br>0x003F FFFF                | Internal ROM                                |  | 1 M Bytes   |

|            | 0x0040 0000                               | Undefined Areas<br>(Abort)                  |  | 252 M Bytes |

|            | 0x0FFF FFFF                               |                                             |  |             |

**Figure 8-2.** Internal Memory Mapping with GPNVM Bit 2 = 0 (default)

**Figure 8-3.** Internal Memory Mapping with GPNVM Bit 2 = 1

|            | 0x0000 0000<br>0x000F FFFF<br>0x0010 0000 | <b>Flash</b> Before Remap<br>SRAM After Remap |  | 1 M Bytes   |

|------------|-------------------------------------------|-----------------------------------------------|--|-------------|

|            | 0x001F FFFF<br>0x0020 0000                | Internal FLASH                                |  | 1 M Bytes   |

| 256M Bytes | 0x002F FFFF<br>0x0030 0000                | Internal SRAM                                 |  | 1 M Bytes   |

|            | 0x0036 FFFF                               | Internal ROM                                  |  | 1 M Bytes   |

|            | 0x0040 0000                               | Undefined Areas<br>(Abort)                    |  | 252 M Bytes |

|            | 0x0FFF FFFF                               |                                               |  | ¢           |

#### 8.1.2 Embedded Flash

#### 8.1.2.1 Flash Overview

The Flash of the SAM7SE512 is organized in two banks (dual plane) of 1024 pages of 256 bytes. It reads as 131,072 32-bit words.

The Flash of the SAM7SE256 is organized in 1024 pages (single plane) of 256 bytes. It reads as 65,536 32-bit words.

The Flash of the SAM7SE32 is organized in 256 pages (single plane) of 128 bytes. It reads as 8192 32-bit words.

The Flash of the SAM7SE32 contains a 128-byte write buffer, accessible through a 32-bit interface.

The Flash of the SAM7SE512/256 contains a 256-byte write buffer, accessible through a 32-bit interface.

The security bit can only be enabled through the Command "Set Security Bit" of the EFC User Interface. Disabling the security bit can only be achieved by asserting the ERASE pin at 1 and after a full flash erase is performed. When the security bit is deactivated, all accesses to the flash are permitted.

It is important to note that the assertion of the ERASE pin should always be longer than 200 ms.

As the ERASE pin integrates a permanent pull-down, it can be left unconnected during normal operation. However, it is safer to connect it directly to GND for the final application.

#### 8.1.2.5 Non-volatile Brownout Detector Control

Two general purpose NVM (GPNVM) bits are used for controlling the brownout detector (BOD), so that even after a power loss, the brownout detector operations remain in their state.

These two GPNVM bits can be cleared or set respectively through the commands "Clear General-purpose NVM Bit" and "Set General-purpose NVM Bit" of the EFC User Interface.

- GPNVM bit 0 is used as a brownout detector enable bit. Setting the GPNVM bit 0 enables the BOD, clearing it disables the BOD. Asserting ERASE clears the GPNVM bit 0 and thus disables the brownout detector by default.

- GPNVM bit 1 is used as a brownout reset enable signal for the reset controller. Setting the GPNVM bit 1 enables the brownout reset when a brownout is detected, Clearing the GPNVM bit 1 disables the brownout reset. Asserting ERASE disables the brownout reset by default.

#### 8.1.2.6 Calibration Bits

Sixteen NVM bits are used to calibrate the brownout detector and the voltage regulator. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the calibration bits.

#### 8.1.3 Fast Flash Programming Interface

The Fast Flash Programming Interface allows programming the device through either a serial JTAG interface or through a multiplexed fully-handshaked parallel port. It allows gang-programming with market-standard industrial programmers.

The FFPI supports read, page program, page erase, full erase, lock, unlock and protect commands.

The Fast Flash Programming Interface is enabled and the Fast Programming Mode is entered when the TST pin and the PA0 and PA1 pins are all tied high and PA2 tied to low.

- The Flash of the SAM7SE512 is organized in 2048 pages of 256 bytes (dual plane). It reads as 131,072 32-bit words.

- The Flash of the SAM7SE256 is organized in 1024 pages of 256 bytes (single plane). It reads as 65,536 32-bit words.

- The Flash of the SAM7SE32 is organized in 256 pages of 128 bytes (single plane). It reads as 32,768 32-bit words.

- The Flash of the SAM7SE512/256 contains a 256-byte write buffer, accessible through a 32bit interface.

- The Flash of the SAM7SE32 contains a 128-byte write buffer, accessible through a 32-bit interface.

### 8.1.4 SAM-BA<sup>®</sup> Boot

The SAM-BA Boot is a default Boot Program which provides an easy way to program in-situ the on-chip Flash memory.

The SAM-BA Boot Assistant supports serial communication via the DBGU or the USB Device Port.

- Communication via the DBGU supports a wide range of crystals from 3 to 20 MHz via software auto-detection.

- Communication via the USB Device Port is limited to an 18.432 MHz crystal.

The SAM-BA Boot provides an interface with SAM-BA Graphic User Interface (GUI).

The SAM-BA Boot is in ROM and is mapped in Flash at address 0x0 when GPNVM bit 2 is set to 0.

### 8.2 External Memories

The external memories are accessed through the External Bus Interface.

Refer to the memory map in Figure 8-1 on page 22.

# 9. System Controller

The System Controller manages all vital blocks of the microcontroller: interrupts, clocks, power, time, debug and reset.

The System Controller peripherals are all mapped to the highest 4 Kbytes of address space, between addresses 0xFFFF F000 and 0xFFFF FFFF.

Figure 9-1 on page 29 shows the System Controller Block Diagram.

Figure 8-1 on page 22 shows the mapping of the User Interface of the System Controller peripherals. Note that the Memory Controller configuration user interface is also mapped within this address space.

• Synchronous output, provides Set and Clear of several I/O lines in a single write

# 9.10 Voltage Regulator Controller

The purpose of this controller is to select the Power Mode of the Voltage Regulator between Normal Mode (bit 0 is cleared) or Standby Mode (bit 0 is set).

# 10.4 PIO Controller A Multiplexing

|          | P                                  | IO Controller A | Application Usage |          |  |

|----------|------------------------------------|-----------------|-------------------|----------|--|

| I/O Line | Peripheral A Peripheral B Comments |                 | Function          | Comments |  |

| PA0      | PWM0                               | A0/NBS0         | High-Drive        |          |  |

| PA1      | PWM1                               | A1/NBS2         | High-Drive        |          |  |

| PA2      | PWM2                               | A2              | High-Drive        |          |  |

| PA3      | TWD                                | A3              | High-Drive        |          |  |

| PA4      | ТѠСК                               | A4              |                   |          |  |

| PA5      | RXD0                               | A5              |                   |          |  |

| PA6      | TXD0                               | A6              |                   |          |  |

| PA7      | RTS0                               | A7              |                   |          |  |

| PA8      | CTS0                               | A8              |                   |          |  |

| PA9      | DRXD                               | A9              |                   |          |  |

| PA10     | DTXD                               | A10             |                   |          |  |

| PA11     | NPCS0                              | A11             |                   |          |  |

| PA12     | MISO                               | A12             |                   |          |  |

| PA13     | MOSI                               | A13             |                   |          |  |

| PA14     | SPCK                               | A14             |                   |          |  |

| PA15     | TF                                 | A15             |                   |          |  |

| PA16     | ТК                                 | A16/BA0         |                   |          |  |

| PA17     | TD                                 | A17/BA1         | AD0               |          |  |

| PA18     | RD                                 | NBS3/CFIOW      | AD1               |          |  |

| PA19     | RK                                 | NCS4/CFCS0      | AD2               |          |  |

| PA20     | RF                                 | NCS2/CFCS1      | AD3               |          |  |

| PA21     | RXD1                               | NCS6/CFCE2      |                   |          |  |

| PA22     | TXD1                               | NCS5/CFCE1      |                   |          |  |

| PA23     | SCK1                               | NWR1/NBS1/CFIOR |                   |          |  |

| PA24     | RTS1                               | SDA10           |                   |          |  |

| PA25     | CTS1                               | SDCKE           |                   |          |  |

| PA26     | DCD1                               | NCS1/SDCS       |                   |          |  |

| PA27     | DTR1                               | SDWE            |                   |          |  |

| PA28     | DSR1                               | CAS             |                   |          |  |

| PA29     | RI1                                | RAS             |                   |          |  |

| PA30     | IRQ1                               | D30             |                   |          |  |

| PA31     | NPCS1                              | D31             |                   |          |  |

Table 10-2. Multiplexing on PIO Controller A

# 10.5 PIO Controller B Multiplexing

|                       | PIC   | O Controller B                     | Application Usage |          |          |  |

|-----------------------|-------|------------------------------------|-------------------|----------|----------|--|

| I/O Line Peripheral A |       | Peripheral A Peripheral B Comments |                   | Function | Comments |  |

| PB0                   | TIOA0 | A0/NBS0                            |                   |          |          |  |

| PB1                   | TIOB0 | A1/NBS2                            |                   |          |          |  |

| PB2                   | SCK0  | A2                                 |                   |          |          |  |

| PB3                   | NPCS3 | A3                                 |                   |          |          |  |

| PB4                   | TCLK0 | A4                                 |                   |          |          |  |

| PB5                   | NPCS3 | A5                                 |                   |          |          |  |

| PB6                   | PCK0  | A6                                 |                   |          |          |  |

| PB7                   | PWM3  | A7                                 |                   |          |          |  |

| PB8                   | ADTRG | A8                                 |                   |          |          |  |

| PB9                   | NPCS1 | A9                                 |                   |          |          |  |

| PB10                  | NPCS2 | A10                                |                   |          |          |  |

| PB11                  | PWM0  | A11                                |                   |          |          |  |

| PB12                  | PWM1  | A12                                |                   |          |          |  |

| PB13                  | PWM2  | A13                                |                   |          |          |  |

| PB14                  | PWM3  | A14                                |                   |          |          |  |

| PB15                  | TIOA1 | A15                                |                   |          |          |  |

| PB16                  | TIOB1 | A16/BA0                            |                   |          |          |  |

| PB17                  | PCK1  | A17/BA1                            |                   |          |          |  |

| PB18                  | PCK2  | D16                                |                   |          |          |  |

| PB19                  | FIQ   | D17                                |                   |          |          |  |

| PB20                  | IRQ0  | D18                                |                   |          |          |  |

| PB21                  | PCK1  | D19                                |                   |          |          |  |

| PB22                  | NPCS3 | D20                                |                   |          |          |  |

| PB23                  | PWM0  | D21                                |                   |          |          |  |

| PB24                  | PWM1  | D22                                |                   |          |          |  |

| PB25                  | PWM2  | D23                                |                   |          |          |  |

| PB26                  | TIOA2 | D24                                |                   |          |          |  |

| PB27                  | TIOB2 | D25                                |                   |          |          |  |

| PB28                  | TCLK1 | D26                                |                   |          |          |  |

| PB29                  | TCLK2 | D27                                |                   |          |          |  |

| PB30                  | NPCS2 | D28                                |                   |          |          |  |

| PB31                  | PCK2  | D29                                |                   |          |          |  |

Table 10-3. Multiplexing on PIO Controller B

- 8- to 16-bit programmable data length per chip select

- Programmable phase and polarity per chip select

- Programmable transfer delays per chip select, between consecutive transfers and between clock and data

- Programmable delay between consecutive transfers

- Selectable mode fault detection

- Maximum frequency at up to Master Clock

### 10.8 Two Wire Interface

- Master, Multi-Master and Slave Mode Operation

- · Compatibility with standard two-wire serial memories

- One, two or three bytes for slave address

- · Sequential read/write operations

- Bit Rate: Up to 400 Kbit/s

- General Call Supported in Slave Mode

### 10.9 USART

- Programmable Baud Rate Generator

- 5- to 9-bit full-duplex synchronous or asynchronous serial communications

- 1, 1.5 or 2 stop bits in Asynchronous Mode

- 1 or 2 stop bits in Synchronous Mode

- Parity generation and error detection

- Framing error detection, overrun error detection

- MSB or LSB first

- Optional break generation and detection

- By 8 or by 16 over-sampling receiver frequency

- Hardware handshaking RTS CTS

- Modem Signals Management DTR-DSR-DCD-RI on USART1

- Receiver time-out and transmitter timeguard

- Multi-drop Mode with address generation and detection

- RS485 with driver control signal

- ISO7816, T = 0 or T = 1 Protocols for interfacing with smart cards

- NACK handling, error counter with repetition and iteration limit

- IrDA<sup>®</sup> modulation and demodulation

- Communication at up to 115.2 Kbps

- Test Modes

- Remote Loopback, Local Loopback, Automatic Echo

### **10.10 Serial Synchronous Controller**

- Provides serial synchronous communication links used in audio and telecom applications

- · Contains an independent receiver and transmitter and a common clock divider

# 40 SAM7SE512/256/32 Summary

#### **Headquarters**

*Atmel Corporation* 2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1) (408) 441-0311 Fax: (+1) (408) 487-2600 International

Atmel Asia Limited Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369 Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 JAPAN Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com www.atmel.com/AT91SAM **Technical Support** AT91SAM Support Atmel techincal support Sales Contacts www.atmel.com/contacts/

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2011 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, Atmel logo and combinations thereof, SAMBA<sup>®</sup>, DataFlash<sup>®</sup>and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM<sup>®</sup>, ARMPowered<sup>®</sup>logo, Cortex<sup>®</sup>, Thumb<sup>®</sup>-2 and others are registered trademarks or trademarks of ARM Ltd. Windows<sup>®</sup> and others are registered trademarks or trademarks of Microsoft Corporation in the US and/or other countries. Other terms and product names may be trademarks of others.