Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product StatusActiveCore ProcessorARM® Cortex®-M4FCore Size32-Bit Single-CoreSpeed160MHzConnectivityCSIO, EBI/EMI, I°C, LINbus, SD, SPI, UART/USART, USBPeripheralsDMA, I°S, LVD, POR, PWM, WDTNumber of I/O154Program Memory Size384KB (384K x 8)Program Memory TypeFLASHEEPROM Size-Notate - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)Purchace LIPLhttps://www.ex.fl.com/product-detail/infineon-techpologies/s6e2df5i0aqx2000a |                            |                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed160MHzConnectivityCSIO, EBI/EMI, I²C, LINbus, SD, SPI, UART/USART, USBPeripheralsDMA, I²S, LVD, POR, PWM, WDTNumber of I/O154Program Memory Size384KB (384K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size36K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)                                                                                                     | Product Status             | Active                                                                       |

| Speed160MHzConnectivityCSIO, EBI/EMI, I²C, LINbus, SD, SPI, UART/USART, USBPeripheralsDMA, I²S, LVD, POR, PWM, WDTNumber of I/O154Program Memory Size384KB (384K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size36K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                 | Core Processor             | ARM® Cortex®-M4F                                                             |

| ConnectivityCSIO, EBI/EMI, I²C, LINbus, SD, SPI, UART/USART, USBPeripheralsDMA, I²S, LVD, POR, PWM, WDTNumber of I/O154Program Memory Size384KB (384K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size36K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)                                                                                                                                           | Core Size                  | 32-Bit Single-Core                                                           |

| PeripheralsDMA, I2S, LVD, POR, PWM, WDTNumber of I/O154Program Memory Size384KB (384K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size36K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)                                                                                                                                                                                                           | Speed                      | 160MHz                                                                       |

| Number of I/O154Program Memory Size384KB (384K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size36K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                   | Connectivity               | CSIO, EBI/EMI, I <sup>2</sup> C, LINbus, SD, SPI, UART/USART, USB            |

| Program Memory Size384KB (384K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size36K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                   | Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                    |

| Program Memory TypeFLASHEEPROM Size-RAM Size36K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                      | Number of I/O              | 154                                                                          |

| EEPROM Size-RAM Size36K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                              | Program Memory Size        | 384KB (384K x 8)                                                             |

| RAM Size36K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                                          | Program Memory Type        | FLASH                                                                        |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                         | EEPROM Size                | -                                                                            |

| Data ConvertersA/D 24x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                              | RAM Size                   | 36K x 8                                                                      |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                       | Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                  |

| Operating Temperature     -40°C ~ 125°C (TA)       Mounting Type     Surface Mount       Package / Case     176-LQFP       Supplier Device Package     176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                     | Data Converters            | A/D 24x12b                                                                   |

| Mounting Type     Surface Mount       Package / Case     176-LQFP       Supplier Device Package     176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                                                        | Oscillator Type            | Internal                                                                     |

| Package / Case     176-LQFP       Supplier Device Package     176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Supplier Device Package 176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mounting Type              | Surface Mount                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Package / Case             | 176-LQFP                                                                     |

| Purchase LIPL https://www.e-xfl.com/product-detail/infineon-technologies/s6e2df5i0agv2000a                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Supplier Device Package    | 176-LQFP (24x24)                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e2df5j0agv2000a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **CAN-FD Interface (One channel)**

Compatible with CAN Specification 2.0A/B

- ■Maximum transfer rate: 5 Mbps

- ■Message buffer for receiver: Up to 192 messages

- Message buffer for transmitter: Up to 32 messages

- CAN with flexible data rate (non-ISO CAN FD)

#### ■Notes:

- CAN FD cannot communicate between non-ISO CAN FD and ISO CAN FD, because non-ISO CAN FD and ISO CAN FD are different frame format.

- □ About the problem of "non-ISO CAN FD", see the White Paper from CiA(CAN in Automation).

- http://www.cannewsletter.org/engineering/standardization/141222\_canfd-and-crc-issued\_white-paper\_bosch

## Multi-function Serial Interface (Max eight channels)

- 64 bytes with FIFO (the FIFO step numbers vary depending on the settings of the communication mode or bit length.)

- Operation mode is selectable from the following for each channel.

□ UART

- □ CSIO

- 🗆 LIN

$\Box I^2C$

## **■**UART

- Full-duplex double buffer

- □ Selection with or without parity supported

- □ Built-in dedicated baud rate generator

- External clock available as a serial clock

- □ Various error detect functions available (parity errors, framing errors, and overrun errors)

## ■CSIO

- □ Full-duplex double buffer

- Built-in dedicated baud rate generator

- Dverrun error detect function available

- □ Serial chip select function (ch.6 and ch.7 only)

- □ Supports High-speed SPI (ch.6 only)

- □ Data length 5 to 16-bit

## ■LIN

- LIN protocol Rev.2.1 supported

- □ Full-duplex double buffer

- □ Master/Slave mode supported

- □ LIN break field generation (can change to 13 to 16-bit length)

- □ LIN break delimiter generation (can change to 1 to 4-bit length)

- □ Various error detect functions available (parity errors, framing errors, and overrun errors)

## ■I<sup>2</sup>C

- □ Standard mode (Max 100 kbps) / Fast mode (Max 400 kbps) supported

- □ Fast mode Plus (Fm+) (Max 1000 kbps, only for ch.4=ch.A) supported

## **DMA Controller (Eight channels)**

The DMA controller has an independent bus for the CPU, so the CPU and the DMA controller can process simultaneously.

- ■8 independently configured and operated channels

- Transfer can be started by software or requested from the built-in peripherals

- Transfer address area: 32-bit (4 Gbytes)

- Transfer mode: Block transfer/Burst transfer/Demand transfer

- Transfer data type: bytes/half-word/word

- Transfer block count: 1 to 16

- ■Number of transfers: 1 to 65536

# DSTC (Descriptor System Data Transfer Controller) (128 channels)

The DSTC can transfer data at high-speed without going via the CPU. The DSTC adopts the descriptor system and, following the specified contents of the descriptor that has already been constructed on the memory, can directly access the memory/peripheral device and performs the data transfer operation.

It supports the software activation, the hardware activation, and the chain activation functions.

## A/D Converter (Max 24 channels)

- 12-bit A/D Converter

- □ Successive Approximation type

- □ Built-in 2 units

- □ Conversion time: 1.0 µs @ 3.3 V

- □ Priority conversion available (priority at two levels)

- □ Scanning conversion mode

- Built-in FIFO for conversion data storage (for SCAN conversion: 16 steps, for priority conversion: four steps)

## **Base Timer (Max eight channels)**

Operation mode is selectable from the followings for each channel.

- 16-bit PWM timer

- 16-bit PPG timer

- ■16-/32-bit reload timer

- ■16-/32-bit PWC timer

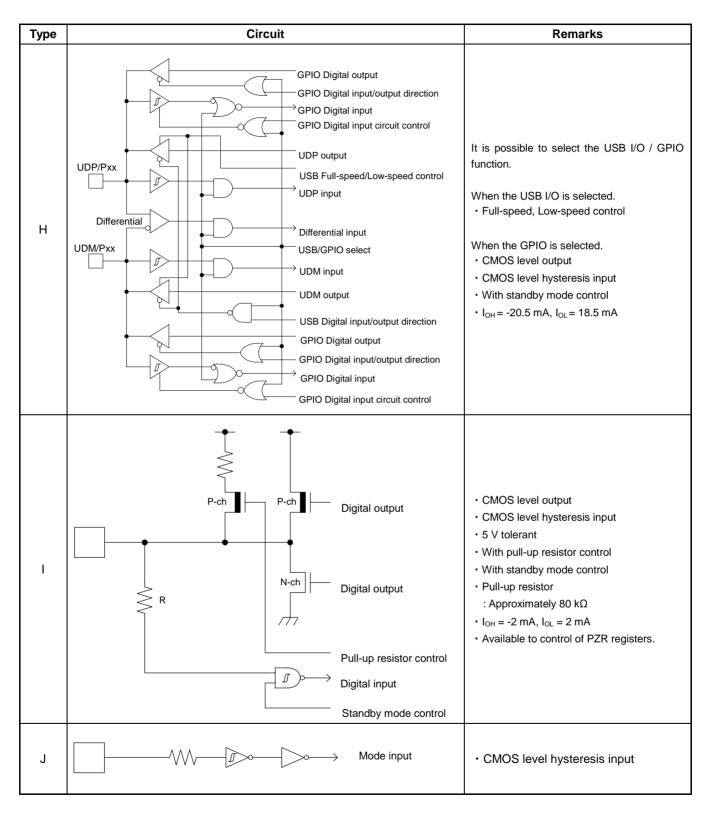

## **General-Purpose I/O Port**

This series can use its pins as general-purpose I/O ports when they are not used for external bus or peripherals. Moreover, the port relocate function is built in. It can set to which I/O port the peripheral function can be allocated.

- Capable of pull-up control per pin

- Capable of reading pin level directly

- ■Built-in port relocate function

- ■Up to 98 general-purpose I/O ports @ 120-pin package

- Some I/O pins are 5V tolerant. See "4. Pin Descriptions" and "5. I/O Circuit Type" for the corresponding pins.

|         |                       | Pin No.                 |              |           | I/O             | Pin           |

|---------|-----------------------|-------------------------|--------------|-----------|-----------------|---------------|

| LQFP176 | LQFP120<br>Ex-LQFP120 | LQFP120<br>(S6E2D55GJA) | FBGA161      | Pin name  | circuit<br>type | state<br>type |

|         |                       | ,                       |              | P3E       |                 |               |

|         |                       |                         |              | SOT7_0    |                 |               |

|         |                       |                         |              | (SDA7_0)  |                 |               |

|         |                       |                         |              | TIOA3_1   |                 |               |

| 9       | 5                     | 5                       | D2           | INT07_1   | G               | к             |

|         |                       |                         |              | I2SDI0_0  |                 |               |

|         |                       |                         |              | RTO03_0   |                 |               |

|         |                       |                         |              | (PPG02_0) |                 |               |

|         |                       |                         |              | MAD07_0   |                 |               |

|         |                       |                         |              | P3F       |                 |               |

|         |                       |                         |              | SCK7_0    |                 |               |

|         |                       |                         |              | (SCL7_0)  |                 |               |

| 10      | 0                     | 0                       | 54           | TIOA4_1   |                 |               |

|         | 6                     | 6                       | D1           | I2SCK0_0  | G               | I             |

|         |                       |                         |              | RTO04_0   |                 |               |

|         |                       |                         |              | (PPG04_0) |                 |               |

|         |                       |                         |              | MAD06_0   |                 |               |

|         |                       |                         |              | P7C       |                 |               |

|         |                       |                         |              | TIOA5_1   | G               |               |

| 11      | 7                     | 7                       | D4           | RTO05_0   |                 | I             |

|         |                       |                         |              | (PPG04_0) |                 |               |

|         |                       |                         |              | MWEX_0    |                 |               |

|         |                       |                         |              | P7B       | - к I           |               |

| 40      | 8 –                   | _                       | о <b>Г</b> 4 | ADTG_2    |                 |               |

| 12      |                       |                         | E4           | GE_HBCSX1 |                 | I             |

|         |                       |                         |              | MOEX_0    |                 |               |

|         |                       |                         |              | P7B       |                 |               |

| _       | _                     | - 8                     | _            | ADTG_2    | к               | I             |

|         |                       |                         |              | MOEX_0    |                 |               |

| 40      |                       |                         |              | PA8       |                 |               |

| 13      | _                     | —                       | —            | GE_SDDQ29 | L               | I             |

|         |                       |                         |              | PA9       |                 |               |

| 14      | _                     | —                       | —            | GE_SDDQ28 | L               | I             |

| 45      |                       |                         |              | PAA       |                 |               |

| 15      | _                     | —                       | —            | GE_SDDQ27 | L               | I             |

| 40      |                       |                         |              | PAB       |                 |               |

| 16      | -                     | _                       | _            | GE_SDDQ26 | L               | I             |

| 47      |                       |                         | PA           |           |                 | ,             |

| 17      | _                     | _                       | _            | GE_SDDQ25 | - L             |               |

| 45      |                       |                         |              | PAD       |                 |               |

| 18      | _                     | —                       | —            | GE_SDDQ24 | L               | I             |

|                        |             |                                                         |         | Pin                   | No.                         |         |

|------------------------|-------------|---------------------------------------------------------|---------|-----------------------|-----------------------------|---------|

| Module                 | Pin Name    | Function                                                | LQFP176 | LQFP120<br>Ex-LQFP120 | LQFP120<br>(S6E2D55GJ<br>A) | FBGA161 |

|                        | I2SMCLK0_0  | I <sup>2</sup> S ch.0 external clock pin                | 6       | 2                     | 2                           | C3      |

|                        | I2SDO0_0    | I <sup>2</sup> S ch.0 serial transition data output pin | 7       | 3                     | 3                           | C2      |

| l <sup>2</sup> S 0     | I2SWS0_0    | I <sup>2</sup> S ch.0 frame synchronization signal pin  | 8       | 4                     | 4                           | D3      |

|                        | I2SDI0_0    | I <sup>2</sup> S ch.0 serial received data input pin    | 9       | 5                     | 5                           | D2      |

|                        | I2SCK0_0    | I <sup>2</sup> S ch.0 bit clock pin                     | 10      | 6                     | 6                           | D1      |

|                        | I2SMCLK1_0  | I <sup>2</sup> S ch.1 external clock pin                | 51      | 33                    | 33                          | M3      |

|                        | I2SDO1_0    | I <sup>2</sup> S ch.1 serial transition data output pin | 52      | 34                    | 34                          | L4      |

| l <sup>2</sup> S 1     | I2SWS1_0    | I <sup>2</sup> S ch.1 frame synchronization signal pin  | 53      | 35                    | 35                          | M4      |

|                        | I2SDI1_0    | I <sup>2</sup> S ch.1 serial received data input pin    | 54      | 36                    | 36                          | K5      |

|                        | I2SCK1_0    | I <sup>2</sup> S ch.1 bit clock pin                     | 55      | 37                    | 37                          | L5      |

|                        | GE_SPCK     | SPI clock output pin                                    | 34      | 20                    | -                           | J1      |

|                        | GE_SPDQ0    |                                                         | 35      | 21                    | -                           | K1      |

| GDC                    | GE_SPDQ1    |                                                         | 38      | 24                    | -                           | J2      |

| High-Speed<br>Quad SPI | GE_SPDQ2    | SPI data input / output pin                             | 39      | 25                    | -                           | J3      |

|                        | GE_SPDQ3    |                                                         | 36      | 22                    | -                           | H2      |

|                        | GE_SPCSX0   | SPI chip select output pin                              | 37      | 23                    | -                           | H3      |

|                        | GE_HBCK     | HBI clock output pin                                    | 34      | 20                    | -                           | J1      |

|                        | GE_HBDQ0    |                                                         | 36      | 22                    | -                           | H2      |

|                        | GE_HBDQ1    |                                                         | 37      | 23                    | -                           | H3      |

|                        | GE_HBDQ2    |                                                         | 38      | 24                    | -                           | J2      |

|                        | GE_HBDQ3    |                                                         | 39      | 25                    | -                           | J3      |

|                        | GE_HBDQ4    | HBI data input / output pin                             | 40      | 26                    | -                           | K2      |

|                        | GE_HBDQ5    |                                                         | 41      | 27                    | -                           | K3      |

| GDC                    | GE_HBDQ6    |                                                         | 42      | 28                    | -                           | L2      |

| HyperBus I/F           | GE_HBDQ7    |                                                         | 43      | 29                    | -                           | L3      |

|                        | GE_HBCSX0   | LIDI ship a last autout sin                             | 35      | 21                    | -                           | K1      |

|                        | GE_HBCSX1   | HBI chip select output pin                              | 12      | 8                     | -                           | E4      |

|                        | GE_HBRWDS   | HBI RWDS input / output pin                             | 33      | 19                    | -                           | G2      |

|                        | GE_HBRESETX | HBI hardware reset output pin                           | 25      | 15                    | -                           | F3      |

|                        | GE_HBINTX   | HBI interrupt input pin                                 | 26      | 16                    | -                           | F2      |

|                        | GE_HBRSTOX  | HBI reset input pin                                     | 27      | 17                    | -                           | F1      |

|                        | GE_HBWPX    | HBI write protect output pin                            | 28      | 18                    | -                           | G3      |

|               |          |                                                                                       |         | Pin                   | No.                         |         |

|---------------|----------|---------------------------------------------------------------------------------------|---------|-----------------------|-----------------------------|---------|

| Module        | Pin Name | Function                                                                              | LQFP176 | LQFP120<br>Ex-LQFP120 | LQFP120<br>(S6E2D55GJ<br>A) | FBGA161 |

| VBAT<br>Power | VBAT     | VBAT power supply pin.<br>Backup power supply (battery etc.) and system power supply. | 81      | 53                    | 53                          | M9      |

| Analog<br>GND | AVSS     | A/D converter GND pin                                                                 | 91      | 63                    | 63                          | K12     |

| C Pin         | С        | Power supply stabilization capacity pin                                               | 60      | 38                    | 38                          | N2      |

## Note:

While this device contains a Test Access Port (TAP) based on the IEEE 1149.1-2001 JTAG standard, it is not fully compliant to all requirements of that standard. This device may contain a 32-bit device ID that is the same as the 32-bit device ID in other devices with different functionality. The TAP pins may also be configurable for purposes other than access to the TAP controller.

## 12.3 DC Characteristics

# 12.3.1 Current Rating

Table 12-2 Typical and Maximum Current Consumption in Normal Operation (PLL), Code Running from Flash Memory (Flash Accelerator Mode and Trace Buffer Function Enabled)

|                 |        | Pin   |            |         | Frequency*4 | Vá                | alue              |               |                     |  |  |  |  |         |     |     |    |

|-----------------|--------|-------|------------|---------|-------------|-------------------|-------------------|---------------|---------------------|--|--|--|--|---------|-----|-----|----|

| Parameter       | Symbol | Name  | Condition  | IS      | (MHz)       | Typ* <sup>1</sup> | Max* <sup>2</sup> | Unit          | Remarks             |  |  |  |  |         |     |     |    |

|                 |        |       |            |         | 160 MHz     | 182               | 279               | mA            |                     |  |  |  |  |         |     |     |    |

|                 |        |       |            |         |             |                   |                   |               |                     |  |  |  |  | 144 MHz | 176 | 270 | mA |

|                 |        |       |            | 120 MHz | 167         | 256               | mA                |               |                     |  |  |  |  |         |     |     |    |

|                 |        |       | Normal     |         | 100 MHz     | 159               | 244               | mA            | *3                  |  |  |  |  |         |     |     |    |

|                 |        |       | operation  | *5      | 80 MHz      | 151               | 233               | mA            | When all peripheral |  |  |  |  |         |     |     |    |

|                 |        | *6,*7 | 5          | 60 MHz  | 143         | 221               | mA                | clocks are ON |                     |  |  |  |  |         |     |     |    |

|                 |        |       | (PLL)      |         | 40 MHz      | 136               | 210               | mA            | GDC clock 160 MHz   |  |  |  |  |         |     |     |    |

|                 |        |       |            |         | 20 MHz      | 128               | 199               | mA            |                     |  |  |  |  |         |     |     |    |

| Dower           |        |       |            |         | 8 MHz       | 123               | 191               | mA            |                     |  |  |  |  |         |     |     |    |

| Power<br>supply | lcc    | VCC   |            |         | 4 MHz       | 122               | 190               | mA            |                     |  |  |  |  |         |     |     |    |

| current         | ICC    | VCC   |            |         | 160 MHz     | 43                | 117               | mA            |                     |  |  |  |  |         |     |     |    |

|                 |        |       |            |         | 144 MHz     | 39                | 112               | mA            |                     |  |  |  |  |         |     |     |    |

|                 |        |       |            |         | 120 MHz     | 34                | 106               | mA            |                     |  |  |  |  |         |     |     |    |

|                 |        |       | Normal     |         | 100 MHz     | 29                | 100               | mA            | *3                  |  |  |  |  |         |     |     |    |

|                 |        |       | operation, | *5      | 80 MHz      | 24                | 95                | mA            | When all peripheral |  |  |  |  |         |     |     |    |

|                 |        |       | *6,*7      | Ŭ       | 60 MHz      | 20                | 90                | mA            | clocks are OFF      |  |  |  |  |         |     |     |    |

|                 |        |       | (PLL)      |         | 40 MHz      | 15                | 84                | mA            |                     |  |  |  |  |         |     |     |    |

|                 |        |       |            | [       | 20 MHz      | 10                | 78                | mA            |                     |  |  |  |  |         |     |     |    |

|                 |        |       |            |         | 8 MHz       | 7                 | 74                | mA            |                     |  |  |  |  |         |     |     |    |

|                 |        |       |            |         | 4 MHz       | 6                 | 73                | mA            |                     |  |  |  |  |         |     |     |    |

\*1: T<sub>A</sub>=+25°C, V<sub>CC</sub>=3.3 V

\*2: TJ=+125°C, Vcc=3.6 V

\*3: When all ports are fixed.

\*4: Frequency is a value of HCLK. PCLK0=PCLK1=PCLK2=HCLK/2

\*5: When operating flash accelerator mode and trace buffer function (FRWTR.RWT = 10, FBFCR.BE = 1)

\*6: Data access is nothing to main flash memory and VFLASH memory

\*7: When using the crystal oscillator of 4 MHz (including the current consumption of the oscillation circuit)

# Table 12-5 Typical and Maximum Current Consumption in Normal Operation (other than PLL), Code with Data Accessing Running from Flash Memory (Flash 0 Wait-cycle Mode and Read Access 0 Wait)

|                 |                               | Pin      |                                            |             | Frequency*4 | Va    | Value             |                                             |                                                                 |

|-----------------|-------------------------------|----------|--------------------------------------------|-------------|-------------|-------|-------------------|---------------------------------------------|-----------------------------------------------------------------|

| Parameter       | Symbol                        | Name     | Condition                                  | IS          | (MHz)       | Typ*1 | Max* <sup>2</sup> | Unit                                        | Remarks                                                         |

|                 |                               |          | Normal<br>operation,<br>*6,*8<br>(built-in | *5          | 4 MHz       | 110   | 181               | mA                                          | *3<br>When all peripheral<br>clocks are ON<br>GDC clock 160 MHz |

|                 |                               |          | High-<br>speed CR)                         |             |             | 4.1   | 74                | mA                                          | *3<br>When all peripheral<br>clocks are OFF                     |

| Power<br>supply |                               | VCC      | VCC Normal operation ,                     |             | 32 kHz      | 0.7   | 76.65             | mA                                          | *3<br>When all peripheral<br>clocks are ON                      |

| current         |                               |          | *6,*7,*8<br>(Sub<br>oscillation)           | *5          |             | 0.69  | 71.65             | mA                                          | *3<br>When all peripheral<br>clocks are OFF                     |

|                 |                               | operatio | Normal<br>operation ,<br>*6,*8             | operation , | 100 kHz     | 0.74  | 88.65             | mA                                          | *3<br>When all peripheral<br>clocks are ON                      |

|                 | (built-in<br>Low-speed<br>CR) |          | 5                                          |             | 0.73        | 74.65 | mA                | *3<br>When all peripheral<br>clocks are OFF |                                                                 |

\*1: T<sub>A</sub>=+25°C, V<sub>CC</sub>=3.3 V

\*2: TJ=+125°C, Vcc=3.6 V

\*3: When all ports are fixed.

\*4: Frequency is a value of HCLK. PCLK0=PCLK1=PCLK2=HCLK/2

\*5: When operating flash 0 wait-cycle mode and read access 0 wait (FRWTR.RWT = 00, FSYNDN.SD = 000)

\*6: With data access to a main flash memory.

\*7: When using the crystal oscillator of 32 kHz (including the current consumption of the oscillation circuit)

\*8: Data access is nothing to VFLASH memory

| 12.4.4 Operating Conditions of Main PLL (In the Case of Using Main Clock f | or Input Clock of PLL) |

|----------------------------------------------------------------------------|------------------------|

|----------------------------------------------------------------------------|------------------------|

$(V_{CC} = 2.7V \text{ to } 3.6V, V_{SS} = 0V)$

| Parameter                                                   | Symbol  | Value |     |     | Unit       | Remarks |

|-------------------------------------------------------------|---------|-------|-----|-----|------------|---------|

| Farameter                                                   | Symbol  | Min   | Тур | Max | Onic       | Remarks |

| PLL oscillation stabilization wait time*1<br>(LOCK UP time) | tlock   | 100   | -   | -   | μs         |         |

| PLL input clock frequency                                   | fplli   | 4     | -   | 16  | MHz        |         |

| PLL multiplication rate                                     | -       | 13    | -   | 100 | multiplier |         |

| PLL macro oscillation clock frequency                       | fpllo   | 200   | -   | 400 | MHz        |         |

| Main PLL clock frequency*2                                  | fclkpll | -     | -   | 200 | MHz        |         |

\*1: Time from when the PLL starts operating until the oscillation stabilizes.

\*2: For more information about Main PLL clock (CLKPLL), see Chapter 2-1: Clock in FM4 Family Peripheral Manual Main part (002-04856).

12.4.5 Operating Conditions of USB/PS/GDC PLL (In the Case of Using Main Clock for Input Clock of PLL) (V<sub>CC</sub> = 2.7V to 3.6V, V<sub>SS</sub> = 0V)

| Parameter                                                   | Symbol              |     | Value |            | Unit       | Remarks                           |

|-------------------------------------------------------------|---------------------|-----|-------|------------|------------|-----------------------------------|

| Falameter                                                   | Symbol              | Min | Тур   | Max        | Unit       | Remarks                           |

| PLL oscillation stabilization wait time*1<br>(LOCK UP time) | t <sub>LOCK</sub>   | 100 | -     | -          | μs         |                                   |

| PLL input clock frequency                                   | f <sub>PLLI</sub>   | 4   | -     | 16         | MHz        |                                   |

| PLL multiplication rate                                     | -                   | 13  | -     | 100        | multiplier |                                   |

| PLL macro oscillation clock frequency                       | f <sub>PLLO</sub>   | 200 | -     | 400<br>384 | MHz<br>MHz | USB/GDC<br>I <sup>2</sup> S       |

| USB clock frequency *2                                      | f <sub>CLKPLL</sub> | -   | -     | 50         | MHz        | After the M frequency division    |

| I <sup>2</sup> S clock frequency *3                         | fclkpll             | -   | -     | 12.288     | MHz        | After the M<br>frequency division |

| GDC clock frequency *4                                      | fclkpll             | -   | -     | 160        | MHz        | After divided by<br>GDC part      |

\*1: Time from when the PLL starts operating until the oscillation stabilizes.

\*2: For more information about USB clock, see Chapter 2-2: USB Clock Generation in FM4 Family Peripheral Manual Communication Macro part (002-04862).

\*3: For more information about I<sup>2</sup>S clock, see Chapter 7-1: I<sup>2</sup>S Clock Generation in FM4 Family Peripheral Manual Communication Macro part (002-04862).

\*4: For more information about GDC clock, see FM4 Family Peripheral Manual GDC part (002-04917).

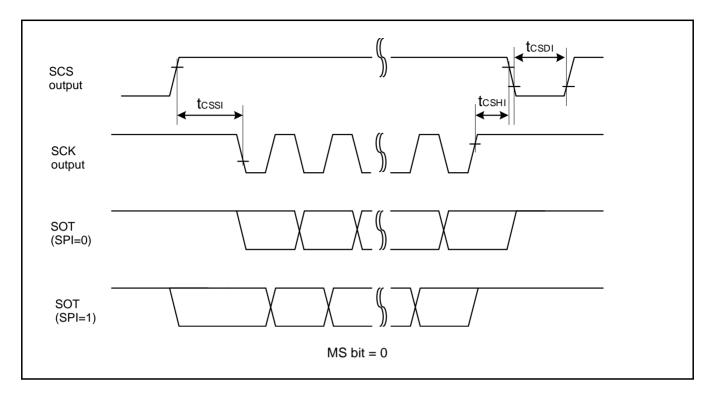

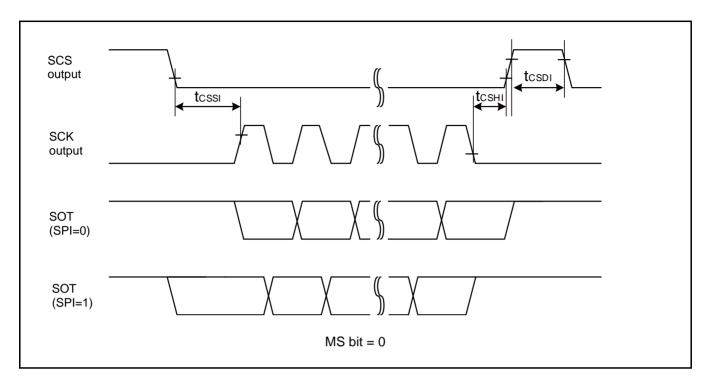

# When Using Synchronous Serial Chip Select (SCINV = 1, CSLVL=1)

$(V_{CC} = 2.7V \text{ to } 3.6V, V_{SS} = 0V)$

| Parameter                                            | Symbol            | Conditions                        | Valu                       | Unit           |      |

|------------------------------------------------------|-------------------|-----------------------------------|----------------------------|----------------|------|

| Faranielei                                           | Symbol            | Conditions                        | Min                        | Max            | Unit |

| SCS↓→SCK↑ setup time                                 | t <sub>CSSI</sub> |                                   | (*1)-50                    | (*1)+0         | ns   |

| SCK↓→SCS↑ hold time                                  | tсsнi             | Internal shift<br>clock operation | (*2)+0                     | (*2)+50        | ns   |

| SCS deselect time                                    | tcsDI             | electropolation                   | (*3)-50+5t <sub>CYCP</sub> | (*3)+50+5tcycp | ns   |

| $SCS \downarrow \rightarrow SCK \uparrow$ setup time | tcsse             |                                   | 3tcycp+30                  | -              | ns   |

| SCK↓→SCS↑ hold time                                  | tcshe             |                                   | 0                          | -              | ns   |

| SCS deselect time                                    | t <sub>CSDE</sub> | External shift<br>clock operation | 3t <sub>CYCP</sub> +30     | -              | ns   |

| SCS↓→SOT delay time                                  | tDSE              |                                   | -                          | 40             | ns   |

| SCS↑→SOT delay time                                  | tDEE              |                                   | 0                          | -              | ns   |

(\*1): CSSU bit valuexserial chip select timing operating clock cycle [ns]

(\*2): CSHD bit valuexserial chip select timing operating clock cycle [ns]

(\*3): CSDS bit valuexserial chip select timing operating clock cycle [ns]

## Notes:

- t<sub>CYCP</sub> indicates the APB bus clock cycle time.

- About the APB bus number which multi-function serial is connected to, see 8. Block Diagram in this data sheet.

- About CSSU, CSHD, CSDS, serial chip select timing operating clock, see FM4 Family Peripheral Manual Main part (002-04856).

- When the external load capacitance  $C_L = 30 \text{ pF}$ .

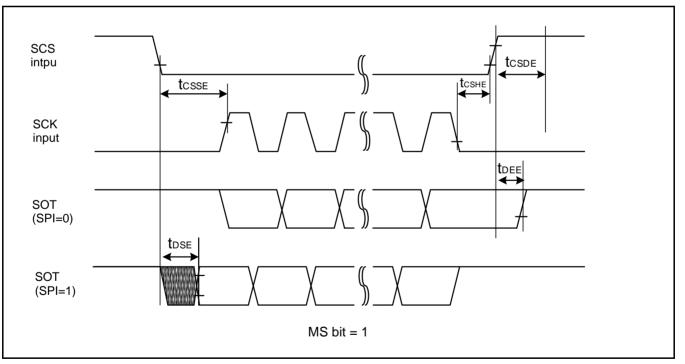

# High-Speed Synchronous Serial (SPI = 0, SCINV = 1)

$(V_{CC} = 2.7V \text{ to } 3.6V, V_{SS} = 0V)$

| <b>B</b>                   |                    |               |                                   | Valu                   | 11   |      |

|----------------------------|--------------------|---------------|-----------------------------------|------------------------|------|------|

| Parameter                  | Symbol             | Pin Name      | Conditions                        | Min                    | Max  | Unit |

| Serial clock cycle time    | tscyc              | SCKx          |                                   | 4t <sub>CYCP</sub>     | -    | ns   |

| SCK↑→SOT delay time        | tshovi             | SCKx,<br>SOTx | Internal shift clock              | - 10                   | + 10 | ns   |

| CIN CCK Leasture time      | 4                  | SCKx,         | Internal shift clock<br>operation | 14                     |      |      |

| SIN→SCK↓ setup time        | tı∨s∟ı             | SINx          | operation                         | 12.5*                  | -    | ns   |

| SCK↓→SIN hold time         | tsLixi             | SCKx,<br>SINx |                                   | 5                      | -    | ns   |

| Serial clock L pulse width | tslsh              | SCKx          |                                   | 2t <sub>CYCP</sub> - 5 | -    | ns   |

| Serial clock H pulse width | tshsl              | SCKx          |                                   | tcycp + 10             | -    | ns   |

| SCK↑→SOT delay time        | t <sub>SHOVE</sub> | SCKx,<br>SOTx |                                   | -                      | 15   | ns   |

| SIN→SCK↓ setup time        | tivsle             | SCKx,<br>SINx | External shift clock<br>operation | 5                      | -    | ns   |

| SCK↓→SIN hold time         | t <sub>SLIXE</sub> | SCKx,<br>SINx |                                   | 5                      | -    | ns   |

| SCK falling time           | tF                 | SCKx          |                                   | -                      | 5    | ns   |

| SCK rising time            | t <sub>R</sub>     | SCKx          |                                   | -                      | 5    | ns   |

## Notes:

- The above characteristics apply to CLK synchronous mode.

- tcycp indicates the APB bus clock cycle time.

About the APB bus number which multi-function serial is connected to, see 8. Block Diagram in this data sheet.

- These characteristics only guarantee the following pins. SIN6\_0, SOT6\_0, SCK6\_0, SCS60\_0

- When the external load capacitance  $C_L = 30 \text{ pF}$ . (For \*, when  $C_L = 10 \text{ pF}$ )

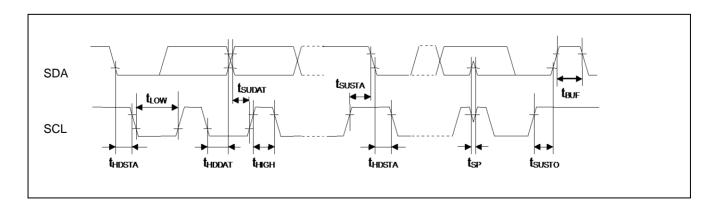

# Fast Mode Plus (Fm+)

| $(V_{CC} =$ | 2.7V | to | 3.6V, | $V_{SS}$ | = | 0V) |

|-------------|------|----|-------|----------|---|-----|

|-------------|------|----|-------|----------|---|-----|

| Parameter                                                                          | Symbol             | Conditions                                             | Fast Mode I            | Fast Mode Plus (Fm+)*6 |      | Remarks |

|------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------|------------------------|------------------------|------|---------|

|                                                                                    | Symbol             | Conditions                                             | Min                    | Max                    | Unit | Remarks |

| SCL clock frequency                                                                | fscl               |                                                        | 0                      | 1000                   | kHz  |         |

| (Repeated) Start condition hold time SDA $\downarrow \rightarrow$ SCL $\downarrow$ | <b>t</b> hdsta     |                                                        | 0.26                   | -                      | μs   |         |

| SCL clock L width                                                                  | tLOW               |                                                        | 0.5                    | -                      | μs   |         |

| SCL clock H width                                                                  | tніgн              |                                                        | 0.26                   | -                      | μs   |         |

| (Repeated) Start condition setup time SCL $\uparrow \rightarrow$ SDA $\downarrow$  | <b>t</b> susta     | C <sub>L</sub> = 30 pF,<br>R = (Vp/I <sub>OL</sub> )*1 | 0.26                   | -                      | μs   |         |

| Data hold time SCL $\downarrow \rightarrow$ SDA $\downarrow \uparrow$              | <b>t</b> hddat     |                                                        | 0                      | 0.45 <sup>*2, *3</sup> | μs   |         |

| Data setup time SDA $\downarrow \uparrow \rightarrow$ SCL $\uparrow$               | t <sub>SUDAT</sub> |                                                        | 50                     | -                      | ns   |         |

| Stop condition setup time SCL $\uparrow \rightarrow$ SDA $\uparrow$                | tsusto             |                                                        | 0.26                   | -                      | μs   |         |

| Bus free time between<br>Stop condition and Start condition                        | t <sub>BUF</sub>   |                                                        | 0.5                    | -                      | μs   |         |

| Noise filter                                                                       | tsP                | 60 MHz ≤<br>t <sub>CYCP</sub> <80 MHz                  | 6 t <sub>CYCP</sub> *4 | -                      | ns   | *5      |

|                                                                                    | LSP                | 80 MHz ≤<br>t <sub>CYCP</sub> ≤100 MHz                 | 8 t <sub>CYCP</sub> *4 | -                      | ns   | *5      |

\*1: R and C<sub>L</sub> represent the pull-up resistance and load capacitance of the SCL and SDA lines, respectively. Vp indicates the power supply voltage of the pull-up resistance and I<sub>OL</sub> indicates V<sub>OL</sub> guaranteed current.

\*2: The maximum t<sub>HDDAT</sub> must satisfy that it does not extend at least L period (t<sub>LOW</sub>) of device's SCL signal.

- \*3: A Fast mode I<sup>2</sup>C bus device can be used on a Standard mode I<sup>2</sup>C bus system as long as the device satisfies the requirement of "t<sub>SUDAT</sub> ≥ 250 ns".

- \*4: tcycP is the APB bus clock cycle time. About the APB bus number that I<sup>2</sup>C is connected to, see 8. Block Diagram in this data sheet. To use fast mode plus (Fm+), set the peripheral bus clock at 64 MHz or more.

- \*5: The noise filter time can be changed by register settings. Change the number of the noise filter steps according to APB bus clock frequency.

- \*6: When using fast mode plus (Fm+), set the I/O pin to the mode corresponding to I<sup>2</sup>C Fm+ in the EPFR register. See Chapter 12 : I/O Port in "FM4 Family Peripheral Manual Main part (002-04856)" for the details.

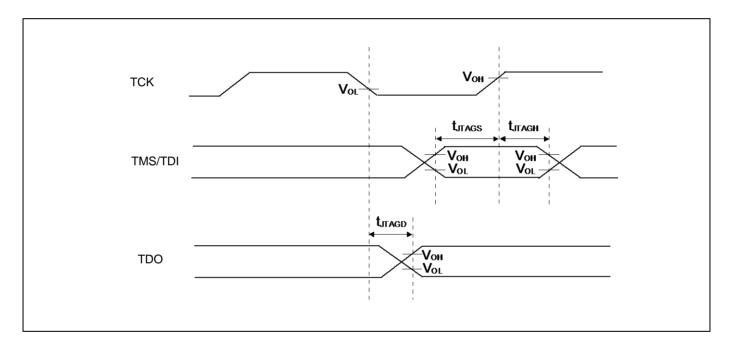

# 12.4.17 JTAG Timing

(V<sub>CC</sub> = 2.7V to 3.6V, V<sub>SS</sub> = 0V)

| Parameter           | Symbol             | Pin Name Conditions Value | lue        | Unit | Remarks |      |         |

|---------------------|--------------------|---------------------------|------------|------|---------|------|---------|

|                     | Symbol             | FIII Naille               | Conditions | Min  | Max     | Onit | Remarks |

| TMS, TDI setup time | t <sub>JTAGS</sub> | TCK,<br>TMS, TDI          | -          | 15   | -       | ns   |         |

| TMS, TDI hold time  | tjtagh             | TCK,<br>TMS, TDI          | -          | 15   | -       | ns   |         |

| TDO delay time      | tjtagd             | TCK,<br>TDO               | -          | -    | 45      | ns   |         |

## Note:

- When the external load capacitance  $C_L$ = 30 pF.

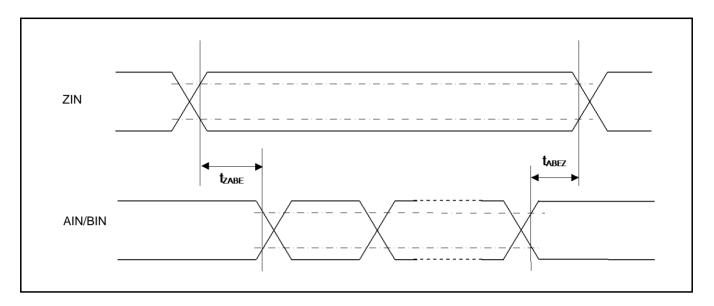

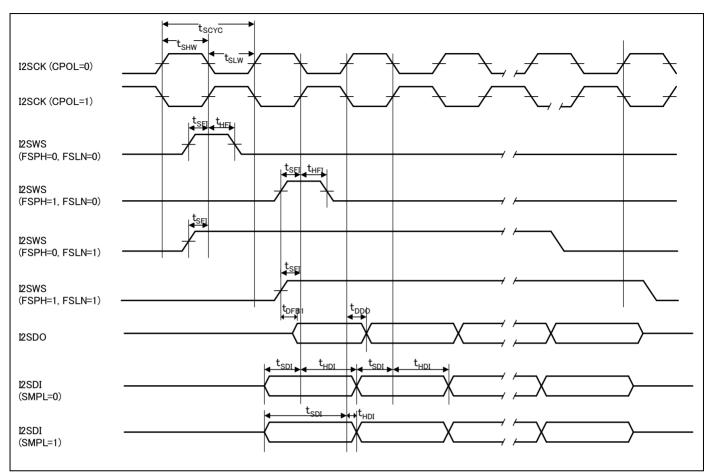

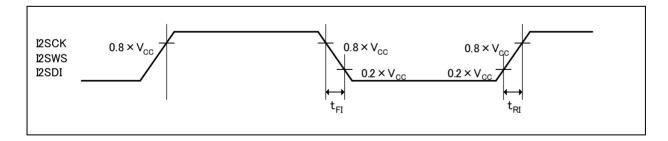

## Notes:

- See Chapter 7-2: PS(Inter-IC Sound bus)Interface in FM4 Family Peripheral Manual Communication part (002-04862) for the details of FSPH, FSLN, SMPL

- I2SCK input is selectable polarity by CPOL bit of CNTREG register

## 12.4.21 GDC: High-Speed Quad SPI Timing

(V\_{CC} = 3.0V to 3.6V, V\_{SS} = 0V)

| Parameter                                         | Symbol         | Pin Name                           | Conditions             | Value              | Unit |      |

|---------------------------------------------------|----------------|------------------------------------|------------------------|--------------------|------|------|

| Farameter                                         | Symbol         | Fin Name                           | Conditions             | Min                | Max  | Unit |

| Serial clock<br>frequency                         | tsсусм         | GE_SPCK                            |                        | -                  | 80   | MHz  |

| Enabled CS→<br>CLK Starting Time<br>(mode0/mode2) | tos∟sĸo2       |                                    |                        | 1.5×tsсусм – 4.25  | -    | ns   |

| Enabled CS→<br>CLK Starting Time<br>(mode1/mode3) | tos∟sĸ13       | GE_SPCK,                           |                        | tsсүсм – 4.25      | -    | ns   |

| CLK Last→<br>Disabled CS Time<br>(mode0/mode2)    | tosksL02       | GE_SPCSX0                          | C∟=20 pF               | tsсүсм             | -    | ns   |

| CLK Last→<br>Disabled CS Time<br>(mode1/mode3)    | tosksl13       |                                    |                        | <b>1.5×t</b> sсусм | -    | ns   |

| SIO Data output time                              | tosdat         | GE_SPCK,<br>GE_SPDQ0,              |                        | -1.25              | 4.25 | ns   |

| SIO Setup                                         | <b>t</b> DSSET | GE_SPDQ1,<br>GE_SPDQ2,<br>GE_SPDQ3 | GE_SPDQ1,<br>GE_SPDQ2, | 4                  | -    | ns   |

| SIO Hold                                          | tsdhold        | 0E_0FDQ3                           |                        | 0.5×tsсусм         | -    | ns   |

## Note:

- See Chapter 8-3: High-Speed Quad SPI controller in FM4 Family Peripheral Manual Communication part (002-04862) for the detail of RTM mode.

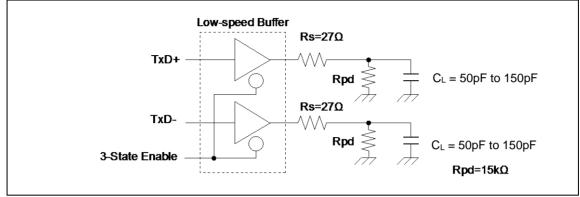

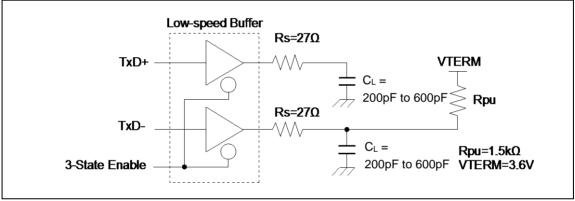

## ■Low-speed load (Upstream port load) - Reference 1

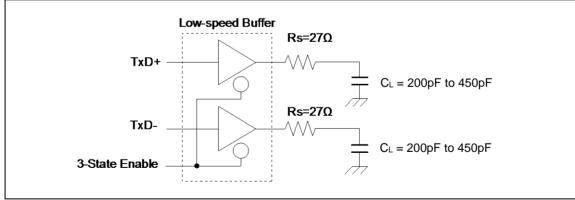

## ■Low-speed load (Downstream port load) - Reference 2

## ■Low-speed load (Compliance load)

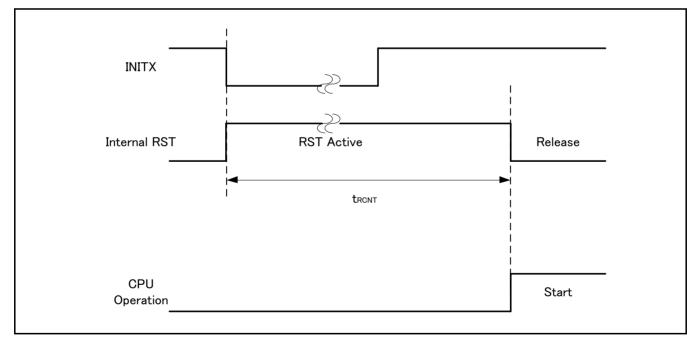

## 12.10.2 Recovery Cause: Reset

The time from reset release to the program operation start is shown.

# **Recovery Count Time**

(Vcc = 2.7V to 3.6V, Vss = 0V)

| _                                                             |               | Va  | Value |      |                       |  |

|---------------------------------------------------------------|---------------|-----|-------|------|-----------------------|--|

| Parameter                                                     | Symbol        | Тур | Max*  | Unit | Remarks               |  |

| Sleep mode                                                    |               | 155 | 266   | μs   |                       |  |

| High-speed CR Timer mode<br>Main Timer mode<br>PLL Timer mode |               | 155 | 266   | μs   |                       |  |

| Low-speed CR timer mode                                       |               | 315 | 567   | μs   |                       |  |

| Sub timer mode                                                | <b>t</b> ront | 315 | 567   | μs   |                       |  |

| RTC mode<br>Stop mode                                         |               | 315 | 567   | μs   |                       |  |

| Deep standby RTC mode                                         |               | 336 | 667   | μs   | without RAM retention |  |

| Deep standby Stop mode                                        |               | 336 | 667   | μs   | with RAM retention    |  |

\*: The maximum value depends on the built-in CR accuracy.

# Example of Standby Recovery Operation (when in INITX Recovery)

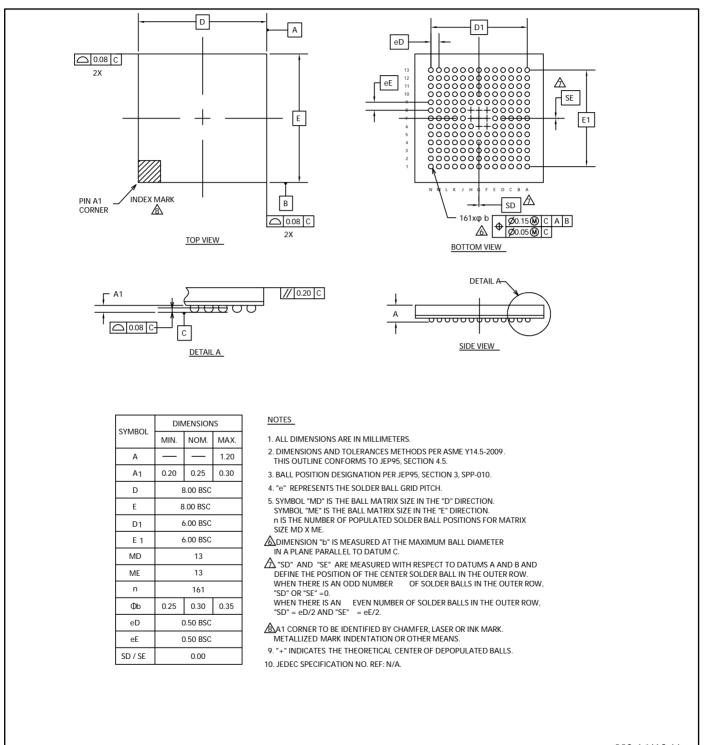

| Package Type | Package Code |  |  |  |

|--------------|--------------|--|--|--|

| FBGA 161     | FDJ 161      |  |  |  |

002-16413 \*\*

PACKAGE OUTLINE, 161 BALL FBGA 8.00X8.00X1.20 MM FDJ161 REV\*\*