# E·XFL

### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 56800E                                                                |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 23                                                                    |

| Program Memory Size        | 12KB (6K x 16)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 16                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 15x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 28-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f8002vwlr |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1<br>2 | Block    | 6F8006/MC56F8002 Family Configuration           |

|--------|----------|-------------------------------------------------|

| 3      |          | view                                            |

|        | 3.1      | 56F8006/56F8002 Features                        |

|        | 3.2      | Award-Winning Development Environment           |

|        | 3.3      | Architecture Block Diagram                      |

|        | 3.4      | Product Documentation                           |

| 4      | <u> </u> | al/Connection Descriptions                      |

|        | 4.1      | Introduction                                    |

|        | 4.2      | Pin Assignment                                  |

| _      | 4.3      | 56F8006/56F8002 Signal Pins                     |

| 5      |          | ory Maps                                        |

|        | 5.1      | Introduction                                    |

|        | 5.2      | Program Map                                     |

|        | 5.3      | Data Map                                        |

|        | 5.4      | Interrupt Vector Table and Reset Vector         |

|        | 5.5      | Peripheral Memory-Mapped Registers              |

| ~      | 5.6      | EOnCE Memory Map                                |

| 6      |          | eral System Control Information                 |

|        | 6.1      | Overview                                        |

|        | 6.2      | Power Pins                                      |

|        | 6.3      | Reset                                           |

|        | 6.4      | On-chip Clock Synthesis                         |

|        | 6.5      | Interrupt Controller                            |

|        | 6.6      | System Integration Module (SIM)                 |

|        | 6.7      | PWM, PDB, PGA, and ADC Connections              |

|        | 6.8      | Joint Test Action Group (JTAG)/Enhanced On-Chip |

| _      | •        | Emulator (EOnCE)                                |

| 7      |          | rity Features                                   |

|        | 7.1      | Operation with Security Enabled40               |

|        | 7.2      | Flash Access Lock and Unlock Mechanisms         |

| ~      | 7.3      | Product Analysis                                |

| 8      | Spec     | ifications41                                    |

|    | 8.1    | General Characteristics                                  |

|----|--------|----------------------------------------------------------|

|    | 8.2    | Absolute Maximum Ratings                                 |

|    | 8.3    | Thermal Characteristics                                  |

|    | 8.4    | Recommended Operating Conditions                         |

|    | 8.5    | DC Electrical Characteristics                            |

|    | 8.6    | Supply Current Characteristics                           |

|    | 8.7    | Flash Memory Characteristics                             |

|    | 8.8    | External Clock Operation Timing                          |

|    | 8.9    | Phase Locked Loop Timing                                 |

|    | 8.10   | Relaxation Oscillator Timing                             |

|    | 8.11   | Reset, Stop, Wait, Mode Select, and Interrupt Timing. 56 |

|    | 8.12   | External Oscillator (XOSC) Characteristics               |

|    | 8.13   | AC Electrical Characteristics                            |

|    | 8.14   | COP Specifications                                       |

|    | 8.15   | PGA Specifications                                       |

|    | 8.16   | ADC Specifications                                       |

|    | 8.17   | HSCMP Specifications                                     |

|    | 8.18   | Optimize Power Consumption                               |

| 9  | Desic  | In Considerations                                        |

|    | 9.1    | Thermal Design Considerations                            |

|    | 9.2    | Electrical Design Considerations                         |

|    | 9.3    | Ordering Information                                     |

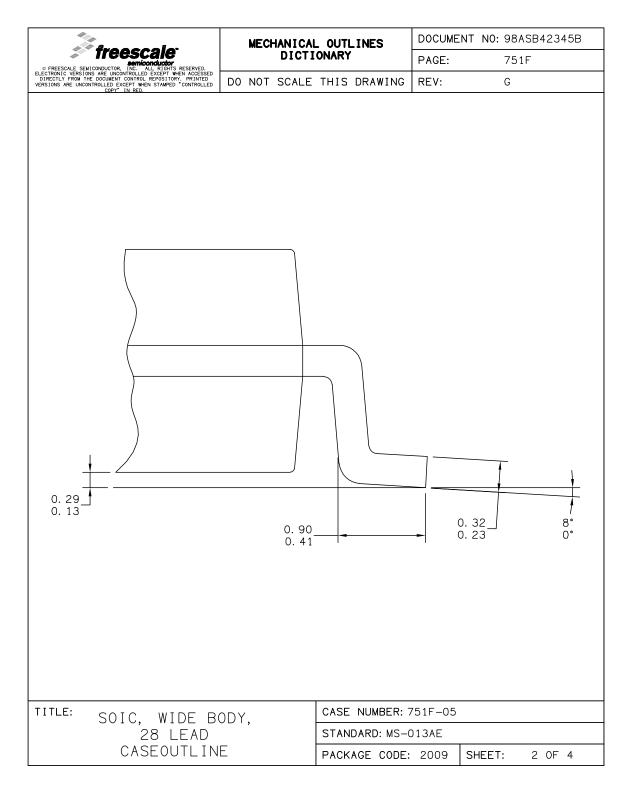

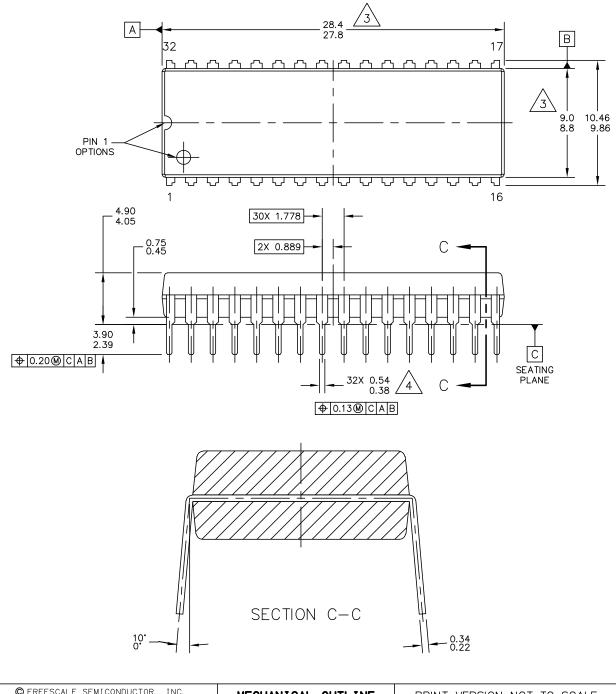

| 10 | Packa  | age Mechanical Outline Drawings                          |

|    | 10.1   | 28-pin SOIC Package                                      |

|    | 10.2   | 32-pin LQFP                                              |

|    | 10.3   | 48-pin LQFP                                              |

|    | 10.4   | 32-Pin PSDIP                                             |

| 11 | Revis  | sion History                                             |

| Ap | oendix |                                                          |

|    | Interr | upt Vector Table                                         |

| Ар | oendix |                                                          |

|    | Perip  | heral Register Memory Map and Reset Value                |

NP

**Block Diagram**

# 2 Block Diagram

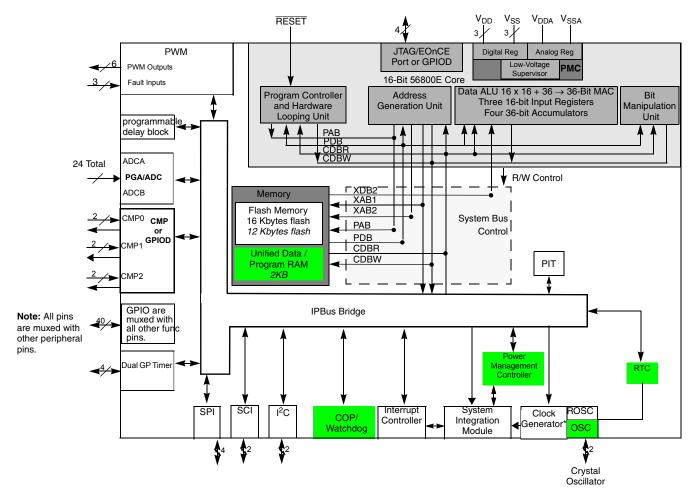

Figure 1 shows a top-level block diagram of the MC56F8006/MC56F8002 digital signal controller. Package options for this family are described later in this document. Italics indicate a 56F8002 device parameter.

Figure 1. MC56F8006/MC56F8002 Block Diagram

# 3 Overview

# 3.1 56F8006/56F8002 Features

# 3.1.1 Core

- Efficient 16-bit 56800E family digital signal controller (DSC) engine with dual Harvard architecture

- As many as 32 million instructions per second (MIPS) at 32 MHz core frequency

- 155 basic instructions in conjunction with up to 20 address modes

- Single-cycle 16 × 16-bit parallel multiplier-accumulator (MAC)

- Four 36-bit accumulators, including extension bits

- 32-bit arithmetic and logic multi-bit shifter

### Overview

- Four programmable fault inputs with programmable digital filter

- Double-buffered PWM registers

- Separate deadtime insertions for rising and falling edges

- Separate top and bottom pulse-width correction by means of software

- Asymmetric PWM output within both Center Aligned and Edge Aligned operation

- Separate top and bottom polarity control

- Each complementary PWM signal pair allows selection of a PWM supply source from:

- PWM generator

- Internal timers

- Analog comparator outputs

- Two independent 12-bit analog-to-digital converters (ADCs)

- 2 x 14 channel external inputs plus seven internal inputs

- Support simultaneous and software triggering conversions

- ADC conversions can be synchronized by PWM and PDB modules

- Sampling rate up to 400 KSPS for 10- or 12-bit conversion result; 470 KSPS for 8-bit conversion result

- Two 16-word result registers

- Two programmable gain amplifier (PGAs)

- Each PGA is designed to amplify and convert differential signals to a single-ended value fed to one of the ADC inputs

- 1X, 2X, 4X, 8X, 16X, or 32X gain

- Software and hardware triggers are available

- Integrated sample/hold circuit

- Includes additional calibration features:

- Offset calibration eliminates any errors in the internal reference used to generate the VDDA/2 output center point

- Gain calibration can be used to verify the gain of the overall datapath

- Both features require software correction of the ADC result

- Three analog comparators (CMPs)

- Selectable input source includes external pins, internal DACs

- Programmable output polarity

- Output can drive timer input, PWM fault input, PWM source, external pin output, and trigger ADCs

- Output falling and rising edge detection able to generate interrupts

- One dual channel 16-bit multi-purpose timer module (TMR)

- Two independent 16-bit counter/timers with cascading capability

- Up to 96 MHz operating clock

- Each timer has capture and compare and quadrature decoder capability

- Up to 12 operating modes

- Four external inputs and two external outputs

- One serial communication interface (SCI) with LIN slave functionality

- Up to 96 MHz operating clock

- Full-duplex or single-wire operation

- Programmable 8- or 9- bit data format

- Two receiver wakeup methods:

- Idle line

- Address mark

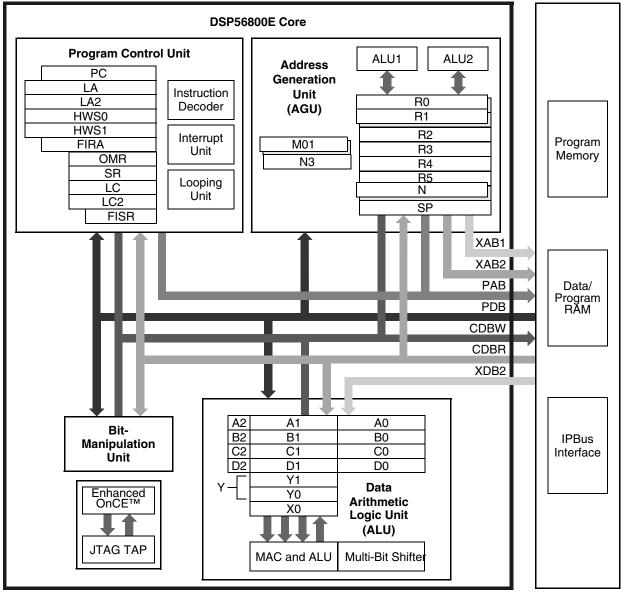

# 3.3 Architecture Block Diagram

The 56F8006/56F8002's architecture is shown in Figure 2 and Figure 3. Figure 2 illustrates how the 56800E system buses communicate with internal memories and the IPBus interface and the internal connections among each unit of the 56800E core. Figure 3 shows the peripherals and control blocks connected to the IPBus bridge. Please see the system integration module (SIM) section in the *MC56F8006 Reference Manual* for information about which signals are multiplexed with those of other peripherals.

Figure 2. 56800E Core Block Diagram

### Table 5. 56F8006/56F8002 Signal and Package Information (continued)

| Signal<br>Name        | 28<br>SOIC | 32<br>LQFP | 32<br>PSDI<br>P | 48<br>LQFP | Туре                           | State<br>During<br>Reset                | Signal Description                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|------------|------------|-----------------|------------|--------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOA3                | 17         | 24         | 20              | 36         | Input/<br>Output               | Input,<br>internal<br>pullup<br>enabled | Port A GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                            |

| (PWM3)                |            |            |                 |            | Output                         | onabiou                                 | PWM3 — The PWM channel 3.                                                                                                                                                                                                                                                                                                                                        |

| (TXD)                 |            |            |                 |            | Output                         |                                         | TXD — The SCI transmit data output or transmit/receive in single wire operation.                                                                                                                                                                                                                                                                                 |

| (EXTAL)               |            |            |                 |            | Analog<br>Input                |                                         | EXTAL — External Crystal Oscillator Input. This input can be<br>connected to a 32.768 kHz or 1–16 MHz external crystal or ceramic<br>resonator. When used to supply a source to the internal PLL, the<br>crystal/resonator must be in the 4 MHz to 8 MHz range. Tie this pin<br>low or configure as GPIO if XTAL is being driven by an external<br>clock source. |

|                       |            |            |                 |            |                                |                                         | to device pins to speed startup.                                                                                                                                                                                                                                                                                                                                 |

|                       |            |            |                 |            |                                |                                         | After reset, the default state is GPIOA3.                                                                                                                                                                                                                                                                                                                        |

| GPIOA4                | 16         | 22         | 18              | 33         | Input/<br>Output               | Input,<br>internal<br>pullup            | Port A GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                            |

| (PWM4)                |            |            |                 |            | Output                         | enabled                                 | PWM4 — The PWM channel 4.                                                                                                                                                                                                                                                                                                                                        |

| (SDA)                 |            |            |                 |            | Input/Open-<br>drain<br>Output |                                         | SDA — The I <sup>2</sup> C serial data line.                                                                                                                                                                                                                                                                                                                     |

| (FAULT1)              |            |            |                 |            | Input                          |                                         | FAULT1 — PWM fault input 1 used for disabling selected PWM outputs in cases where fault conditions originate off-chip.                                                                                                                                                                                                                                           |

| (TIN2)                |            |            |                 |            | Input                          |                                         | TIN2 — Dual timer module channel 2 input                                                                                                                                                                                                                                                                                                                         |

|                       |            |            |                 |            |                                |                                         | After reset, the default state is GPIOA4.                                                                                                                                                                                                                                                                                                                        |

| GPIOA5                | 14         | 20         | 16              | 29         | Input/<br>Output               | Input,<br>internal                      | Port A GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                            |

| (PWM5)                |            |            |                 |            | Output                         | pullup<br>enabled                       | PWM5 — The PWM channel 5.                                                                                                                                                                                                                                                                                                                                        |

| (FAULT2/<br>EXT_SYNC) |            |            |                 |            | Input/<br>Output               |                                         | FAULT2 — PWM fault input 2 used for disabling selected PWM outputs in cases where fault conditions originate off-chip.<br>EXT_SYNC — When not being used as a fault input, this pin can be used to receive a pulse to reset the PWM counter or to generate a positive pulse at the start of every PWM cycle.                                                     |

| (TIN3)                |            |            |                 |            | Input                          |                                         | TIN3 — Dual timer module channel 3 input                                                                                                                                                                                                                                                                                                                         |

|                       |            |            |                 |            |                                |                                         | After reset, the default state is GPIOA5.                                                                                                                                                                                                                                                                                                                        |

# 5.6 EOnCE Memory Map

Control registers of the EOnCE are located at the top of data memory space. These locations are fixed by the 56F800E core. These registers can also be accessed through JTAG port if flash security is not set. Table 11 lists all EOnCE registers necessary to access or control the EOnCE.

| Address                      | Register Acronym          | Register Name                                               |

|------------------------------|---------------------------|-------------------------------------------------------------|

| X:0xFF FFFF                  | OTX1/ORX1                 | Transmit Register Upper Word<br>Receive Register Upper Word |

| X:0xFF FFFE                  | OTX/ORX<br>(32 bits)      | Transmit Register<br>Receive Register                       |

| X:0xFF FFFD                  | OTXRXSR                   | Transmit and Receive Status and Control Register            |

| X:0xFF FFFC                  | OCLSR                     | Core Lock/Unlock Status Register                            |

| X:0xFF FFFB–<br>X:0xFF FFA1  |                           | Reserved                                                    |

| X:0xFF FFA0                  | OCR                       | Control Register                                            |

| X:0xFF FF9F–<br>X:0xFF FF9E  | OSCNTR<br>(24 bits)       | Instruction Step Counter                                    |

| X:0xFF FF9D                  | OSR                       | Status Register                                             |

| X:0xFF FF9C                  | OBASE                     | Peripheral Base Address Register                            |

| X:0xFF FF9B                  | OTBCR                     | Trace Buffer Control Register                               |

| X:0xFF FF9A                  | OTBPR                     | Trace Buffer Pointer Register                               |

| X:0xFF FF99–<br>X:0xFF FF98  | OTB<br>(21–24 bits/stage) | Trace Buffer Register Stages                                |

| X:0xFF FF97–<br>X:0xFF FF96  | OBCR<br>(24 bits)         | Breakpoint Unit Control Register                            |

| X:0xFF FF95–<br>X:0xFF FF94  | OBAR1<br>(24 bits)        | Breakpoint Unit Address Register 1                          |

| X:0xFF FF93–<br>X:0xFF FF92  | OBAR2 (32 bits)           | Breakpoint Unit Address Register 2                          |

| X:0xFF FF91–<br>X:0xFF FF90  | OBMSK (32 bits)           | Breakpoint Unit Mask Register 2                             |

| X:0xFF FF8F                  |                           | Reserved                                                    |

| X:0xFF FF8E                  | OBCNTR                    | EOnCE Breakpoint Unit Counter                               |

| X:0xFF FF8D                  |                           | Reserved                                                    |

| X:0xFF FF8C                  |                           | Reserved                                                    |

| X:0xFF FF8B                  |                           | Reserved                                                    |

| X:0xFF FF8A                  | OESCR                     | External Signal Control Register                            |

| X:0xFF FF89 –<br>X:0xFF FF00 |                           | Reserved                                                    |

### Table 11. EOnCE Memory Map

### Security Features

application software could communicate over a serial port, for example, to validate the authenticity of the requested access, then grant it until the next device reset. The inclusion of such a back door technique is at the discretion of the system designer.

# 7.1 Operation with Security Enabled

After you have programmed flash with the application code, or as part of the programming of the flash with the application code, the 56F8006/56F8002 can be secured by programming the security word, 0x0002, into program memory location 0x00 1FF7. This can also be effected by use of the CodeWarrior IDE menu flash lock command. This nonvolatile word keeps the device secured after reset, caused, for example, by a power-down of the device. Refer to the flash memory chapter in the *MC56F8006 Peripheral Reference Manual* for detail. When flash security mode is enabled, the 56F8006/56F8002 disables the core EOnCE debug capabilities. Normal program execution is otherwise unaffected.

# 7.2 Flash Access Lock and Unlock Mechanisms

There are several methods that effectively lock or unlock the on-chip flash.

# 7.2.1 Disabling EOnCE Access

On-chip flash can be read by issuing commands across the EOnCE port, which is the debug interface for the 56800E CPU. The TCK, TMS, TDO, and TDI pins comprise a JTAG interface onto which the EOnCE port functionality is mapped. When the device boots, the chip-level JTAG TAP (test access port) is active and provides the chip's boundary scan capability and access to the ID register, but proper implementation of flash security blocks any attempt to access the internal flash memory via the EOnCE port when security is enabled. This protection is effective when the device comes out of reset, even prior to the execution of any code at startup.

# 7.2.2 Flash Lockout Recovery Using JTAG

If the device is secured, one lockout recovery mechanism is the complete erasure of the internal flash contents, including the configuration field, thus disabling security (the protection register is cleared). This does not compromise security, as the entire contents of your secured code stored in flash are erased before security is disabled on the device on the next reset or power-up sequence.

To start the lockout recovery sequence via JTAG, the JTAG public instruction (LOCKOUT\_RECOVERY) must first be shifted into the chip-level TAP controller's instruction register. After the LOCKOUT\_RECOVERY instruction has been shifted into the instruction register, the clock divider value must be shifted into the corresponding 7-bit data register. After the data register has been updated, you must transition the TAP controller into the RUN-TEST/IDLE state for the lockout sequence to commence. The controller must remain in this state until the erase sequence is complete. Refer to the *MC56F8006 Peripheral Reference Manual* for detail, or contact Freescale.

### NOTE

After the lockout recovery sequence has completed, you must reset the JTAG-TAP controller and device to return to normal unsecured operation. Power-on reset resets both too.

# 7.2.3 Flash Lockout Recovery Using CodeWarrior

CodeWarrior can unlock a device by selecting the *Debug* menu, then selecting *DSP56800E*, followed by *Unlock Flash*. Another mechanism is also built into CodeWarrior using the device's memory configuration file. The command *"Unlock Flash on Connect 1"* in the *.cfg* file accomplishes the same task as using the *Debug* menu.

This lockout recovery mechanism is the complete erasure of the internal flash contents, including the configuration field, thus disabling security (the protection register is cleared).

Specifications

# 8.9 Phase Locked Loop Timing

### Table 25. Phase Locked Loop Timing

| Characteristic                                                                    | Symbol                 | Min | Тур | Мах  | Unit |

|-----------------------------------------------------------------------------------|------------------------|-----|-----|------|------|

| PLL input reference frequency <sup>1</sup>                                        | f <sub>ref</sub>       | 4   | 8   |      | MHz  |

| PLL output frequency <sup>2</sup>                                                 | f <sub>op</sub>        | 120 | 192 | _    | MHz  |

| PLL lock time <sup>3 4</sup>                                                      | t <sub>plls</sub>      | _   | 40  | 100  | μs   |

| Accumulated jitter using an 8 MHz external crystal as the PLL source <sup>5</sup> | J <sub>A</sub>         | _   | _   | 0.37 | %    |

| Cycle-to-cycle jitter                                                             | t <sub>jitterpll</sub> | _   | 350 | _    | ps   |

<sup>1</sup> An externally supplied reference clock should be as free as possible from any phase jitter for the PLL to work correctly. The PLL is optimized for 8 MHz input.

- <sup>2</sup> The core system clock operates at 1/6 of the PLL output frequency.

- <sup>3</sup> This is the time required after the PLL is enabled to ensure reliable operation.

- <sup>4</sup> From powerdown to powerup state at 32 MHz system clock state.

- <sup>5</sup> This is measured on the CLKO signal (programmed as system clock) over 264 system clocks at 32 MHz system clock frequency and using an 8 MHz oscillator frequency.

# 8.10 Relaxation Oscillator Timing

### Table 26. Relaxation Oscillator Timing

| Characteristic                                                                                                       | Symbol                  | Minimum | Typical     | Maximum      | Unit       |

|----------------------------------------------------------------------------------------------------------------------|-------------------------|---------|-------------|--------------|------------|

| Relaxation oscillator output frequency <sup>1</sup><br>Normal Mode<br>Standby Mode                                   | f <sub>op</sub>         | _       | 8.05<br>400 |              | MHz<br>kHz |

| Relaxation oscillator stabilization time <sup>2</sup>                                                                | t <sub>roscs</sub>      |         | 1           | 3            | ms         |

| Cycle-to-cycle jitter. This is measured on the CLKO signal (programmed prescaler_clock) over 264 clocks <sup>3</sup> | t <sub>jitterrosc</sub> | _       | 400         | _            | ps         |

| Variation over temperature –40 °C to 105 °C $^4$                                                                     |                         | _       |             | -3.0 to +2.0 | %          |

| Variation over temperature 0 °C to 105 °C <sup>5</sup>                                                               |                         | —       | _           | -2.0 to +2.0 | %          |

| Variation over temperature –40 °C to 125 °C $^4$                                                                     |                         | —       | _           | -3.5 to +3.0 | %          |

<sup>1</sup> Output frequency after factory trim.

<sup>2</sup> This is the time required from standby to normal mode transition.

<sup>3</sup> J<sub>A</sub> is required to meet QSCI requirements.

<sup>4</sup> See Figure 22. The power supply VDD must be greater than or equal to 2.6 V. Below 2.6 V, the maximum variation over the whole temperature and whole voltage range from 1.8 V to 2.6 V will be +/-16%.

<sup>5</sup> This data is only applied to devices with temperature range from -40 °C to 105 °C.

Specifications

# 8.16 ADC Specifications

| Characteristic              | Conditions                                                            | Symb              | Min                            | Typ <sup>1</sup> | Мах                            | Unit | Comment         |

|-----------------------------|-----------------------------------------------------------------------|-------------------|--------------------------------|------------------|--------------------------------|------|-----------------|

| Input voltage               |                                                                       | V <sub>ADIN</sub> | V <sub>REFL</sub> <sup>2</sup> | _                | V <sub>REFH</sub> <sup>3</sup> | V    |                 |

| Input<br>capacitance        |                                                                       | C <sub>ADIN</sub> | —                              | 4.5              | 5.5                            | pF   |                 |

| Input resistance            |                                                                       | R <sub>ADIN</sub> |                                | 5                | 7                              | kΩ   |                 |

| Analog source<br>resistance | 12-bit mode<br>f <sub>ADCK</sub> > 4 MHz<br>f <sub>ADCK</sub> < 4 MHz | R <sub>AS</sub>   |                                | _                | 2<br>5                         | kΩ   | External to MCU |

|                             | 10-bit mode<br>f <sub>ADCK</sub> > 4 MHz<br>f <sub>ADCK</sub> < 4 MHz |                   |                                | _                | 5<br>10                        |      |                 |

|                             | 8-bit mode (all valid f <sub>ADCK</sub> )                             |                   | _                              |                  | 10                             |      |                 |

|                             | High speed (ADLPC=0)                                                  | f <sub>ADCK</sub> | 0.4                            | _                | 8.0                            | MHz  |                 |

| clock freq.                 | Low power (ADLPC=1)                                                   | 1                 | 0.4                            |                  | 4.0                            |      |                 |

**Table 36. ADC Operating Conditions**

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup>  $V_{REFL} = V_{SSA}$

$^{3}$  V<sub>REFH</sub> = V<sub>DDA</sub>

Figure 37. ADC Input Impedance Equivalency Diagram

junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

When heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back-calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

# 9.2 Electrical Design Considerations

### CAUTION

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, take normal precautions to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level.

Use the following list of considerations to assure correct operation of the 56F8006/56F8002:

- Provide a low-impedance path from the board power supply to each  $V_{DD}$  pin on the 56F8006/56F8002 and from the board ground to each  $V_{SS}$  (GND) pin.

- The minimum bypass requirement is to place 0.01–0.1µF capacitors positioned as near as possible to the package supply pins. The recommended bypass configuration is to place one bypass capacitor on each of the V<sub>DD</sub>/V<sub>SS</sub> pairs, including V<sub>DDA</sub>/V<sub>SSA</sub>. Ceramic and tantalum capacitors tend to provide better tolerances.

- Ensure that capacitor leads and associated printed circuit traces that connect to the chip  $V_{DD}$  and  $V_{SS}$  (GND) pins are as short as possible.

- Bypass the  $V_{DD}$  and  $V_{SS}$  with approximately 100  $\mu$ F, plus the number of 0.1  $\mu$ F ceramic capacitors.

- PCB trace lengths should be minimal for high-frequency signals.

- Consider all device loads as well as parasitic capacitance due to PCB traces when calculating capacitance. This is especially critical in systems with higher capacitive loads that could create higher transient currents in the  $V_{DD}$  and  $V_{SS}$  circuits.

- Take special care to minimize noise levels on the  $V_{\text{REF}}, V_{\text{DDA}},$  and  $V_{\text{SSA}}$  pins.

- Using separate power planes for  $V_{DD}$  and  $V_{DDA}$  and separate ground planes for  $V_{SS}$  and  $V_{SSA}$  are recommended. Connect the separate analog and digital power and ground planes as near as possible to power supply outputs. If an analog circuit and digital circuit are powered by the same power supply, you should connect a small inductor or ferrite bead in serial with  $V_{DDA}$  and  $V_{SSA}$  traces.

- Physically separate analog components from noisy digital components by ground planes. Do not place an analog trace in parallel with digital traces. Place an analog ground trace around an analog signal trace to isolate it from digital traces.

- Because the flash memory is programmed through the JTAG/EOnCE port, SPI, SCI, or I<sup>2</sup>C, the designer should provide an interface to this port if in-circuit flash programming is desired.

- If desired, connect an external RC circuit to the  $\overline{\text{RESET}}$  pin. The resistor value should be in the range of 4.7 k $\Omega$ -10 k $\Omega$ ; the capacitor value should be in the range of 0.22  $\mu$ F-4.7  $\mu$ F.

- Configuring the RESET pin to GPIO output in normal operation in a high-noise environment may help to improve the performance of noise transient immunity.

- Add a 2.2 k $\Omega$  external pullup on the TMS pin of the JTAG port to keep EOnCE in a restate during normal operation if JTAG converter is not present.

- During reset and after reset but before I/O initialization, all I/O pins are at input state with internal pullup enabled. The typical value of internal pullup is around 33 k $\Omega$ . These internal pullups can be disabled by software.

- To eliminate PCB trace impedance effect, each ADC input should have a no less than 33 pF 10  $\Omega$  RC filter.

- External clamp diodes on analog input pins are recommended.

**Design Considerations**

# 9.3 Ordering Information

Table 40 lists the pertinent information needed to place an order. Consult a Freescale Semiconductor sales office or authorized distributor to determine availability and to order devices.

| Device    | Supply<br>Voltage | Package Type                                   | Pin<br>Count | Frequency<br>(MHz) | Ambient<br>Temperature<br>Range      | Order Number                              |

|-----------|-------------------|------------------------------------------------|--------------|--------------------|--------------------------------------|-------------------------------------------|

| MC56F8002 | 1.8–3.6 V         | Small Outline IC (SOIC)                        | 28           | 32                 | -40° to + 105° C<br>-40° to + 125° C | MC56F8002VWL<br>MC56F8002MWL <sup>1</sup> |

| MC56F8006 | 1.8–3.6 V         | Small Outline IC (SOIC)                        | 28           | 32                 | -40° to + 105° C<br>-40° to + 125° C | MC56F8006VWL<br>MC56F8006MWL <sup>1</sup> |

| MC56F8006 | 1.8–3.6 V         | Low-Profile Quad Flat Pack<br>(LQFP)           | 32           | 32                 | -40° to + 105° C<br>-40° to + 125° C | MC56F8006VLC<br>MC56F8006MLC <sup>1</sup> |

| MC56F8006 | 1.8–3.6 V         | Low-Profile Quad Flat Pack<br>(LQFP)           | 48           | 32                 | -40° to + 105° C<br>-40° to + 125° C | MC56F8006VLF<br>MC56F8006MLF <sup>1</sup> |

| MC56F8006 | 1.8–3.6 V         | Plastic Shrink Dual In-line<br>Package (PSDIP) | 32           | 32                 | –40° to + 105° C                     | MC56F8006VBM                              |

### Table 40. 56F8006/56F8002 Ordering Information

<sup>1</sup> This package is RoHS compliant.

NP

### Package Mechanical Outline Drawings

# 10.4 32-Pin PSDIP

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL | OUTLINE              | PRINT VERSION NO | T TO SCALE |  |

|---------------------------------------------------------|------------|----------------------|------------------|------------|--|

| TITLE:                                                  |            | DOCUMENT NO          | ): 98ASA99330D   | REV: A     |  |

| 32 LEAD PDIP                                            |            | CASE NUMBER: 1376-02 |                  |            |  |

|                                                         |            | STANDARD: NO         | N-JEDEC          |            |  |

### Package Mechanical Outline Drawings

NOTES:

- 1. ALL DIMENSION ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14. 5-1994.

- 3. DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

- DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.        | MECHANICA | LOUTLINE     | PRINT VERSION NOT TO SCALE |             |  |  |  |  |  |

|----------------------------------------------------------------|-----------|--------------|----------------------------|-------------|--|--|--|--|--|

| TITLE:                                                         |           | DOCUMENT NO  | ): 98ASA99330D             | REV: A      |  |  |  |  |  |

| 32 LEAD PDIP                                                   |           | CASE NUMBER  | 8: 1376–02                 | 25 APR 2005 |  |  |  |  |  |

|                                                                |           | STANDARD: NO | N-JEDEC                    |             |  |  |  |  |  |

| Figure 41. 56F8006/56F8002 32-Pin PSDIP Mechanical Information |           |              |                            |             |  |  |  |  |  |

NP

88

# Table 44. Detailed Peripheral Memory Map (continued)

Peripheral Register Memory Map and Reset Value

| Offset<br>Addr.<br>(Hex) | Reset<br>Value<br>(Hex) | Periph. | Register        | Bit<br>15 | 14     | 13      | 12       | 11      | 10      | 9       | 8       | 7      | 6      | 5      | 4      | 3    | 2      | 1    | Bit<br>0 |

|--------------------------|-------------------------|---------|-----------------|-----------|--------|---------|----------|---------|---------|---------|---------|--------|--------|--------|--------|------|--------|------|----------|

| 1A                       | 0000                    | TMR1    | TMR1_<br>CSCTRL | DBG       | i_EN   | FAULT   | ALT_LOAD | 0       | 0       | 0       | 0       | TCF2EN | TCF1EN | TCF2   | TCF1   | C    | L2     | с    | L1       |

| 1B                       | 0000                    | TMR1    | TMR1_<br>FILT   | 0         | 0      | 0       | 0        | 0       | F       | ILT_CN  | Т       |        |        |        | FILT_  | _PER |        |      |          |

| 1C–1F                    | _                       | TMR1    | Reserved        |           |        |         |          |         |         |         | RESE    | RVED   |        |        |        |      |        |      |          |

| 20                       | 0000                    | PWM     | PWM_<br>CTRL    |           | LD     | FQ      |          | HALF    | IPOL2   | IPOL1   | IPOL0   | PR     | SC     | PWMRIE | PWMF   | ISE  | INS    | Грок | PWMEN    |

| 21                       | 0000                    | PWM     | PWM_<br>FCTRL   | 0         | 0      | 0       | 0        | FPOL3   | FPOL2   | FPOL1   | FPOL0   | FIE3   | FMODE3 | FIE2   | FMODE2 | FIE1 | FMODE1 | FIE0 | FMODE0   |

| 22                       | 0000                    | PWM     | PWM_<br>FLTACK  | FPIN3     | FFLAG3 | FPIN2   | FFLAG2   | FPIN1   | FFLAG1  | FPINO   | FFLAGO  |        | FTACK3 |        | FTACK2 |      | FTACK1 |      | FTACK0   |

| 23                       | 0000                    | PWM     | PWM_<br>OUT     | PAD_EN    | 0      | OUTCTL5 | OUTCTL4  | OUTCTL3 | OUTCTL2 | OUTCTL1 | ουτςτιο | 0      | 0      | OUT5   | OUT4   | OUT3 | OUT2   | OUT1 | OUTO     |

| 24                       | 0000                    | PWM     | PWM_<br>CNTR    | 0         |        |         |          |         |         |         |         | CR     |        |        |        |      |        |      |          |

| 25                       | 0000                    | PWM     | PWM_<br>CMOD    | 0         |        |         |          |         |         |         | F       | PWMCN  | Λ      |        |        |      |        |      |          |

| 26                       | 0000                    | PWM     | PWM_<br>VAL0    |           | -      |         |          |         |         |         | PM      | VAL    |        |        |        |      |        |      |          |

| 27                       | 0000                    | PWM     | PWM_<br>VAL1    |           |        |         |          |         |         |         | PM      | VAL    |        |        |        |      |        |      |          |

| 28                       | 0000                    | PWM     | PWM_<br>VAL2    |           |        |         |          |         |         |         | PM      | VAL    |        |        |        |      |        |      |          |

MC56F8006/MC56F8002 Digital Signal Controller, Rev. 4

Freescale Semiconductor

Freescale Semiconductor

| MC56F8006/MC56F8002 E   |

|-------------------------|

| 8002 Digital S          |

| ίΞ.                     |

| ynal Controller, Rev. 4 |

\_

| Offset<br>Addr.<br>(Hex) | Reset<br>Value<br>(Hex) | Periph. | Register        | Bit<br>15 | 14    | 13   | 12    | 11     | 10       | 9       | 8        | 7       | 6        | 5        | 4     | 3     | 2    | 1       | Bit<br>0 |  |

|--------------------------|-------------------------|---------|-----------------|-----------|-------|------|-------|--------|----------|---------|----------|---------|----------|----------|-------|-------|------|---------|----------|--|

| C3                       | 0000                    | PGA1    | PGA1_STS        | 0         | 0     | 0    | 0     | 0      | 0        | 0       | 0        | 0       | 0        | 0        | 0     | 0     | 0    | RUNNING | STCOMP   |  |

| C4–DF                    | _                       | PGA1    | Reserved        |           |       |      |       |        |          |         | RESE     | RVED    |          |          |       |       |      |         |          |  |

| E0                       | 0200                    | SCI     | SCI_RATE        |           |       |      |       |        |          | SBR     |          |         |          |          |       |       | FF   | RAC_SE  | 3R       |  |

| E1                       | 0000                    | SCI     | SCI_<br>CTRL1   | LOOP      | SWAI  | RSRC | М     | WAKE   | POL      | PE      | PT       | TEIE    | TIIE     | RFIE     | REIE  | TE    | RE   | RWU     | SBK      |  |

| E2                       | 0000                    | SCI     | SCI_<br>CTRL2   | 0         | 0     | 0    | 0     | 0      | 0        | 0       | 0        | 0       | 0        | 0        | 0     |       | 0    | 0       | 0        |  |

| E3                       | C000                    | SCI     | SCI_STAT        | TDRE      | TIDLE | RDRF | RIDLE | OR     | NF       | FE      | PF       | 0       | 0        | 0        | 0     | LSE   | 0    | 0       | RAF      |  |

| E4                       | 0000                    | SCI     | SCI_DATA        | 0         | 0     | 0    | 0     | 0      | 0        | 0       |          |         | RE       | CEIVE_   | TRANS | MIT_D | ATA  |         |          |  |

| E5–FF                    |                         | SCI     | Reserved        |           | •     |      |       |        |          |         | RESE     | RVED    |          |          |       |       |      |         |          |  |

| 00                       | 6141                    | SPI     | SPI_<br>SCTRL   |           | SPR   |      | DSO   | ERRIE  | MODFEN   | SPRIE   | SPMSTR   | CPOL    | СРНА     | SPE      | SPTIE | SPRF  | OVRF | MODF    | SPTE     |  |

| 01                       | 000F                    | SPI     | SPI_<br>DSCTRL  | WOM       | 0     | 0    | BD2X  | SSB_IN | SSB_DATA | SSB_ODM | SSB_AUTO | SSB_DDR | SSB_STRB | SSB_OVER | SPR3  |       | DS   |         |          |  |

| 02                       | 0000                    | SPI     | SPI_DRCV        | R15       | R14   | R13  | R12   | R11    | R10      | R9      | R8       | R7      | R6       | R5       | R4    | R3    | R2   | R1      | R0       |  |

| 03                       | 0000                    | SPI     | SPI_DXMIT       | T15       | T14   | T13  | T12   | T11    | T10      | Т9      | Т8       | T7      | T6       | T5       | T4    | Т3    | T2   | T1      | T0       |  |

| 04–1F                    | _                       | SPI     | Reserved        |           |       |      |       |        |          |         | RESE     | RVED    |          |          |       |       |      |         |          |  |

| 20                       | 0000                    | I2C     | I2C_ADDR        | 0         | 0     | 0    | 0     | 0      | 0        | 0       | 0        | AD7     | AD6      | AD5      | AD4   | AD3   | AD2  | AD1     | 0        |  |

| 21                       | 0000                    | I2C     | I2C_<br>FREQDIV | 0         | 0     | 0    | 0     | 0      | 0        | 0       | 0        | ML      | JLT      |          | ICR   |       |      |         |          |  |

Table 44. Detailed Peripheral Memory Map (continued)

Peripheral Register Memory Map and Reset Value

93

100

# Table 44. Detailed Peripheral Memory Map (continued)

| Offset F |                         |         |                   |           |    |    |    |    |    |   |      |        |   |   |   |       |     |      | r        |  |

|----------|-------------------------|---------|-------------------|-----------|----|----|----|----|----|---|------|--------|---|---|---|-------|-----|------|----------|--|

| Addr. \  | Reset<br>Value<br>(Hex) | Periph. | Register          | Bit<br>15 | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7      | 6 | 5 | 4 | 3     | 2   | 1    | Bit<br>0 |  |

| 0D       | 0000                    | GPIOE   | GPIOE_<br>SLEW    | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | SLEW   |   |   |   |       |     |      |          |  |

| 0E-1F    | _                       | GPIOE   | Reserved          |           |    |    |    |    |    |   | RESE | RVED   |   |   |   |       |     |      |          |  |

| 20 (     | 00FF                    | GPIOF   | GPIOF_<br>PUR     | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 |       | Pl  | JR   |          |  |

| 21       | 0000                    | GPIOF   | GPIOF_DR          | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 |       | D   | R    |          |  |

| 22       | 0000                    | GPIOF   | GPIOF_<br>DDR     | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 |       | DI  | DR   |          |  |

| 23       | 0080                    | GPIOF   | GPIOF_<br>PER     | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 |       |     |      |          |  |

| 24       | _                       | GPIOF   | Reserved          |           |    |    | I  |    |    |   | RESE | ERVED  |   |   |   |       |     |      |          |  |

| 25       | 0000                    | GPIOF   | GPIOF_<br>IENR    | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 | IENR  |     |      |          |  |

| 26       | 0000                    | GPIOF   | GPIOF_<br>IPOLR   | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 |       | IPC | DLR  |          |  |

| 27       | 0000                    | GPIOF   | GPIOF_<br>IPR     | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 |       | IF  | ۲R   |          |  |

| 28       | 0000                    | GPIOF   | GPIOF_<br>IESR    | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 |       | IE  | SR   |          |  |

| 29       | —                       | GPIOF   | Reserved          |           |    |    |    |    |    |   | RESE | RVED   |   |   |   |       |     |      |          |  |

| 2A       | 0000                    | GPIOF   | gpiof_<br>Rawdata | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 |       | RAW | DATA |          |  |

| 2B       | 0000                    | GPIOF   | GPIOF_<br>DRIVE   | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 | DRIVE |     |      |          |  |

| 2C (     | 00FF                    | GPIOF   | GPIOF_IFE         | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 |       |     |      |          |  |

| 2D       | 0000                    | GPIOF   | GPIOF_<br>SLEW    | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0      | 0 | 0 | 0 | SLEW  |     |      |          |  |

| 2E–3F    |                         | GPIOF   | Reserved          |           |    |    |    |    |    |   | RESE | SERVED |   |   |   |       |     |      |          |  |

Freescale Semiconductor

102

# MC56F8006/MC56F8002 Digital Signal Controller, Rev. 4

| Offset<br>Addr.<br>(Hex) | Reset<br>Value<br>(Hex) | Periph. | Register     | Bit<br>15 | 14   | 13     | 12   | 11         | 10         | 9          | 8        | 7      | 6      | 5     | 4      | 3             | 2         | 1        | Bit<br>0 |  |  |  |

|--------------------------|-------------------------|---------|--------------|-----------|------|--------|------|------------|------------|------------|----------|--------|--------|-------|--------|---------------|-----------|----------|----------|--|--|--|

| 4E                       | 0000                    | SIM     | SIM_GPSC     | 0         | 0    | 0      | 0    | 0          | 0          | 0          | 0        | 0      | 0      | 0     | 0      | 0             | 0         | GPS_C6   | GPS_C0   |  |  |  |

| 4F                       | 0000                    | SIM     | SIM_GPSD     | 0         | 0    | 0      | 0    | 0          | 0          | 0          | GPS      | 6_D3   | GPS    | _D2   | GPS    | 6_D1          | (         | GPS_D0   |          |  |  |  |

| 50                       | 0000                    | SIM     | SIM_IPS0     | 0         | 0    | 0      | 0    | IPS_FAULT3 | IPS_FAULT2 | IPS_FAULT1 | IP       | S_PSR( | C2     | IP    | S_PSR  | C1            | IP        | IPS_PSRC |          |  |  |  |

| 51                       | 0000                    | SIM     | SIM_IPS1     | 0         | IPS  | S_C2_V | VS   | IP         | S_C1_V     | VS         | IP       | S_C0_V | VS     |       | IPS_T1 |               |           |          |          |  |  |  |

| 52–5F                    |                         | SIM     | Reserved     |           |      |        |      |            |            |            | RESERVED |        |        |       |        |               | · · · · · |          |          |  |  |  |

| 60                       | 0208                    | PMC     | PMC_SCR      | OORF      | LVDF | PPDF   | PORF | OORIE      | LVDIE      | LVDRE      | PPDE     | LPR    | LPRS   | LPWUI | BGBE   | H LVDE LVLS P |           | PR       | OT       |  |  |  |

| 61                       | 00 <sup>2</sup>         | PMC     | PMC_CR2      | 0         | 0    | 0      | 0    | 0          | 0          | 0          | LPO_EN   | LF     | PO_TRI | М     |        |               | TRIM      | IM       |          |  |  |  |

| 7F                       |                         | PMC     | Reserved     |           |      |        |      | •          | •          |            | RESE     | RVED   |        |       |        |               |           |          |          |  |  |  |

| 80                       | 0000                    | CMP0    | CMP0_<br>CR0 | 0         | 0    | 0      | 0    | 0          | 0          | 0          | 0        | 0      | FIL    | TER_C | NT     | PI            | ЛC        | MMC      |          |  |  |  |

| 81                       | 0000                    | CMP0    | CMP0_<br>CR1 | 0         | 0    | 0      | 0    | 0          | 0          | 0          | 0        | SE     | WE     | 0     | PMODE  | INV           | cos       | OPE      | EN       |  |  |  |

| 82                       | 0000                    | CMP0    | CMP0_<br>FPR | 0         | 0    | 0      | 0    | 0          | 0          | 0          | 0        |        |        |       | FILT_  | _PER          |           |          |          |  |  |  |

| 83                       | 0000                    | CMP0    | CMP0_<br>SCR | 0         | 0    | 0      | 0    | 0          | 0          | 0          | 0        | 0      | 0      | 0     | IER    | IEF           | CFR       | CFF      | соит     |  |  |  |

| 84–9F                    |                         | CMP0    | Reserved     |           |      |        |      |            |            |            | RESE     | RVED   |        |       |        |               |           |          |          |  |  |  |

| A0                       | 0000                    | CMP1    | CMP1_<br>CR0 | 0         | 0    | 0      | 0    | 0          | 0          | 0          | 0        | 0      | FIL    | TER_C | NT     | PI            | ЛС        | M        | ИС       |  |  |  |

Table 44. Detailed Peripheral Memory Map (continued)

Peripheral Register Memory Map and Reset Value

|  | $\mathbf{A}$ |  |  |

|--|--------------|--|--|

|  |              |  |  |

| - |  |

|---|--|

| 0 |  |

| 4 |  |

|   |  |

# Table 44. Detailed Peripheral Memory Map (continued)

| Offset<br>Addr.<br>(Hex) | Reset<br>Value<br>(Hex) | Periph. | Register       | Bit<br>15 | 14       | 13 | 12 | 11 | 10   | 9 | 8    | 7     | 6      | 5      | 4      | 3   | 2     | 1    | Bit<br>0 |

|--------------------------|-------------------------|---------|----------------|-----------|----------|----|----|----|------|---|------|-------|--------|--------|--------|-----|-------|------|----------|

| 02                       | 0000                    | PDB     | PDB_<br>DELAYB |           |          | L  |    | L  | L    |   | DEL  | AYB   |        |        |        |     | I     | •    |          |

| 03                       | FFFF                    | PDB     | PDB_MOD        |           | MOD      |    |    |    |      |   |      |       |        |        |        |     |       |      |          |

| 04                       | FFFF                    | PDB     | PDB_<br>COUNT  |           | COUNT    |    |    |    |      |   |      |       |        |        |        |     |       |      |          |

| 05–1F                    |                         | PDB     | Reserved       |           | RESERVED |    |    |    |      |   |      |       |        |        |        |     |       |      |          |

| 20                       | 0000                    | RTC     | RTC_SC         | 0         | 0        | 0  | 0  | 0  | 0    | 0 | 0    | RTIF  | RTC    | LKS    | RTIE   |     | RT    | CPS  |          |

| 21                       | 0000                    | RTC     | RTC_CNT        | 0         | 0        | 0  | 0  | 0  | 0    | 0 | 0    |       |        |        | RTC    | CNT |       |      |          |

| 22                       | 0000                    | RTC     | RTC_MOD        | 0         | 0        | 0  | 0  | 0  | 0    | 0 | 0    |       |        |        | RTCI   | MOD |       |      |          |

| 23–FF                    |                         | RTC     | Reserved       |           |          |    |    |    |      |   | RESE | RVED  | D      |        |        |     |       |      |          |

| 00                       | 0000                    | HFM     | FM_<br>CLKDIV  | 0         | 0        | 0  | 0  | 0  | 0    | 0 | 0    | DIVLD | PRDIV8 | DIV    |        |     |       |      |          |

| 01                       | 0000                    | HFM     | FM_CNFG        | 0         | 0        | 0  | 0  | 0  | LOCK | 0 | AEIE | CBEIE | CCIE   | KEYACC | 0      | 0   | 0     | LBTS | BTS      |

| 03                       | -000 <sup>3</sup>       | HFM     | FM_SECHI       | KEYEN     | SECSTAT  | 0  | 0  | 0  | 0    | 0 | 0    | 0     | 0      | 0      | 0      | 0   | 0     | 0    | 0        |

| 04                       | 0000                    | HFM     | FM_<br>SECLO   | 0         | 0        | 0  | 0  | 0  | 0    | 0 | 0    | 0     | 0      | 0      | 0      | 0   | 0     | SE   | EC       |

| 06–0F                    |                         | HFM     | Reserved       |           |          |    |    |    |      |   | RESE | RVED  |        |        |        |     |       |      |          |

| 10                       | FFFF <sup>6</sup>       | HFM     | FM_PROT        |           |          |    |    |    |      |   | PRO  | TECT  |        |        |        |     |       |      |          |

| 11                       | —                       | HFM     | Reserved       |           | RESERVED |    |    |    |      |   |      |       |        |        |        |     |       |      |          |

| 13                       | 00C0                    | HFM     | FM_USTAT       | 0         | 0        | 0  | 0  | 0  | 0    | 0 | 0    | CBEIF | CCIF   | PVIOL  | ACCERR | 0   | BLANK | 0    | 0        |

| 14                       | 0000                    | HFM     | FM_CMD         | 0         | 0        | 0  | 0  | 0  | 0    | 0 | 0    | 0     |        |        |        | CMD |       |      |          |

Peripheral Register Memory Map and Reset Value

Freescale Semiconductor

### Table 44. Detailed Peripheral Memory Map (continued)

| Offset<br>Addr.<br>(Hex) | Reset<br>Value<br>(Hex) | Periph. | Register      | Bit<br>15 | 14           | 13 | 12 | 11 | 10 | 9 | 8    | 7    | 6 | 5 | 4 | 3 | 2 | 1 | Bit<br>0 |

|--------------------------|-------------------------|---------|---------------|-----------|--------------|----|----|----|----|---|------|------|---|---|---|---|---|---|----------|

| 17                       | —                       | HFM     | Reserved      |           |              |    |    | •  |    |   | RESE | RVED |   |   |   |   |   |   |          |

| 18                       | 0000                    | HFM     | FM_DATA       |           |              |    |    |    |    |   | FMD  | DATA |   |   |   |   |   |   |          |

| 19                       |                         | HFM     | Reserved      |           | RESERVED     |    |    |    |    |   |      |      |   |   |   |   |   |   |          |

| 1A                       | FFFF <sup>4</sup>       | HFM     | FM_OPT0       |           |              |    |    |    |    |   | IFR_ | OPT0 |   |   |   |   |   |   |          |

| 1B                       | FFFF <sup>5</sup>       | HFM     | FM_OPT1       |           |              |    |    |    |    |   | IFR_ | OPT1 |   |   |   |   |   |   |          |

| 1D                       | FFFF <sup>6</sup>       | HFM     | FM_<br>TSTSIG |           | TST_AREA_SIG |    |    |    |    |   |      |      |   |   |   |   |   |   |          |

| 1E–3F                    | —                       | HFM     | Reserved      |           | RESERVED     |    |    |    |    |   |      |      |   |   |   |   |   |   |          |

<sup>1</sup> The binary reset value of this register is 0000 0000 0UUU UUUU, where U represents an undefined value. Spaces have been added to the value for clarity.

<sup>2</sup> The binary reset value of this register is 0000 0000 111NC NC NC NC NC. Spaces have been added to the value for clarity.

<sup>3</sup> The binary reset value of this register is FS00 0000 0000 0000, where F indicates that the reset state is loaded from the flash array during reset, and where S indicates that the reset state is determined by the security state of the module. Spaces have been added to the value for clarity.

Peripheral Register Memory Map and Reset Value

<sup>4</sup> The reset state is loaded from the flash array during reset.

<sup>5</sup> The reset state is loaded from the flash array during reset.

<sup>6</sup> The reset state is loaded from the flash array during reset.