Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | -                                                         |

| Core Size                  | -                                                         |

| Speed                      | -                                                         |

| Connectivity               | -                                                         |

| Peripherals                | -                                                         |

| Number of I/O              | -                                                         |

| Program Memory Size        | -                                                         |

| Program Memory Type        | -                                                         |

| EEPROM Size                | -                                                         |

| RAM Size                   | -                                                         |

| Voltage - Supply (Vcc/Vdd) | -                                                         |

| Data Converters            | -                                                         |

| Oscillator Type            | -                                                         |

| Operating Temperature      | -                                                         |

| Mounting Type              | -                                                         |

| Package / Case             | -                                                         |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc56f8006vlf |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 MC56F8006/MC56F8002 Family Configuration

MC56F8006/MC56F8002 device comparison in Table 1.

| Table 1 | MC56F8006 | Series | Device | Comparison |

|---------|-----------|--------|--------|------------|

|---------|-----------|--------|--------|------------|

| Facture                                                                                   |        | MC56F8006 |        | MC56F8002 |

|-------------------------------------------------------------------------------------------|--------|-----------|--------|-----------|

| Feature                                                                                   | 28-pin | 32-pin    | 48-pin | 28-pin    |

| Flash memory size (Kbytes)                                                                |        | 16        |        | 12        |

| RAM size (Kbytes)                                                                         |        | 2         | 2      |           |

| Analog comparators (ACMP)                                                                 |        | ;         | 3      |           |

| Analog-to-digital converters (ADC)                                                        |        | 2         | 2      |           |

| Unshielded ADC inputs                                                                     | 6      | 7         | 7      | 6         |

| Shielded ADC inputs                                                                       | 9      | 11        | 17     | 9         |

| Total number of ADC input pins <sup>1</sup>                                               | 15     | 18        | 24     | 15        |

| Programmable gain amplifiers (PGA)                                                        |        | :         | 2      |           |

| Pulse-width modulator (PWM) outputs                                                       | 6      |           |        |           |

| PWM fault inputs                                                                          | 3      | 4         | 4      | 3         |

| Inter-integrated circuit (IIC)                                                            |        | ·         | 1      |           |

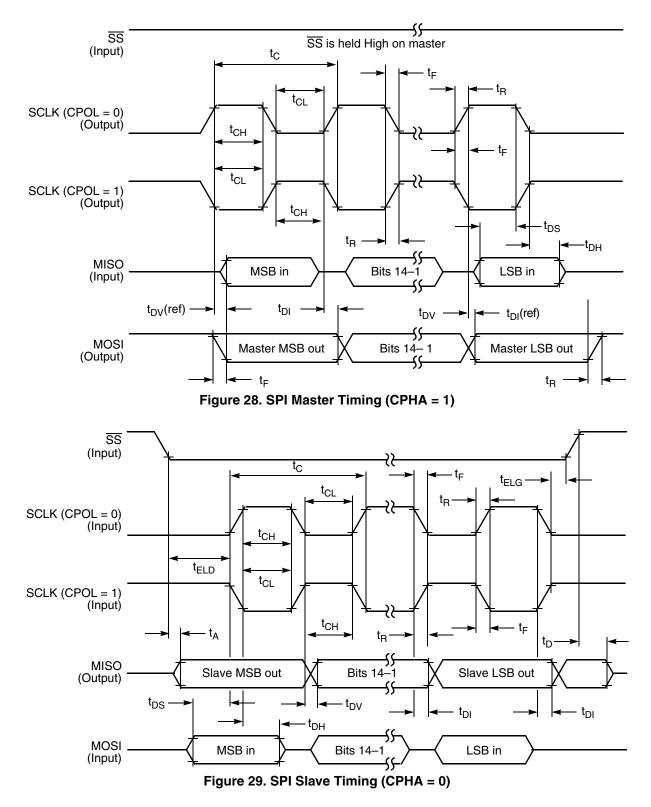

| Serial peripheral interface (SPI)                                                         |        |           | 1      |           |

| High speed serial communications interface (SCI)                                          |        |           | 1      |           |

| Programmable interrupt timer (PIT)                                                        |        |           | 1      |           |

| Programmable delay block (PDB)                                                            |        |           | 1      |           |

| 16-bit multi-purpose timers (TMR)                                                         |        | 2         | 2      |           |

| Real-time counter (RTC)                                                                   |        |           | 1      |           |

| Computer operating properly (COP) timer                                                   |        | Y         | es     |           |

| Phase-locked loop (PLL)                                                                   |        | Y         | es     |           |

| 1 kHz on-chip oscillator                                                                  |        | Y         | es     |           |

| 8 MHz (400 kHz at standby mode) on-chip ROSC                                              |        | Y         | es     |           |

| Crystal oscillator                                                                        |        | Y         | es     |           |

| Power management controller (PMC)                                                         |        | Y         | es     |           |

| IEEE 1149.1 Joint Test Action Group (JTAG) interface                                      |        | Y         | es     |           |

| Enhanced on-chip emulator (EOnCE) IEEE 1149.1 Joint<br>Test Action Group (JTAG) interface |        | Y         | es     |           |

<sup>1</sup> Some ADC inputs share the same pin. See Table 4.

**Block Diagram**

# 2 Block Diagram

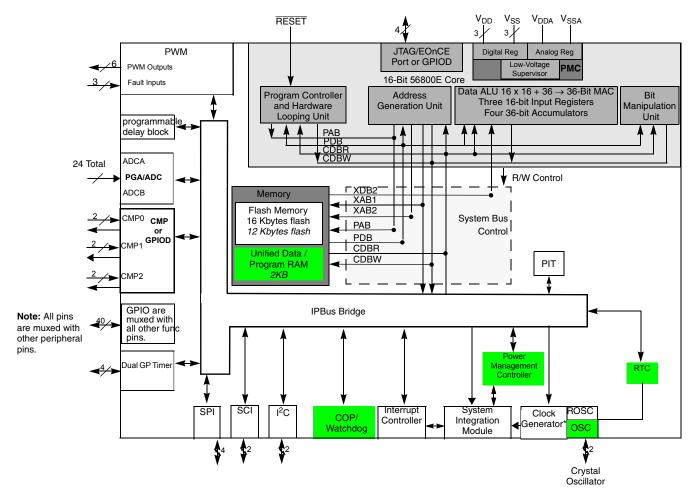

Figure 1 shows a top-level block diagram of the MC56F8006/MC56F8002 digital signal controller. Package options for this family are described later in this document. Italics indicate a 56F8002 device parameter.

Figure 1. MC56F8006/MC56F8002 Block Diagram

# 3 Overview

## 3.1 56F8006/56F8002 Features

### 3.1.1 Core

- Efficient 16-bit 56800E family digital signal controller (DSC) engine with dual Harvard architecture

- As many as 32 million instructions per second (MIPS) at 32 MHz core frequency

- 155 basic instructions in conjunction with up to 20 address modes

- Single-cycle 16 × 16-bit parallel multiplier-accumulator (MAC)

- Four 36-bit accumulators, including extension bits

- 32-bit arithmetic and logic multi-bit shifter

#### MC56F8006/MC56F8002 Digital Signal Controller, Rev. 4

## 3.3 Architecture Block Diagram

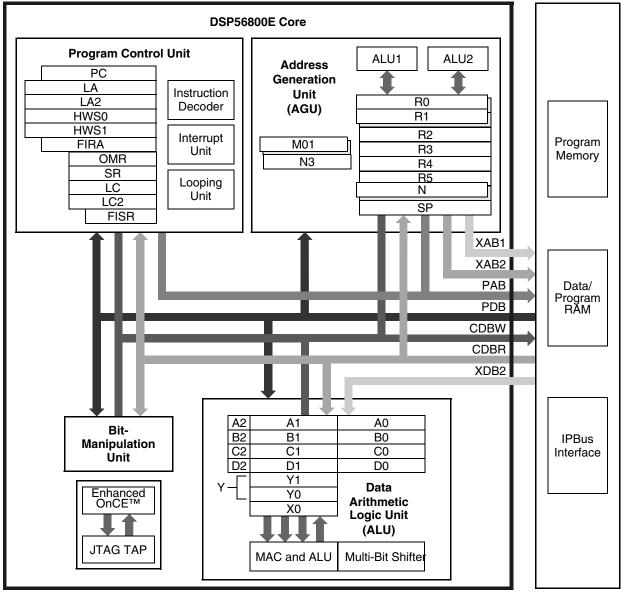

The 56F8006/56F8002's architecture is shown in Figure 2 and Figure 3. Figure 2 illustrates how the 56800E system buses communicate with internal memories and the IPBus interface and the internal connections among each unit of the 56800E core. Figure 3 shows the peripherals and control blocks connected to the IPBus bridge. Please see the system integration module (SIM) section in the *MC56F8006 Reference Manual* for information about which signals are multiplexed with those of other peripherals.

Figure 2. 56800E Core Block Diagram

Figure 7. Top View, MC56F8006 48-Pin LQFP Package

### 4.3 56F8006/56F8002 Signal Pins

After reset, each pin is configured for its primary function (listed first). Any alternate functionality must be programmed via the GPIO module's peripheral enable registers (GPIO\_x\_PER) and SIM module's (GPS\_xn) GPIO peripheral select registers. If CLKIN or XTAL is selected as device external clock input, the CLK\_MOD bit in the OCCS oscillator control register (OSCTL) needs to be set too. EXT\_SEL bit in OSCTL selects CLKIN or XTAL.

### Table 5. 56F8006/56F8002 Signal and Package Information (continued)

| Signal<br>Name        | 28<br>SOIC | 32<br>LQFP | 32<br>PSDI<br>P | 48<br>LQFP | Туре                           | State<br>During<br>Reset                | Signal Description                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|------------|------------|-----------------|------------|--------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOA3                | 17         | 24         | 20              | 36         | Input/<br>Output               | Input,<br>internal<br>pullup<br>enabled | Port A GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                            |

| (PWM3)                |            |            |                 |            | Output                         | onabiou                                 | PWM3 — The PWM channel 3.                                                                                                                                                                                                                                                                                                                                        |

| (TXD)                 |            |            |                 |            | Output                         |                                         | TXD — The SCI transmit data output or transmit/receive in single wire operation.                                                                                                                                                                                                                                                                                 |

| (EXTAL)               |            |            |                 |            | Analog<br>Input                |                                         | EXTAL — External Crystal Oscillator Input. This input can be<br>connected to a 32.768 kHz or 1–16 MHz external crystal or ceramic<br>resonator. When used to supply a source to the internal PLL, the<br>crystal/resonator must be in the 4 MHz to 8 MHz range. Tie this pin<br>low or configure as GPIO if XTAL is being driven by an external<br>clock source. |

|                       |            |            |                 |            |                                |                                         | to device pins to speed startup.                                                                                                                                                                                                                                                                                                                                 |

|                       |            |            |                 |            |                                |                                         | After reset, the default state is GPIOA3.                                                                                                                                                                                                                                                                                                                        |

| GPIOA4                | 16         | 22         | 18              | 33         | Input/<br>Output               | Input,<br>internal<br>pullup            | Port A GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                            |

| (PWM4)                |            |            |                 |            | Output                         | enabled                                 | PWM4 — The PWM channel 4.                                                                                                                                                                                                                                                                                                                                        |

| (SDA)                 |            |            |                 |            | Input/Open-<br>drain<br>Output |                                         | SDA — The I <sup>2</sup> C serial data line.                                                                                                                                                                                                                                                                                                                     |

| (FAULT1)              |            |            |                 |            | Input                          |                                         | FAULT1 — PWM fault input 1 used for disabling selected PWM outputs in cases where fault conditions originate off-chip.                                                                                                                                                                                                                                           |

| (TIN2)                |            |            |                 |            | Input                          |                                         | TIN2 — Dual timer module channel 2 input                                                                                                                                                                                                                                                                                                                         |

|                       |            |            |                 |            |                                |                                         | After reset, the default state is GPIOA4.                                                                                                                                                                                                                                                                                                                        |

| GPIOA5                | 14         | 20         | 16              | 29         | Input/<br>Output               | Input,<br>internal                      | Port A GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                            |

| (PWM5)                |            |            |                 |            | Output                         | pullup<br>enabled                       | PWM5 — The PWM channel 5.                                                                                                                                                                                                                                                                                                                                        |

| (FAULT2/<br>EXT_SYNC) |            |            |                 |            | Input/<br>Output               |                                         | FAULT2 — PWM fault input 2 used for disabling selected PWM outputs in cases where fault conditions originate off-chip.<br>EXT_SYNC — When not being used as a fault input, this pin can be used to receive a pulse to reset the PWM counter or to generate a positive pulse at the start of every PWM cycle.                                                     |

| (TIN3)                |            |            |                 |            | Input                          |                                         | TIN3 — Dual timer module channel 3 input                                                                                                                                                                                                                                                                                                                         |

|                       |            |            |                 |            |                                |                                         | After reset, the default state is GPIOA5.                                                                                                                                                                                                                                                                                                                        |

#### Signal/Connection Descriptions

| Table 5. 56F8006/56F8002 | Signal and Packa | ge Information | (continued) |

|--------------------------|------------------|----------------|-------------|

|                          |                  |                |             |

| Signal                | 28 | 32   | 32        | 48   |                            | State                                  |                                                                                                                                                     |

|-----------------------|----|------|-----------|------|----------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                  |    | LQFP | PSDI<br>P | LQFP | Туре                       | During<br>Reset                        | Signal Description                                                                                                                                  |

| GPIOE5                |    |      |           | 16   | Input/<br>Output           | Input,<br>internal<br>pullup           | Port E GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                               |

| (ANA8 and<br>CMP2_P1) |    |      |           |      | Analog<br>Input            | enabled                                | ANA8 and CMP2_P1— Analog input to channel 8 of ADCA and positive input 1 of analog comparator 2.                                                    |

|                       |    |      |           |      |                            |                                        | After reset, the default state is GPIOE5.                                                                                                           |

| GPIOE6                |    |      |           | 28   | Input/<br>Output           | Input,<br>internal<br>pullup<br>enable | Port E GPIO — This GPIO pin can be individually programmed as<br>an input or output pin.<br>After reset, the default state is GPIOE6.               |

| GPIOE7                |    |      |           | 34   | Input/                     | Input,                                 | Port E GPIO — This GPIO pin can be individually programmed as                                                                                       |

|                       |    |      |           | •    | Output                     | internal<br>pullup                     | an input or output pin                                                                                                                              |

| (CMP1_M3)             |    |      |           |      | Analog<br>Input            | enabled                                | CMP1_M3 — Analog input to both negative input 3 of analog comparator 1.                                                                             |

|                       |    |      |           |      |                            |                                        | After reset, the default state is GPIOE7.                                                                                                           |

| GPIOF0                | 18 | 25   | 21        | 37   | Input/<br>Output           | Input,<br>internal                     | Port F GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                               |

| (XTAL)                |    |      |           |      | Analog<br>Input/<br>Output | pullup<br>enabled                      | XTAL — External Crystal Oscillator Output. This output connects the internal crystal oscillator output to an external crystal or ceramic resonator. |

|                       |    |      |           |      |                            |                                        | After reset, the default state is GPIOF0.                                                                                                           |

| GPIOF1                |    |      |           | 40   | Input/<br>Output           | Input,<br>internal                     | Port F GPIO — This GPIO pin can be individually programmed as an input or output pin                                                                |

| (CMP1_P3)             |    |      |           |      | Analog<br>Input            | pullup<br>enabled                      | CMP1_P3 — Analog input to both positive input 3 of analog comparator 1.                                                                             |

|                       |    |      |           |      |                            |                                        | After reset, the default state is GPIOF1                                                                                                            |

| GPIOF2                |    |      |           | 41   | Input/<br>Output           | Input,<br>internal<br>pullup           | Port F GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                               |

| (CMP0_M3)             |    |      |           |      | Analog<br>Input            | enabled                                | CMP0_M3 — Analog input to both negative input 3 of analog comparator 0.                                                                             |

|                       |    |      |           |      |                            |                                        | After reset, the default state is GPIOF2.                                                                                                           |

| GPIOF3                |    |      |           | 42   | Input/<br>Output           | Input,<br>internal                     | Port F GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                               |

| (CMP0_P3)             |    |      |           |      | Analog<br>Input            | pullup<br>enabled                      | CMP0_P3 — Analog input to both positive input 3 of analog comparator 0.                                                                             |

|                       |    |      |           |      |                            |                                        | After reset, the default state is GPIOF3.                                                                                                           |

#### **Memory Maps**

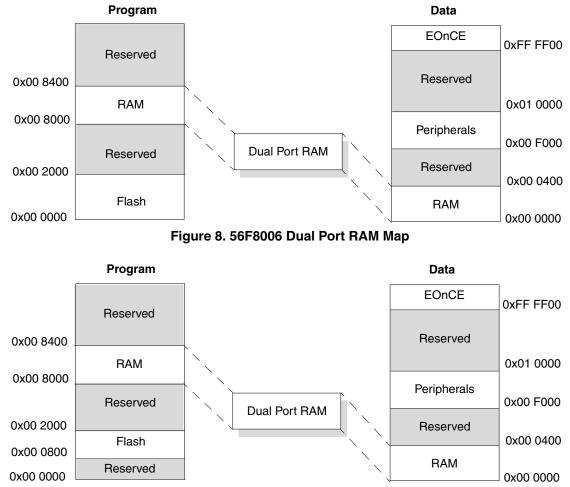

On-chip RAM is also mapped into program space starting at P: 0x00 8000. This makes for easier online reprogramming of on-chip flash.

Figure 9. 56F8002 Dual Port RAM Map

## 5.4 Interrupt Vector Table and Reset Vector

The location of the vector table is determined by the vector base address register (VBA). The value in this register is used as the upper 14 bits of the interrupt vector VAB[20:0]. The lower seven bits are determined based on the highest priority interrupt and are then appended onto VBA before presenting the full VAB to the core. Please see the *MC56F8006 Peripheral Reference Manual* for detail. The reset startup addresses of 56F8002 and 56F8006 are different.

- 56F8006 startup address is located at 0x00 0000. The reset value of VBA is reset to a value of 0x0000 that corresponds to address 0x00 0000

- 56F8002 startup address is located at 0x00 0800. The reset value of VBA is reset to a value of 0x0010 that corresponds to address 0x00 0800

By default, the chip reset address and COP reset address correspond to vector 0 and 1 of the interrupt vector table. In these instances, the first two locations in the vector table must contain branch or JMP instructions. All other entries must contain JSR instructions.

The highest number vector, a user assignable vector USER6 (vector 50), can be defined as a fast interrupt if the instruction located in this vector location is not a JSR or BSR instruction. Please see section 9.3.3.3 of *DSP56800E 16-Bit Core Reference Manual* for detail.

### 7.2.4 Flash Lockout Recovery without Mass Erase

### 7.2.4.1 Without Presenting Back Door Access Keys to the Flash Unit

A user can un-secure a secured device by programming the word 0x0000 into program flash location 0x00 1FF7. After completing the programming, the JTAG TAP controller and the device must be reset to return to normal unsecured operation.

You are responsible for directing the device to invoke the flash programming subroutine to reprogram the word 0x0000 into program flash location 0x00 1FF7. This is done by, for example, toggling a specific pin or downloading a user-defined key through serial interfaces.

#### NOTE

Flash contents can be programmed only from 1s to 0s.

### 7.2.4.2 Presenting Back Door Access Key to the Flash Unit

It is possible to temporarily bypass the security through a back door access scheme, using a 4-word key, to temporarily unlock of the flash. A back door access requires support from the embedded software. This software would typically permit an external user to enter a four word code through one of the communications interfaces and then use it to attempt the unlock sequence. If your input matches the four word code stored at location 0x00 1FFC–0x00 1FFF in the flash memory, the part immediately becomes unsecured (at runtime) and you can access internal memory via JTAG/EOnCE port. Refer to the *MC56F8006 Peripheral Reference Manual* for detail. The key must be entered in four consecutive accesses to the flash, so this routine should be designed to run in RAM.

### 7.3 Product Analysis

The recommended method of unsecuring a secured device for product analysis of field failures is via the method described in Section 7.2.4.2, "Presenting Back Door Access Key to the Flash Unit." The customer would need to supply technical support with the details of the protocol to access the subroutines in flash memory. An alternative method for performing analysis on a secured device would be to mass-erase and reprogram the flash with the original code, but modify the security word or not program the security word.

# 8 Specifications

### 8.1 General Characteristics

The 56F8006/56F8002 is fabricated in high-density low power and low leakage CMOS with a maximum voltage of 3.6 V digital inputs during normal operation without causing damage.

Absolute maximum ratings in Table 12 are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond these ratings may affect device reliability or cause permanent damage to the device.

Unless otherwise stated, all specifications within this chapter apply over the temperature range of  $-40^{\circ}$ C to 105°C ambient temperature over the following supply ranges:  $V_{SS} = V_{SSA} = 0V$ ,  $V_{DD} = V_{DDA} = 3.0-3.6$  V,  $CL \le 50$  pF,  $f_{OP} = 32$  MHz

### CAUTION

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level.

#### MC56F8006/MC56F8002 Digital Signal Controller, Rev. 4

Specifications

## 8.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified Table 12 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, take normal precautions to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ) or the programmable pullup resistor associated with the pin is enabled.

| Characteristic                                          | Symbol           | Notes           | Min  | Max                  | Unit |

|---------------------------------------------------------|------------------|-----------------|------|----------------------|------|

| Supply Voltage Range                                    | V <sub>DD</sub>  |                 | -0.3 | 3.8                  | V    |

| Analog Supply Voltage Range                             | V <sub>DDA</sub> |                 | -0.3 | 3.6                  | V    |

| Voltage difference $V_{DD}$ to $V_{DDA}$                | $\Delta V_{DD}$  |                 | -0.3 | 0.3                  | V    |

| Voltage difference $V_{SS}$ to $V_{SSA}$                | $\Delta V_{SS}$  |                 | -0.3 | 0.3                  | V    |

| Digital Input Voltage Range                             | V <sub>IN</sub>  | Pin Groups 1, 2 | -0.3 | V <sub>DD</sub> +0.3 | V    |

| Oscillator Voltage Range                                | V <sub>OSC</sub> | Pin Group 4     | TBD  | TBD                  | V    |

| Analog Input Voltage Range                              | V <sub>INA</sub> | Pin Group 3     | -0.3 | 3.6                  | V    |

| Input clamp current, per pin $(V_{IN} < 0)^{1 \ 2 \ 3}$ | V <sub>IC</sub>  |                 | —    | -25.0                | mA   |

| Output clamp current, per pin $(V_0 < 0)^{123}$         | V <sub>OC</sub>  |                 | —    | -20.0                | mA   |

| Output Voltage Range<br>(Normal Push-Pull mode)         | V <sub>OUT</sub> | Pin Group 1     | -0.3 | V <sub>DD</sub>      | V    |

| Ambient Temperature<br>Industrial                       | T <sub>A</sub>   |                 | -40  | 105                  | °C   |

| Storage Temperature Range<br>(Extended Industrial)      | T <sub>STG</sub> |                 | -55  | 150                  | °C   |

| Table 1 | 2. Absolute | Maximum | Ratings |

|---------|-------------|---------|---------|

|---------|-------------|---------|---------|

$(V_{SS} = 0 \text{ V}, V_{SSA} = 0 \text{ V})$

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

$^2\,$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$

<sup>3</sup> Power supply must maintain regulation within operating VDD range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{In} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD}$  loads shunt current greater than maximum injection current. This is the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present or if the clock rate is low (which would reduce overall power consumption).

## 8.2.1 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, use normal handling precautions to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM), and the charge device model (CDM).

| Characteristic                            | Comments                   | Symbol              | Value<br>(LQFP) | Unit |

|-------------------------------------------|----------------------------|---------------------|-----------------|------|

| Junction to ambient<br>Natural convection | Single layer board<br>(1s) | $R_{	hetaJA}$       | 79              | °C/W |

| Junction to ambient<br>Natural convection | Four layer board<br>(2s2p) | $R_{	hetaJMA}$      | 55              | °C/W |

| Junction to ambient<br>(@200 ft/min)      | Single layer board<br>(1s) | $R_{	hetaJMA}$      | 66              | °C/W |

| Junction to ambient<br>(@200 ft/min)      | Four layer board<br>(2s2p) | $R_{	hetaJMA}$      | 48              | °C/W |

| Junction to board                         |                            | $R_{	heta JB}$      | 34              | °C/W |

| Junction to case                          |                            | $R_{	ext{	heta}JC}$ | 20              | °C/W |

| Junction to package top                   | Natural Convection         | $\Psi_{JT}$         | 4               | °C/W |

Table 18. 48LQFP Package Thermal Characteristics

#### NOTE

Junction-to-ambient thermal resistance determined per JEDEC JESD51–3 and JESD51–6. Thermal test board meets JEDEC specification for this package.

Junction-to-board thermal resistance determined per JEDEC JESD51–8. Thermal test board meets JEDEC specification for the specified package.

Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51–2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

See Section 9.1, "Thermal Design Considerations," for more detail on thermal design considerations.

### 8.4 Recommended Operating Conditions

This section includes information about recommended operating conditions.

Specifications

| Mode                                            | Conditions                                                                                                                                                                                                                       | Typical<br>25                |                  | Maximum<br>105               |                  | Maximum @ 3.6 V,<br>125 °C   |                  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|------------------------------|------------------|------------------------------|------------------|--|

|                                                 |                                                                                                                                                                                                                                  | I <sub>DD</sub> <sup>1</sup> | I <sub>DDA</sub> | I <sub>DD</sub> <sup>1</sup> | I <sub>DDA</sub> | I <sub>DD</sub> <sup>1</sup> | I <sub>DDA</sub> |  |

| LPwait <sup>3</sup>                             | 32.768 kHz device clock;<br>Clocked by a 32.768 kHz external crystal<br>oscillator in power down;<br>PLL disabled;<br>All peripheral modules disabled and clock<br>gated off;<br>processor core in wait state                    | 157.55 μA                    | 1.57 mA          | 380 μA                       | 3.4 mA           | 398 μA                       | 3.6 mA           |  |

| Stop                                            | 32 MHz device clock<br>relaxation oscillator (ROSC) in high speed<br>mode;<br>PLL engaged;<br>all peripheral module and core clocks are off;<br>ADC/DAC/comparator powered off;<br>processor core in stop state                  | 8.21 mA                      | 65.51 μA         | 9.8 mA                       | 130 μA           | 10.3 mA                      | 132 μA           |  |

| LSstop <sup>2</sup>                             | 200 kHz device clock;<br>relaxation oscillator (ROSC) in standby<br>mode;<br>PLL disabled;<br>all peripheral modules disabled and clock<br>gated off;<br>processor core in stop state.                                           | 194.69 μA                    | 65.51 μA         | 340 μA                       | 120 μΑ           | 357 μΑ                       | 123 μA           |  |

| LPstop <sup>2</sup>                             | 32.768 kHz device clock;<br>Clocked by a 32.768 kHz external crystal<br>relaxation oscillator (ROSC) in power down;<br>PLL disabled;<br>all peripheral modules disabled and clock<br>gated off;<br>processor core in stop state. | 2.77 μΑ                      | 13.99 nA         | 45 μΑ                        | 3.0 μΑ           | 58 μΑ                        | 3.6 μA           |  |

| PPD <sup>4</sup> with<br>XOSC                   | 32.768 kHz clock fed on XTAL<br>RTC or COP monitoring XOSC (but no<br>wakeup)<br>processor core in stop state                                                                                                                    | 879.72 nA                    | 11.56 nA         | 18 μA                        | 2.4 μA           | 22 μΑ                        | 3.0 μΑ           |  |

| PPD with LP<br>oscillator<br>(1 kHz)<br>enabled | RTC or COP monitoring LP oscillator (but no wakeup);<br>processor core in stop state.                                                                                                                                            | 499.15 nA                    | 13.9 nA          | 14 μA                        | 2.4 μA           | 17 μΑ                        | 2.8 mA           |  |

| PPD with no<br>clock<br>monitoring              | RTC and LP oscillator are disabled;<br>processor core in stop state.                                                                                                                                                             | 494.04 nA                    | 12.88 nA         | 14 μA                        | 2.4 μA           | 17 μΑ                        | 2.8 μA           |  |

| Table 22. Supply Curren | t Consumption (continued) |

|-------------------------|---------------------------|

|-------------------------|---------------------------|

<sup>1</sup> No output switching; all ports configured as inputs; all inputs low; no DC loads.

<sup>2</sup> Low speed mode: LPR (lower voltage regulator control bit) = 0 and voltage regulator is in full regulation. Characterization only.

<sup>3</sup> Low power mode: LPR (lower voltage regulator control bit) = 1; the voltage regulator is put into standby.

<sup>4</sup> Partial power down mode: PPDE (partial power down enable bit) = 1; power management controller (PMC) enters partial power down mode the next time that the STOP command is executed.

### 8.7 Flash Memory Characteristics

Table 23. Flash Timing Parameters

| Characteristic            | Symbol | Min | Тур | Мах | Unit |

|---------------------------|--------|-----|-----|-----|------|

| Program time <sup>1</sup> | tprog  | 20  | _   | 40  | μs   |

| Erase time <sup>2</sup>   | terase | 20  | —   | —   | ms   |

| Mass erase time           | tme    | 100 | —   | —   | ms   |

There is additional overhead that is part of the programming sequence. See the *MC56F8006 Peripheral Reference Manual* for detail.

<sup>2</sup> Specifies page erase time. There are 512 bytes per page in the program flash memory.

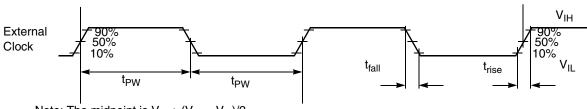

## 8.8 External Clock Operation Timing

#### Table 24. External Clock Operation Timing Requirements<sup>1</sup>

| Characteristic                                              | Symbol            | Min                 | Тур | Max                | Unit |

|-------------------------------------------------------------|-------------------|---------------------|-----|--------------------|------|

| Frequency of operation (external clock driver) <sup>2</sup> | f <sub>osc</sub>  | _                   | _   | 64                 | MHz  |

| Clock pulse width <sup>3</sup>                              | t <sub>PW</sub>   | 6.25                | _   | —                  | ns   |

| External clock input rise time <sup>4</sup>                 | t <sub>rise</sub> | _                   | _   | 3                  | ns   |

| External clock input fall time <sup>5</sup>                 | t <sub>fall</sub> | _                   | _   | 3                  | ns   |

| Input high voltage overdrive by an external clock           | V <sub>ih</sub>   | 0.85V <sub>DD</sub> | _   | —                  | V    |

| Input high voltage overdrive by an external clock           | V <sub>il</sub>   | —                   |     | 0.3V <sub>DD</sub> | V    |

<sup>1</sup> Parameters listed are guaranteed by design.

<sup>2</sup> See Figure 21 for detail on using the recommended connection of an external clock driver.

<sup>3</sup> The chip may not function if the high or low pulse width is smaller than 6.25 ns.

<sup>4</sup> External clock input rise time is measured from 10% to 90%.

<sup>5</sup> External clock input fall time is measured from 90% to 10%.

Note: The midpoint is  $V_{IL} + (V_{IH} - V_{IL})/2$ .

Figure 21. External Clock Timing

Specifications

## 8.9 Phase Locked Loop Timing

#### Table 25. Phase Locked Loop Timing

| Characteristic                                                                    | Symbol                 | Min | Тур | Мах  | Unit |

|-----------------------------------------------------------------------------------|------------------------|-----|-----|------|------|

| PLL input reference frequency <sup>1</sup>                                        | f <sub>ref</sub>       | 4   | 8   |      | MHz  |

| PLL output frequency <sup>2</sup>                                                 | f <sub>op</sub>        | 120 | 192 | _    | MHz  |

| PLL lock time <sup>3 4</sup>                                                      | t <sub>plls</sub>      | _   | 40  | 100  | μs   |

| Accumulated jitter using an 8 MHz external crystal as the PLL source <sup>5</sup> | J <sub>A</sub>         | _   | _   | 0.37 | %    |

| Cycle-to-cycle jitter                                                             | t <sub>jitterpll</sub> | _   | 350 | _    | ps   |

<sup>1</sup> An externally supplied reference clock should be as free as possible from any phase jitter for the PLL to work correctly. The PLL is optimized for 8 MHz input.

- <sup>2</sup> The core system clock operates at 1/6 of the PLL output frequency.

- <sup>3</sup> This is the time required after the PLL is enabled to ensure reliable operation.

- <sup>4</sup> From powerdown to powerup state at 32 MHz system clock state.

- <sup>5</sup> This is measured on the CLKO signal (programmed as system clock) over 264 system clocks at 32 MHz system clock frequency and using an 8 MHz oscillator frequency.

## 8.10 Relaxation Oscillator Timing

#### Table 26. Relaxation Oscillator Timing

| Characteristic                                                                                                       | Symbol                  | Minimum | Typical     | Maximum      | Unit       |

|----------------------------------------------------------------------------------------------------------------------|-------------------------|---------|-------------|--------------|------------|

| Relaxation oscillator output frequency <sup>1</sup><br>Normal Mode<br>Standby Mode                                   | f <sub>op</sub>         | _       | 8.05<br>400 |              | MHz<br>kHz |

| Relaxation oscillator stabilization time <sup>2</sup>                                                                |                         |         | 1           | 3            | ms         |

| Cycle-to-cycle jitter. This is measured on the CLKO signal (programmed prescaler_clock) over 264 clocks <sup>3</sup> | t <sub>jitterrosc</sub> | _       | 400         | _            | ps         |

| Variation over temperature –40 °C to 105 °C $^4$                                                                     |                         | _       |             | -3.0 to +2.0 | %          |

| Variation over temperature 0 °C to 105 °C <sup>5</sup>                                                               |                         |         | _           | -2.0 to +2.0 | %          |

| Variation over temperature –40 °C to 125 °C $^4$                                                                     |                         | —       | —           | -3.5 to +3.0 | %          |

<sup>1</sup> Output frequency after factory trim.

<sup>2</sup> This is the time required from standby to normal mode transition.

<sup>3</sup> J<sub>A</sub> is required to meet QSCI requirements.

<sup>4</sup> See Figure 22. The power supply VDD must be greater than or equal to 2.6 V. Below 2.6 V, the maximum variation over the whole temperature and whole voltage range from 1.8 V to 2.6 V will be +/-16%.

<sup>5</sup> This data is only applied to devices with temperature range from -40 °C to 105 °C.

# 8.11 Reset, Stop, Wait, Mode Select, and Interrupt Timing

### NOTE

All address and data buses described here are internal.

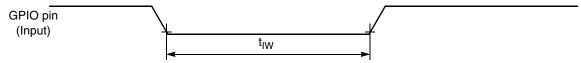

Table 27. Reset, Stop, Wait, Mode Select, and Interrupt Timing<sup>1,2</sup>

| Characteristic                                                              | Symbol           | Typical Min              | Typical Max              | Unit | See Figure |

|-----------------------------------------------------------------------------|------------------|--------------------------|--------------------------|------|------------|

| Minimum RESET Assertion Duration                                            | t <sub>RA</sub>  | 4T                       | —                        | ns   | —          |

| Minimum GPIO pin Assertion for Interrupt                                    | t <sub>IW</sub>  | 2T                       | —                        | ns   | Figure 24  |

| RESET deassertion to First Address Fetch                                    | t <sub>RDA</sub> | 96T <sub>OSC</sub> + 64T | 97T <sub>OSC</sub> + 65T | ns   | _          |

| Delay from Interrupt Assertion to Fetch of first instruction (exiting Stop) | t <sub>IF</sub>  | —                        | 6T                       | ns   | —          |

<sup>1</sup> In the formulas, T = system clock cycle and  $T_{osc}$  = oscillator clock cycle. For an operating frequency of 32 MHz, T = 31.25 ns. At 4 MHz (used coming out of reset and stop modes), T = 250 ns.

<sup>2</sup> Parameters listed are guaranteed by design.

Figure 24. GPIO Interrupt Timing (Negative Edge-Sensitive)

## 8.12 External Oscillator (XOSC) Characteristics

Reference Figure 10, and Figure 11, and Figure 12 for crystal or resonator circuits.

Specifications

MC56F8006/MC56F8002 Digital Signal Controller, Rev. 4

| Characteristic                                  | Conditions               | Symb                | Min  | Typ <sup>1</sup> | Max  | Unit             | Comment              |

|-------------------------------------------------|--------------------------|---------------------|------|------------------|------|------------------|----------------------|

| Supply current<br>ADLPC=1<br>ADLSMP=1<br>ADCO=1 |                          | I <sub>DDAD</sub>   |      | 120              |      | μΑ               |                      |

| Supply current<br>ADLPC=1<br>ADLSMP=0<br>ADCO=1 |                          | I <sub>DDAD</sub>   | _    | 202              | _    | μΑ               |                      |

| Supply current<br>ADLPC=0<br>ADLSMP=1<br>ADCO=1 |                          | I <sub>DDAD</sub>   |      | 288              |      | μΑ               |                      |

| Supply current<br>ADLPC=0<br>ADLSMP=0<br>ADCO=1 |                          | I <sub>DDAD</sub>   | _    | 0.532            | 1    | mA               |                      |

| ADC                                             | High speed (ADLPC=0)     | f <sub>ADACK</sub>  | 2    | 3.3              | 5    | MHz              | t <sub>ADACK</sub> = |

| asynchronous<br>clock source                    | Low power (ADLPC=1)      |                     | 1.25 | 2                | 3.3  |                  | 1/f <sub>ADACK</sub> |

| Conversion time                                 | Short sample (ADLSMP=0)  | t <sub>ADC</sub>    |      | 20               |      | ADCK             |                      |

| (including<br>sample time)                      | Long sample (ADLSMP=1)   |                     |      | 40               | —    | cycles           |                      |

| Sample time                                     | Short sample (ADLSMP=0)  | t <sub>ADS</sub>    |      | 3.5              | —    | ADCK             | -                    |

|                                                 | Long sample (ADLSMP=1)   |                     | _    | 23.5             | —    | cycles           |                      |

| Differential                                    | 12-bit mode              | DNL                 | _    | ±1.75            | —    | LSB <sup>2</sup> |                      |

| Non-linearity                                   | 10-bit mode <sup>3</sup> |                     | _    | ±0.5             | ±1.0 |                  |                      |

|                                                 | 8-bit mode <sup>3</sup>  |                     | _    | ±0.3             | ±0.5 |                  |                      |

| Integral                                        | 12-bit mode              | INL                 | _    | ±1.5             | —    | LSB <sup>2</sup> |                      |

| non-linearity                                   | 10-bit mode              |                     | _    | ±0.5             | ±1.0 |                  |                      |

|                                                 | 8-bit mode               |                     | _    | ±0.3             | ±0.5 |                  |                      |

| Quantization                                    | 12-bit mode              | EQ                  | _    | -1 to 0          | —    | LSB <sup>2</sup> |                      |

| error                                           | 10-bit mode              |                     | _    | —                | ±0.5 |                  |                      |

|                                                 | 8-bit mode               |                     | —    | —                | ±0.5 |                  |                      |

| Input leakage                                   | 12-bit mode              | E <sub>IL</sub>     | —    | ±2               | —    | LSB <sup>2</sup> | Pad leakage4 *       |

| error                                           | 10-bit mode              |                     | _    | ±0.2             | ±4   | 1                | R <sub>AS</sub>      |

|                                                 | 8-bit mode               |                     | —    | ±0.1             | ±1.2 | 1                |                      |

| Temp sensor                                     | –40°C–25°C               | m                   | _    | 1.646            | —    | mV/°C            |                      |

| slope                                           | 25°C–125°C               |                     | —    | 1.769            | —    | 1                |                      |

| Temp sensor<br>voltage                          | 25°C                     | V <sub>TEMP25</sub> |      | 701.2            |      | mV               |                      |

Power consumption is given by the following equation:

| Total power = | A:  | internal [static component]          |

|---------------|-----|--------------------------------------|

|               | +B: | internal [state-dependent component] |

|               | +C: | internal [dynamic component]         |

|               | +D: | external [dynamic component]         |

|               | +E: | external [static component]          |

A, the internal [static] component, is comprised of the DC bias currents for the oscillator, leakage currents, PLL, and voltage references. These sources operate independently of processor state or operating frequency.

B, the internal [state-dependent] component, reflects the supply current required by certain on-chip resources only when those resources are in use. These include RAM, flash memory, and the ADCs.

C, the internal [dynamic] component, is classic  $C*V^{2*F}$  CMOS power dissipation corresponding to the 56800E core and standard cell logic.

D, the external [dynamic] component, reflects power dissipated on-chip as a result of capacitive loading on the external pins of the chip. This is also commonly described as  $C^*V^{2*}F$ , although simulations on two of the I/O cell types used on the 56800E reveal that the power-versus-load curve does have a non-zero Y-intercept.

Table 39. I/O Loading Coefficients at 10 MHz

|            | Intercept | Slope      |

|------------|-----------|------------|

| 8 mA drive | 1.3       | 0.11 mW/pF |

| 4 mA drive | 1.15 mW   | 0.11 mW/pF |

Power due to capacitive loading on output pins is (first order) a function of the capacitive load and frequency at which the outputs change. Table 39 provides coefficients for calculating power dissipated in the I/O cells as a function of capacitive load. In these cases:

#### TotalPower = Σ((Intercept + Slope\*Cload)\*frequency/10 MHz)

where:

- Summation is performed over all output pins with capacitive loads

- Total power is expressed in mW

- C<sub>load</sub> is expressed in pF

Because of the low duty cycle on most device pins, power dissipation due to capacitive loads was found to be fairly low when averaged over a period of time.

E, the external [static component], reflects the effects of placing resistive loads on the outputs of the device. Sum the total of all  $V^2/R$  or IV to arrive at the resistive load contribution to power. Assume V = 0.5 for the purposes of these rough calculations. For instance, if there is a total of eight PWM outputs driving 10 mA into LEDs, then P = 8\*0.5\*0.01 = 40 mW.

In previous discussions, power consumption due to parasitics associated with pure input pins is ignored, as it is assumed to be negligible.

Egn. 2

Eqn. 1

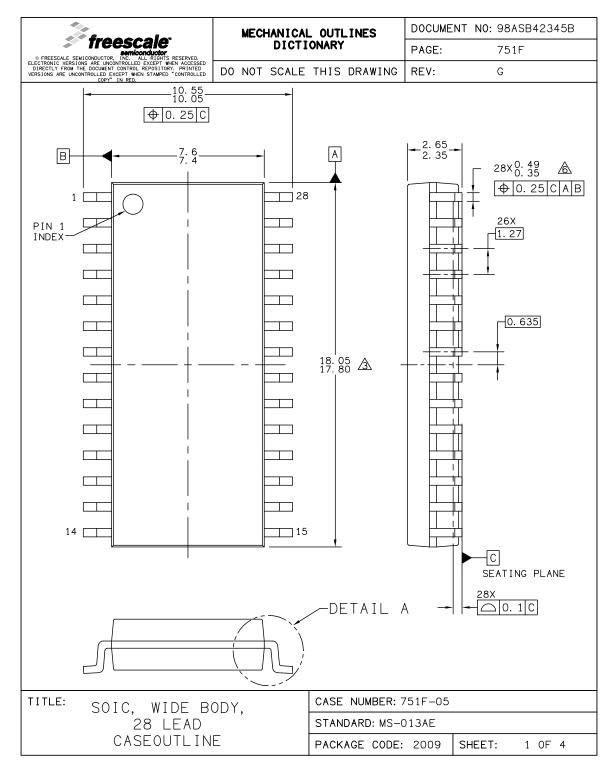

# **10** Package Mechanical Outline Drawings

## 10.1 28-pin SOIC Package

MC56F8006/MC56F8002 Digital Signal Controller, Rev. 4

#### **Interrupt Vector Table**

| Peripheral         | Vector<br>Number | User<br>Encoding | Priority<br>Level | Vector Base<br>Address + | Interrupt Function                           |

|--------------------|------------------|------------------|-------------------|--------------------------|----------------------------------------------|

| Reserved           | 34- 39           | 0x22-0x27        | 0                 | P:0x44 -<br>P:0x4E       | Reserved                                     |

| core               | 40               | N/A              | 0                 | P:0x50                   | SW Interrupt 0                               |

| core               | 41               | N/A              | 1                 | P:0x52                   | SW Interrupt 1                               |

| core               | 42               | N/A              | 2                 | P:0x54                   | SW Interrupt 2                               |

| core               | 43               | N/A              | 3                 | P:0x56                   | SW Interrupt 3                               |

| SWILP              | 44               | N/A              | -1                | P:0x58                   | SW Interrupt Low Priority                    |

| USER1              | 45               | N/A              | 1                 | P:0x5A                   | User Programmable Priority Level 1 Interrupt |

| USER2              | 46               | N/A              | 1                 | P:0x5C                   | User Programmable Priority Level 1 Interrupt |

| USER3              | 47               | N/A              | 1                 | P:0x5E                   | User Programmable Priority Level 1 Interrupt |

| USER4              | 48               | N/A              | 2                 | P:0x60                   | User Programmable Priority Level 2 Interrupt |

| USER5              | 49               | N/A              | 2                 | P:0x62                   | User Programmable Priority Level 2 Interrupt |

| USER6 <sup>3</sup> | 50               | N/A              | 2                 | P:0x64                   | User Programmable Priority Level 2 Interrupt |

### Table 43. Interrupt Vector Table Contents<sup>1</sup> (continued)

<sup>1</sup> Two words are allocated for each entry in the vector table. This does not allow the full address range to be referenced from the vector table, providing only 19 bits of address.

<sup>2</sup> If the VBA is set to the reset value, the first two locations of the vector table overlay the chip reset addresses because the reset address would match the base of this vector table.

<sup>3</sup> USER6 vector can be defined as a fast interrupt if the instruction located in this vector location is not a JSR or BSR instruction. Please see section 9.3.3.3 of *DSP56800E 16-Bit Core Reference Manual* for detail.

# Appendix B Peripheral Register Memory Map and Reset Value

### NOTE

In Table 44, ADC0 stands for ADCA, ADC1 stands for ADCB, and GPIOn is the same as GPIO\_n (for example, GPIOA\_PUR is the same as GPIO\_A\_PUR).

Table 44. Detailed Peripheral Memory Map

| Offset<br>Addr.<br>(Hex) | Reset<br>Value<br>(Hex) | Periph. | Register        | Bit<br>15 | 14                | 13  | 12    | 11  | 10    | 9   | 8     | 7          | 6          | 5      | 4    | 3       | 2     | 1   | Bit<br>0 |

|--------------------------|-------------------------|---------|-----------------|-----------|-------------------|-----|-------|-----|-------|-----|-------|------------|------------|--------|------|---------|-------|-----|----------|

| 00                       | 0000                    | TMR0    | TMR0_<br>COMP1  |           | COMPARISON_1      |     |       |     |       |     |       |            |            |        |      |         |       |     |          |

| 01                       | 0000                    | TMR0    | TMR0_<br>COMP2  |           | COMPARISON_2      |     |       |     |       |     |       |            |            |        |      |         |       |     |          |

| 02                       | 0000                    | TMR0    | TMR0_<br>CAPT   |           | CAPTURE           |     |       |     |       |     |       |            |            |        |      |         |       |     |          |

| 03                       | 0000                    | TMR0    | TMR0_<br>LOAD   |           | LOAD              |     |       |     |       |     |       |            |            |        |      |         |       |     |          |

| 04                       | 0000                    | TMR0    | TMR0_<br>HOLD   |           | HOLD              |     |       |     |       |     |       |            |            |        |      |         |       |     |          |

| 05                       | 0000                    | TMR0    | TMR0_<br>CNTR   |           |                   |     |       |     |       |     | COUI  | NTER       |            |        |      |         |       |     |          |

| 06                       | 0000                    | TMR0    | TMR0_<br>CTRL   |           | СМ                |     | PCS   |     |       |     | S     | SCS ONCE   |            | LENGTH | DIR  | Co_INIT |       | ОМ  |          |

| 07                       | 0000                    | TMR0    | TMR0_<br>SCTRL  | TCF       | TCFIE             | TOF | TOFIE | IEF | IEFIE | IPS | INPUT | CAPT<br>MC | URE_<br>DE | MSTR   | EEOF | VAL     | FORCE | OPS | OEN      |

| 08                       | 0000                    | TMR0    | TMR0_<br>CMPLD1 |           | COMPARATOR_LOAD_1 |     |       |     |       |     |       |            |            |        |      |         |       |     |          |

| 09                       | 0000                    | TMR0    | TMR0_<br>CMPLD2 |           | COMPARATOR_LOAD_2 |     |       |     |       |     |       |            |            |        |      |         |       |     |          |

Peripheral Register Memory Map and Reset Value