# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 59                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 2x16b, 8x10b; D/A 2x12b                                       |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 100-TQFP                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f060-gqr   |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 14.7.1.Enable/Reset WDT                                                               | 166 |

|---------------------------------------------------------------------------------------|-----|

| 14.7.2.Disable WDT                                                                    |     |

| 14.7.3.Disable WDT Lockout                                                            |     |

| 14.7.4.Setting WDT Interval                                                           |     |

| 15. Oscillators                                                                       |     |

| 15.1.Programmable Internal Oscillator                                                 |     |

| 15.2.External Oscillator Drive Circuit                                                |     |

|                                                                                       |     |

| 15.3.System Clock Selection<br>15.4.External Crystal Example                          |     |

|                                                                                       |     |

| 15.5.External RC Example                                                              |     |

| 15.6.External Capacitor Example                                                       |     |

| 16. Flash Memory                                                                      |     |

| 16.1.Programming The Flash Memory                                                     |     |

| 16.2.Non-volatile Data Storage                                                        |     |

| 16.3.Security Options                                                                 |     |

| 16.3.1.Summary of Flash Security Options                                              |     |

| 17. External Data Memory Interface and On-Chip XRAM                                   |     |

| 17.1.Accessing XRAM                                                                   |     |

| 17.1.1.16-Bit MOVX Example                                                            |     |

| 17.1.2.8-Bit MOVX Example                                                             |     |

| 17.2.Configuring the External Memory Interface                                        |     |

| 17.3.Port Selection and Configuration                                                 |     |

| 17.4.Multiplexed and Non-multiplexed Selection                                        |     |

| 17.4.1.Multiplexed Configuration                                                      | 190 |

| 17.4.2.Non-multiplexed Configuration                                                  |     |

| 17.5.Memory Mode Selection                                                            |     |

| 17.5.1.Internal XRAM Only                                                             |     |

| 17.5.2.Split Mode without Bank Select                                                 | 192 |

| 17.5.3.Split Mode with Bank Select                                                    | 193 |

| 17.5.4.External Only                                                                  | 193 |

| 17.6.Timing                                                                           | 194 |

| 17.6.1.Non-multiplexed Mode                                                           | 196 |

| 17.6.1.1.16-bit MOVX: EMI0CF[4:2] = '101', '110', or '111'                            | 196 |

| 17.6.1.2.8-bit MOVX without Bank Select: EMI0CF[4:2] = '101' or '111'                 | 197 |

| 17.6.1.3.8-bit MOVX with Bank Select: EMI0CF[4:2] = '110'                             | 198 |

|                                                                                       |     |

| 17.6.2.Multiplexed Mode<br>17.6.2.1.16-bit MOVX: EMI0CF[4:2] = '001', '010', or '011' | 199 |

| 17.6.2.2.8-bit MOVX without Bank Select: EMI0CF[4:2] = '001' or '011'                 |     |

| 17.6.2.3.8-bit MOVX with Bank Select: EMI0CF[4:2] = (010'                             |     |

| 18. Port Input/Output                                                                 |     |

| 18.1.Ports 0 through 3 and the Priority Crossbar Decoder                              | 205 |

| 18.1.1.Crossbar Pin Assignment and Allocation                                         |     |

| 18.1.2.Configuring the Output Modes of the Port Pins                                  |     |

| 18.1.3.Configuring Port Pins as Digital Inputs                                        |     |

| 18.1.4.Weak Pull-ups                                                                  |     |

|                                                                                       | -01 |

|     | Figure 7.14. ADC2LTL: ADC2 Less-Than Data Low Byte Register<br>Figure 7.15. ADC Window Compare Example: Right-Justified Single-Ended Data<br>Figure 7.16. ADC Window Compare Example: Left-Justified Single-Ended Data<br>Figure 7.17. ADC Window Compare Example: Right-Justified Differential Data | . 99<br>. 99<br>100 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| ~   | Figure 7.18. ADC Window Compare Example: Left-Justified Differential Data                                                                                                                                                                                                                            |                     |

| 8.  | DACs, 12-Bit Voltage Mode (DAC0 and DAC1, C8051F060/1/2/3)                                                                                                                                                                                                                                           |                     |

|     | Figure 8.1. DAC Functional Block Diagram                                                                                                                                                                                                                                                             |                     |

|     | Figure 8.2. DACOH: DACO High Byte Register                                                                                                                                                                                                                                                           |                     |

|     | Figure 8.3. DACOL: DACO Low Byte Register                                                                                                                                                                                                                                                            |                     |

|     | Figure 8.4. DAC0CN: DAC0 Control Register                                                                                                                                                                                                                                                            |                     |

|     | Figure 8.5. DAC1H: DAC1 High Byte Register<br>Figure 8.6. DAC1L: DAC1 Low Byte Register                                                                                                                                                                                                              |                     |

|     | Figure 8.7. DAC1CN: DAC1 Control Register                                                                                                                                                                                                                                                            |                     |

| ٩   | Voltage Reference 2 (C8051F060/2)                                                                                                                                                                                                                                                                    |                     |

| Э.  | Figure 9.1. Voltage Reference Functional Block Diagram                                                                                                                                                                                                                                               |                     |

|     | Figure 9.2. REF2CN: Reference Control Register 2                                                                                                                                                                                                                                                     |                     |

| 10  | Voltage Reference 2 (C8051F061/3)                                                                                                                                                                                                                                                                    |                     |

|     | Figure 10.1. Voltage Reference Functional Block Diagram                                                                                                                                                                                                                                              |                     |

|     | Figure 10.2. REF2CN: Reference Control Register 2                                                                                                                                                                                                                                                    |                     |

| 11. | .Voltage Reference 2 (C8051F064/5/6/7)                                                                                                                                                                                                                                                               |                     |

|     | Figure 11.1. Voltage Reference Functional Block Diagram                                                                                                                                                                                                                                              |                     |

|     | Figure 11.2. REF2CN: Reference Control Register 2                                                                                                                                                                                                                                                    |                     |

| 12  | Comparators                                                                                                                                                                                                                                                                                          |                     |

|     | Figure 12.1. Comparator Functional Block Diagram                                                                                                                                                                                                                                                     | 117                 |

|     | Figure 12.2. Comparator Hysteresis Plot                                                                                                                                                                                                                                                              | 118                 |

|     | Figure 12.3. CPTnCN: Comparator 0, 1, and 2 Control Register                                                                                                                                                                                                                                         |                     |

|     | Figure 12.4. CPTnMD: Comparator Mode Selection Register                                                                                                                                                                                                                                              |                     |

| 13  | CIP-51 Microcontroller                                                                                                                                                                                                                                                                               |                     |

|     | Figure 13.1. CIP-51 Block Diagram                                                                                                                                                                                                                                                                    |                     |

|     | Figure 13.2. Memory Map                                                                                                                                                                                                                                                                              |                     |

|     | Figure 13.3. SFR Page Stack                                                                                                                                                                                                                                                                          | 133                 |

|     | Figure 13.4. SFR Page Stack While Using SFR Page 0x0F To Access Port 5                                                                                                                                                                                                                               | 134                 |

|     | Figure 13.5. SFR Page Stack After ADC2 Window Comparator Interrupt Occurs.                                                                                                                                                                                                                           |                     |

|     | Figure 13.6. SFR Page Stack Upon PCA Interrupt Occurring During an ADC2 ISR                                                                                                                                                                                                                          |                     |

|     | 136<br>Figure 12.7 SEP Dage Stock Upon Beturn From DCA Interrupt                                                                                                                                                                                                                                     | 107                 |

|     | Figure 13.7. SFR Page Stack Upon Return From PCA Interrupt<br>Figure 13.8. SFR Page Stack Upon Return From ADC2 Window Interrupt                                                                                                                                                                     |                     |

|     | Figure 13.9. SFRPGCN: SFR Page Control Register                                                                                                                                                                                                                                                      |                     |

|     | Figure 13.10. SFRPAGE: SFR Page Register                                                                                                                                                                                                                                                             |                     |

|     | Figure 13.11. SFRNEXT: SFR Next Register                                                                                                                                                                                                                                                             |                     |

|     | Figure 13.12. SFRLAST: SFR Last Register                                                                                                                                                                                                                                                             |                     |

|     | Figure 13.13. SP: Stack Pointer                                                                                                                                                                                                                                                                      |                     |

|     | Figure 13.14. DPL: Data Pointer Low Byte                                                                                                                                                                                                                                                             |                     |

|     | Figure 13.15. DPH: Data Pointer High Byte                                                                                                                                                                                                                                                            |                     |

|     | Figure 13.16. PSW: Program Status Word                                                                                                                                                                                                                                                               |                     |

#### 1.1.3. Additional Features

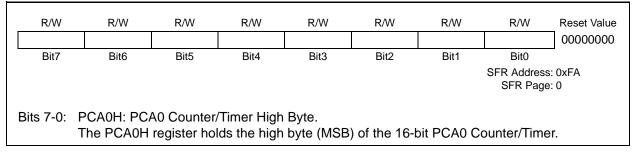

The C8051F06x MCU family includes several key enhancements to the CIP-51 core and peripherals to improve overall performance and ease of use in end applications.

The extended interrupt handler provides 22 interrupt sources into the CIP-51, allowing the numerous analog and digital peripherals to interrupt the controller. An interrupt driven system requires less intervention by the MCU, giving it more effective throughput. The extra interrupt sources are very useful when building multi-tasking, real-time systems.

There are up to seven reset sources for the MCU: an on-board VDD monitor, a Watchdog Timer, a missing clock detector, a voltage level detection from Comparator0, a forced software reset, the CNVSTR2 input pin, and the /RST pin. The /RST pin is bi-directional, accommodating an external reset, or allowing the internally generated POR to be output on the /RST pin. Each reset source except for the VDD monitor and Reset Input pin may be disabled by the user in software; the VDD monitor is enabled/disabled via the MONEN pin. The Watchdog Timer may be permanently enabled in software after a power-on reset during MCU initialization.

The MCU has an internal, stand alone clock generator which is used by default as the system clock after any reset. If desired, the clock source may be switched on the fly to the external oscillator, which can use a crystal, ceramic resonator, capacitor, RC, or external clock source to generate the system clock. This can be extremely useful in low power applications, allowing the MCU to run from a slow (power saving) external crystal source, while periodically switching to the fast (up to 25 MHz) internal oscillator as needed.

Figure 1.6. On-Board Clock and Reset

26

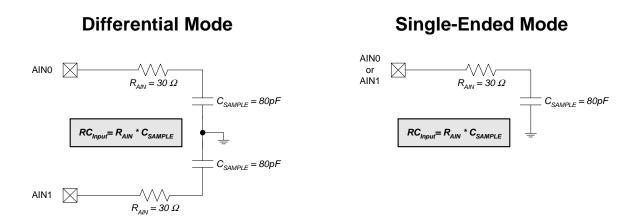

### 5.3.3. Settling Time Requirements

The ADC requires a minimum tracking time before an accurate conversion can be performed. This tracking time is determined by the ADC input resistance, the ADC sampling capacitance, any external source resistance, and the accuracy required for the conversion. Figure 5.5 shows the equivalent ADC input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required settling time for a given settling accuracy (*SA*) may be approximated by Equation 5.1. An absolute minimum tracking time of 280 ns is required prior to the start of a conversion.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

#### Equation 5.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the ADC input resistance and any external source resistance. *n* is the ADC resolution in bits (16).

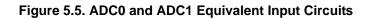

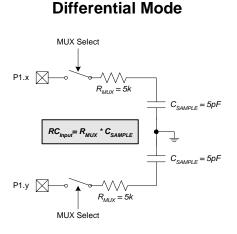

#### 7.2.3. Settling Time Requirements

A minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the AMUX2 resistance, the ADC2 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the minimum tracking time requirements.

Figure 7.4 shows the equivalent ADC2 input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required ADC2 settling time for a given settling accuracy (SA) may be approximated by Equation 7.1. When measuring the Temperature Sensor output,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 7.1 for ADC2 minimum settling time requirements.

#### **Equation 7.1. ADC2 Settling Time Requirements**

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX2 resistance and any external source resistance.

*n* is the ADC resolution in bits (10).

#### Figure 7.4. ADC2 Equivalent Input Circuits

Single-Ended Mode

# 7.3. Programmable Window Detector

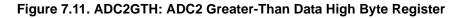

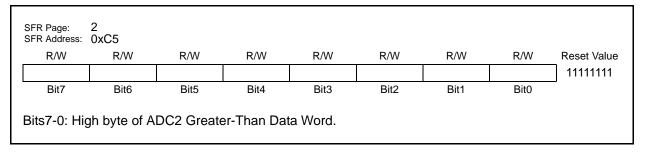

The ADC Programmable Window Detector continuously compares the ADC2 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD2WINT in register ADC2CN) can also be used in polled mode. The ADC2 Greater-Than (ADC2GTH, ADC2GTL) and Less-Than (ADC2LTH, ADC2LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC2 Less-Than and ADC2 Greater-Than registers.

| R/W   | R/W                         | R/W           | R/W           | R/W           | R/W          | R/W       | R/W        | Reset Valu              |

|-------|-----------------------------|---------------|---------------|---------------|--------------|-----------|------------|-------------------------|

| PDMA0 | PS1                         | PCAN0         | PADC2         | PWADC2        | PT4          | PADC1     | PT3        | 0000000                 |

| Bit7  | Bit6                        | Bit5          | Bit4          | Bit3          | Bit2         | Bit1      | Bit0       |                         |

|       |                             |               |               |               |              |           | SFR Addres | s: 0xF7<br>e: All Pages |

|       |                             |               |               |               |              |           | SERFAY     | e. All Fayes            |

| Bit7: | PDMA0: DM                   | A0 Interrup   | t Priority Co | ontrol.       |              |           |            |                         |

|       | This bit sets               |               |               |               |              |           |            |                         |

|       | 0: DMA0 inte                | errupt set to | low priority  |               |              |           |            |                         |

|       | 1: DMA0 inte                | errupt set to | high priorit  | y.            |              |           |            |                         |

| Bit6: | PS1: UART1                  | I Interrupt F | Priority Cont | rol.          |              |           |            |                         |

|       | This bit sets               | the priority  | of the UAR    | T1 interrupt. |              |           |            |                         |

|       | 0: UART1 in                 | terrupt set t | o low priori  | ty.           |              |           |            |                         |

|       | 1: UART1 in                 |               | 0 1           |               |              |           |            |                         |

| Bit5: | PCAN0: CAI                  | •             | •             |               |              |           |            |                         |

|       | This bit sets               |               |               |               |              |           |            |                         |

|       | 0: CAN Inter                | •             |               |               |              |           |            |                         |

|       | 1: CAN Inter                |               |               |               |              |           |            |                         |

| Bit4: | PADC2: ADC                  |               |               |               |              |           |            |                         |

|       | This bit sets               |               |               |               |              | nterrupt. |            |                         |

|       | 0: ADC2 End                 |               |               |               |              |           |            |                         |

|       | 1: ADC2 End                 |               |               |               | • •          |           |            |                         |

| Bit3: | PWADC2: A                   |               |               |               | Priority C   | Control.  |            |                         |

|       | 0: ADC2 Wir                 |               | •             |               |              |           |            |                         |

|       | 1: ADC2 Wir                 |               | •             | • • •         |              |           |            |                         |

| Bit2: | PT4: Timer 4                |               |               |               |              |           |            |                         |

|       | This bit sets               |               |               |               |              |           |            |                         |

|       | 0: Timer 4 in               |               |               |               |              |           |            |                         |

| Bit1: | 1: Timer 4 in<br>PADC1: AD0 |               |               |               | ity Contro   |           |            |                         |

| 5111. | This bit sets               |               |               |               |              |           |            |                         |

|       | 0: ADC1 End                 |               |               |               |              | •         |            |                         |

|       | 1: ADC1 End                 |               |               |               |              |           |            |                         |

| Bit0: | PT3: Timer 3                |               |               |               | i priority i | evel.     |            |                         |

| 5110. | This bit sets               |               |               |               | -            |           |            |                         |

|       | 0: Timer 3 in               |               |               |               | 5.           |           |            |                         |

|       |                             | ionupi set i  |               | (y 16v6).     |              |           |            |                         |

# Figure 13.24. EIP2: Extended Interrupt Priority 2

#### Table 15.1. Internal Oscillator Electrical Characteristics

-40°C to +85°C unles otherwise specified.

| Parameter                                           | Conditions   | Min | Тур  | Max | Units |

|-----------------------------------------------------|--------------|-----|------|-----|-------|

| Calibrated Internal Oscillator<br>Frequency         |              | 24  | 24.5 | 25  | MHz   |

| Internal Oscillator Supply<br>Current (3.0V Supply) | OSCICN.7 = 1 |     | 550  |     | μA    |

#### 15.2. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/ resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 15.1. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 and/or XTAL1 pin(s) as shown in Option 2, 3, or 4 of Figure 15.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see Figure 15.5).

#### 15.3. System Clock Selection

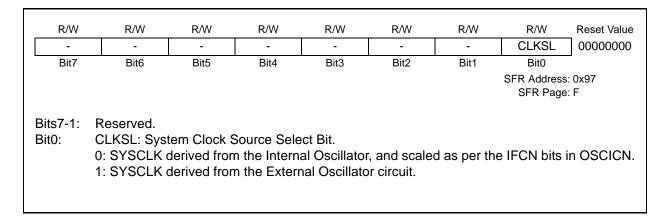

The CLKSL bit in register CLKSEL selects which oscillator generates the system clock. CLKSL must be set to '1' for the system clock to run from the external oscillator; however the external oscillator may still clock peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal and external oscillator, so long as the selected oscillator is enabled and settled. The internal oscillator requires little start-up time, and may be enabled and selected as the system clock in the same write to OSCICN. External crystals and ceramic resonators typically require a start-up time before they are settled and ready for use as the system clock. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to '1' by hardware when the external oscillator is settled. To avoid reading a false XTLVLD, in crystal mode software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD. RC and C modes typically require no startup time.

Figure 15.4. CLKSEL: Oscillator Clock Selection Register

Step 8. Clear the PSWE bit to redirect MOVX write commands to the XRAM data space.

Step 9. Re-enable interrupts.

Write/Erase timing is automatically controlled by hardware. Note that code execution in the 8051 is stalled while the Flash is being programmed or erased.

| Parameter        | Conditions          | Min  | Тур     | Max | Units       |

|------------------|---------------------|------|---------|-----|-------------|

| Flash Size *     | C8051F060/1/2/3/4/5 |      | 65664 † | •   | Bytes       |

| Flash Size *     | C8051F066/7         |      | 32896   |     | Bytes       |

| Endurance        |                     | 20 k | 100 k   |     | Erase/Write |

| Erase Cycle Time |                     | 10   | 12      | 14  | ms          |

| Write Cycle Time |                     | 40   | 50      | 60  | μs          |

| Table 16.1. Flash | Electrical | Characteristics |

|-------------------|------------|-----------------|

|-------------------|------------|-----------------|

\* Includes 128-byte Scratch Pad Area

† 1024 Bytes at location 0xFC00 to 0xFFFF are reserved.

# 16.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction (as described in the previous section) and read using the MOVC instruction.

An additional 128-byte sector of Flash memory is included for non-volatile data storage. Its smaller sector size makes it particularly well suited as general purpose, non-volatile scratchpad memory. Even though Flash memory can be written a single byte at a time, an entire sector must be erased first. In order to change a single byte of a multi-byte data set, the data must be moved to temporary storage. The 128-byte sector size facilitates updating data without wasting program memory or RAM space. The 128-byte sector is double-mapped over the normal Flash memory area; its address ranges from 0x00 to 0x7F (see Figure 16.1 and Figure 16.2). To access this 128-byte sector, the SFLE bit in PSCTL must be set to logic 1. Code execution from this 128-byte scratchpad sector is not supported.

# 17. External Data Memory Interface and On-Chip XRAM

The C8051F060/1/2/3/4/5/6/7 MCUs include 4 k bytes of on-chip RAM mapped into the external data memory space (XRAM). In addition, the C8051F060/2/4/6 include an External Data Memory Interface which can be used to access off-chip memories and memory-mapped devices connected to the GPIO ports. The external memory space may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using the MOVX indirect addressing mode using R0 or R1. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMI0CN, shown in Figure 17.1). Note: the MOVX instruction can also be used for writing to the Flash memory. See Section "16. Flash Memory" on page 177 for details. The MOVX instruction accesses XRAM by default.

# 17.1. Accessing XRAM

The XRAM memory space (both internal and external) is accessed using the MOVX instruction. The MOVX instruction has two forms, both of which use an indirect addressing method. The first method uses the Data Pointer, DPTR, a 16-bit register which contains the effective address of the XRAM location to be read or written. The second method uses R0 or R1 in combination with the EMI0CN register to generate the effective XRAM address. Examples of both of these methods are given below.

#### 17.1.1. 16-Bit MOVX Example

The 16-bit form of the MOVX instruction accesses the memory location pointed to by the contents of the DPTR register. The following series of instructions reads the value of the byte at address 0x1234 into the accumulator A:

| MOV  | DPTR, #1234h | ; load DPTR with 16-bit address to read (0x1234) |  |

|------|--------------|--------------------------------------------------|--|

| MOVX | A, @DPTR     | ; load contents of 0x1234 into accumulator A     |  |

The above example uses the 16-bit immediate MOV instruction to set the contents of DPTR. Alternately, the DPTR can be accessed through the SFR registers DPH, which contains the upper 8-bits of DPTR, and DPL, which contains the lower 8-bits of DPTR.

#### 17.1.2. 8-Bit MOVX Example

The 8-bit form of the MOVX instruction uses the contents of the EMI0CN SFR to determine the upper 8-bits of the effective address to be accessed and the contents of R0 or R1 to determine the lower 8-bits of the effective address to be accessed. The following series of instructions read the contents of the byte at address 0x1234 into the accumulator A.

| MOV  | EMIOCN, #12h | ; load high byte of address into EMIOCN      |

|------|--------------|----------------------------------------------|

| MOV  | R0, #34h     | ; load low byte of address into RO (or R1)   |

| MOVX | a, @R0       | ; load contents of 0x1234 into accumulator A |

# C8051F060/1/2/3/4/5/6/7

| Parameter           | Description                    | Min                   | Max                    | Units |

|---------------------|--------------------------------|-----------------------|------------------------|-------|

| T <sub>SYSCLK</sub> | System Clock Period            | 40                    |                        | ns    |

| T <sub>ACS</sub>    | Address / Control Setup Time   | 0                     | 3*T <sub>SYSCLK</sub>  | ns    |

| T <sub>ACW</sub>    | Address / Control Pulse Width  | 1*T <sub>SYSCLK</sub> | 16*T <sub>SYSCLK</sub> | ns    |

| T <sub>ACH</sub>    | Address / Control Hold Time    | 0                     | 3*T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEH</sub>   | Address Latch Enable High Time | 1*T <sub>SYSCLK</sub> | 4*T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEL</sub>   | Address Latch Enable Low Time  | 1*T <sub>SYSCLK</sub> | 4*T <sub>SYSCLK</sub>  | ns    |

| T <sub>WDS</sub>    | Write Data Setup Time          | 1*T <sub>SYSCLK</sub> | 19*T <sub>SYSCLK</sub> | ns    |

| T <sub>WDH</sub>    | Write Data Hold Time           | 0                     | 3*T <sub>SYSCLK</sub>  | ns    |

| T <sub>RDS</sub>    | Read Data Setup Time           | 20                    |                        | ns    |

| T <sub>RDH</sub>    | Read Data Hold Time            | 0                     |                        | ns    |

Table 17.1. AC Parameters for External Memory Interface

# C8051F060/1/2/3/4/5/6/7

| R/W                                                                                                                                                                                                                                                                                                                                                                                                      | R/W                                                                                                                                                                                                               | R/W  | R/W  | R/W  | R/W  | R/W  | R/W                       | Reset Value        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|---------------------------|--------------------|--|

| P3.7                                                                                                                                                                                                                                                                                                                                                                                                     | P3.6                                                                                                                                                                                                              | P3.5 | P3.4 | P3.3 | P3.2 | P3.1 | P3.0                      | 11111111           |  |

| Bit7                                                                                                                                                                                                                                                                                                                                                                                                     | Bit6                                                                                                                                                                                                              | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0                      | Bit<br>Addressable |  |

|                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |      |      |      |      |      | SFR Address:<br>SFR Page: |                    |  |

| <ul> <li>Bits7-0: P3.[7:0]: Port3 Output Latch Bits.<br/>(Write - Output appears on I/O pins per XBR0, XBR1, XBR2, and XBR3 Registers)</li> <li>0: Logic Low Output.</li> <li>1: Logic High Output (open if corresponding P3MDOUT.n bit = 0).<br/>(Read - Regardless of XBR0, XBR1, XBR2, and XBR3 Register settings).</li> <li>0: P3.n pin is logic low.</li> <li>1: P3.n pin is logic high.</li> </ul> |                                                                                                                                                                                                                   |      |      |      |      |      |                           |                    |  |

| Note:                                                                                                                                                                                                                                                                                                                                                                                                    | Although P3 is not brought out to pins on the C8051F061/3/5/7 devices, the Port Data regis-<br>ter is still present and can be used by software. See "Configuring Ports which are not Pinned<br>Out" on page 219. |      |      |      |      |      |                           |                    |  |

#### Figure 18.17. P3: Port3 Data Register

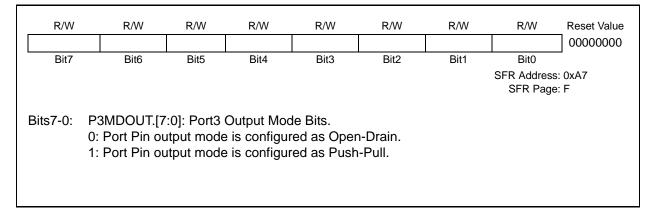

#### Figure 18.18. P3MDOUT: Port3 Output Mode Register

# C8051F060/1/2/3/4/5/6/7

| R/W                                                                                                                                                                                                                                                                                                                                                     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W                     | Reset Value        |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------------------------|--------------------|--|

| P5.7                                                                                                                                                                                                                                                                                                                                                    | P5.6 | P5.5 | P5.4 | P5.3 | P5.2 | P5.1 | P5.0                    | 11111111           |  |

| Bit7                                                                                                                                                                                                                                                                                                                                                    | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0                    | Bit<br>Addressable |  |

|                                                                                                                                                                                                                                                                                                                                                         |      |      |      |      |      |      | SFR Address<br>SFR Page | •···= •            |  |

| <ul> <li>Bits7-0: P5.[7:0]: Port5 Output Latch Bits.</li> <li>Write - Output appears on I/O pins.</li> <li>0: Logic Low Output.</li> <li>1: Logic High Output (open, if corresponding P5MDOUT bit = 0). See Figure 18.22.</li> <li>Read - Returns states of I/O pins.</li> <li>0: P5.n pin is logic low.</li> <li>1: P5.n pin is logic high.</li> </ul> |      |      |      |      |      |      |                         |                    |  |

| Note: P5.[7:0] can be driven by the External Data Memory Interface (as Address[15:8] in Non-mul-<br>tiplexed mode). See Section "17. External Data Memory Interface and On-Chip XRAM" on<br>page 187 for more information about the External Memory Interface.                                                                                          |      |      |      |      |      |      |                         |                    |  |

#### Figure 18.21. P5: Port5 Data Register

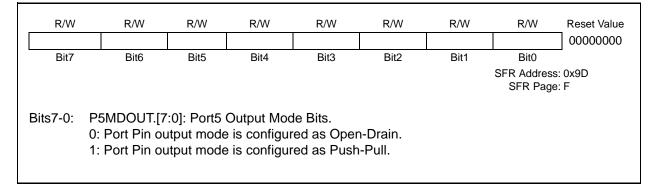

#### Figure 18.22. P5MDOUT: Port5 Output Mode Register

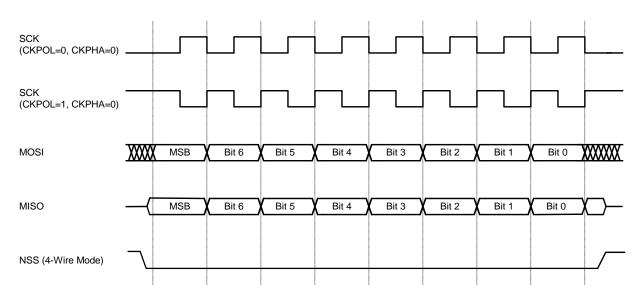

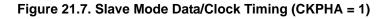

# 21.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 21.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and reenabling SPI0 with the SPIEN bit. Figure 21.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

# 21.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

Note that all of the following bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- 2. The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- 3. The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

Figure 21.6. Slave Mode Data/Clock Timing (CKPHA = 0)

| R/W      | R/W                                            | R/W                                                                                                                                                                                                                                                                                                                                                                                   | R/W              | R/W  | R/W  | R/W  | R/W                              | Reset Value |  |  |

|----------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|----------------------------------|-------------|--|--|

| Bit7     | Bit6                                           | Bit5                                                                                                                                                                                                                                                                                                                                                                                  | Bit4             | Bit3 | Bit2 | Bit1 | Bit0                             | 0000000     |  |  |

|          | Ыю                                             | 010                                                                                                                                                                                                                                                                                                                                                                                   | DIL <del>I</del> |      | DILZ | DICI | SFR Address: 0x99<br>SFR Page: 1 |             |  |  |

| Bits7-0: | This SFR ac<br>data is writte<br>sion. Writing | BUF1[7:0]: Serial Data Buffer Bits 7-0 (MSB-LSB).<br>his SFR accesses two registers; a transmit shift register and a receive latch register. When<br>ata is written to SBUF1, it goes to the transmit shift register and is held for serial transmis-<br>on. Writing a byte to SBUF1 is what initiates the transmission. A read of SBUF1 returns the<br>ontents of the receive latch. |                  |      |      |      |                                  |             |  |  |

Figure 23.8. SBUF1: Serial (UART1) Port Data Buffer Register

### 24.2. Timer 2, Timer 3, and Timer 4

Timers 2, 3, and 4 are 16-bit counter/timers, each formed by two 8-bit SFRs: TMRnL (low byte) and TMRnH (high byte) where n = 2, 3, and 4 for timers 2, 3, and 4 respectively. These timers feature autoreload, capture, and toggle output modes with the ability to count up or down. Capture Mode and Autoreload mode are selected using bits in the Timer 2, 3, and 4 Control registers (TMRnCN). Toggle output mode is selected using the Timer 2, 3, and 4 Configuration registers (TMRnCF). These timers may also be used to generate a square-wave at an external pin. Timers 2, 3, and 4 can use either the system clock (divided by one, two, or twelve), external clock (divided by eight) or transitions on an external input pin as its clock source. Timer 2 and 3 can be used to start an ADC Data Conversion and Timers 2, 3, and 4 can schedule DAC outputs. Timers 1, 2, 3, or 4 may be used to generate baud rates for UART 0. Only Timer 1 can be used to generate baud rates for UART 1.

The Counter/Timer Select bit C/Tn bit (TMRnCN.1) configures the peripheral as a counter or timer. Clearing C/Tn configures the Timer to be in a timer mode (i.e., the selected timer clock source as the input for the timer). When C/Tn is set to 1, the timer is configured as a counter (i.e., high-to-low transitions at the Tn input pin increment (or decrement) the counter/timer register. Refer to Section "18.1. Ports 0 through 3 and the Priority Crossbar Decoder" on page 205 for information on selecting and configuring external I/O pins for digital peripherals, such as the Tn pin.

Timer 2, 3, and 4 can use either SYSCLK, SYSCLK divided by 2, SYSCLK divided by 12, an external clock divided by 8, or high-to-low transitions on the Tn input pin as its clock source when operating in Counter/ Timer with Capture mode. Clearing the C/Tn bit (TnCON.1) selects the system clock/external clock as the input for the timer. The Timer Clock Select bits TnM0 and TnM1 in TMRnCF can be used to select the system clock undivided, system clock divided by two, system clock divided by 12, or an external clock provided at the XTAL1/XTAL2 pins divided by 8 (see Figure 24.14). When C/Tn is set to logic 1, a high-to-low transition at the Tn input pin increments the counter/timer register (i.e., configured as a counter).

#### 24.2.1. Configuring Timer 2, 3, and 4 to Count Down

Timers 2, 3, and 4 have the ability to count down. When the timer's respective Decrement Enable Bit (DCENn) in the Timer Configuration Register (See Figure 24.14) is set to '1', the timer can then count *up* or *down*. When DCENn = 1, the direction of the timer's count is controlled by the TnEX pin's logic level. When TnEX = 1, the counter/timer will count up; when TnEX = 0, the counter/timer will count down. To use this feature, TnEX must be enabled in the digital crossbar and configured as a digital input.

Note: When DCENn = 1, other functions of the TnEX input (i.e., capture and auto-reload) are not available. TnEX will only control the direction of the timer when DCENn = 1.

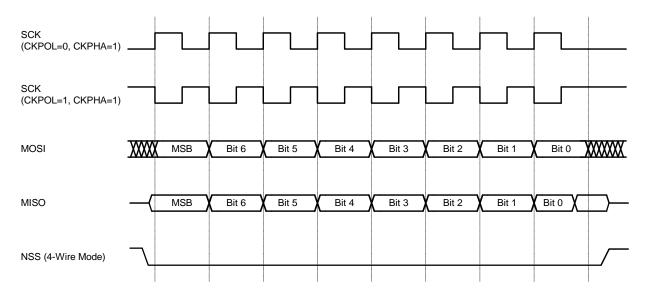

### 25.2.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes PCA0 to capture the value of the PCA0 counter/ timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software.

#### Figure 25.4. PCA Capture Mode Diagram

Note: The signal at CEXn must be high or low for at least 2 system clock cycles in order to be valid.

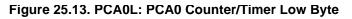

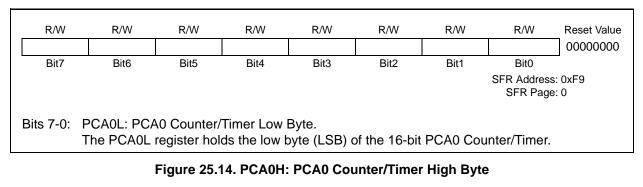

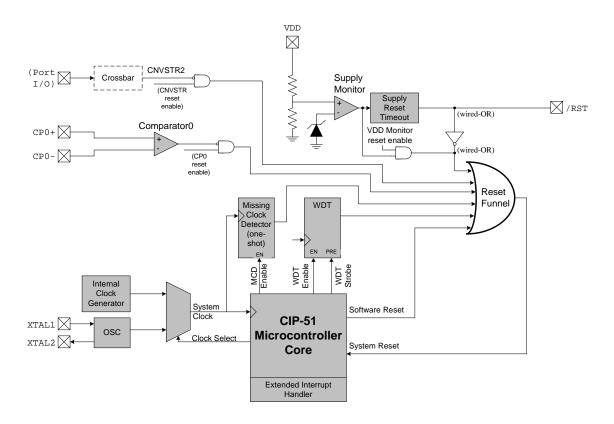

# 25.3. Register Descriptions for PCA0

Following are detailed descriptions of the special function registers related to the operation of PCA0.

| R/W   | R/W                                                                                                                                                                         | R/W           | R/W        | R/W       | R/W           | R/W          | R/W                     | Reset Valu |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|-----------|---------------|--------------|-------------------------|------------|--|--|--|

| CF    | CR                                                                                                                                                                          | CCF5          | CCF4       | CCF3      | CCF2          | CCF1         | CCF0                    | 0000000    |  |  |  |

| Bit7  | Bit6                                                                                                                                                                        | Bit5          | Bit4       | Bit3      | Bit2          | Bit1         | Bit0                    |            |  |  |  |

|       |                                                                                                                                                                             |               |            |           |               |              | SFR Address<br>SFR Page |            |  |  |  |

| Bit7: | CF: PCA Counter/Timer Overflow Flag.                                                                                                                                        |               |            |           |               |              |                         |            |  |  |  |

|       | Set by hardware when the PCA0 Counter/Timer overflows from 0xFFFF to 0x0000. When                                                                                           |               |            |           |               |              |                         |            |  |  |  |

|       | the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the CPU to ver                                                                                |               |            |           |               |              |                         |            |  |  |  |

|       | tor to the CF interrupt service routine. This bit is not automatically cleared by hardware and                                                                              |               |            |           |               |              |                         |            |  |  |  |

|       | must be clea                                                                                                                                                                |               |            |           |               |              |                         |            |  |  |  |

| Bit6: | CR: PCA0 C                                                                                                                                                                  | counter/Tim   | er Run Con | trol.     |               |              |                         |            |  |  |  |

|       | This bit enables/disables the PCA0 Counter/Timer.                                                                                                                           |               |            |           |               |              |                         |            |  |  |  |

|       | 0: PCA0 Cou                                                                                                                                                                 |               |            |           |               |              |                         |            |  |  |  |

|       | 1: PCA0 Cou                                                                                                                                                                 |               |            |           |               |              |                         |            |  |  |  |

| Bit5: | CCF5: PCA                                                                                                                                                                   |               | •          |           |               |              |                         |            |  |  |  |

|       | This bit is set by hardware when a match or capture occurs. When the CCF interrupt is                                                                                       |               |            |           |               |              |                         |            |  |  |  |

|       | enabled, setting this bit causes the CPU to vector to the CCF interrupt service routine. This                                                                               |               |            |           |               |              |                         |            |  |  |  |

|       | bit is not automatically cleared by hardware and must be cleared by software.<br>CCF4: PCA0 Module 4 Capture/Compare Flag.                                                  |               |            |           |               |              |                         |            |  |  |  |

| Bit4: |                                                                                                                                                                             |               | •          |           |               |              |                         |            |  |  |  |

|       | This bit is set by hardware when a match or capture occurs. When the CCF interrupt is                                                                                       |               |            |           |               |              |                         |            |  |  |  |

|       | enabled, setting this bit causes the CPU to vector to the CCF interrupt service routine. This                                                                               |               |            |           |               |              |                         |            |  |  |  |

| Bit3: | bit is not automatically cleared by hardware and must be cleared by software.<br>CCF3: PCA0 Module 3 Capture/Compare Flag.                                                  |               |            |           |               |              |                         |            |  |  |  |

|       | This bit is se                                                                                                                                                              |               | •          |           |               | re Whon th   | o CCE into              | rrunt ie   |  |  |  |

|       | enabled, set                                                                                                                                                                |               |            |           | •             |              |                         |            |  |  |  |

| Bit2: | bit is not aut                                                                                                                                                              |               |            |           |               |              |                         |            |  |  |  |

|       | CCF2: PCA                                                                                                                                                                   | •             | •          |           |               | cleared by   | sonware.                |            |  |  |  |

| 5112. | This bit is se                                                                                                                                                              |               | •          |           |               | rs When th   | e CCE inte              | rrunt is   |  |  |  |

|       |                                                                                                                                                                             |               |            |           |               |              |                         |            |  |  |  |

|       | enabled, setting this bit causes the CPU to vector to the CCF interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software. |               |            |           |               |              |                         |            |  |  |  |

| Bit1: | CCF1: PCA                                                                                                                                                                   |               |            |           |               |              |                         |            |  |  |  |

|       | This bit is se                                                                                                                                                              |               | •          |           |               | rs. When th  | ne CCF inte             | rrupt is   |  |  |  |

|       | enabled, set                                                                                                                                                                |               |            |           |               |              |                         |            |  |  |  |

|       | bit is not aut                                                                                                                                                              |               |            |           |               |              |                         |            |  |  |  |

| Bit0: | CCF0: PCA                                                                                                                                                                   |               |            |           |               | )            |                         |            |  |  |  |

|       | This bit is se                                                                                                                                                              |               |            |           |               | rs. When th  | ne CCF inte             | rrupt in   |  |  |  |

|       |                                                                                                                                                                             |               |            |           |               |              |                         | nupus      |  |  |  |

|       | enabled, set                                                                                                                                                                |               | causes the | CPU to ve | ctor to the C | CCF interrup | ot service ro           |            |  |  |  |

|       | enabled, set<br>bit is not aut                                                                                                                                              | ting this bit |            |           | ctor to the C |              |                         |            |  |  |  |

#### Figure 25.10. PCA0CN: PCA Control Register