Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | 8051                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 25MHz                                                        |

| Connectivity               | CANbus, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT           |

| Number of I/O              | 24                                                           |

| Program Memory Size        | 64KB (64K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 4.25K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 2x16b, 8x10b; D/A 2x12b                                  |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 64-TQFP                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f063r |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | Figure 24.6. CKCON: Clock Control Register                         | 203 |

|-----|--------------------------------------------------------------------|-----|

|     | Figure 24.7. TL0: Timer 0 Low Byte                                 |     |

|     | Figure 24.8. TL1: Timer 1 Low Byte                                 |     |

|     | Figure 24.9. TH0: Timer 0 High Byte                                |     |

|     | Figure 24.10. TH1: Timer 1 High Byte                               |     |

|     | Figure 24.11. T2, 3, and 4 Capture Mode Block Diagram              |     |

|     | Figure 24.12. T2, 3, and 4 Auto-reload Mode Block Diagram          |     |

|     | Figure 24.13. TMRnCN: Timer 2, 3, and 4 Control Registers          |     |

|     | Figure 24.14. TMRnCF: Timer 2, 3, and 4 Configuration Registers    |     |

|     | Figure 24.15. RCAPnL: Timer 2, 3, and 4 Capture Register Low Byte  |     |

|     | Figure 24.16. RCAPnH: Timer 2, 3, and 4 Capture Register High Byte |     |

|     | Figure 24.17. TMRnL: Timer 2, 3, and 4 Low Byte                    |     |

|     | Figure 24.18. TMRnH: Timer 2, 3, and 4 High Byte                   |     |

| 25. | Programmable Counter Array                                         |     |

|     | Figure 25.1. PCA Block Diagram                                     | 303 |

|     | Figure 25.2. PCA Counter/Timer Block Diagram                       | 304 |

|     | Figure 25.3. PCA Interrupt Block Diagram                           |     |

|     | Figure 25.4. PCA Capture Mode Diagram                              |     |

|     | Figure 25.5. PCA Software Timer Mode Diagram                       | 307 |

|     | Figure 25.6. PCA High Speed Output Mode Diagram                    |     |

|     | Figure 25.7. PCA Frequency Output Mode                             |     |

|     | Figure 25.8. PCA 8-Bit PWM Mode Diagram                            |     |

|     | Figure 25.9. PCA 16-Bit PWM Mode                                   |     |

|     | Figure 25.10. PCA0CN: PCA Control Register                         |     |

|     | Figure 25.11. PCA0MD: PCA0 Mode Register                           |     |

|     | Figure 25.12. PCA0CPMn: PCA0 Capture/Compare Mode Registers        |     |

|     | Figure 25.13. PCA0L: PCA0 Counter/Timer Low Byte                   |     |

|     | Figure 25.14. PCA0H: PCA0 Counter/Timer High Byte                  |     |

|     | Figure 25.15. PCA0CPLn: PCA0 Capture Module Low Byte               |     |

|     | Figure 25.16. PCA0CPHn: PCA0 Capture Module High Byte              |     |

|     | JTAG (IEEE 1149.1)                                                 |     |

|     |                                                                    | 317 |

|     | Figure 26.2. DEVICEID: JTAG Device ID Register                     |     |

|     | Figure 26.3. FLASHCON: JTAG Flash Control Register                 |     |

|     | Figure 26.4. FLASHDAT: JTAG Flash Data Register                    |     |

| 77  | Figure 26.5. FLASHADR: JTAG Flash Address Register                 |     |

| 21. | Document Change List                                               | 3Z1 |

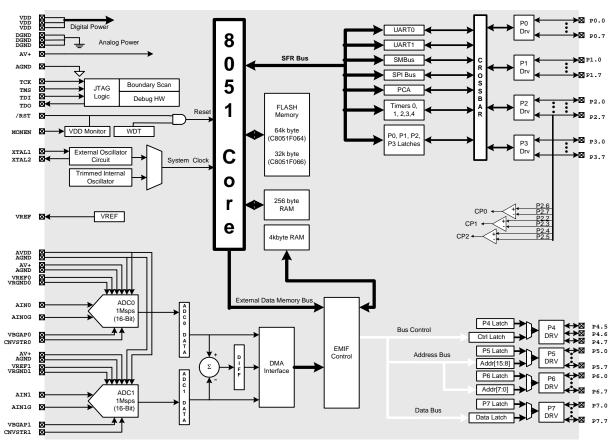

Figure 1.3. C8051F064 / C8051F066 Block Diagram

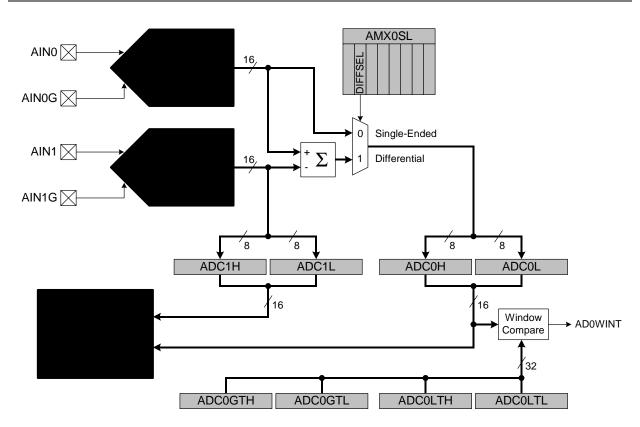

Figure 5.2. 16-bit ADC0 and ADC1 Data Path Diagram

### 5.1. Single-Ended or Differential Operation

ADC0 and ADC1 can be programmed to operate independently as single-ended ADCs, or together to accept a differential input. In single-ended mode, the ADCs can be configured to sample simultaneously, or to use different conversion speeds. In differential mode, ADC1 is a slave to ADC0, and its configuration is based on ADC0 settings, except during offset or gain calibrations. The DIFFSEL bit in the Channel Select Register AMX0SL (Figure 5.6) selects between single-ended and differential mode.

#### 5.1.1. Pseudo-Differential Inputs

The inputs to the ADCs are pseudo-differential. The actual voltage measured by each ADC is equal to the voltage between the AINn pin and the AINnG pin. AINnG must be a DC signal between -0.2 and 0.6 V. In most systems, AINnG will be connected to AGND. If not tied to AGND, the AINnG signal can be used to negate a limited amount of fixed offset, but it is recommended that the internal offset calibration features of the device be used for this purpose. When operating in differential mode, AIN0G and AIN1G should be tied together. AINn must remain above AINnG in both modes for accurate conversion results.

### 5.3. ADC Modes of Operation

ADC0 and ADC1 have a maximum conversion speed of 1 Msps. The conversion clocks for the ADCs are derived from the system clock. The ADCnSC bits in the ADCnCF register determine how many system clocks (from 1 to 16) are used for each conversion clock.

#### 5.3.1. Starting a Conversion

For ADC0, conversions can be initiated in one of four ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM1, AD0CM0) in ADC0CN. For ADC0, conversions may be initiated by:

- 1. Writing a '1' to the AD0BUSY bit of ADC0CN;

- 2. A Timer 3 overflow (i.e. timed continuous conversions);

- 3. A rising edge detected on the external ADC convert start signal, CNVSTR0;

- 4. A Timer 2 overflow (i.e. timed continuous conversions).

ADC1 conversions can be initiated in five different ways, according to the ADC1 Start of Conversion Mode bits (AD1CM2-AD1CM0) in ADC1CN. For ADC1, conversions may be initiated by:

- 1. Writing a '1' to the AD1BUSY bit of ADC1CN;

- 2. A Timer 3 overflow (i.e. timed continuous conversions);

- 3. A rising edge detected on the external ADC convert start signal, CNVSTR1;

- 4. A Timer 2 overflow (i.e. timed continuous conversions);

- 5. Writing a '1' to the AD0BUSY bit of ADC0CN.

The ADnBUSY bit is set to logic 1 during conversion and restored to logic 0 when conversion is complete. The falling edge of ADnBUSY triggers an interrupt (when enabled) and sets the ADnINT interrupt flag (ADCnCN.5). In single-ended mode, the converted data for ADCn is available in the ADCn data word MSB and LSB registers, ADCnH, ADCnL. In differential mode, the converted data (combined from ADC0 and ADC1) is available in the ADC0 data word MSB and LSB registers, ADC0H, ADC0L.

When initiating conversions by writing a '1' to ADnBUSY, the ADnINT bit should be polled to determine when a conversion has completed (ADCn interrupts may also be used). The recommended polling procedure is shown below.

Step 1. Write a '0' to ADnINT; Step 2. Write a '1' to ADnBUSY; Step 3. Poll ADnINT for '1';

Step 4. Process ADCn data.

When an external start-of-conversion source is required in differential mode the two pins (CNVSTR0 and CNVSTR1) should be tied together.

#### 5.3.2. Tracking Modes

The ADnTM bit in register ADCnCN controls the ADCn track-and-hold mode. When the ADC is enabled, the ADC input is continuously tracked when a conversion is not in progress. When the ADnTM bit is logic 1, each conversion is preceded by a tracking period (after the start-of-conversion signal). When the CNVSTRn signal is used to initiate conversions, the ADC will track until a rising edge occurs on the CNVSTRn pin (see Figure 5.4 and Table 5.1 for conversion timing parameters). Setting ADnTM to 1 can be useful to ensure that settling time requirements are met when an external multiplexer is used on the analog input (see Section "5.3.3. Settling Time Requirements" on page 56).

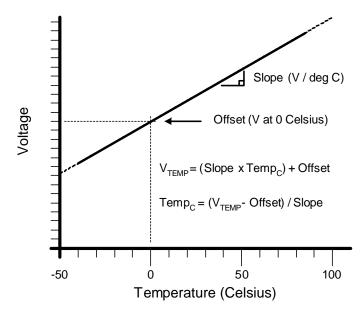

Figure 7.2. Temperature Sensor Transfer Function

#### 7.2. Modes of Operation

ADC2 has a maximum conversion speed of 200 ksps. The ADC2 conversion clock is a divided version of the system clock, determined by the AD2SC bits in the ADC2CF register (system clock divided by (AD2SC + 1) for  $0 \le AD2SC \le 31$ ). The ADC2 conversion clock should be no more than 3 MHz.

#### 7.2.1. Starting a Conversion

A conversion can be initiated in one of four ways, depending on the programmed states of the ADC2 Start of Conversion Mode bits (AD2CM1-0) in register ADC2CN. Conversions may be initiated by one of the following:

- 1. Writing a '1' to the AD2BUSY bit of register ADC2CN

- 2. A Timer 3 overflow (i.e. timed continuous conversions)

- 3. A rising edge on the CNVSTR2 input signal (Assigned by the crossbar)

- 4. A Timer 2 overflow

When CNVSTR2 is used as a conversion start source, it must be enabled in the crossbar, and the corresponding pin must be set to open-drain, high-impedance mode (see Section "18. Port Input/Output" on page 203 for more details on Port I/O configuration).

Writing a '1' to AD2BUSY provides software control of ADC2 whereby conversions are performed "ondemand". During conversion, the AD2BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD2BUSY triggers an interrupt (when enabled) and sets the ADC2 interrupt flag (AD2INT). Note: When polling for ADC conversion completions, the ADC2 interrupt flag (AD2INT) should be used. Converted data is available in the ADC2 data registers, ADC2H and ADC2L, when bit AD2INT is logic 1. Note that when Timer 2 or Timer 3 overflows are used as the conversion source, low byte overflows are used if the timer is in 8-bit mode; and high byte overflows are used if the timer is in 16bit mode. See Section "24. Timers" on page 287 for timer configuration.

| SFR Page:<br>SFR Address:                                                                                                                                                                                                                                                                                     | 2<br>0xBC |            |              |            |      |      |      |             |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|--------------|------------|------|------|------|-------------|--|

| R/W                                                                                                                                                                                                                                                                                                           | R/W       | R/W        | R/W          | R/W        | R/W  | R/W  | R/W  | Reset Value |  |

| AD2SC4                                                                                                                                                                                                                                                                                                        | AD2SC3    | AD2SC2     | AD2SC1       | AD2SC0     | -    | -    | -    | 11111000    |  |

| Bit7                                                                                                                                                                                                                                                                                                          | Bit6      | Bit5       | Bit4         | Bit3       | Bit2 | Bit1 | Bit0 |             |  |

| Bits7-3: AD2SC4-0: ADC2 SAR Conversion Clock Period Bits.<br>SAR Conversion clock is derived from system clock by the following equation, where ADSC refers to the 5-bit value held in bits AD2SC4-AD2SC0. SAR Conversion clock requirements are given in Table 7.1.<br>$ADSC = \frac{SYSCLK}{CLK_{SAR}} - 1$ |           |            |              |            |      |      |      |             |  |

| Bits2-0:                                                                                                                                                                                                                                                                                                      | UNUSED. R | ead = 000b | ; Write = do | on't care. |      |      |      |             |  |

|                                                                                                                                                                                                                                                                                                               |           |            |              |            |      |      |      |             |  |

### Figure 7.7. ADC2CF: ADC2 Configuration Register

102

## 11. Voltage Reference 2 (C8051F064/5/6/7)

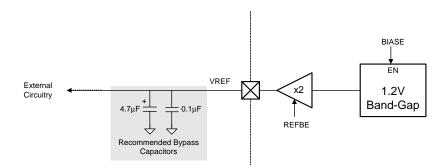

The internal voltage reference circuit consists of a 1.2 V, temperature stable bandgap voltage reference generator and a gain-of-two output buffer amplifier. The internal reference may be routed to the VREF pin as shown in Figure 11.1. The maximum load seen by the VREF pin must be less than 200  $\mu$ A to AGND. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to AGND, as shown in Figure 11.1.

The Reference Control Register 2, REF2CN (defined in Figure 11.2) enables/disables the internal reference generator. The BIASE bit in REF2CN enables the on-board reference generator while the REFBE bit enables the gain-of-two buffer amplifier which drives the VREF pin. When disabled, the supply current drawn by the bandgap and buffer amplifier falls to less than 1  $\mu$ A (typical) and the output of the buffer amplifier enters a high impedance state. If the internal bandgap is used as the reference voltage generator, BIASE and REFBE must both be set to logic 1. If the internal reference is not used, REFBE may be set to logic 0. The electrical specifications for the Voltage Reference are given in Table 11.1.

#### Figure 11.1. Voltage Reference Functional Block Diagram

| R/W       | R/W                                                                                                        | R/W             | R/W           | R/W           | R/W           | R/W           | R/W           | Reset Value        |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------|-----------------|---------------|---------------|---------------|---------------|---------------|--------------------|--|--|--|

| CPnEN     | CPnOUT                                                                                                     | CPnRIF          | CPnFIF        | CPnHYP1       | CPnHYP0       | CPnHYN1       | CPnHYN0       | 00000000           |  |  |  |

| Bit7      | Bit6                                                                                                       | Bit5            | Bit4          | Bit3          | Bit2          | Bit1          | Bit0          | Bit<br>Addressable |  |  |  |

| SFR Addre | SFR Address: CPT0CN: 0x88; CPT1CN: 0x88; CPT2CN: 0x88                                                      |                 |               |               |               |               |               |                    |  |  |  |

| SFR Pag   | SFR Pages: CPT0CN: page 1; CPT1CN: page 2; CPT2CN: page 3                                                  |                 |               |               |               |               |               |                    |  |  |  |

|           |                                                                                                            | _               |               | _             |               |               |               |                    |  |  |  |

| Bit7:     | CPnEN: Com                                                                                                 | •               | •             | lease see r   | ote below.    | .)            |               |                    |  |  |  |

|           | 0: Comparato                                                                                               |                 |               |               |               |               |               |                    |  |  |  |

| D'10      | 1: Comparate                                                                                               |                 |               |               |               |               |               |                    |  |  |  |

| Bit6:     | CPnOUT: Co<br>0: Voltage on                                                                                |                 | •             | e Flag.       |               |               |               |                    |  |  |  |

|           | 1: Voltage on                                                                                              |                 |               |               |               |               |               |                    |  |  |  |

| Bit5:     | CPnRIF: Cor                                                                                                |                 |               | Interrunt Fla | a             |               |               |                    |  |  |  |

| Dito.     | 0: No Compa                                                                                                | •               |               | •             | •             | e this flag v | vas last clea | ared               |  |  |  |

|           | 1: Comparate                                                                                               |                 |               |               |               |               |               |                    |  |  |  |

| Bit4:     | CPnFIF: Con                                                                                                |                 |               |               |               |               | ,             |                    |  |  |  |

|           | 0: No Compa                                                                                                |                 |               |               |               | ce this flag  | was last clea | ared.              |  |  |  |

|           | 1: Comparato                                                                                               |                 |               |               |               |               |               |                    |  |  |  |

| Bits3-2:  | CPnHYP1-0:                                                                                                 | Comparato       | or Positive I | Hysteresis (  | Control Bits. |               | -             |                    |  |  |  |

|           | 00: Positive H                                                                                             | Hysteresis I    | Disabled.     |               |               |               |               |                    |  |  |  |

|           | 01: Positive H                                                                                             |                 |               |               |               |               |               |                    |  |  |  |

|           | 10: Positive H                                                                                             |                 |               |               |               |               |               |                    |  |  |  |

|           | 11: Positive H                                                                                             |                 |               |               |               |               |               |                    |  |  |  |

| Bits1-0:  | CPnHYN1-0:                                                                                                 | •               | •             | Hysteresis    | Control Bits  | 6.            |               |                    |  |  |  |

|           | 00: Negative                                                                                               |                 |               |               |               |               |               |                    |  |  |  |

|           | 01: Negative Hysteresis = 5 mV.                                                                            |                 |               |               |               |               |               |                    |  |  |  |

|           | 10: Negative                                                                                               |                 |               |               |               |               |               |                    |  |  |  |

| NOTE.     | 11: Negative                                                                                               |                 |               |               |               |               |               | d Defere           |  |  |  |

| NOTE:     | Upon enablin                                                                                               | •               |               | •             |               |               |               |                    |  |  |  |

|           | using a comp                                                                                               |                 |               |               |               |               |               |                    |  |  |  |

|           | the specified "Power-up time" as specified in Table 12.1, "Comparator Electrical Chara tics," on page 122. |                 |               |               |               |               |               |                    |  |  |  |

|           | abs, on page                                                                                               | , 1 <u>22</u> . |               |               |               |               |               |                    |  |  |  |

|           |                                                                                                            |                 |               |               |               |               |               |                    |  |  |  |

#### Figure 12.3. CPTnCN: Comparator 0, 1, and 2 Control Register

#### Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 64K-byte program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

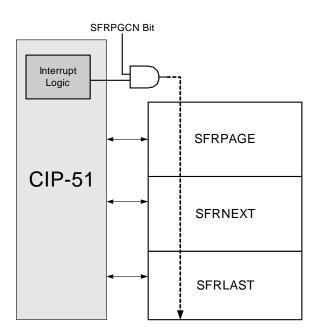

Figure 13.3. SFR Page Stack

Automatic hardware switching of the SFR Page on interrupts may be enabled or disabled as desired using the SFR Automatic Page Control Enable Bit located in the SFR Page Control Register (SFRPGCN). This function defaults to 'enabled' upon reset. In this way, the autoswitching function will be enabled unless disabled in software.

A summary of the SFR locations (address and SFR page) is provided in Table 13.2. in the form of an SFR memory map. Each memory location in the map has an SFR page row, denoting the page in which that SFR resides. Note that certain SFRs are accessible from ALL SFR pages, and are denoted by the "(ALL PAGES)" designation. For example, the Port I/O registers P0, P1, P2, and P3 all have the "(ALL PAGES)" designation, indicating these SFRs are accessible from all SFR pages regardless of the SFRPAGE register value.

| A D D R E S S | SFR<br>P<br>A<br>G<br>E | 0(8)                               | 1(9)                          | 2(A)                           | 3(B)                           | 4(C)                       | 5(D)                    | 6(E)                       | 7(F)                    |

|---------------|-------------------------|------------------------------------|-------------------------------|--------------------------------|--------------------------------|----------------------------|-------------------------|----------------------------|-------------------------|

| F8            | 0<br>1<br>2<br>3<br>F   | SPIOCN<br>CANOCN<br>DMA0CF<br>P7   | PCA0L<br>DMA0CTL              | PCA0H<br>DMA0CTH               | PCA0CPL0<br>DMA0CSL            | PCA0CPH0<br>DMA0CSH        | PCA0CPL1<br>DMA0BND     | PCA0CPH1<br>DMA0ISW        | WDTCN<br>(ALL PAGES)    |

| F0            | 0<br>1<br>2<br>3<br>F   | B<br>(ALL PAGES)                   |                               |                                |                                |                            |                         | EIP1<br><b>(ALL PAGES)</b> | EIP2<br>(ALL PAGES)     |

| E8            | 0<br>1<br>2<br>3<br>F   | ADC0CN<br>ADC1CN<br>ADC2CN<br>P6   | PCA0CPL2                      | PCA0CPH2                       | PCA0CPL3                       | PCA0CPH3                   | PCA0CPL4                | PCA0CPH4                   | RSTSRC                  |

| E0            | 0<br>1<br>2<br>3<br>F   | ACC<br>(ALL PAGES)                 | PCA0CPL5<br>XBR0              | PCA0CPH5<br>XBR1               | XBR2                           | XBR3                       |                         | EIE1<br>(ALL PAGES)        | EIE2<br>(ALL PAGES)     |

| D8            | 0<br>1<br>2<br>3<br>F   | PCA0CN<br>CAN0DATL<br>DMA0CN<br>P5 | PCA0MD<br>CAN0DATH<br>DMA0DAL | PCA0CPM0<br>CAN0ADR<br>DMA0DAH | PCA0CPM1<br>CAN0TST<br>DMA0DSL | PCA0CPM2<br>DMA0DSH        | PCA0CPM3<br>DMA0IPT     | PCA0CPM4<br>DMA0IDT        | PCA0CPM5                |

| D0            | 0<br>1<br>2<br>3<br>F   | PSW<br>(ALL PAGES)                 | REF0CN<br>REF1CN<br>REF2CN    | DAC0L<br>DAC1L                 | DAC0H<br>DAC1H                 | DAC0CN<br>DAC1CN           |                         |                            |                         |

| C8            | 0<br>1<br>2<br>3<br>F   | TMR2CN<br>TMR3CN<br>TMR4CN<br>P4   | TMR2CF<br>TMR3CF<br>TMR4CF    | RCAP2L<br>RCAP3L<br>RCAP4L     | RCAP2H<br>RCAP3H<br>RCAP4H     | TMR2L<br>TMR3L<br>TMR4L    | TMR2H<br>TMR3H<br>TMR4H |                            | SMB0CR                  |

| C0            | 0<br>1<br>2<br>3<br>F   | SMB0CN<br>CAN0STA                  | SMB0STA                       | SMB0DAT                        | SMB0ADR                        | ADC0GTL<br>ADC2GTL         | ADC0GTH<br>ADC2GTH      | ADC0LTL<br>ADC2LTL         | ADC0LTH<br>ADC2LTH      |

| B8            | 0<br>1<br>2<br>3<br>F   | IP<br>(ALL PAGES)                  | SADEN0                        | AMX2CF<br>ADC0CPT              | AMX0SL<br>AMX2SL<br>ADC0CCF    | ADC0CF<br>ADC1CF<br>ADC2CF |                         | ADC0L<br>ADC1L<br>ADC2L    | ADC0H<br>ADC1H<br>ADC2H |

|               |                         | 0(8)                               | 1(9)                          | 2(A)                           | 3(B)                           | 4(C)                       | 5(D)                    | 6(E)                       | 7(F)                    |

Table 13.2. Special Function Register (SFR) Memory Map

Rev. 1.2

| R                                | R                                                                                                                                          | R          | R/W                         | R/W          | R/W         | R/W   | R/W  | Reset Value |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------|--------------|-------------|-------|------|-------------|--|--|--|

| CTXOU                            | Г -                                                                                                                                        | -          |                             | CP2E         | CNVST2E     | T3EXE | T3E  | 00000000    |  |  |  |

| Bit7                             | Bit6                                                                                                                                       | Bit5       | Bit4                        | Bit3         | Bit2        | Bit1  | Bit0 | 1           |  |  |  |

| SFR Address: 0xE4<br>SFR Page: F |                                                                                                                                            |            |                             |              |             |       |      |             |  |  |  |

| Bit7:                            | CTXOUT: CA<br>0: CTX pin o<br>1: CTX pin o                                                                                                 | utput mode | is configur                 | ed as open   | -drain.     |       |      |             |  |  |  |

| Bit6-4:                          | Reserved                                                                                                                                   | •          | 0                           | •            | •           |       |      |             |  |  |  |

| Bit3:                            | CP2E: CP2 Output Enable Bit.<br>0: CP2 unavailable at Port pin.<br>1: CP2 routed to Port pin.                                              |            |                             |              |             |       |      |             |  |  |  |

| Bit2:                            | CNVST2E: A<br>0: CNVST2 f                                                                                                                  | DC2 Exter  | nal Convert<br>navailable a | at Port pin. | Enable Bit. |       |      |             |  |  |  |

| Bit1:                            | 1: CNVST2 for ADC2 routed to Port pin.<br>T3EXE: T3EX Input Enable Bit.<br>0: T3EX unavailable at Port pin.<br>1: T3EX routed to Port pin. |            |                             |              |             |       |      |             |  |  |  |

| Bit0:                            | T3E: T3 Input Enable Bit.<br>0: T3 unavailable at Port pin.<br>1: T3 routed to Port pin.                                                   |            |                             |              |             |       |      |             |  |  |  |

|                                  |                                                                                                                                            |            |                             |              |             |       |      |             |  |  |  |

### Figure 18.8. XBR3: Port I/O Crossbar Register 3

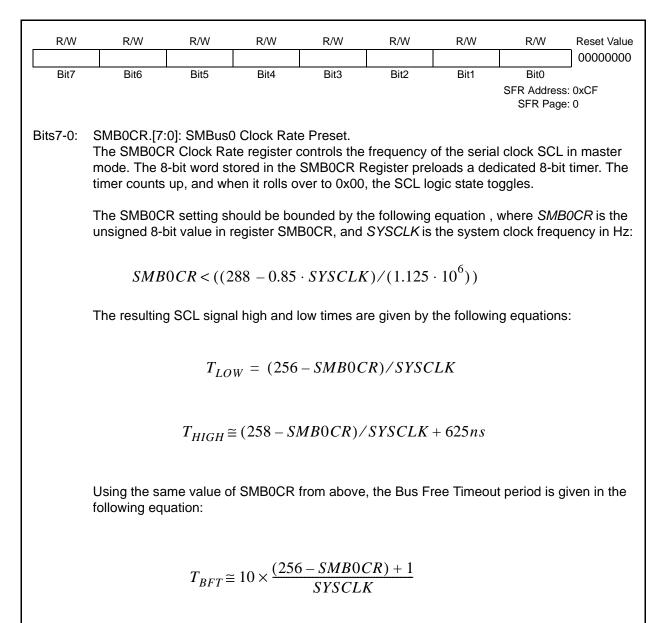

### 20.4.2. Clock Rate Register

Figure 20.9. SMB0CR: SMBus0 Clock Rate Register

### 23.2. Operational Modes

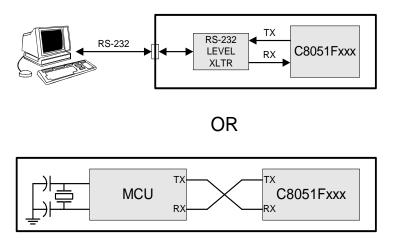

UART1 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S1MODE bit (SCON1.7). Typical UART connection options are shown below.

Figure 23.3. UART Interconnect Diagram

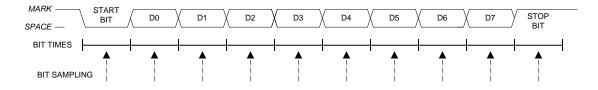

#### 23.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX1 pin and received at the RX1 pin. On receive, the eight data bits are stored in SBUF1 and the stop bit goes into RB81 (SCON1.2).

Data transmission begins when software writes a data byte to the SBUF1 register. The TI1 Transmit Interrupt Flag (SCON1.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN1 Receive Enable bit (SCON1.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF1 receive register if the following conditions are met: RI1 must be logic 0, and if MCE1 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF1 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF1, the stop bit is stored in RB81 and the RI1 flag is set. If these conditions are not met, SBUF1 and RB81 will not be loaded and the RI1 flag will not be set. An interrupt will occur if enabled when either TI1 or RI1 is set.

| R/W               | R/W                                                                                                                                                                                                                                                                                                                                          | R/W                           | R/W                          | R/W             | R/W         | R/W          | R/W          | Reset Value |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------|-----------------|-------------|--------------|--------------|-------------|--|--|--|--|

| -                 | -                                                                                                                                                                                                                                                                                                                                            | -                             | T1M                          | TOM             | -           | SCA1         | SCA0         | 00000000    |  |  |  |  |

| Bit7              | Bit6                                                                                                                                                                                                                                                                                                                                         | Bit5                          | Bit4                         | Bit3            | Bit2        | Bit1         | Bit0         |             |  |  |  |  |

|                   | SFR Address: 0x8E<br>SFR Page: 0                                                                                                                                                                                                                                                                                                             |                               |                              |                 |             |              |              |             |  |  |  |  |

| Bits7-5:<br>Bit4: | UNUSED. Read = 000b, Write = don't care.<br>T1M: Timer 1 Clock Select.<br>This select the clock source supplied to Timer 1. T1M is ignored when C/T1 is set to logic 1.<br>0: Timer 1 uses the clock defined by the prescale bits, SCA1-SCA0.                                                                                                |                               |                              |                 |             |              |              |             |  |  |  |  |

| Bit3:             | <ol> <li>1: Timer 1 uses the system clock.</li> <li>T0M: Timer 0 Clock Select.</li> <li>This bit selects the clock source supplied to Timer 0. T0M is ignored when C/T0 is set to logic 1.</li> <li>0: Counter/Timer 0 uses the clock defined by the prescale bits, SCA1-SCA0.</li> <li>1: Counter/Timer 0 uses the system clock.</li> </ol> |                               |                              |                 |             |              |              |             |  |  |  |  |

| Bit2:<br>Bits1-0: | UNUSED.<br>SCA1-SCA                                                                                                                                                                                                                                                                                                                          | Read = 0b,<br>\0: Timer 0/1   | Write = don'<br>I Prescale B | t care.<br>Bits |             |              | <b>T</b>     |             |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                              | control the o<br>scaled clock |                              | ie clock sup    | Died to Tin | her 0 and/or | limer 1 if ( | configured  |  |  |  |  |

|                   | SCA1                                                                                                                                                                                                                                                                                                                                         | SCA0                          | Presc                        | aled Clock      |             |              |              |             |  |  |  |  |

|                   | 0                                                                                                                                                                                                                                                                                                                                            | 0                             | System clo                   | ck divided b    | y 12        |              |              |             |  |  |  |  |

|                   | 0 1 System clock divided by 4                                                                                                                                                                                                                                                                                                                |                               |                              |                 |             |              |              |             |  |  |  |  |

|                   | 1                                                                                                                                                                                                                                                                                                                                            | 0                             | System clo                   | ck divided b    | y 48        |              |              |             |  |  |  |  |

|                   | 1                                                                                                                                                                                                                                                                                                                                            | 1                             | External clo                 | ock divided     | oy 8†       |              |              |             |  |  |  |  |

| †Note:            |                                                                                                                                                                                                                                                                                                                                              |                               |                              |                 |             |              |              |             |  |  |  |  |

### Figure 24.6. CKCON: Clock Control Register

### 24.2. Timer 2, Timer 3, and Timer 4

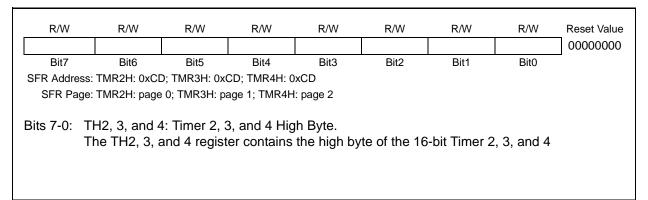

Timers 2, 3, and 4 are 16-bit counter/timers, each formed by two 8-bit SFRs: TMRnL (low byte) and TMRnH (high byte) where n = 2, 3, and 4 for timers 2, 3, and 4 respectively. These timers feature autoreload, capture, and toggle output modes with the ability to count up or down. Capture Mode and Autoreload mode are selected using bits in the Timer 2, 3, and 4 Control registers (TMRnCN). Toggle output mode is selected using the Timer 2, 3, and 4 Configuration registers (TMRnCF). These timers may also be used to generate a square-wave at an external pin. Timers 2, 3, and 4 can use either the system clock (divided by one, two, or twelve), external clock (divided by eight) or transitions on an external input pin as its clock source. Timer 2 and 3 can be used to start an ADC Data Conversion and Timers 2, 3, and 4 can schedule DAC outputs. Timers 1, 2, 3, or 4 may be used to generate baud rates for UART 0. Only Timer 1 can be used to generate baud rates for UART 1.

The Counter/Timer Select bit C/Tn bit (TMRnCN.1) configures the peripheral as a counter or timer. Clearing C/Tn configures the Timer to be in a timer mode (i.e., the selected timer clock source as the input for the timer). When C/Tn is set to 1, the timer is configured as a counter (i.e., high-to-low transitions at the Tn input pin increment (or decrement) the counter/timer register. Refer to Section "18.1. Ports 0 through 3 and the Priority Crossbar Decoder" on page 205 for information on selecting and configuring external I/O pins for digital peripherals, such as the Tn pin.

Timer 2, 3, and 4 can use either SYSCLK, SYSCLK divided by 2, SYSCLK divided by 12, an external clock divided by 8, or high-to-low transitions on the Tn input pin as its clock source when operating in Counter/ Timer with Capture mode. Clearing the C/Tn bit (TnCON.1) selects the system clock/external clock as the input for the timer. The Timer Clock Select bits TnM0 and TnM1 in TMRnCF can be used to select the system clock undivided, system clock divided by two, system clock divided by 12, or an external clock provided at the XTAL1/XTAL2 pins divided by 8 (see Figure 24.14). When C/Tn is set to logic 1, a high-to-low transition at the Tn input pin increments the counter/timer register (i.e., configured as a counter).

#### 24.2.1. Configuring Timer 2, 3, and 4 to Count Down

Timers 2, 3, and 4 have the ability to count down. When the timer's respective Decrement Enable Bit (DCENn) in the Timer Configuration Register (See Figure 24.14) is set to '1', the timer can then count *up* or *down*. When DCENn = 1, the direction of the timer's count is controlled by the TnEX pin's logic level. When TnEX = 1, the counter/timer will count up; when TnEX = 0, the counter/timer will count down. To use this feature, TnEX must be enabled in the digital crossbar and configured as a digital input.

Note: When DCENn = 1, other functions of the TnEX input (i.e., capture and auto-reload) are not available. TnEX will only control the direction of the timer when DCENn = 1.

#### Figure 24.18. TMRnH: Timer 2, 3, and 4 High Byte

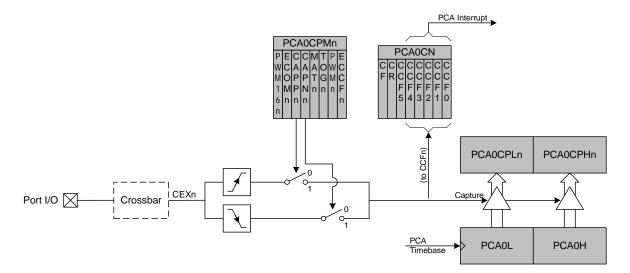

#### 25.2.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes PCA0 to capture the value of the PCA0 counter/ timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software.

#### Figure 25.4. PCA Capture Mode Diagram

Note: The signal at CEXn must be high or low for at least 2 system clock cycles in order to be valid.