# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                           |

| Number of I/O              | 59                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 2x16b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 100-TQFP                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f066-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F060/1/2/3/4/5/6/7

|           | MIPS (Peak) | Flash Memory | RAM  | External Memory Interface | SMBus/I2C and SPI | CAN          | UARTS | Timers (16-bit) | Programmable Counter Array | Digital Port I/O's | 16-bit 1 Msps ADC Typical INL (LSBs) | 10-bit 200 ksps ADC Inputs | Voltage Reference | Temperature Sensor | DAC Resolution (bits) | DAC Outputs | Analog Comparators | Package  |

|-----------|-------------|--------------|------|---------------------------|-------------------|--------------|-------|-----------------|----------------------------|--------------------|--------------------------------------|----------------------------|-------------------|--------------------|-----------------------|-------------|--------------------|----------|

| C8051F060 | 25          | 64 k         | 4352 | ~                         | V                 | V            | 2     | 5               | $\checkmark$               | 59                 | ±0.75                                | 8                          | $\checkmark$      | $\checkmark$       | 12                    | 2           | 3                  | 100 TQFP |

| C8051F061 | 25          | 64 k         | 4352 | -                         | $\checkmark$      | $\checkmark$ | 2     | 5               | $\checkmark$               | 24                 | ±0.75                                | 8                          | $\checkmark$      | $\checkmark$       | 12                    | 2           | 3                  | 64 TQFP  |

| C8051F062 | 25          | 64 k         | 4352 | $\checkmark$              | $\checkmark$      | $\checkmark$ | 2     | 5               | $\checkmark$               | 59                 | ±1.5                                 | 8                          | $\checkmark$      | $\checkmark$       | 12                    | 2           | 3                  | 100 TQFP |

| C8051F063 | 25          | 64 k         | 4352 | -                         | $\checkmark$      | $\checkmark$ | 2     | 5               | $\checkmark$               | 24                 | ±1.5                                 | 8                          | $\checkmark$      | $\checkmark$       | 12                    | 2           | 3                  | 64 TQFP  |

| C8051F064 | 25          | 64 k         | 4352 | $\checkmark$              | $\checkmark$      | -            | 2     | 5               | $\checkmark$               | 59                 | ±0.75                                | -                          | $\checkmark$      | -                  | -                     | -           | 3                  | 100 TQFP |

| C8051F065 | 25          | 64 k         | 4352 | -                         | $\checkmark$      | -            | 2     | 5               | $\checkmark$               | 24                 | ±0.75                                | -                          | $\checkmark$      | -                  | -                     | -           | 3                  | 64 TQFP  |

| C8051F066 | 25          | 32 k         | 4352 | $\checkmark$              | $\checkmark$      | -            | 2     | 5               | $\checkmark$               | 59                 | ±0.75                                | -                          | $\checkmark$      | -                  | -                     | -           | 3                  | 100 TQFP |

| C8051F067 | 25          | 32 k         | 4352 | -                         | ~                 | -            | 2     | 5               | $\checkmark$               | 24                 | ±0.75                                | -                          | $\checkmark$      | -                  | -                     | -           | 3                  | 64 TQFP  |

Table 1.1. Product Selection Guide

Т

\_

------

-

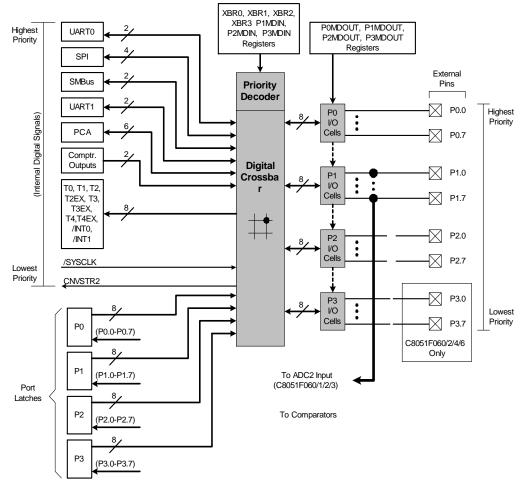

#### 1.4. Programmable Digital I/O and Crossbar

Three standard 8051 Ports (0, 1, and 2) are available on the MCUs. The C8051F060/2/4/6 have 4 additional 8-bit ports (3, 5, 6, and 7), and a 3-bit port (port 4) for a total of 59 general-purpose I/O Pins. The Ports behave like the standard 8051 with a few enhancements.

Each port pin can be configured as either a push-pull or open-drain output. Also, the "weak pull-ups" which are normally fixed on an 8051 can be globally disabled, providing additional power saving capabilities for low-power applications.

Perhaps the most unique enhancement is the Digital Crossbar. This is a large digital switching network that allows mapping of internal digital system resources to Port I/O pins on P0, P1, P2, and P3. (See Figure 1.9) Unlike microcontrollers with standard multiplexed digital I/O ports, all combinations of functions are supported with all package options offered.

The on-chip counter/timers, serial buses, HW interrupts, comparator outputs, and other digital signals in the controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This allows the user to select the exact mix of general purpose Port I/O and digital resources needed for the particular application.

#### 1.7. Serial Ports

The C8051F06x MCU Family includes two Enhanced Full-Duplex UARTs, an enhanced SPI Bus, and SMBus/I2C. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little intervention by the CPU. The serial buses do not "share" resources such as timers, interrupts, or Port I/O, so any or all of the serial buses may be used together with any other.

|                  |      | Pin Nu | mbers                     |                        |       |                                                                   |  |  |  |

|------------------|------|--------|---------------------------|------------------------|-------|-------------------------------------------------------------------|--|--|--|

| Name             | F060 | F061   | F064                      | F065                   | Туре  | Description                                                       |  |  |  |

|                  | F062 | F063   | F066                      | F067                   |       |                                                                   |  |  |  |

| P7.2/AD2m/<br>D2 | 70   |        | 70                        |                        | D I/O | Port 7.2. See Port Input/Output section for complete description. |  |  |  |

| P7.3/AD3m/<br>D3 | 69   |        | 69                        |                        | D I/O | Port 7.3. See Port Input/Output section for complete description. |  |  |  |

| P7.4/AD4m/<br>D4 | 68   |        | 68                        |                        | D I/O | Port 7.4. See Port Input/Output section for complete description. |  |  |  |

| P7.5/AD5m/<br>D5 | 67   |        | 67                        |                        | D I/O | Port 7.5. See Port Input/Output section for complete description. |  |  |  |

| P7.6/AD6m/<br>D6 | 66   |        | 66                        |                        | D I/O | Port 7.6. See Port Input/Output section for complete description. |  |  |  |

| P7.7/AD7m/<br>D7 | 65   |        | 65                        |                        | D I/O | Port 7.7. See Port Input/Output section for complete description. |  |  |  |

| NC               |      |        | 1, 2, 3,<br>25, 94,<br>95 | 17,59,<br>60,62,<br>64 |       | No Connection.                                                    |  |  |  |

Table 4.1. Pin Definitions (Continued)

# C8051F060/1/2/3/4/5/6/7

|                                                                                                   |                                                     | ingle-Ended Mode    |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------|

| (AMX0SL = 0x00)<br>AIN0-AIN0G (Volts)                                                             | ADC0H:ADC0L                                         | <b>—</b>            |

| VREF * (65535/65536)                                                                              | 0xFFFF                                              | <b></b>             |

| VREF / 2                                                                                          | 0x8000                                              |                     |

| VREF * (32767/65536)                                                                              | 0x7FFF                                              |                     |

| 0                                                                                                 | 0x0000                                              |                     |

| Example: ADC0 Data Word Con<br>(AMX0SL = 0x40)<br>AIN0-AIN1 (Volts)                               | version Map, AIN0-AIN1 Diffe                        | erential Input Pair |

| (AMX0SL = 0x40)<br>AIN0-AIN1 (Volts)                                                              | ADC0H:ADC0L                                         | erential Input Pair |

| (AMX0SL = 0x40)<br>AIN0-AIN1 (Volts)<br>VREF * (32767/32768)                                      | ADC0H:ADC0L<br>0x7FFF                               | erential Input Pair |

| (AMX0SL = 0x40)<br>AIN0-AIN1 (Volts)<br>VREF * (32767/32768)<br>VREF / 2                          | ADC0H:ADC0L                                         | erential Input Pair |

| (AMX0SL = 0x40)<br>AIN0-AIN1 (Volts)<br>VREF * (32767/32768)                                      | ADC0H:ADC0L<br>0x7FFF<br>0x4000                     | erential Input Pair |

| (AMX0SL = 0x40)<br>AIN0-AIN1 (Volts)<br>VREF * (32767/32768)<br>VREF / 2<br>VREF * (1/32768)      | ADC0H:ADC0L<br>0x7FFF<br>0x4000<br>0x0001           | erential Input Pair |

| (AMX0SL = 0x40)<br>AIN0-AIN1 (Volts)<br>VREF * (32767/32768)<br>VREF / 2<br>VREF * (1/32768)<br>0 | ADC0H:ADC0L<br>0x7FFF<br>0x4000<br>0x0001<br>0x0000 | erential Input Pair |

#### Figure 5.15. ADC0 Data Word Example

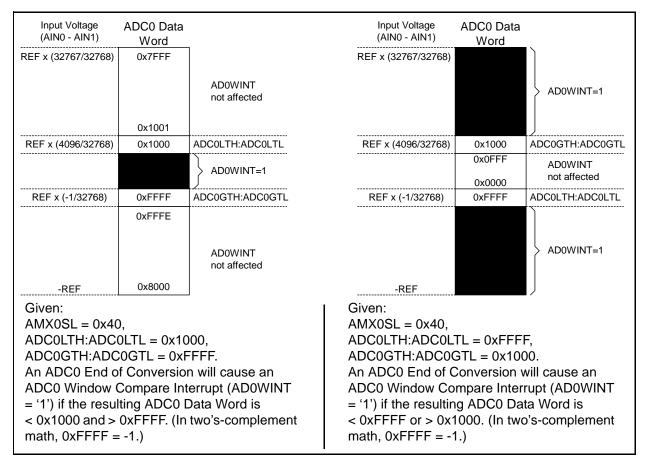

Figure 5.29. 16-Bit ADC0 Window Interrupt Example: Differential Data

| R/W       | R                            | R/W         | R/W          | R/W          | R/W        | R/W          | R/W           | Reset Value   |

|-----------|------------------------------|-------------|--------------|--------------|------------|--------------|---------------|---------------|

| DMA0HL    |                              | R/W         | R/ VV        | DMA0CIE      | DMA0CI     | DMA0EOE      | DMA0EO        | 00000000      |

| Bit7      | Bit6                         | -<br>Bit5   | -<br>Bit4    | Bit3         | Bit2       | Bit1         | Bit0          | 0000000       |

| DII/      | DILO                         | БІІЭ        | DIL4         | БЦЭ          | DILZ       | DILI         | DILU          |               |

| Bit 7:    | DMA0HLT: Ha                  | alt DMA0 C  | )ff-Chip XR  | AM Access    | (C8051F0   | 60/2/4/6 Onl | v).           |               |

|           | 0: DMA0 has                  |             |              |              |            |              | <i>J</i> /-   |               |

|           | 1: Processor                 |             |              |              |            | DMA0 will y  | wait until th | is bit is '0' |

|           | before writing               |             | •            |              | •          |              |               |               |

| Bit 6:    | DMA0XBY: O                   | ff-chip XR/ | AM Busy F    | lag (C8051F  | 060/2/4/6  | Only).       |               |               |

|           | 0: DMA0 is no                | t accessin  | g off-chip 2 | KRAM.        |            |              |               |               |

|           | 1: DMA0 is ac                | cessing of  | f-chip XRA   | M.           |            |              |               |               |

| Bits 5-4: | RESERVED.                    | Write to 00 | )b.          |              |            |              |               |               |

| Bit 3:    | DMA0CIE: Re                  |             |              |              | Enable.    |              |               |               |

|           | 0: Disable Re                | •           |              |              |            |              |               |               |

|           | 1: Enable Rep                |             |              |              |            |              |               |               |

| Bit 2:    | DMA0CI: Rep                  |             |              | •            |            |              |               |               |

|           | 0: Repeat Co                 |             |              |              |            |              |               |               |

| <b>-</b>  | 1: Repeat Co                 |             |              |              |            | e cleared by | software.     |               |

| Bit 1:    | DMA0EOE: E                   | •           |              |              |            |              |               |               |

|           | 0: Disable En                |             |              | •            |            |              |               |               |

| D:4 0.    | 1: Enable End                | •           |              | ipt.         |            |              |               |               |

| Bit 0:    | DMA0EO: En                   |             | •            | a nathaon r  |            |              |               |               |

|           | 0: End-Of-Op<br>1: End-Of-Op |             |              |              |            | it must be a | loorod by a   | oftworo       |

|           | I. End-OI-Op                 |             | liucion na   | s been lecel | veu. mis i | on must be c | lealed by S   | onware.       |

|           |                              |             |              |              |            |              |               |               |

|           |                              |             |              |              |            |              |               |               |

|           |                              |             |              |              |            |              |               |               |

|           |                              |             |              |              |            |              |               |               |

#### Figure 6.5. DMA0CF: DMA0 Configuration Register

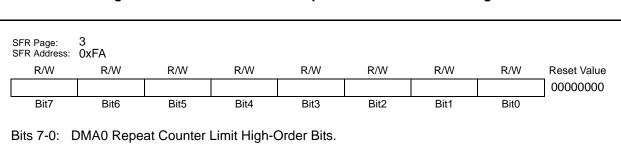

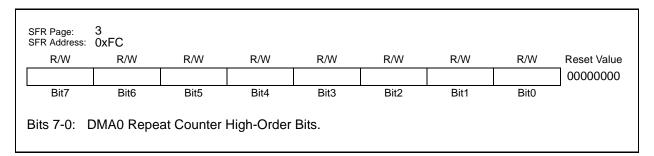

#### Figure 6.14. DMA0CTH: DMA0 Repeat Counter Limit MSB Register

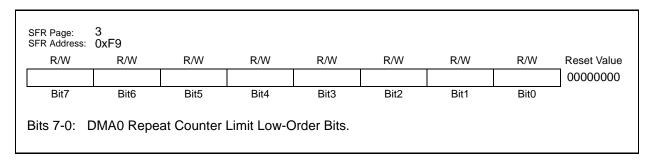

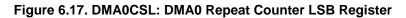

#### Figure 6.15. DMA0CTL: DMA0 Repeat Counter Limit LSB Register

#### Figure 6.16. DMA0CSH: DMA0 Repeat Counter MSB Register

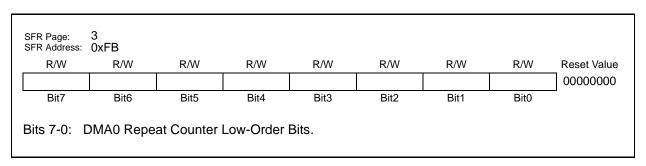

#### 13.2. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. There are 256 bytes of internal data memory and 64 k bytes (C8051F060/1/2/3/4/5) or 32 k bytes (C8051F066/7) of internal program memory address space implemented within the CIP-51. The CIP-51 memory organization is shown in Figure 13.2.

#### Figure 13.2. Memory Map

#### 13.2.1. Program Memory

The CIP-51 has a 64 k byte program memory space. The C8051F060/1/2/3/4/5 devices implement 64 k bytes of this program memory space as in-system re-programmable Flash memory, organized in a contiguous block from addresses 0x0000 to 0xFFFF. Note: 1024 bytes (0xFC00 to 0xFFFF) of this memory are reserved, and are not available for user program storage. The C8051F066/7 implement 32 k bytes of this program memory space as in-system re-programmable Flash memory, organized in a contiguous block from addresses 0x0000 to 0xFFFF.

Program memory is normally assumed to be read-only (using the MOVC instruction). However, the CIP-51 can write to program memory by enabling Flash writes, and using the MOVX instruction. This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to Section "16. Flash Memory" on page 177 for further details.

| R/W      | R/W         | R/W            | R/W                              | R/W                 | R/W          | R/W            | R/W                     | Reset Value           |

|----------|-------------|----------------|----------------------------------|---------------------|--------------|----------------|-------------------------|-----------------------|

| CY       | AC          | F0             | RS1                              | RS0                 | OV           | F1             | PARITY                  | 00000000              |

| Bit7     | Bit6        | Bit5           | Bit4                             | Bit3                | Bit2         | Bit1           | Bit0                    | Bit<br>Addressable    |

|          |             |                |                                  |                     |              |                | SFR Address<br>SFR Page | : 0xD0<br>: All Pages |

| Bit7:    | CY: Carry   |                |                                  |                     |              |                |                         |                       |

|          |             |                | e last arithme<br>ared to 0 by a |                     |              |                | ddition) or a           | borrow                |

| Bit6:    | AC: Auxilia | ,              |                                  |                     | intelle oper | allons.        |                         |                       |

|          |             |                | e last arithme                   | •                   |              |                | ```                     |                       |

|          | tions.      | subtraction    | ) the high ord                   | er nibble. It       | is cleared   | to 0 by all ot | ther arithme            | ic opera-             |

| Bit5:    | F0: User F  | lag 0.         |                                  |                     |              |                |                         |                       |

| Dite 4.0 |             |                | ble, general p                   | ourpose flag        | for use un   | der software   | e control.              |                       |

| Bits4-3: |             | •              | ank Select.<br>ch register bai   | nk is used o        | lurina reais | ster accesse   | S.                      |                       |

|          |             |                | in regioner ison                 |                     |              |                |                         |                       |

|          | RS1         | RS0            | Register Bank                    | Add                 | ess          |                |                         |                       |

|          | 0           | 0              | 0                                | 0x00 -              | 0x07         |                |                         |                       |

|          | 0           | 1              | 1                                | 0x08 -              | 0x0F         |                |                         |                       |

|          | 1           | 0              | 2                                | 0x10 -              | 0x17         |                |                         |                       |

|          | 1           | 1              | 3                                | 0x18 -              | 0x1F         |                |                         |                       |

| Bit2:    | OV: Overfl  | ow Flag        |                                  |                     |              |                |                         |                       |

| Ditz.    |             | •              | ler the followi                  | na circumst         | ances:       |                |                         |                       |

|          |             |                | SUBB instruct                    |                     |              | inge overflov  | <i>N</i> .              |                       |

|          |             |                | sults in an ov                   |                     |              |                |                         |                       |

|          | • A DIV ins | truction ca    | uses a divide-                   | by-zero co          | ndition.     |                |                         |                       |

|          | The OV bit  | is cleared     | to 0 by the AD                   | DD, ADDC,           | SUBB, MU     | IL, and DIV i  | nstructions i           | n all other           |

|          | cases.      |                |                                  |                     |              |                |                         |                       |

| Bit1:    | F1: User F  | 0              |                                  |                     |              |                |                         |                       |

| Dire     |             |                | ble, general p                   | ourpose flag        | for use un   | ider software  | e control.              |                       |

| Bit0:    | PARITY: P   |                |                                  | 1. I. ( I. 10. 1. ) |              |                |                         |                       |

|          |             | set to 1 if th | e sum of the e                   | eight dits in i     | ine accumi   | liator is odd  | and cleared             | II THE SUM            |

|          | is even.    |                |                                  |                     |              |                |                         |                       |

| <u></u>  |             |                |                                  |                     |              |                |                         |                       |

#### Figure 13.16. PSW: Program Status Word

Step 8. Clear the PSWE bit to redirect MOVX write commands to the XRAM data space.

Step 9. Re-enable interrupts.

Write/Erase timing is automatically controlled by hardware. Note that code execution in the 8051 is stalled while the Flash is being programmed or erased.

| Parameter        | Conditions          | Min  | Тур     | Max   | Units       |

|------------------|---------------------|------|---------|-------|-------------|

| Flash Size *     | C8051F060/1/2/3/4/5 |      | 65664 † | •     | Bytes       |

| Flash Size *     | C8051F066/7         |      | 32896   | Bytes |             |

| Endurance        |                     | 20 k | 100 k   |       | Erase/Write |

| Erase Cycle Time |                     | 10   | 12      | 14    | ms          |

| Write Cycle Time |                     | 40   | 50      | 60    | μs          |

| Table 16.1. Flash | Electrical | Characteristics |

|-------------------|------------|-----------------|

|-------------------|------------|-----------------|

\* Includes 128-byte Scratch Pad Area

† 1024 Bytes at location 0xFC00 to 0xFFFF are reserved.

#### 16.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction (as described in the previous section) and read using the MOVC instruction.

An additional 128-byte sector of Flash memory is included for non-volatile data storage. Its smaller sector size makes it particularly well suited as general purpose, non-volatile scratchpad memory. Even though Flash memory can be written a single byte at a time, an entire sector must be erased first. In order to change a single byte of a multi-byte data set, the data must be moved to temporary storage. The 128-byte sector size facilitates updating data without wasting program memory or RAM space. The 128-byte sector is double-mapped over the normal Flash memory area; its address ranges from 0x00 to 0x7F (see Figure 16.1 and Figure 16.2). To access this 128-byte sector, the SFLE bit in PSCTL must be set to logic 1. Code execution from this 128-byte scratchpad sector is not supported.

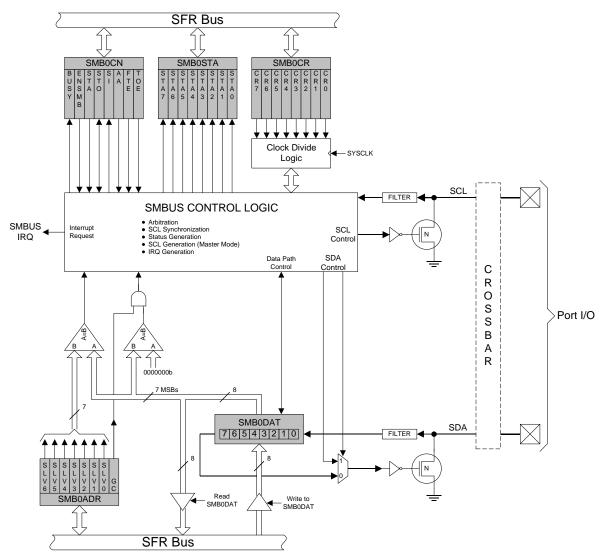

### 20. System Management BUS / I2C BUS (SMBUS0)

The SMBus0 I/O interface is a two-wire, bi-directional serial bus. SMBus0 is compliant with the System Management Bus Specification, version 1.1, and compatible with the I2C serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus0 interface autonomously controlling the serial transfer of the data. A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

SMBus0 may operate as a master and/or slave, and may function on a bus with multiple masters. SMBus0 provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation.

| 0x60 | Own slave address + W received. ACK trans-<br>mitted.                                                      | Wait for data.                                                                    |

|------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 0x68 | Arbitration lost in sending SLA + R/W as mas-<br>ter. Own address + W received. ACK transmit-<br>ted.      | Save current data for retry when bus is free. Wait for data.                      |

| 0x70 | General call address received. ACK transmit-<br>ted.                                                       | Wait for data.                                                                    |

| 0x78 | Arbitration lost in sending SLA + R/W as mas-<br>ter. General call address received. ACK trans-<br>mitted. | Save current data for retry when bus is free.                                     |

| 0x80 | Data byte received. ACK transmitted.                                                                       | Read SMB0DAT. Wait for next byte or STOP.                                         |

| 0x88 | Data byte received. NACK transmitted.                                                                      | Set STO to reset SMBus.                                                           |

| 0x90 | Data byte received after general call address.<br>ACK transmitted.                                         | Read SMB0DAT. Wait for next byte or STOP.                                         |

| 0x98 | Data byte received after general call address.<br>NACK transmitted.                                        | Set STO to reset SMBus.                                                           |

| 0xA0 | STOP or repeated START received.                                                                           | No action necessary.                                                              |

| 0xA8 | Own address + R received. ACK transmitted.                                                                 | Load SMB0DAT with data to transmit.                                               |

| 0xB0 | Arbitration lost in transmitting SLA + R/W as<br>master. Own address + R received. ACK<br>transmitted.     | Save current data for retry when bus is free. Load SMB0DAT with data to transmit. |

| 0xB8 | Data byte transmitted. ACK received.                                                                       | Load SMB0DAT with data to transmit.                                               |

| 0xC0 | Data byte transmitted. NACK received.                                                                      | Wait for STOP.                                                                    |

| 0xC8 | Last data byte transmitted (AA=0). ACK received.                                                           | Set STO to reset SMBus.                                                           |

| 0xD0 | SCL Clock High Timer per SMB0CR timed out                                                                  | Set STO to reset SMBus.                                                           |

| 0x00 | Bus Error (illegal START or STOP)                                                                          | Set STO to reset SMBus.                                                           |

| 0xF8 | ldle                                                                                                       | State does not set SI.                                                            |

| Table 20.1. SMB0STA Status Codes and | States |

|--------------------------------------|--------|

|--------------------------------------|--------|

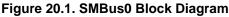

## 21. Enhanced Serial Peripheral Interface (SPI0)

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

#### Figure 21.1. SPI Block Diagram

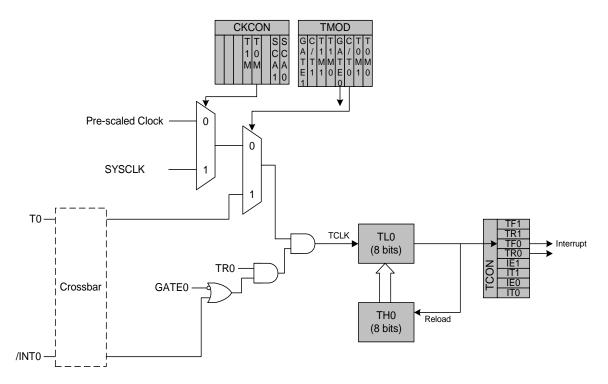

#### 21.6. SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following figures.

| R          | R/W                                                                                                                                                                                                                  | R/W                                                                           | R/W                                                                      | R                                                                        | R                                          | R                          | R              | Reset Value                  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------|----------------------------|----------------|------------------------------|--|--|--|

| SPIBSY     | MSTEN                                                                                                                                                                                                                | CKPHA                                                                         | CKPOL                                                                    | SLVSEL                                                                   | NSSIN                                      | SRMT                       | RXBMT          | 00000111                     |  |  |  |

| Bit7       | Bit6                                                                                                                                                                                                                 | Bit5                                                                          | Bit4                                                                     | Bit3                                                                     | Bit2                                       | Bit1                       | Bit0           |                              |  |  |  |

|            | SFR Address: 0x9A<br>SFR Page: 0                                                                                                                                                                                     |                                                                               |                                                                          |                                                                          |                                            |                            |                |                              |  |  |  |

| Bit 7:     | SPIBSY: SP                                                                                                                                                                                                           |                                                                               |                                                                          |                                                                          |                                            | <b></b>                    |                | ,                            |  |  |  |

| Bit 6:     | This bit is set to logic 1 when a SPI transfer is in progress (Master or slave Mode).<br>MSTEN: Master Mode Enable.<br>0: Disable master mode. Operate in slave mode.<br>1: Enable master mode. Operate as a master. |                                                                               |                                                                          |                                                                          |                                            |                            |                |                              |  |  |  |

| Bit 5:     | CKPHA: SP<br>This bit cont                                                                                                                                                                                           | l0 Clock Pha<br>rols the SPI                                                  | ase.<br>0 clock pha                                                      | ase.                                                                     |                                            |                            |                |                              |  |  |  |

| Bit 4:     | 0: Data centered on first edge of SCK period. <sup>†</sup><br>1: Data centered on second edge of SCK period. <sup>†</sup>                                                                                            |                                                                               |                                                                          |                                                                          |                                            |                            |                |                              |  |  |  |

| Bit 3:     | 1: SCK line I<br>SLVSEL: Sla<br>This bit is se<br>is cleared to                                                                                                                                                      | high in idle s<br>ave Selected<br>at to logic 1 v<br>logic 0 whe              | state.<br>d Flag (rea<br>whenever t<br>n NSS is h                        | he NSS pin<br>ligh (slave n                                              | ot selected                                | ). This bit d              | oes not indi   | cate the                     |  |  |  |

| Bit 2:     | instantaneou<br>NSSIN: NSS<br>This bit mim<br>the register i                                                                                                                                                         | S Instantane                                                                  | ous Pin İnp<br>Intaneous V                                               | out (read on<br>/alue that is                                            | ly).<br>present on                         |                            |                |                              |  |  |  |

| Bit 1:     | SRMT: Shift<br>This bit will b<br>and there is<br>receive buffe<br>the transmit<br>NOTE: SRM                                                                                                                         | Register Er<br>be set to log<br>no new info<br>er. It returns<br>buffer or by | npty (Valid<br>ic 1 when a<br>rmation av<br>to logic 0 v<br>a transition | in Slave Mo<br>all data has<br>ailable to re<br>when a data<br>n on SCK. | ode, read or<br>been transf<br>ad from the | ferred in/ou<br>transmit b | uffer or write | e to the                     |  |  |  |

| Bit 0:     | RXBMT: Red<br>This bit will the<br>information.<br>this bit will re<br>NOTE: RXB                                                                                                                                     | ceive Buffer<br>be set to log<br>If there is ne<br>eturn to logio             | Empty (Va<br>ic 1 when t<br>ew informatic 0.                             | lid in Slave<br>the receive<br>tion availabl                             | buffer has b                               | een read a                 |                |                              |  |  |  |

| sampled of | mode, data or<br>one SYSCLK<br>ee Table 21.1                                                                                                                                                                         | before the e                                                                  | end of each                                                              | n data bit, to                                                           |                                            |                            |                | ta on MISO is<br>r the slave |  |  |  |

| Figure | 21 8  | SPI0CFG:   | SPI0  | Confid | nuration | Register |

|--------|-------|------------|-------|--------|----------|----------|

| Iguie  | 21.0. | 51 1001 0. | 01.10 | Count  | Juration | Register |

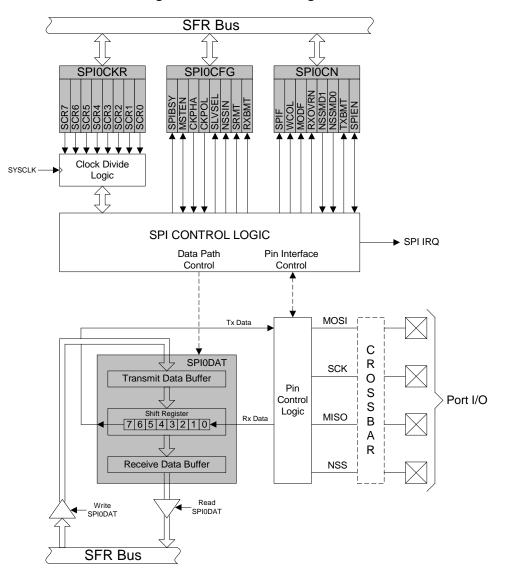

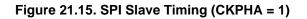

Figure 21.14. SPI Slave Timing (CKPHA = 0)

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

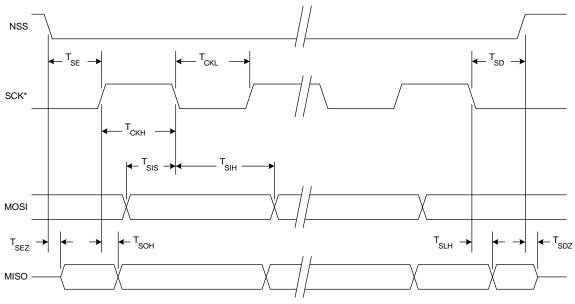

### 23. UART1

UART1 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "23.1. Enhanced Baud Rate Generation" on page 278). Received data buffering allows UART1 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART1 has two associated SFRs: Serial Control Register 1 (SCON1) and Serial Data Buffer 1 (SBUF1). The single SBUF1 location provides access to both transmit and receive registers. Reading SBUF1 accesses the buffered Receive register; writing SBUF1 accesses the Transmit register.

With UART1 interrupts enabled, an interrupt is generated each time a transmit is completed (TI1 is set in SCON1), or a data byte has been received (RI1 is set in SCON1). The UART1 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART1 interrupt (transmit complete or receive complete).

|                              | Frequency: 24.5 MHz          |                      |                                  |                       |                                                 |                  |                                     |  |  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|-------------------------------------|--|--|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select) <sup>†</sup> | T1M <sup>†</sup> | Timer 1<br>Reload<br>Value<br>(hex) |  |  |

| SYSCLK from<br>Internal Osc. | 230400                       | -0.32%               | 106                              | SYSCLK                | XX                                              | 1                | 0xCB                                |  |  |

|                              | 115200                       | -0.32%               | 212                              | SYSCLK                | XX                                              | 1                | 0x96                                |  |  |

|                              | 57600                        | 0.15%                | 426                              | SYSCLK                | XX                                              | 1                | 0x2B                                |  |  |

|                              | 28800                        | -0.32%               | 848                              | SYSCLK / 4            | 01                                              | 0                | 0x96                                |  |  |

|                              | 14400                        | 0.15%                | 1704                             | SYSCLK / 12           | 00                                              | 0                | 0xB9                                |  |  |

|                              | 9600                         | -0.32%               | 2544                             | SYSCLK / 12           | 00                                              | 0                | 0x96                                |  |  |

|                              | 2400                         | -0.32%               | 10176                            | SYSCLK / 48           | 10                                              | 0                | 0x96                                |  |  |

| Sy<br>Int                    | 1200                         | 0.15%                | 20448                            | SYSCLK / 48           | 10                                              | 0                | 0x2B                                |  |  |

|                              |                              | V - Don't oor        | -                                |                       |                                                 |                  |                                     |  |  |

#### Table 23.1. Timer Settings for Standard Baud Rates Using the Internal Oscillator

X = Don't care

<sup>†</sup>SCA1-SCA0 and T1M bit definitions can be found in Section 24.1.

| Table 23.2. Timer Settings for Standard Baud Rates Using an External Oscillator |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

|                              | Frequency: 25.0 MHz          |                      |                                  |                       |                                                 |                  |                                     |  |  |  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|-------------------------------------|--|--|--|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select) <sup>†</sup> | T1M <sup>†</sup> | Timer 1<br>Reload<br>Value<br>(hex) |  |  |  |

| SYSCLK from<br>External Osc. | 230400                       | -0.47%               | 108                              | SYSCLK                | XX                                              | 1                | 0xCA                                |  |  |  |

|                              | 115200                       | 0.45%                | 218                              | SYSCLK                | XX                                              | 1                | 0x93                                |  |  |  |

|                              | 57600                        | -0.01%               | 434                              | SYSCLK                | XX                                              | 1                | 0x27                                |  |  |  |

|                              | 28800                        | 0.45%                | 872                              | SYSCLK / 4            | 01                                              | 0                | 0x93                                |  |  |  |

|                              | 14400                        | -0.01%               | 1736                             | SYSCLK/4              | 01                                              | 0                | 0x27                                |  |  |  |

|                              | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                              | 0                | 0x5D                                |  |  |  |

|                              | 2400                         | 0.45%                | 10464                            | SYSCLK / 48           | 10                                              | 0                | 0x93                                |  |  |  |

|                              | 1200                         | -0.01%               | 20832                            | SYSCLK / 48           | 10                                              | 0                | 0x27                                |  |  |  |

| SYSCLK from<br>Internal Osc. | 57600                        | -0.47%               | 432                              | EXTCLK / 8            | 11                                              | 0                | 0xE5                                |  |  |  |

|                              | 28800                        | -0.47%               | 864                              | EXTCLK / 8            | 11                                              | 0                | 0xCA                                |  |  |  |

|                              | 14400                        | 0.45%                | 1744                             | EXTCLK / 8            | 11                                              | 0                | 0x93                                |  |  |  |

|                              | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                              | 0                | 0x5D                                |  |  |  |

X = Don't care

<sup>†</sup>SCA1-SCA0 and T1M bit definitions can be found in Section 24.1.

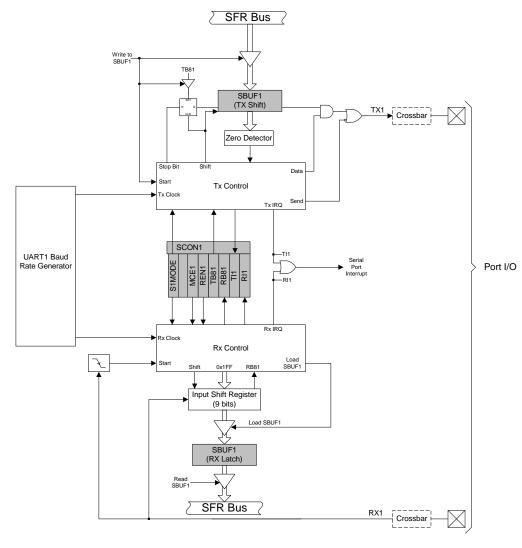

#### 24.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

#### 24.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 or Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from 0xFF to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal /INT0 is low.

Figure 24.2. T0 Mode 2 Block Diagram

#### 24.2. Timer 2, Timer 3, and Timer 4

Timers 2, 3, and 4 are 16-bit counter/timers, each formed by two 8-bit SFRs: TMRnL (low byte) and TMRnH (high byte) where n = 2, 3, and 4 for timers 2, 3, and 4 respectively. These timers feature autoreload, capture, and toggle output modes with the ability to count up or down. Capture Mode and Autoreload mode are selected using bits in the Timer 2, 3, and 4 Control registers (TMRnCN). Toggle output mode is selected using the Timer 2, 3, and 4 Configuration registers (TMRnCF). These timers may also be used to generate a square-wave at an external pin. Timers 2, 3, and 4 can use either the system clock (divided by one, two, or twelve), external clock (divided by eight) or transitions on an external input pin as its clock source. Timer 2 and 3 can be used to start an ADC Data Conversion and Timers 2, 3, and 4 can schedule DAC outputs. Timers 1, 2, 3, or 4 may be used to generate baud rates for UART 0. Only Timer 1 can be used to generate baud rates for UART 1.

The Counter/Timer Select bit C/Tn bit (TMRnCN.1) configures the peripheral as a counter or timer. Clearing C/Tn configures the Timer to be in a timer mode (i.e., the selected timer clock source as the input for the timer). When C/Tn is set to 1, the timer is configured as a counter (i.e., high-to-low transitions at the Tn input pin increment (or decrement) the counter/timer register. Refer to Section "18.1. Ports 0 through 3 and the Priority Crossbar Decoder" on page 205 for information on selecting and configuring external I/O pins for digital peripherals, such as the Tn pin.

Timer 2, 3, and 4 can use either SYSCLK, SYSCLK divided by 2, SYSCLK divided by 12, an external clock divided by 8, or high-to-low transitions on the Tn input pin as its clock source when operating in Counter/ Timer with Capture mode. Clearing the C/Tn bit (TnCON.1) selects the system clock/external clock as the input for the timer. The Timer Clock Select bits TnM0 and TnM1 in TMRnCF can be used to select the system clock undivided, system clock divided by two, system clock divided by 12, or an external clock provided at the XTAL1/XTAL2 pins divided by 8 (see Figure 24.14). When C/Tn is set to logic 1, a high-to-low transition at the Tn input pin increments the counter/timer register (i.e., configured as a counter).

#### 24.2.1. Configuring Timer 2, 3, and 4 to Count Down

Timers 2, 3, and 4 have the ability to count down. When the timer's respective Decrement Enable Bit (DCENn) in the Timer Configuration Register (See Figure 24.14) is set to '1', the timer can then count *up* or *down*. When DCENn = 1, the direction of the timer's count is controlled by the TnEX pin's logic level. When TnEX = 1, the counter/timer will count up; when TnEX = 0, the counter/timer will count down. To use this feature, TnEX must be enabled in the digital crossbar and configured as a digital input.

Note: When DCENn = 1, other functions of the TnEX input (i.e., capture and auto-reload) are not available. TnEX will only control the direction of the timer when DCENn = 1.