Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                          |

| Number of I/O              | 24                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 2x16b                                                      |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 64-TQFP                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f067-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 04 5 Optical Ole all Titoria a                         | 050 |

|--------------------------------------------------------|-----|

| 21.5.Serial Clock Timing                               | 256 |

| 21.6.SPI Special Function Registers                    |     |

| 22. UART0                                              | 265 |

| 22.1.UART0 Operational Modes                           | 266 |

| 22.1.1.Mode 0: Synchronous Mode                        | 266 |

| 22.1.2.Mode 1: 8-Bit UART, Variable Baud Rate          | 267 |

| 22.1.3.Mode 2: 9-Bit UART, Fixed Baud Rate             | 269 |

| 22.1.4.Mode 3: 9-Bit UART, Variable Baud Rate          |     |

| 22.2.Multiprocessor Communications                     |     |

| 22.2.1.Configuration of a Masked Address               |     |

| 22.2.2.Broadcast Addressing                            | 271 |

| 22.3.Frame and Transmission Error Detection            | 272 |

| 23. UART1                                              |     |

| 23.1.Enhanced Baud Rate Generation                     |     |

|                                                        |     |

| 23.2.Operational Modes<br>23.2.1.8-Bit UART            |     |

|                                                        |     |

| 23.2.2.9-Bit UART                                      |     |

| 23.3.Multiprocessor Communications                     |     |

| 24. Timers                                             | 287 |

| 24.1.Timer 0 and Timer 1                               |     |

| 24.1.1.Mode 0: 13-bit Counter/Timer                    |     |

| 24.1.2.Mode 1: 16-bit Counter/Timer                    |     |

| 24.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload    |     |

| 24.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) | 290 |

| 24.2.Timer 2, Timer 3, and Timer 4                     | 295 |

| 24.2.1.Configuring Timer 2, 3, and 4 to Count Down     | 295 |

| 24.2.2.Capture Mode                                    |     |

| 24.2.3.Auto-Reload Mode                                | 297 |

| 24.2.4.Toggle Output Mode                              |     |

| 25. Programmable Counter Array                         |     |

| 25.1.PCA Counter/Timer                                 |     |

| 25.2.Capture/Compare Modules                           |     |

| 25.2.1.Edge-triggered Capture Mode                     |     |

| 25.2.2.Software Timer (Compare) Mode                   |     |

| 25.2.3.High Speed Output Mode                          |     |

| 25.2.4.Frequency Output Mode                           |     |

| 25.2.5.8-Bit Pulse Width Modulator Mode                | 210 |

| 25.2.6.16-Bit Pulse Width Modulator Mode               |     |

|                                                        |     |

| 25.3.Register Descriptions for PCA0                    |     |

| 26.JTAG (IEEE 1149.1)                                  |     |

| 26.1.Boundary Scan                                     |     |

| 26.1.1.EXTEST Instruction                              |     |

| 26.1.2.SAMPLE Instruction                              |     |

| 26.1.3.BYPASS Instruction                              |     |

| 26.1.4.IDCODE Instruction                              | 321 |

| Figure 18.5. XBR0: Port I/O Crossbar Register 0<br>Figure 18.6. XBR1: Port I/O Crossbar Register 1<br>Figure 18.7. XBR2: Port I/O Crossbar Register 2<br>Figure 18.8. XBR3: Port I/O Crossbar Register 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 210                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 18.6. XBR1: Port I/O Crossbar Register 1<br>Figure 18.7. XBR2: Port I/O Crossbar Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 212                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

| Figure 18.9. P0: Port0 Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 214                                                                                                                                             |

| Figure 18.10. P0MDOUT: Port0 Output Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 214                                                                                                                                             |

| Figure 18.11. P1: Port1 Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

| Figure 18.12. P1MDIN: Port1 Input Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 215                                                                                                                                             |

| Figure 18.13. P1MDOUT: Port1 Output Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 216                                                                                                                                             |

| Figure 18.14. P2: Port2 Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

| Figure 18.15. P2MDIN: Port2 Input Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 217                                                                                                                                             |

| Figure 18.16. P2MDOUT: Port2 Output Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 217                                                                                                                                             |

| Figure 18.17. P3: Port3 Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 218                                                                                                                                             |

| Figure 18.18. P3MDOUT: Port3 Output Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 218                                                                                                                                             |

| Figure 18.19. P4: Port4 Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 221                                                                                                                                             |

| Figure 18.20. P4MDOUT: Port4 Output Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 221                                                                                                                                             |

| Figure 18.21. P5: Port5 Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 222                                                                                                                                             |

| Figure 18.22. P5MDOUT: Port5 Output Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 222                                                                                                                                             |

| Figure 18.23. P6: Port6 Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 223                                                                                                                                             |

| Figure 18.24. P6MDOUT: Port6 Output Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 223                                                                                                                                             |

| Figure 18.25. P7: Port7 Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

| Figure 18.26. P7MDOUT: Port7 Output Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

| 19. Controller Area Network (CAN0, C8051F060/1/2/3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

| Figure 19.1. CAN Controller Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

| Figure 19.2. Typical CAN Bus Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

| Figure 19.3. CAN0DATH: CAN Data Access Register High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |

| Figure 19.4. CAN0DATL: CAN Data Access Register Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |

| Figure 19.5. CAN0ADR: CAN Address Index Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 232                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

| Figure 19.6. CAN0CN: CAN Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 232                                                                                                                                             |

| Figure 19.6. CAN0CN: CAN Control Register<br>Figure 19.7. CAN0TST: CAN Test Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 232<br>233                                                                                                                                      |

| Figure 19.6. CAN0CN: CAN Control Register<br>Figure 19.7. CAN0TST: CAN Test Register<br>Figure 19.8. CAN0STA: CAN Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 232<br>233<br>233                                                                                                                               |

| Figure 19.6. CAN0CN: CAN Control Register<br>Figure 19.7. CAN0TST: CAN Test Register<br>Figure 19.8. CAN0STA: CAN Status Register<br>20. System Management BUS / I2C BUS (SMBUS0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 232<br>233<br>233<br><b>235</b>                                                                                                                 |

| Figure 19.6. CAN0CN: CAN Control Register<br>Figure 19.7. CAN0TST: CAN Test Register<br>Figure 19.8. CAN0STA: CAN Status Register<br>20. System Management BUS / I2C BUS (SMBUS0)<br>Figure 20.1. SMBus0 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 232<br>233<br>233<br>235<br>235                                                                                                                 |

| <ul> <li>Figure 19.6. CAN0CN: CAN Control Register</li> <li>Figure 19.7. CAN0TST: CAN Test Register</li> <li>Figure 19.8. CAN0STA: CAN Status Register</li> <li>20. System Management BUS / I2C BUS (SMBUS0)</li> <li>Figure 20.1. SMBus0 Block Diagram</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 232<br>233<br>233<br>235<br>235<br>236                                                                                                          |

| <ul> <li>Figure 19.6. CANOCN: CAN Control Register</li> <li>Figure 19.7. CANOTST: CAN Test Register</li> <li>Figure 19.8. CANOSTA: CAN Status Register</li> <li><b>20. System Management BUS / I2C BUS (SMBUS0)</b></li> <li>Figure 20.1. SMBus0 Block Diagram</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                | 232<br>233<br>233<br>235<br>235<br>236<br>237                                                                                                   |

| <ul> <li>Figure 19.6. CANOCN: CAN Control Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 232<br>233<br>233<br>235<br>236<br>237<br>238                                                                                                   |

| <ul> <li>Figure 19.6. CANOCN: CAN Control Register</li> <li>Figure 19.7. CANOTST: CAN Test Register</li> <li>Figure 19.8. CANOSTA: CAN Status Register</li> <li><b>20. System Management BUS / I2C BUS (SMBUS0)</b></li> <li>Figure 20.1. SMBus0 Block Diagram</li> <li>Figure 20.2. Typical SMBus Configuration</li> <li>Figure 20.3. SMBus Transaction</li> <li>Figure 20.4. Typical Master Transmitter Sequence</li></ul>                                                                                                                                                                                                                                                                                            | 232<br>233<br>233<br>235<br>235<br>236<br>237<br>238<br>238                                                                                     |

| Figure 19.6. CANOCN: CAN Control Register<br>Figure 19.7. CANOTST: CAN Test Register<br>Figure 19.8. CANOSTA: CAN Status Register<br><b>20. System Management BUS / I2C BUS (SMBUS0)</b><br>Figure 20.1. SMBus0 Block Diagram<br>Figure 20.2. Typical SMBus Configuration<br>Figure 20.3. SMBus Transaction<br>Figure 20.4. Typical Master Transmitter Sequence<br>Figure 20.5. Typical Master Receiver Sequence<br>Figure 20.6. Typical Slave Transmitter Sequence                                                                                                                                                                                                                                                     | 232<br>233<br>233<br>235<br>235<br>236<br>237<br>238<br>238<br>238<br>239                                                                       |

| Figure 19.6. CANOCN: CAN Control Register<br>Figure 19.7. CANOTST: CAN Test Register<br>Figure 19.8. CANOSTA: CAN Status Register.<br><b>20. System Management BUS / I2C BUS (SMBUS0)</b><br>Figure 20.1. SMBus0 Block Diagram<br>Figure 20.2. Typical SMBus Configuration<br>Figure 20.3. SMBus Transaction<br>Figure 20.4. Typical Master Transmitter Sequence.<br>Figure 20.5. Typical Master Receiver Sequence.<br>Figure 20.6. Typical Slave Transmitter Sequence.<br>Figure 20.7. Typical Slave Receiver Sequence.                                                                                                                                                                                                | 232<br>233<br>233<br>235<br>235<br>235<br>236<br>237<br>238<br>238<br>238<br>239<br>240                                                         |

| Figure 19.6. CANOCN: CAN Control Register<br>Figure 19.7. CANOTST: CAN Test Register<br>Figure 19.8. CANOSTA: CAN Status Register<br><b>20. System Management BUS / I2C BUS (SMBUS0)</b><br>Figure 20.1. SMBus0 Block Diagram<br>Figure 20.2. Typical SMBus Configuration<br>Figure 20.3. SMBus Transaction<br>Figure 20.4. Typical Master Transmitter Sequence<br>Figure 20.5. Typical Master Receiver Sequence<br>Figure 20.6. Typical Slave Transmitter Sequence<br>Figure 20.7. Typical Slave Receiver Sequence<br>Figure 20.8. SMB0CN: SMBus0 Control Register                                                                                                                                                     | 232<br>233<br>233<br>235<br>235<br>235<br>236<br>237<br>238<br>238<br>238<br>239<br>240<br>240<br>243                                           |

| Figure 19.6. CANOCN: CAN Control Register<br>Figure 19.7. CANOTST: CAN Test Register<br>Figure 19.8. CANOSTA: CAN Status Register<br><b>20. System Management BUS / I2C BUS (SMBUS0)</b><br>Figure 20.1. SMBus0 Block Diagram<br>Figure 20.2. Typical SMBus Configuration<br>Figure 20.3. SMBus Transaction<br>Figure 20.4. Typical Master Transmitter Sequence<br>Figure 20.5. Typical Master Receiver Sequence<br>Figure 20.6. Typical Slave Transmitter Sequence<br>Figure 20.7. Typical Slave Receiver Sequence<br>Figure 20.8. SMB0CN: SMBus0 Control Register<br>Figure 20.9. SMB0CR: SMBus0 Clock Rate Register                                                                                                  | 232<br>233<br>233<br>235<br>235<br>235<br>236<br>237<br>238<br>238<br>238<br>238<br>239<br>240<br>240<br>243<br>244                             |

| Figure 19.6. CAN0CN: CAN Control Register<br>Figure 19.7. CAN0TST: CAN Test Register<br>Figure 19.8. CAN0STA: CAN Status Register<br><b>20. System Management BUS / I2C BUS (SMBUS0)</b><br>Figure 20.1. SMBus0 Block Diagram<br>Figure 20.2. Typical SMBus Configuration<br>Figure 20.3. SMBus Transaction<br>Figure 20.4. Typical Master Transmitter Sequence<br>Figure 20.5. Typical Master Receiver Sequence<br>Figure 20.6. Typical Slave Transmitter Sequence<br>Figure 20.7. Typical Slave Receiver Sequence<br>Figure 20.8. SMB0CN: SMBus0 Control Register<br>Figure 20.9. SMB0CR: SMBus0 Clock Rate Register<br>Figure 20.10. SMB0DAT: SMBus0 Data Register                                                   | 232<br>233<br>233<br>235<br>235<br>236<br>237<br>238<br>238<br>238<br>238<br>238<br>239<br>240<br>240<br>243<br>244<br>245                      |

| Figure 19.6. CANOCN: CAN Control Register<br>Figure 19.7. CANOTST: CAN Test Register<br>Figure 19.8. CANOSTA: CAN Status Register<br><b>20. System Management BUS / I2C BUS (SMBUS0)</b><br>Figure 20.1. SMBus0 Block Diagram<br>Figure 20.2. Typical SMBus Configuration<br>Figure 20.3. SMBus Transaction<br>Figure 20.4. Typical Master Transmitter Sequence<br>Figure 20.5. Typical Master Receiver Sequence<br>Figure 20.6. Typical Slave Transmitter Sequence<br>Figure 20.7. Typical Slave Receiver Sequence<br>Figure 20.8. SMB0CN: SMBus0 Control Register<br>Figure 20.9. SMB0CR: SMBus0 Clock Rate Register<br>Figure 20.10. SMB0DAT: SMBus0 Data Register<br>Figure 20.11. SMB0ADR: SMBus0 Address Register | 232<br>233<br>233<br>235<br>235<br>235<br>236<br>237<br>238<br>238<br>238<br>238<br>239<br>240<br>243<br>244<br>245<br>245<br>246               |

| Figure 19.6. CAN0CN: CAN Control Register<br>Figure 19.7. CAN0TST: CAN Test Register<br>Figure 19.8. CAN0STA: CAN Status Register<br><b>20. System Management BUS / I2C BUS (SMBUS0)</b><br>Figure 20.1. SMBus0 Block Diagram<br>Figure 20.2. Typical SMBus Configuration<br>Figure 20.3. SMBus Transaction<br>Figure 20.4. Typical Master Transmitter Sequence<br>Figure 20.5. Typical Master Receiver Sequence<br>Figure 20.6. Typical Slave Transmitter Sequence<br>Figure 20.7. Typical Slave Receiver Sequence<br>Figure 20.8. SMB0CN: SMBus0 Control Register<br>Figure 20.9. SMB0CR: SMBus0 Clock Rate Register<br>Figure 20.10. SMB0DAT: SMBus0 Data Register                                                   | 232<br>233<br>233<br>235<br>235<br>235<br>236<br>237<br>238<br>238<br>238<br>238<br>238<br>239<br>240<br>240<br>243<br>244<br>245<br>246<br>247 |

## 1.1. CIP-51<sup>™</sup> Microcontroller Core

### 1.1.1. Fully 8051 Compatible

The C8051F06x family of devices utilizes Silicon Labs' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The core has all the peripherals included with a standard 8052, including five 16-bit counter/timers, two full-duplex UARTs, 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space, and bit-addressable I/O Ports.

### 1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12-to-24 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

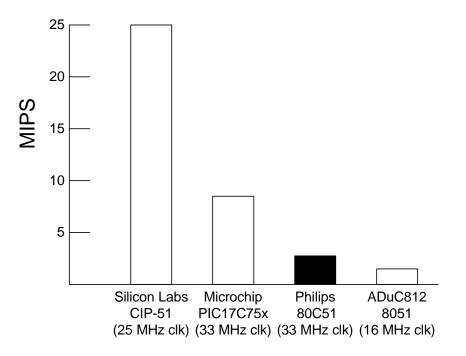

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. Figure 1.5 shows a comparison of peak throughputs of various 8-bit microcontroller cores with their maximum system clocks.

Figure 1.5. Comparison of Peak MCU Execution Speeds

### 1.2. On-Chip Memory

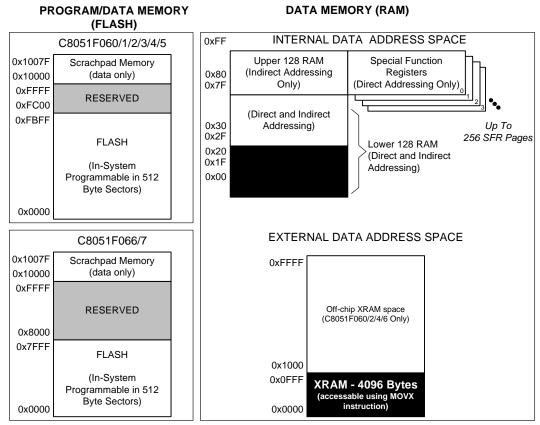

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The CIP-51 SFR address space contains up to 256 *SFR Pages*. In this way, the CIP-51 MCU can accommodate the many SFRs required to control and configure the various peripherals featured on the device. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

The CIP-51 in the C8051F060/1/2/3/4/5/6/7 MCUs additionally has an on-chip 4 kB RAM block. The onchip 4 kB block can be addressed over the entire 64 k external data memory address range (overlapping 4 k boundaries). The C8051F060/2/4/6 also have an external memory interface (EMIF) for accessing offchip data memory or memory-mapped peripherals. External data memory address space can be mapped to on-chip memory only, off-chip memory only, or a combination of the two (addresses up to 4 k directed to on-chip, above 4 k directed to EMIF). The EMIF is also configurable for multiplexed or non-multiplexed address/data lines.

The MCU's program memory consists of 64 k (C8051F060/1/2/3/4/5) or 32 k (C8051F066/7) of Flash. This memory may be reprogrammed in-system in 512 byte sectors, and requires no special off-chip programming voltage. On the C8051F060/1/2/3/4/5, the 1024 bytes from addresses 0xFC00 to 0xFFFF are reserved. There is also a single 128 byte Scratchpad Memory sector on all devices which may be used by firmware for non-volatile data storage. See Figure 1.7 for the MCU system memory map.

Figure 1.7. On-Chip Memory Map

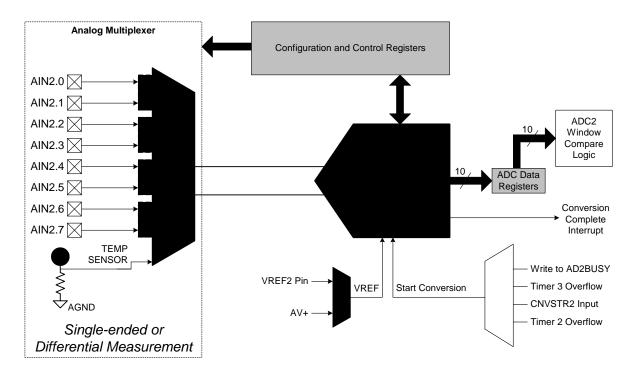

## 1.9. 10-Bit Analog to Digital Converter

The C8051F060/1/2/3 devices have an on-board 10-bit SAR ADC (ADC2) with a 9-channel input multiplexer and programmable gain amplifier. This ADC features a 200 ksps maximum throughput and true 10-bit performance with an INL of ±1LSB. Eight input pins are available for measurement and can be programmed as single-ended or differential inputs. Additionally, the on-chip temperature sensor can be used as an input to the ADC. The ADC is under full control of the CIP-51 microcontroller via the Special Function Registers. The ADC2 voltage reference is selected between the analog power supply (AV+) and the external VREF2 pin. User software may put ADC2 into shutdown mode to save power.

A flexible conversion scheduling system allows ADC2 conversions to be initiated by software commands, timer overflows, or an external input signal. Conversion completions are indicated by a status bit and an interrupt (if enabled), and the resulting 10-bit data word is latched into two SFR locations upon completion.

ADC2 also contains Window Compare registers, which can be configured to interrupt the controller when ADC2 data is within or outside of a specified range. ADC2 can monitor a key voltage continuously in background mode, and not interrupt the controller unless the converted data is within the specified window.

Figure 1.13. 10-Bit ADC Diagram

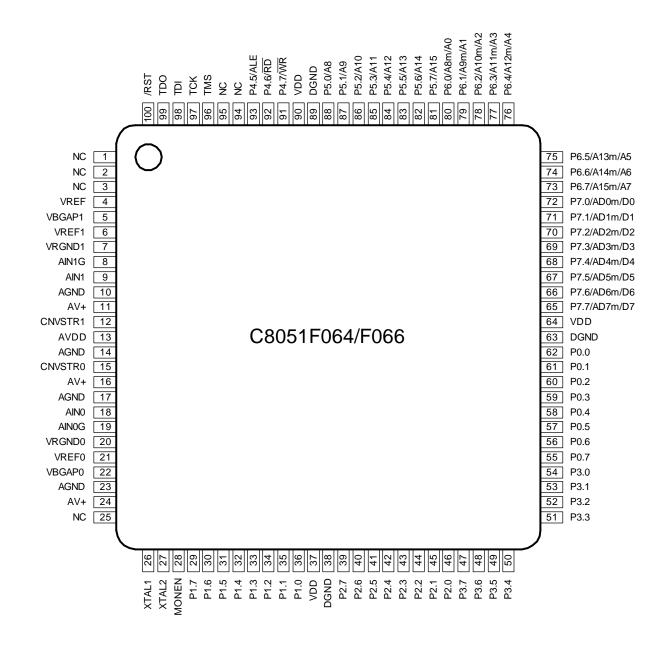

Figure 4.2. C8051F064 / C8051F066 Pinout Diagram (TQFP-100)

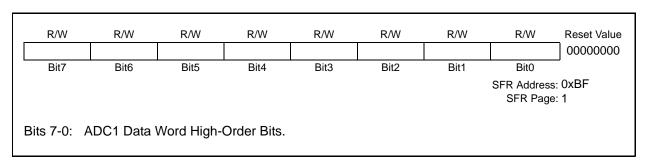

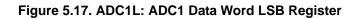

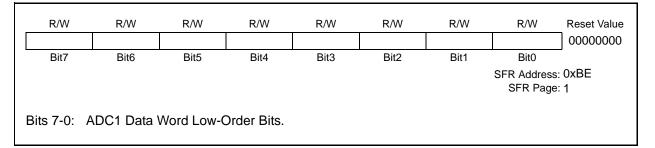

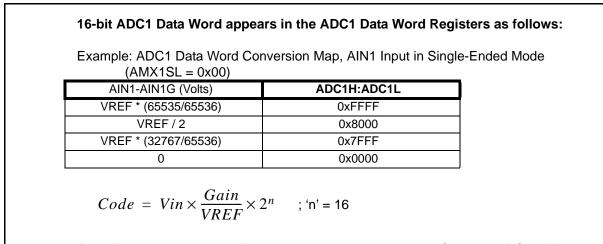

### Figure 5.16. ADC1H: ADC1 Data Word MSB Register

### Figure 5.18. ADC1 Data Word Example

For differential mode, the differential data word appears in ADC0H and ADC0L. The singleended ADC1 results are always present in ADC1H and ADC1L, regardless of the operating mode.

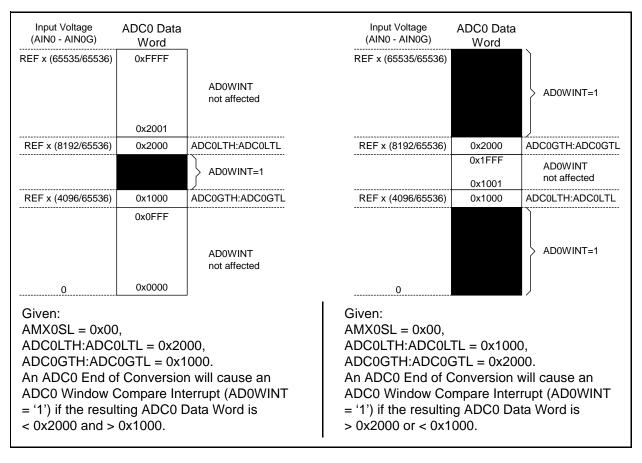

## 5.5. ADC0 Programmable Window Detector

The ADC0 Programmable Window Detector continuously compares the ADC0 output to user-programmed limits, and notifies the system when an out-of-bound condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in ADC0CN) can also be used in polled mode. The high and low bytes of the reference words are loaded into the ADC0 Greater-Than and ADC0 Less-Than registers (ADC0GTH, ADC0GTL, ADC0LTH, and ADC0LTL). The Window Detector can be used in single-ended or differential mode. In signle-ended mode, the Window Detector compares the ADC0GTx and ADC0LTx registers to the output of ADC0. In differential mode, the combined output of ADC0 and ADC1 (contained in the ADC0 data registers) is used for the comparison. Reference comparisons are shown starting on page 71. Notice that the window detector flag can be asserted when the measured data is inside or outside the user-programmed limits, depending on the programming of the ADC0GTx and ADC0LTx registers.

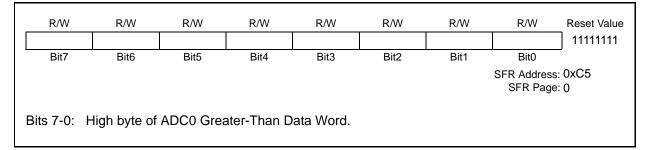

Figure 5.24. ADC0GTH: ADC0 Greater-Than Data High Byte Register

Figure 5.25. ADC0GTL: ADC0 Greater-Than Data Low Byte Register

| R/W                                                | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W                   | Reset Value |  |  |

|----------------------------------------------------|------|------|------|------|------|------|-----------------------|-------------|--|--|

| Bit7                                               | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0                  | 11111111    |  |  |

|                                                    |      |      |      |      |      |      | SFR Addres<br>SFR Pag | -           |  |  |

| Bits 7-0: Low byte of ADC0 Greater-Than Data Word. |      |      |      |      |      |      |                       |             |  |  |

Figure 5.28. 16-Bit ADC0 Window Interrupt Example: Single-Ended Data

| R/W                                                                                                                                                                   | R/W R/W          | R/W                           | R/W   | R/W     | R/W                            | R/W    | Reset Value  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|-------|---------|--------------------------------|--------|--------------|--|

| -                                                                                                                                                                     |                  | - AM                          | X2AD3 | AMX2AD2 | AMX2AD1                        | AMX2AD | 00000000     |  |

| Bit7                                                                                                                                                                  | Bit6 Bit5        | Bit4                          | Bit3  | Bit2    | Bit1                           | Bit0   |              |  |

| Bits 7-4: UNUSED. Read = 0000b; Write = don't care.<br>Bits 3-0: AMX2AD3-0: AMX2 Address Bits.<br>0000-1111b: ADC input multiplexer channel selected per chart below. |                  |                               |       |         |                                |        |              |  |

| AMX2AD3-0                                                                                                                                                             | Single-Ended     | Measurement                   | AMX2  | 2AD3-0  | Differential Measurement       |        |              |  |

| 0000                                                                                                                                                                  | AIN2.0           | AIN01IC = 0                   | 00    | 000     | +(AIN2.0) -(A                  | IN2.1) | AIN01IC = 1  |  |

| 0001                                                                                                                                                                  | AIN2.1           |                               | 00    | 001     | +(AIN2.1) -(A                  | IN2.0) | AINOTIC = 1  |  |

| 0010                                                                                                                                                                  | AIN2.2           | AIN23IC = 0                   | 00    | 010     | +(AIN2.2) -(A                  | IN2.3) | AIN23IC = 1  |  |

|                                                                                                                                                                       | AIN2.3           |                               | 00    | 011     | +(AIN2.3) -(A                  | IN2.2) | AIN25IC = 1  |  |

| 0011                                                                                                                                                                  |                  |                               | 0,    | 100     | +(AIN2.4) -(A                  | IN2.5) | AIN45IC = 1  |  |

| 0011<br>0100                                                                                                                                                          | AIN2.4           | $\Delta N M A E I = 0$        |       |         |                                |        | AIIN45IC = 1 |  |

|                                                                                                                                                                       | AIN2.4<br>AIN2.5 | - AIN45IC = 0                 | -     | 101     | +(AIN2.5) -(A                  | IN2.4) |              |  |

| 0100                                                                                                                                                                  |                  |                               | 0.    |         | +(AIN2.5) -(A<br>+(AIN2.6) -(A | IN2.7) |              |  |

| 0100<br>0101                                                                                                                                                          | AIN2.5           | - AIN45IC = 0 $- AIN67IC = 0$ | 0,    | 110     | . , .                          | IN2.7) | AIN67IC = 1  |  |

### Figure 7.6. AMX2SL: AMUX2 Channel Select Register

Comparator interrupts can be generated on either rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see Section "13.3. Interrupt Handler" on page 151). The rising and/or falling -edge interrupts are enabled using the comparator's Rising/Falling Edge Interrupt Enable Bits (CPnRIE and CPnFIE) in their respective Comparator Mode Selection Register (CPTnMD), shown in Figure 12.4. These bits allow the user to control which edge (or both) will cause a comparator interrupt. However, the comparator interrupt must also be enabled in the Extended Interrupt Enable Register (EIE1). The CPnFIF flag is set to logic 1 upon a Comparator falling-edge interrupt, and the CPnRIF flag is set to logic 1 upon the Comparator can be obtained at any time by reading the CPnOUT bit. A Comparator is enabled by setting its respective CPnEN bit to logic 1, and is disabled by clearing this bit to logic 0.Upon enabling a comparator, the output of the comparator is not immediately valid. Before using a comparator as an interrupt or reset source, software should wait for a minimum of the specified "Power-up time" as specified in Table 12.1, "Comparator Electrical Characteristics," on page 122.

## **12.1. Comparator Inputs**

| Comparator Input | Port PIN |

|------------------|----------|

| CP0 +            | P2.6     |

| CP0 -            | P2.7     |

| CP1 +            | P2.2     |

| CP1 -            | P2.3     |

| CP2 +            | P2.4     |

| CP2 -            | P2.5     |

The Port pins selected as comparator inputs should be configured as analog inputs in the Port 2 Input Configuration Register (for details on Port configuration, see Section "18.1.3. Configuring Port Pins as Digital Inputs" on page 207). The inputs for Comparator are on Port 2 as follows:

| R/W       | R/W                              | R/W          | R/W           | R/W           | R/W           | R/W           | R/W           | Reset Value        |

|-----------|----------------------------------|--------------|---------------|---------------|---------------|---------------|---------------|--------------------|

| CPnEN     | -                                | CPnRIF       | CPnFIF        | CPnHYP1       | CPnHYP0       | CPnHYN1       | CPnHYN0       | 00000000           |

| Bit7      | Bit6                             | Bit5         | Bit4          | Bit3          | Bit2          | Bit1          | Bit0          | Bit<br>Addressable |

| SFR Addre | ss: CPT0CN: 0x8                  | 8; CPT1CN: 0 | x88; CPT2CN   | l: 0x88       |               |               |               |                    |

| SFR Pag   | es: CPT0CN: pag                  | e 1; CPT1CN  | : page 2; CPT | 2CN: page 3   |               |               |               |                    |

| D::-7     |                                  | . –          |               |               |               |               |               |                    |

| Bit7:     | CPnEN: Com                       |              |               | lease see r   | iote below.   | )             |               |                    |

|           | 0: Comparate<br>1: Comparate     |              |               |               |               |               |               |                    |

| Bit6:     | CPnOUT: Co                       |              |               | Flag          |               |               |               |                    |

| Dito.     | 0: Voltage on                    |              |               | r lay.        |               |               |               |                    |

|           | 1: Voltage on                    |              |               |               |               |               |               |                    |

| Bit5:     | CPnRIF: Cor                      |              |               | Interrupt Fla | g.            |               |               |                    |

|           | 0: No Compa                      |              | 0 0           | •             | •             | e this flag v | vas last clea | ared.              |

|           | 1: Comparate                     | or Rising Ed | dge Interrup  | ot has occur  | red. Must b   | e cleared b   | y software.   |                    |

| Bit4:     | CPnFIF: Con                      | •            |               | •             | •             |               |               |                    |

|           | 0: No Compa                      |              |               |               |               | •             |               | ared.              |

|           | 1: Comparate                     | •            | •             |               |               |               | by software.  |                    |

| Bits3-2:  | CPnHYP1-0:                       |              |               | Hysteresis C  | Control Bits. |               |               |                    |

|           | 00: Positive I                   |              |               |               |               |               |               |                    |

|           | 01: Positive I<br>10: Positive I |              |               |               |               |               |               |                    |

|           | 11: Positive F                   |              |               |               |               |               |               |                    |

| Bits1-0:  | CPnHYN1-0:                       |              |               | Hysteresis    | Control Bits  | 2             |               |                    |

| Bitor o.  | 00: Negative                     |              | •             |               | Control Dia   |               |               |                    |

|           | 01: Negative                     |              |               |               |               |               |               |                    |

|           | 10: Negative                     |              |               |               |               |               |               |                    |

|           | 11: Negative                     | Hysteresis   | = 20 mV.      |               |               |               |               |                    |

| NOTE:     | Upon enablin                     | ig a compa   | rator, the o  | utput of the  | comparator    | is not imme   | ediately vali | d. Before          |

|           | using a comp                     |              |               |               |               |               |               |                    |

|           | the specified                    | •            | time" as sp   | ecified in Ta | ble 12.1, "C  | Comparator    | Electrical C  | haracteris-        |

|           | tics," on page                   | e 122.       |               |               |               |               |               |                    |

|           |                                  |              |               |               |               |               |               |                    |

### Figure 12.3. CPTnCN: Comparator 0, 1, and 2 Control Register

| DAA                                                      | DAA                                              | DAM            | DAM           | 5             | P          |        | DAM    | Desc()/slas |  |  |  |

|----------------------------------------------------------|--------------------------------------------------|----------------|---------------|---------------|------------|--------|--------|-------------|--|--|--|

| R/W                                                      | R/W                                              | R/W            | R/W           | R             | R          | R/W    | R/W    | Reset Value |  |  |  |

| -                                                        | -                                                | CPnRIE         | CPnFIE        | -             | -          | CPnMD1 | CPnMD0 | 00000010    |  |  |  |

| Bit7                                                     | Bit6                                             | Bit5           | Bit4          | Bit3          | Bit2       | Bit1   | Bit0   |             |  |  |  |

| SFR Addre                                                | ss: CPT0MD: 0                                    | x89; CPT1MD:   | 0x89; CPT2M   | D: 0x89       |            |        |        |             |  |  |  |

| SFR Page: CPT0MD: page 1; CPT1MD: page 2; CPT2MD: page 3 |                                                  |                |               |               |            |        |        |             |  |  |  |

|                                                          |                                                  |                |               |               |            |        |        |             |  |  |  |

| Bits7-6:                                                 | Bits7-6: UNUSED. Read = 00b, Write = don't care. |                |               |               |            |        |        |             |  |  |  |

| Bit 5:                                                   | CPnRIE: Co                                       | omparator R    | ising-Edge    | Interrupt Ena | able Bit.  |        |        |             |  |  |  |

|                                                          | 0: Compara                                       | tor rising-ec  | lge interrupt | disabled.     |            |        |        |             |  |  |  |

|                                                          | 1: Compara                                       | tor rising-ed  | lge interrupt | enabled.      |            |        |        |             |  |  |  |

| Bit 4:                                                   | CPnFIE: Co                                       | mparator Fa    | alling-Edge   | Interrupt En  | able Bit.  |        |        |             |  |  |  |

|                                                          | 0: Compara                                       | tor falling-ed | dge interrup  | t disabled.   |            |        |        |             |  |  |  |

|                                                          | 1: Compara                                       | tor falling-ed | dge interrup  | t enabled.    |            |        |        |             |  |  |  |

| Bits3-2:                                                 | UNUSED. F                                        | Read = $00b$ , | Write = dor   | i't care.     |            |        |        |             |  |  |  |

| Bits1-0:                                                 | CPnMD1-C                                         |                |               |               |            |        |        |             |  |  |  |

|                                                          |                                                  |                |               | e for the Con | nparator.  |        |        |             |  |  |  |

|                                                          |                                                  |                | •             |               | •          |        |        |             |  |  |  |

|                                                          | Mode                                             | CPnMD1         | CPnMD0        | N             | otes       |        |        |             |  |  |  |

|                                                          | 0                                                | 0              | 0             | Fastest Re    | sponse Tin | ne     |        |             |  |  |  |

|                                                          | 1                                                | 0              | 1             |               | -          |        |        |             |  |  |  |

|                                                          | 2                                                | 1              | 0             |               | -          |        |        |             |  |  |  |

|                                                          | 3                                                | 1              | 1             | Lowest Pov    | ver Consun | np-    |        |             |  |  |  |

|                                                          | 3                                                | I              | I             | t             | ion        |        |        |             |  |  |  |

|                                                          |                                                  |                |               |               |            |        |        |             |  |  |  |

### Figure 12.4. CPTnMD: Comparator Mode Selection Register

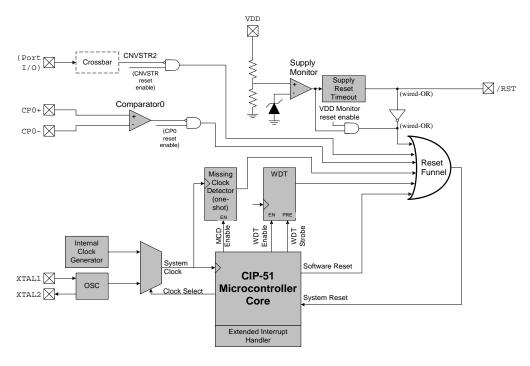

# 14. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External port pins are forced to a known configuration

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost even though the data on the stack are not altered.

The I/O port latches are reset to 0xFF (all logic 1's), activating internal weak pull-ups which take the external I/O pins to a high state. The external I/O pins do not go high immediately, but will go high within four system clock cycles after entering the reset state. This allows power to be conserved while the part is held in reset. For VDD Monitor resets, the /RST pin is driven low until the end of the VDD reset timeout.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator running at its lowest frequency. Refer to Section "15. Oscillators" on page 171 for information on selecting and configuring the system clock source. The Watchdog Timer is enabled using its longest timeout interval (see Section "14.7. Watchdog Timer Reset" on page 165). Once the system clock source is stable, program execution begins at location 0x0000.

There are seven sources for putting the MCU into the reset state: power-on, power-fail, external /RST pin, external CNVSTR2 signal, software command, Comparator0, Missing Clock Detector, and Watchdog Timer. Each reset source is described in the following sections.

### Figure 14.1. Reset Sources

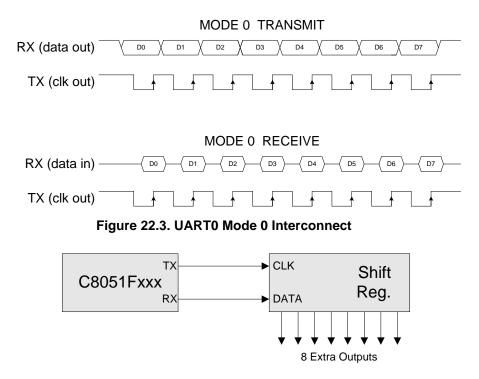

The Mode 0 baud rate is SYSCLK / 12. RX0 is forced to open-drain in Mode 0, and an external pull-up will typically be required.

Figure 22.2. UART0 Mode 0 Timing Diagram

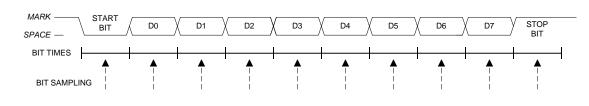

### 22.1.2. Mode 1: 8-Bit UART, Variable Baud Rate

Mode 1 provides standard asynchronous, full duplex communication using a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if SM20 is logic 1, the stop bit must be logic 1.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 are set.

Figure 22.4. UART0 Mode 1 Timing Diagram

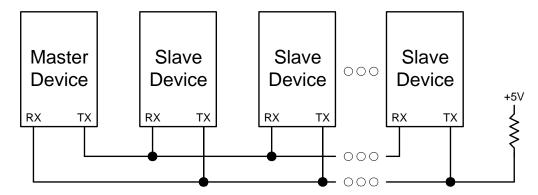

address as valid. If a master were to then send an address of "11111111", all three slave devices would recognize the address as a valid broadcast address.

### 22.3. Frame and Transmission Error Detection

### All Modes:

The Transmit Collision bit (TXCOL0 bit in register SCON0) reads '1' if user software writes data to the SBUF0 register while a transmit is in progress. Note that the TXCOL0 bit is also used as the SM20 bit when written by user software. This bit does not generate an interrupt.

#### Modes 1, 2, and 3:

The Receive Overrun bit (RXOV0 in register SCON0) reads '1' if a new data byte is latched into the receive buffer before software has read the previous byte. Note that the RXOV0 bit is also used as the SM10 bit when written by user software. The Frame Error bit (FE0 in register SSTA0) reads '1' if an invalid (low) STOP bit is detected. Note that the FE0 bit is also used as the SM00 bit when written by user software. The RXOV0 and FE0 bits do not generate interrupts.

| R/W    | R/W                                                                        | R/W                                                           | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W                                           | R/W                         | R/W           | R/W                   | Reset Value        |